#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 32MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, POR, PSMC, PWM, WDT                              |

| Number of I/O              | 35                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 512 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                              |

| Data Converters            | A/D 14x12b; D/A 1x8b                                                     |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

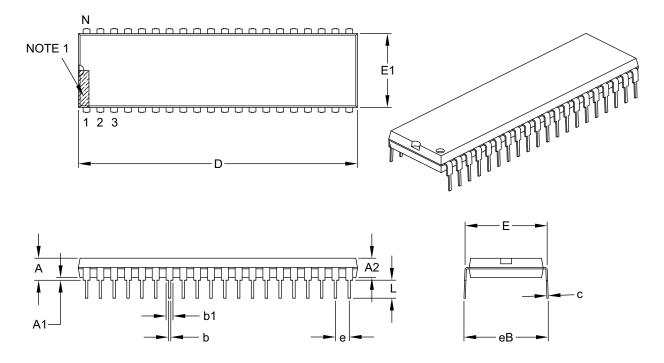

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                 |

| Supplier Device Package    | 40-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1784-i-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.0 MEMORY ORGANIZATION

These devices contain the following types of memory:

- Program Memory

- Configuration Words

- Device ID

- User ID

- Flash Program Memory

- Data Memory

- Core Registers

- Special Function Registers

- General Purpose RAM

- Common RAM

- Data EEPROM memory<sup>(1)</sup>

|         | Program Memory Control".            |      |    |         |       |      |        |      |

|---------|-------------------------------------|------|----|---------|-------|------|--------|------|

|         | Section 12.0 "Data EEPROM and Flash |      |    |         |       |      |        |      |

|         | the                                 | EECC | N  | registe | rs is | des  | cribed | 1 in |

|         |                                     |      |    | ess Fla |       |      | ,      | 0    |

| Note 1: | The                                 | Data | EE | PROM    | Mer   | mory | and    | the  |

The following features are associated with access and control of program memory and data memory:

- PCL and PCLATH

- Stack

- Indirect Addressing

# 3.1 Program Memory Organization

The enhanced mid-range core has a 15-bit program counter capable of addressing a 32K x 14 program memory space. Table 3-1 shows the memory sizes implemented for the PIC16(L)F1784/6/7 family. Accessing a location above these boundaries will cause a wrap-around within the implemented memory space. The Reset vector is at 0000h and the interrupt vector is at 0004h (see Figures 3-1 and 3-2).

#### TABLE 3-1: DEVICE SIZES AND ADDRESSES

| Device          | Program Memory Space (Words) | Last Program Memory Address |  |  |

|-----------------|------------------------------|-----------------------------|--|--|

| PIC16(L)F1784   | 4,096                        | 0FFFh                       |  |  |

| PIC16(L)F1786/7 | 8,192                        | 1FFFh                       |  |  |

# PIC16(L)F1784 MEMORY MAP (BANKS 8-31)

|              | BANK 8                                |              | BANK 9                                |                                      | BANK 10                                                             |                      | BANK 11                               |              | BANK 12                               |              | BANK 13                               |              | BANK 14                               |                      | BANK 15                               |

|--------------|---------------------------------------|--------------|---------------------------------------|--------------------------------------|---------------------------------------------------------------------|----------------------|---------------------------------------|--------------|---------------------------------------|--------------|---------------------------------------|--------------|---------------------------------------|----------------------|---------------------------------------|

| 400h<br>40Bh | Core Registers<br>(Table 3-2)         | 480h<br>48Bh | Core Registers<br>(Table 3-2)         | 500h<br>50Bh                         | Core Registers<br>(Table 3-2)                                       | 580h<br>58Bh         | Core Registers<br>(Table 3-2)         | 600h<br>60Bh | Core Registers<br>(Table 3-2)         | 680h<br>68Bh | Core Registers<br>(Table 3-2)         | 700h<br>70Bh | Core Registers<br>(Table 3-2)         | 780h<br>78Bh         | Core Registers<br>(Table 3-2)         |

| 40Ch         |                                       | 48Ch         |                                       | 50Ch<br>510h<br>511h<br>512h         | Unimplemented<br>Read as '0'<br>OPA1CON<br>—                        | 58Ch                 |                                       | 60Ch         |                                       | 68Ch         |                                       | 70Ch         |                                       | 78Ch                 |                                       |

|              | Unimplemented<br>Read as '0'          |              | Unimplemented<br>Read as '0'          | 513h<br>514h<br>519h<br>51Ah<br>51Bh | OPA2CON<br>Unimplemented<br>Read as '0'<br>CLKRCON<br>Unimplemented |                      | Unimplemented<br>Read as '0'          |              | Unimplemented<br>Read as '0'          |              | Unimplemented<br>Read as '0'          |              | Unimplemented<br>Read as '0'          |                      | Unimplemented<br>Read as '0'          |

| 46Fh         |                                       | 4EFh         |                                       | 56Fh                                 | Read as '0'                                                         | 5EFh                 |                                       | 66Fh         |                                       | 6EFh         |                                       | 76Fh         |                                       | 7EFh                 |                                       |

| 470h<br>47Fh | Common RAM<br>(Accesses<br>70h – 7Fh) | 4F0h<br>4FFh | Common RAM<br>(Accesses<br>70h – 7Fh) | 570h<br>57Fh                         | Common RAM<br>(Accesses<br>70h – 7Fh)                               | 5F0h<br>5FFh         | Common RAM<br>(Accesses<br>70h – 7Fh) | 670h<br>67Fh | Common RAM<br>(Accesses<br>70h – 7Fh) | 6F0h<br>6FFh | Common RAM<br>(Accesses<br>70h – 7Fh) | 770h<br>77Fh | Common RAM<br>(Accesses<br>70h – 7Fh) | 7F0h<br>7FFh         | Common RAM<br>(Accesses<br>70h – 7Fh) |

|              | BANK 16                               | I I          | BANK 17                               |                                      | BANK 18                                                             | 01111                | BANK 19                               | 0.111        | BANK 20                               | 0.1.11       | BANK 21                               |              | BANK 22                               |                      | BANK 23                               |

| 800h<br>80Bh | Core Registers<br>(Table 3-2)         | 880h<br>88Bh | Core Registers<br>(Table 3-2)         | 900h<br>90Bh                         | Core Registers<br>(Table 3-2)                                       | 980h<br>98Bh         | Core Registers<br>(Table 3-2)         | A00h<br>A0Bh | Core Registers<br>(Table 3-2)         | A80h<br>A8Bh | Core Registers<br>(Table 3-2)         | B00h<br>B0Bh | Core Registers<br>(Table 3-2)         | B80h<br>B8Bh         | Core Registers<br>(Table 3-2)         |

| 80Ch         | See Table 3-10                        | 88Ch         | Unimplemented<br>Read as '0'          | 90Ch                                 | Unimplemented<br>Read as '0'                                        | 98Ch                 | Unimplemented<br>Read as '0'          | A0Ch         | Unimplemented<br>Read as '0'          | A8Ch         | Unimplemented<br>Read as '0'          | B0Ch         | Unimplemented<br>Read as '0'          | B8Ch                 | Unimplemented<br>Read as '0'          |

| 86Fh<br>870h | Common RAM<br>(Accesses               | 8EFh<br>8F0h | Common RAM<br>(Accesses               | 96Fh<br>970h                         | Common RAM<br>(Accesses                                             | 9EFh<br>9F0h         | Common RAM<br>(Accesses               | A6Fh<br>A70h | Common RAM<br>(Accesses               | AEFh<br>AF0h | Common RAM<br>(Accesses               | B6Fh<br>B70h | Common RAM<br>(Accesses               | BEFh<br>BF0h         | Common RAM<br>(Accesses               |

| 87Fh         | 70h – 7Fh)                            | 8FFh         | 70h – 7Fh)                            | 97Fh                                 | 70h – 7Fh)                                                          | 9FFh                 | 70h – 7Fh)                            | A7Fh         | 70h – 7Fh)                            | AFFh         | 70h – 7Fh)                            | B7Fh         | 70h – 7Fh)                            | BFFh                 | 70h – 7Fh)                            |

| _            | BANK 24                               |              | BANK 25                               |                                      | BANK 26                                                             |                      | BANK 27                               |              | BANK 28                               |              | BANK 29                               |              | BANK 30                               |                      | BANK 31                               |

| C00h<br>C0Bh | Core Registers<br>(Table 3-2)         | C80h<br>C8Bh | Core Registers<br>(Table 3-2)         | D00h<br>D0Bh                         | Core Registers<br>(Table 3-2)                                       | D80h<br>D8Bh         | Core Registers<br>(Table 3-2)         | E00h<br>E0Bh | Core Registers<br>(Table 3-2)         | E80h<br>E8Bh | Core Registers<br>(Table 3-2)         | F00h<br>F0Bh | Core Registers<br>(Table 3-2)         | F80h<br>F8Bh         | Core Registers<br>(Table 3-2)         |

| C0Ch<br>C6Fh | Unimplemented<br>Read as '0'          | C8Ch<br>CEFh | Unimplemented<br>Read as '0'          | D0Ch<br>D6Fh                         | Unimplemented<br>Read as '0'                                        | D8Ch<br>DEFh         | Unimplemented<br>Read as '0'          | E0Ch<br>E6Fh | Unimplemented<br>Read as '0'          | E8Ch<br>EEFh | Unimplemented<br>Read as '0'          | F0Ch<br>F6Fh | Unimplemented<br>Read as '0'          | F8Ch<br>FEFh         | See Table 3-9                         |

| C70h<br>C70h | Common RAM<br>(Accesses<br>70h – 7Fh) | CF0h<br>CFFh | Common RAM<br>(Accesses<br>70h – 7Fh) | DoFn<br>D70h<br>D7Fh                 | Common RAM<br>(Accesses<br>70h – 7Fh)                               | DEFN<br>DF0h<br>DFFh | Common RAM<br>(Accesses<br>70h – 7Fh) | E70h         | Common RAM<br>(Accesses<br>70h – 7Fh) | EF0h<br>EFFh | Common RAM<br>(Accesses<br>70h – 7Fh) | F70h<br>F7Fh | Common RAM<br>(Accesses<br>70h – 7Fh) | FEFN<br>FF0h<br>FFFh | Common RAM<br>(Accesses<br>70h – 7Fh) |

Legend: = Unimplemented data memory locations, read as '0'

TABLE 3-6:

|      | LE 3-12:       | SFLUAL          |                                                                       | IN REGIS  |           |          |          | 7        |         |                      |                                 |

|------|----------------|-----------------|-----------------------------------------------------------------------|-----------|-----------|----------|----------|----------|---------|----------------------|---------------------------------|

| Addr | Name           | Bit 7           | Bit 6                                                                 | Bit 5     | Bit 4     | Bit 3    | Bit 2    | Bit 1    | Bit 0   | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

| Bank | 16 (Continued) | )               |                                                                       |           | •         |          |          |          |         |                      |                                 |

| 831h | PSMC2CON       | PSMC2EN         | PSMC2LD                                                               | PSMC2DBFE | PSMC2DBRE |          | P2MOE    | )E<3:0>  |         | 0000 0000            | 0000 0000                       |

| 832h | PSMC2MDL       | P2MDLEN         | P2MDLPOL                                                              | P2MDLBIT  | _         |          | P2MSR    | C<3:0>   |         | 000- 0000            | 000- 0000                       |

| 833h | PSMC2SYNC      | P2POFST         | P2PRPOL                                                               | P2DCPOL   | _         | —        | —        | P2SYN    | C<1:0>  | 00000                | 00000                           |

| 834h | PSMC2CLK       | —               | _                                                                     | P2CPF     | RE<1:0>   | —        | —        | P2CSR    | C<1:0>  | 0000                 | 0000                            |

| 835h | PSMC2OEN       | _               | _                                                                     | _         | —         | _        | _        | P2OEB    | P2OEA   | 00                   | 00                              |

| 836h | PSMC2POL       | —               | P2INPOL                                                               | —         | —         | —        | —        | P2POLB   | P2POLA  | -000                 | -000                            |

| 837h | PSMC2BLNK      | —               | —                                                                     | P2FEB     | M<1:0>    | —        | —        | P2REB    | M<1:0>  | 0000                 | 0000                            |

| 838h | PSMC2REBS      | P2REBIN         | _                                                                     | —         | P2REBSC4  | P2REBSC3 | P2REBSC2 | P2REBSC1 | _       | 00 000-              | 00 000-                         |

| 839h | PSMC2FEBS      | P2FEBIN         | _                                                                     | —         | P2FEBSC4  | P2FEBSC3 | P2FEBSC2 | P2FEBSC1 | _       | 00 000-              | 00 000-                         |

| 83Ah | PSMC2PHS       | P2PHSIN         | _                                                                     | —         | P2PHSC4   | P2PHSC3  | P2PHSC2  | P2PHSC1  | P2PHST  | 00 0000              | 00 0000                         |

| 83Bh | PSMC2DCS       | P2DCSIN         | _                                                                     | —         | P2DCSC4   | P2DCSC3  | P2DCSC2  | P2DCSC1  | P2DCST  | 00 0000              | 00 0000                         |

| 83Ch | PSMC2PRS       | P2PRSIN         | —                                                                     | —         | P2PRSC4   | P2PRSC3  | P2PRSC2  | P2PRSC1  | P2PRST  | 00 0000              | 00 0000                         |

| 83Dh | PSMC2ASDC      | P2ASE           | P2ASDEN                                                               | P2ARSEN   | —         | _        | _        | _        | P2ASDOV | 0000                 | 0000                            |

| 83Eh | PSMC2ASDL      | —               | _                                                                     | P2ASDLF   | P2ASDLE   | P2ASDLD  | P2ASDLC  | P2ASDLB  | P2ASDLA | 00 0000              | 00 0000                         |

| 83Fh | PSMC2ASDS      | P2ASDSIN        | _                                                                     | —         | P2ASDSC4  | P2ASDSC3 | P2ASDSC2 | P2ASDSC1 | —       | 00 000-              | 00 000-                         |

| 840h | PSMC2INT       | P2TOVIE         | P2TPHIE                                                               | P2TDCIE   | P2TPRIE   | P2TOVIF  | P2TPHIF  | P2TDCIF  | P2TPRIF | 0000 0000            | 0000 0000                       |

| 841h | PSMC2PHL       | Phase Low Co    | unt                                                                   |           |           |          |          |          |         | 0000 0000            | 0000 0000                       |

| 842h | PSMC2PHH       | Phase High Co   | ount                                                                  |           |           |          |          |          |         | 0000 0000            | 0000 0000                       |

| 843h | PSMC2DCL       | Duty Cycle Lov  | w Count                                                               |           |           |          |          |          |         | 0000 0000            | 0000 0000                       |

| 844h | PSMC2DCH       | Duty Cycle Hig  | gh Count                                                              |           |           |          |          |          |         | 0000 0000            | 0000 0000                       |

| 845h | PSMC2PRL       | Period Low Co   | ount                                                                  |           |           |          |          |          |         | 0000 0000            | 0000 0000                       |

| 846h | PSMC2PRH       | Period High Co  | ount                                                                  |           |           |          |          |          |         | 0000 0000            | 0000 0000                       |

| 847h | PSMC2TMRL      | Time base Lov   | v Counter                                                             |           |           |          |          |          |         | 0000 0001            | 0000 0001                       |

| 848h | PSMC2TMRH      | Time base Hig   | h Counter                                                             |           |           |          |          |          |         | 0000 0000            | 0000 0000                       |

| 849h | PSMC2DBR       | rising Edge De  | ad-band Cou                                                           | nter      |           |          |          |          |         | 0000 0000            | 0000 0000                       |

| 84Ah | PSMC2DBF       | Falling Edge D  | Falling Edge Dead-band Counter 0000 0000 0                            |           |           |          |          |          |         |                      | 0000 0000                       |

| 84Bh | PSMC2BLKR      | rising Edge Bla | rising Edge Blanking Counter 0000 0000 0                              |           |           |          |          |          |         |                      | 0000 0000                       |

| 84Ch | PSMC2BLKF      | Falling Edge B  | lanking Coun                                                          | ter       |           | r        |          |          |         | 0000 0000            | 0000 0000                       |

| 84Dh | PSMC2FFA       | —               | —         —         Fractional Frequency Adjust Register         0000 |           |           |          |          |          |         | 0000                 | 0000                            |

| 84Eh | PSMC2STR0      | —               | —                                                                     | —         | —         | —        | —        | P2STRB   | P2STRA  | 01                   | 01                              |

| 84Fh | PSMC2STR1      | P2SYNC          | —                                                                     | —         | -         | —        | —        | P2LSMEN  | P2HSMEN | 000                  | 000                             |

| 850h | _              | Unimplemente    | d                                                                     |           |           |          |          |          |         | —                    | -                               |

TABLE 3-12: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Legend:

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

**Note 1:** These registers can be addressed from any bank.

2: Unimplemented, read as '1'.

3: PIC16(L)F1784/7 only.

4: PIC16F1784/6/7 only.

| TABLE 3-12: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED | TABLE 3-12: | R SUMMARY (CONTINUED) |

|----------------------------------------------------------|-------------|-----------------------|

|----------------------------------------------------------|-------------|-----------------------|

|                 | ••••••                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                           |                                               |                                                        |                                                                                                | 1                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                  |                                                                                                                                          |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-----------------------------------------------|--------------------------------------------------------|------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| Name            | Bit 7                                                                                                                                | Bit 6                                                                                                                                                                                                                                                                                                                                                                                                                                    | Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 |                                               |                                                        |                                                                                                |                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                  | Value on<br>all other<br>Resets                                                                                                          |

| Bank 31         |                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                           |                                               |                                                        |                                                                                                |                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                  |                                                                                                                                          |

| _               | Unimplemente                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                           |                                               |                                                        |                                                                                                |                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                  | _                                                                                                                                        |

| STATUS_<br>SHAD | —                                                                                                                                    | -                                                                                                                                                                                                                                                                                                                                                                                                                                        | —                                         | —                                             | —                                                      | Z                                                                                              | DC                                                                                       | С                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | xxx                                                                                                              | uuu                                                                                                                                      |

| WREG_SHAD       | Working Regis                                                                                                                        | orking Register Shadow xxxx xxxx uuuu uuuu                                                                                                                                                                                                                                                                                                                                                                                               |                                           |                                               |                                                        |                                                                                                |                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                  |                                                                                                                                          |

| BSR_SHAD        | _                                                                                                                                    | — — Bank Select Register Shadow                                                                                                                                                                                                                                                                                                                                                                                                          |                                           |                                               |                                                        |                                                                                                |                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                  | u uuuu                                                                                                                                   |

| PCLATH_<br>SHAD | Program Counter Latch High Register Shadow                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                           |                                               |                                                        |                                                                                                |                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | -xxx xxxx                                                                                                        | uuuu uuuu                                                                                                                                |

| FSR0L_SHAD      | Indirect Data Memory Address 0 Low Pointer Shadow                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                           |                                               |                                                        |                                                                                                |                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | uuuu uuuu                                                                                                        |                                                                                                                                          |

| FSR0H_<br>SHAD  | Indirect Data M                                                                                                                      | lemory Addre                                                                                                                                                                                                                                                                                                                                                                                                                             | ss 0 High Poin                            | ter Shadow                                    |                                                        |                                                                                                |                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | XXXX XXXX                                                                                                        | uuuu uuuu                                                                                                                                |

| FSR1L_SHAD      | Indirect Data M                                                                                                                      | lemory Addre                                                                                                                                                                                                                                                                                                                                                                                                                             | ss 1 Low Point                            | er Shadow                                     |                                                        |                                                                                                |                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | XXXX XXXX                                                                                                        | uuuu uuuu                                                                                                                                |

| FSR1H_<br>SHAD  | Indirect Data M                                                                                                                      | ndirect Data Memory Address 1 High Pointer Shadow xxxx xxxx uuuu u                                                                                                                                                                                                                                                                                                                                                                       |                                           |                                               |                                                        |                                                                                                |                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                  | uuuu uuuu                                                                                                                                |

| _               | Unimplemente                                                                                                                         | Jnimplemented                                                                                                                                                                                                                                                                                                                                                                                                                            |                                           |                                               |                                                        |                                                                                                |                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | —                                                                                                                | _                                                                                                                                        |

| STKPTR          | —                                                                                                                                    | — — Current Stack Pointer                                                                                                                                                                                                                                                                                                                                                                                                                |                                           |                                               |                                                        |                                                                                                |                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                  | 1 1111                                                                                                                                   |

| TOSL            | Top of Stack Lo                                                                                                                      | Top of Stack Low byte xxxx xxxx 1                                                                                                                                                                                                                                                                                                                                                                                                        |                                           |                                               |                                                        |                                                                                                |                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | uuuu uuuu                                                                                                        |                                                                                                                                          |

| TOSH            | —                                                                                                                                    | Top of Stack                                                                                                                                                                                                                                                                                                                                                                                                                             | High byte                                 |                                               |                                                        |                                                                                                |                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | -xxx xxxx                                                                                                        | -uuu uuuu                                                                                                                                |

|                 | Name   STATUS_ SHAD  STATUS_ SHAD  WREG_SHAD  BSR_SHAD  PCLATH_ SHAD  FSR0L_SHAD  FSR0H_ SHAD  FSR1L_SHAD  FSR1H_ SHAD  STKPTR  TOSL | Name     Bit 7       C 31     Unimplemente       STATUS_<br>SHAD     —       VREG_SHAD     Working Regis       BSR_SHAD     —       PCLATH_<br>SHAD     Moirking Regis       FSR0L_SHAD     Indirect Data M       FSR0H_<br>SHAD     Indirect Data M       FSR1L_SHAD     Indirect Data M       FSR1H_<br>SHAD     Indirect Data M       FSR1H_<br>SHAD     Indirect Data M       FSR1H_<br>STKPTR     —       TOSL     Top of Stack Log | Name     Bit 7     Bit 6       <31        | Name     Bit 7     Bit 6     Bit 5       < 31 | Name     Bit 7     Bit 6     Bit 5     Bit 4       <31 | Name       Bit 7       Bit 6       Bit 5       Bit 4       Bit 3         -       Unimplemented | Name       Bit 7       Bit 6       Bit 5       Bit 4       Bit 3       Bit 2         (31 | Name       Bit 7       Bit 6       Bit 5       Bit 4       Bit 3       Bit 2       Bit 1         C31        Unimplemented         Z       DC         STATUS_<br>SHAD          Z       DC         WREG_SHAD       Working Register Shadow       Bank Select Register Shadow       BSR_SHAD         Bank Select Register Shadow         PCLATH_<br>SHAD         Bank Select Register Shadow         DC         SRS_SHAD         Bank Select Register Shadow         DC         SROL_SHAD       Indirect Data Memory Address 0 Low Pointer Shadow         Stadow          FSROL_SHAD       Indirect Data Memory Address 1 Low Pointer Shadow             FSR1L_SHAD       Indirect Data Memory Address 1 Low Pointer Shadow             FSR1H_SHAD       Indirect Data Memory Address 1 High Pointer Shadow              Unimplemented         Current Stack Pointer           TOP of Stack Low byte | Name       Bit 7       Bit 6       Bit 5       Bit 4       Bit 3       Bit 2       Bit 1       Bit 0         <31 | Name       Bit 7       Bit 6       Bit 5       Bit 4       Bit 3       Bit 2       Bit 1       Bit 0       Value on POR, BOR         <31 |

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'. These registers can be addressed from any bank. Unimplemented, read as '1'. Legend:

Note

1: 2:

PIC16(L)F1784/7 only. 3:

4: PIC16F1784/6/7 only.

# 4.0 DEVICE CONFIGURATION

Device configuration consists of Configuration Words, Code Protection and Device ID.

### 4.1 Configuration Words

There are several Configuration Word bits that allow different oscillator and memory protection options. These are implemented as Configuration Word 1 at 8007h and Configuration Word 2 at 8008h.

Note: The DEBUG bit in Configuration Words is managed automatically by device development tools including debuggers and programmers. For normal device operation, this bit should be maintained as a '1'.

#### 13.6 Register Definitions: PORTB

#### **REGISTER 13-11: PORTB: PORTB REGISTER**

| R/W-x/u                                 | R/W-x/u | R/W-x/u           | R/W-x/u                                               | R/W-x/u                            | R/W-x/u | R/W-x/u | R/W-x/u |  |  |

|-----------------------------------------|---------|-------------------|-------------------------------------------------------|------------------------------------|---------|---------|---------|--|--|

| RB7                                     | RB6     | RB5               | RB4                                                   | RB3                                | RB2     | RB1     | RB0     |  |  |

| bit 7                                   |         |                   |                                                       |                                    |         |         | bit 0   |  |  |

|                                         |         |                   |                                                       |                                    |         |         |         |  |  |

| Legend:                                 |         |                   |                                                       |                                    |         |         |         |  |  |

| R = Readable I                          | bit     | W = Writable      | bit                                                   | U = Unimplemented bit, read as '0' |         |         |         |  |  |

| u = Bit is unchanged x = Bit is unknown |         |                   | -n/n = Value at POR and BOR/Value at all other Resets |                                    |         |         |         |  |  |

| '1' = Bit is set                        |         | '0' = Bit is clea | ared                                                  |                                    |         |         |         |  |  |

bit 7-0 **RB<7:0>**: PORTB General Purpose I/O Pin bits<sup>(1)</sup> 1 = Port pin is ≥ VIH 0 = Port pin is ≤ VIL

#### REGISTER 13-12: TRISB: PORTB TRI-STATE REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| TRISB7  | TRISB6  | TRISB5  | TRISB4  | TRISB3  | TRISB2  | TRISB1  | TRISB0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

TRISB<7:0>: PORTB Tri-State Control bits

1 = PORTB pin configured as an input (tri-stated)

0 = PORTB pin configured as an output

#### REGISTER 13-13: LATB: PORTB DATA LATCH REGISTER

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

| LATB7   | LATB6   | LATB5   | LATB4   | LATB3   | LATB2   | LATB1   | LATB0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 LATB<7:0>: PORTB Output Latch Value bits<sup>(1)</sup>

**Note 1:** Writes to PORTB are actually written to corresponding LATB register. Reads from PORTB register is return of actual I/O pin values.

**Note 1:** Writes to PORTB are actually written to corresponding LATB register. Reads from PORTB register is return of actual I/O pin values.

| R/W-1/1          | R/W-1/1 R/W     |                                                                            | R/W-1/1                                               | R/W-1/1                                                                                                                                   | R/W-1/1                                                                                                                                                                                            | R/W-1/1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|------------------|-----------------|----------------------------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| ANSB6            | ANSB5 ANSB4     |                                                                            | ANSB3                                                 | ANSB2                                                                                                                                     | ANSB1                                                                                                                                                                                              | ANSB0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|                  |                 |                                                                            |                                                       | •                                                                                                                                         |                                                                                                                                                                                                    | bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|                  |                 |                                                                            |                                                       |                                                                                                                                           |                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|                  |                 |                                                                            |                                                       |                                                                                                                                           |                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |