Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PSMC, PWM, WDT                               |

| Number of I/O              | 35                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 512 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 14x12b; D/A 1x8b                                                      |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-TQFP                                                                   |

| Supplier Device Package    | 44-TQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1784-i-pt |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Digital Peripheral Features:**

- Timer0: 8-Bit Timer/Counter with 8-Bit Programmable Prescaler

- Enhanced Timer1:

- 16-bit timer/counter with prescaler

- External Gate Input mode

- Dedicated low-power 32 kHz oscillator driver

- Timer2: 8-Bit Timer/Counter with 8-Bit Period Register, Prescaler and Postscaler

- Two Capture/Compare/PWM modules (CCP):

- 16-bit capture, maximum resolution 12.5 ns

- 16-bit compare, max resolution 31.25 ns

- 10-bit PWM, max frequency 32 kHz

- Master Synchronous Serial Port (SSP) with SPI and I<sup>2</sup>C<sup>™</sup> with:

- 7-bit address masking

- SMBus/PMBus<sup>™</sup> compatibility

- Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART):

- RS-232, RS-485 and LIN compatible

- Auto-baud detect

- Auto-wake-up on start

# **Oscillator Features:**

- Operate up to 32 MHz from Precision Internal Oscillator:

- Factory calibrated to ±1%, typical

- Software selectable frequency range from 32 MHz to 31 kHz

- 31 kHz Low-Power Internal Oscillator

- 32.768 kHz Timer1 Oscillator:

- Available as system clock

- Low-power RTC

- External Oscillator Block with:

- 4 crystal/resonator modes up to 32 MHz using 4x PLL

- 3 external clock modes up to 32 MHz

- 4x Phase-Locked Loop (PLL)

- Fail-Safe Clock Monitor:

- Detect and recover from external oscillator failure

- Two-Speed Start-up:

- Minimize latency between code execution and external oscillator start-up

# **General Microcontroller Features:**

- Power-Saving Sleep mode

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR) with Selectable Trip Point

- Extended Watchdog Timer (WDT)

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

- In-Circuit Debug (ICD)

- Enhanced Low-Voltage Programming (LVP)

- Operating Voltage Range:

- 1.8V to 3.6V (PIC16LF1784/6/7)

- 2.3V to 5.5V (PIC16F1784/6/7)

#### **Table of Contents**

| 1.0   | Device Overview                                |     |

|-------|------------------------------------------------|-----|

| 2.0   | Enhanced Mid-Range CPU                         |     |

| 3.0   | Memory Organization                            | 23  |

| 4.0   | Device Configuration                           | 53  |

| 5.0   | Resets                                         | 59  |

| 6.0   | Oscillator Module                              | 67  |

| 7.0   | Reference Clock Module                         | 85  |

| 8.0   | Interrupts                                     |     |

| 9.0   | Power-Down Mode (Sleep)                        | 103 |

|       | Low Dropout (LDO) Voltage Regulator            |     |

| 11.0  | Watchdog Timer (WDT)                           |     |

| 12.0  | Date EEPROM and Flash Program Memory Control   |     |

| 13.0  | I/O Ports                                      | 125 |

| 14.0  | Interrupt-on-Change                            |     |

| 15.0  | Fixed Voltage Reference (FVR)                  |     |

|       | Temperature Indicator                          |     |

| 17.0  | Analog-to-Digital Converter (ADC) Module       |     |

| 18.0  | Operational Amplifier (OPA) Module             |     |

|       | Digital-to-Analog Converter (DAC) Module       |     |

|       | Comparator Module                              |     |

| 21.0  | Timer0 Module                                  | 196 |

|       | Timer1 Module                                  |     |

|       | Timer2 Module                                  |     |

|       | Programmable Switch Mode Control (PSMC) Module |     |

|       | Capture/Compare/PWM Module                     |     |

|       | Master Synchronous Serial Port (MSSP) Module   |     |

|       | · · · · · · · · · · · · · · · · · · ·          |     |

|       | In-Circuit Serial Programming™ (ICSP™)         |     |

|       | Instruction Set Summary                        |     |

|       | Electrical Specifications                      |     |

| 31.0  | DC and AC Characteristics Graphs and Tables    |     |

| 32.0  | Development Support                            |     |

|       | Packaging Information                          |     |

|       | ndix A: Revision History                       |     |

|       | Aicrochip Web Site                             |     |

|       | omer Change Notification Service               |     |

|       | omer Support                                   |     |

| Produ | uct Identification System                      | 462 |

# PIC16(L)F1784/6/7

#### TABLE 3-12: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

|            |         |              |       |       |       |       |       | /     |       |                      |                                 |

|------------|---------|--------------|-------|-------|-------|-------|-------|-------|-------|----------------------|---------------------------------|

| Addr       | Name    | Bit 7        | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

| Bank       | c 11-15 |              |       |       |       |       |       |       |       |                      |                                 |

| x0Ch       |         |              |       |       |       |       |       |       |       |                      |                                 |

| or<br>x8Ch |         |              |       |       |       |       |       |       |       |                      |                                 |

| to         | _       | Unimplemente | d     |       |       |       |       |       |       | _                    | _                               |

| x6Fh       |         |              |       |       |       |       |       |       |       |                      |                                 |

| or<br>xEFh |         |              |       |       |       |       |       |       |       |                      |                                 |

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

**1:** These registers can be addressed from any bank.

**2:** Unimplemented, read as '1'.

3: PIC16(L)F1784/7 only.

Note

4: PIC16F1784/6/7 only.

# PIC16(L)F1784/6/7

#### Value on Value on Addr Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Name all other POR, BOR Resets Bank 16 (Continued) PSMC3LD **P3DBRE** 851h PSMC3CON PSMC3EN **P3DBFE** P3MODE<3:0> 0000 0000 0000 0000 PSMC3MDL P3MDLEN 852h P3MDLPOL P3MDLBIT P3MSRC<3:0> \_ 000- 0000 000 -0000 --00 853h PSMC3SYNC **P3POFST P3PRPOL P3DCPOL** \_ P3SYNC<1:0> 000---00 000-P3CPRE<1:0> P3CSRC<1:0> 854h PSMC3CLK -00 --00 -00 --00 855h PSMC3OEN P3OEB P3OEA --00 --00 \_ \_ \_ \_ \_ \_ 856h PSMC3POL **P3INPOL P3POLB** P3POLA \_ -0----00 -0----00 857h PSMC3BLNK P3FEBM<1:0> P3REBM<1:0> --00 --00 --00 --00 858h PSMC3REBS **P3REBSIN** P3REBSC4 P3REBSC3 P3REBSC2 P3REBSC1 0--0 000-0--0 000 P3FEBSC2 859h PSMC3FEBS **P3FEBSIN** P3FEBSC4 P3FEBSC3 P3FEBSC1 0--0 000-0--0 000-85Ah PSMC3PHS **P3PHSIN** P3PHSC4 P3PHSC3 P3PHSC2 P3PHSC1 **P3PHST** 0--0 0000 0--0 0000 PSMC3DCS P3DCSC1 85Bh **P3DCSIN** P3DCSC4 P3DCSC3 P3DCSC2 0--0 0000 P3DCST 0--0 0000 P3PRSC4 P3PRSC3 P3PRSC2 P3PRSC1 85Ch PSMC3PRS **P3PRSIN P3PRST** 0--0 0000 0--0 0000 PSMC3ASDC **P3ARSEN** 85Dh P3ASE **P3ASDEN P3ASDOV** 000- ---0 000----0 \_ 85Eh PSMC3ASDL \_ **P3ASDLB P3ASDLA** ------00 \_\_\_\_ --00 85Fh PSMC3ASDS **P3ASDSIN** P3ASDSC4 P3ASDSC3 P3ASDSC2 P3ASDSC1 0--0 000-0--0 000 860h PSMC3INT **P3TOVIE P3TPHIE P3TDCIE P3TPRIE P3TOVIF** P3TPHIF P3TDCIF P3TPRIF 0000 0000 0000 0000 861h PSMC3PHL Phase Low Count 0000 0000 0000 0000 PSMC3PHH Phase High Count 862h 0000 0000 0000 0000 863h PSMC3DCL Duty Cycle Low Count 0000 0000 0000 0000 864h PSMC3DCH Duty Cycle High Count 0000 0000 0000 0000 865h PSMC3PRL Period Low Count 0000 0000 0000 0000 866h PSMC3PRH Period High Count 0000 0000 0000 0000 867h PSMC3TMRL Time base Low Counter 0000 0001 0000 0001 PSMC3TMRH 868h Time base High Counter 0000 0000 0000 0000 869h PSMC3DBR Rising Edge Dead-band Counter 0000 0000 0000 0000 PSMC3DBF 86Ah Falling Edge Dead-band Counter 0000 0000 0000 0000 86Bh PSMC3BLKR Rising Edge Blanking Counter 0000 0000 0000 0000 86Ch PSMC3BLKF Falling Edge Blanking Counter 0000 0000 0000 0000 86Dh PSMC3FFA 0000 Fractional Frequency Adjust Register ----0000 86Eh PSMC3STR0 P3STRA **P3STRB** -01 --01 **P3HSMEN** 86Fh PSMC3STR1 **P3LSMEN** P3SSYNC 0 - - ---00 0-----00

#### TABLE 3-12: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Bank 17-30

Note

| x0Ch |   |               |   |   |  |  |

|------|---|---------------|---|---|--|--|

| or   |   |               |   |   |  |  |

| x8Ch |   |               |   |   |  |  |

| to   | _ | Unimplemented | — | — |  |  |

| x1Fh |   |               |   |   |  |  |

| or   |   |               |   |   |  |  |

| x9Fh |   |               |   |   |  |  |

| 1    |   |               |   |   |  |  |

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved.

Shaded locations are unimplemented, read as '0'.

1: These registers can be addressed from any bank.

2: Unimplemented, read as '1'.

3: PIC16(L)F1784/7 only.

4: PIC16F1784/6/7 only.

# 4.3 Code Protection

Code protection allows the device to be protected from unauthorized access. Program memory protection and data EEPROM protection are controlled independently. Internal access to the program memory and data EEPROM are unaffected by any code protection setting.

#### 4.3.1 PROGRAM MEMORY PROTECTION

The entire program memory space is protected from external reads and writes by the  $\overline{CP}$  bit in Configuration Words. When  $\overline{CP} = 0$ , external reads and writes of program memory are inhibited and a read will return all '0's. The CPU can continue to read program memory, regardless of the protection bit settings. Writing the program memory is dependent upon the write protection setting. See **Section 4.4** "Write **Protection**" for more information.

# 4.3.2 DATA EEPROM PROTECTION

The entire data EEPROM is protected from external reads and writes by the CPD bit. When CPD = 0, external reads and writes of data EEPROM are inhibited. The CPU can continue to read and write data EEPROM regardless of the protection bit settings.

## 4.4 Write Protection

Write protection allows the device to be protected from unintended self-writes. Applications, such as bootloader software, can be protected while allowing other regions of the program memory to be modified.

The WRT<1:0> bits in Configuration Words define the size of the program memory block that is protected.

# 4.5 User ID

Four memory locations (8000h-8003h) are designated as ID locations where the user can store checksum or other code identification numbers. These locations are readable and writable during normal execution. See **Section 12.5 "User ID, Device ID and Configuration Word Access**" for more information on accessing these memory locations. For more information on checksum calculation, see the *"PIC16(L)F178X Memory Programming Specification"* (DS41457).

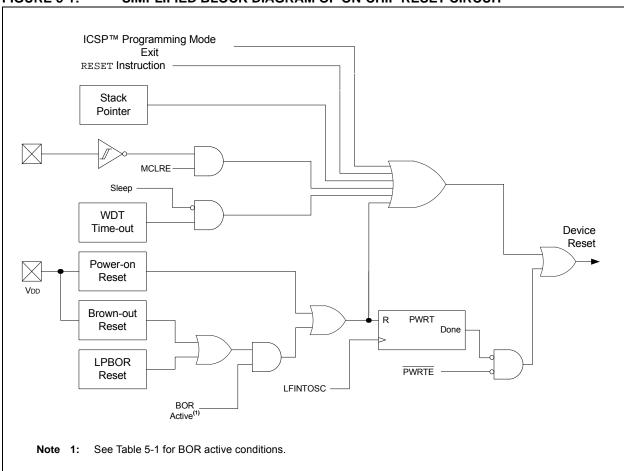

A simplified block diagram of the On-Chip Reset Circuit

is shown in Figure 5-1.

# 5.0 RESETS

There are multiple ways to reset this device:

- Power-On Reset (POR)

- Brown-Out Reset (BOR)

- Low-Power Brown-Out Reset (LPBOR)

- MCLR Reset

- WDT Reset

- RESET instruction

- Stack Overflow

- Stack Underflow

- · Programming mode exit

To allow VDD to stabilize, an optional Power-up Timer can be enabled to extend the Reset time after a BOR or POR event.

#### FIGURE 5-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

# 5.13 Power Control (PCON) Register

The Power Control (PCON) register contains flag bits to differentiate between a:

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- Reset Instruction Reset (RI)

- MCLR Reset (RMCLR)

- Watchdog Timer Reset (RWDT)

- Stack Underflow Reset (STKUNF)

- Stack Overflow Reset (STKOVF)

# 5.14 Register Definitions: Power Control

#### REGISTER 5-2: PCON: POWER CONTROL REGISTER

| R/W/HS-0/q  | R/W/HS-0/q | U-0 | R/W/HC-1/q | R/W/HC-1/q | R/W/HC-1/q | R/W/HC-q/u | R/W/HC-q/u |

|-------------|------------|-----|------------|------------|------------|------------|------------|

| STKOVF      | STKUNF     | _   | RWDT       | RMCLR      | RI         | POR        | BOR        |

| bit 7 bit 0 |            |     |            |            |            |            |            |

| Legend:                    |                      |                                                       |

|----------------------------|----------------------|-------------------------------------------------------|

| HC = Bit is cleared by har | dware                | HS = Bit is set by hardware                           |

| R = Readable bit           | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged       | x = Bit is unknown   | -m/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set           | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7 | STKOVF: Stack Overflow Flag bit                                                                   |

|-------|---------------------------------------------------------------------------------------------------|

|       | 1 = A Stack Overflow occurred                                                                     |

|       | 0 = A Stack Overflow has not occurred or cleared by firmware                                      |

| bit 6 | STKUNF: Stack Underflow Flag bit                                                                  |

|       | 1 = A Stack Underflow occurred                                                                    |

|       | 0 = A Stack Underflow has not occurred or cleared by firmware                                     |

| bit 5 | Unimplemented: Read as '0'                                                                        |

| bit 4 | RWDT: Watchdog Timer Reset Flag bit                                                               |

|       | 1 = A Watchdog Timer Reset has not occurred or set to '1' by firmware                             |

|       | 0 = A Watchdog Timer Reset has occurred (cleared by hardware)                                     |

| bit 3 | RMCLR: MCLR Reset Flag bit                                                                        |

|       | 1 = A MCLR Reset has not occurred or set to '1' by firmware                                       |

|       | <ul> <li>A MCLR Reset has occurred (cleared by hardware)</li> </ul>                               |

| bit 2 | RI: RESET Instruction Flag bit                                                                    |

|       | 1 = A RESET instruction has not been executed or set to '1' by firmware                           |

|       | 0 = A RESET instruction has been executed (cleared by hardware)                                   |

| bit 1 | POR: Power-on Reset Status bit                                                                    |

|       | 1 = No Power-on Reset occurred                                                                    |

|       | 0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)             |

| bit 0 | BOR: Brown-out Reset Status bit                                                                   |

|       | 1 = No Brown-out Reset occurred                                                                   |

|       | 0 = A Brown-out Reset occurred (must be set in software after a Power-on Reset or Brown-out Reset |

|       | occurs)                                                                                           |

|       |                                                                                                   |

The PCON register bits are shown in Register 5-2.

#### EXAMPLE 12-2: DATA EEPROM WRITE

| Required<br>Sequence | BANKSEL<br>MOVLW<br>MOVLW<br>MOVWF<br>BCF<br>BCF<br>BSF<br>BCF<br>MOVLW<br>MOVLW<br>MOVLW<br>BSF<br>BSF<br>BCF<br>BCF<br>BCF | EECON1, WREN<br>INTCON, GIE<br>55h<br>EECON2<br>0AAh<br>EECON2<br>EECON1, WR<br>INTCON, GIE<br>EECON1, WREN | <pre>;Data Memory Address to write<br/>;<br/>;Data Memory Value to write<br/>;Deselect Configuration space<br/>;Point to DATA memory<br/>;Enable writes<br/>;Disable INTs.<br/>;<br/>;Write 55h<br/>;<br/>;Write 55h<br/>;<br/>;Write AAh<br/>;Set WR bit to begin write<br/>;Enable Interrupts<br/>;Disable writes</pre> |

|----------------------|------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                      |                                                                                                                              | •                                                                                                           | -                                                                                                                                                                                                                                                                                                                         |

|                      | BTFSC                                                                                                                        | EECON1, WR                                                                                                  | ;Wait for write to complete                                                                                                                                                                                                                                                                                               |

|                      | GOTO                                                                                                                         | \$-2                                                                                                        | ;Done                                                                                                                                                                                                                                                                                                                     |

|                      |                                                                                                                              |                                                                                                             |                                                                                                                                                                                                                                                                                                                           |

|                              | Q1 Q2 Q3 Q4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Flash ADDR                   | I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I |

| Flash Data                   | INSTR (PC) INSTR (PC + 1) ZEEDATH,EEDATL INSTR (PC + 3) INSTR (PC + 4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                              | INSTR(PC - 1)       BSF PMCON1,RD       INSTR(PC + 1)       Forced NOP       INSTR(PC + 3)       INSTR(PC + 4)         executed here       executed here       executed here       executed here       executed here                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| RD bit                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| EEDATH<br>EEDATL<br>Register |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Register                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

#### 13.3.7 PORTA FUNCTIONS AND OUTPUT PRIORITIES

Each PORTA pin is multiplexed with other functions. The pins, their combined functions and their output priorities are shown in Table 13-2.

When multiple outputs are enabled, the actual pin control goes to the peripheral with the highest priority.

Analog input functions, such as ADC, and comparator inputs, are not shown in the priority lists. These inputs are active when the I/O pin is set for Analog mode using the ANSELx registers. Digital output functions may control the pin when it is in Analog mode with the priority shown in the priority list.

| Pin Name | Function Priority <sup>(1)</sup> |

|----------|----------------------------------|

| RA0      | RA0                              |

| RA1      | OPA1OUT<br>RA1                   |

| RA2      | DAC1OUT1<br>RA2                  |

| RA3      | RA3                              |

| RA4      | C1OUT<br>RA4                     |

| RA5      | C2OUT<br>RA5                     |

| RA6      | CLKOUT<br>C2OUT<br>RA6           |

| RA7      | RA7                              |

TABLE 13-2: PORTA OUTPUT PRIORITY

Note 1: Priority listed from highest to lowest.

## 13.7 PORTC Registers

#### 13.7.1 DATA REGISTER

PORTC is an 8-bit wide bidirectional port. The corresponding data direction register is TRISC (Register 13-20). Setting a TRISC bit (= 1) will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISC bit (= 0) will make the corresponding PORTC pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). Example 13-1 shows how to initialize an I/O port.

Reading the PORTC register (Register 13-19) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATC).

#### 13.7.2 DIRECTION CONTROL

The TRISC register (Register 13-20) controls the PORTC pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISC register are maintained set when using them as analog inputs. I/O pins configured as analog inputs always read '0'.

## 13.7.3 OPEN DRAIN CONTROL

The ODCONC register (Register 13-23) controls the open-drain feature of the port. Open drain operation is independently selected for each pin. When an ODCONC bit is set, the corresponding port output becomes an open drain driver capable of sinking current only. When an ODCONC bit is cleared, the corresponding port output pin is the standard push-pull drive capable of sourcing and sinking current.

#### 13.7.4 SLEW RATE CONTROL

The SLRCONC register (Register 13-24) controls the slew rate option for each port pin. Slew rate control is independently selectable for each port pin. When an SLRCONC bit is set, the corresponding port pin drive is slew rate limited. When an SLRCONC bit is cleared, The corresponding port pin drive slews at the maximum rate possible.

#### 13.7.5 INPUT THRESHOLD CONTROL

The INLVLC register (Register 13-25) controls the input voltage threshold for each of the available PORTC input pins. A selection between the Schmitt Trigger CMOS or the TTL Compatible thresholds is available. The input threshold is important in determining the value of a read of the PORTC register and also the

level at which an interrupt-on-change occurs, if that feature is enabled. See **Section TABLE 30-1: "Supply Voltage"** for more information on threshold levels.

| Note: | Changing the input threshold selection       |

|-------|----------------------------------------------|

|       | should be performed while all peripheral     |

|       | modules are disabled. Changing the thresh-   |

|       | old level during the time a module is active |

|       | may inadvertently generate a transition      |

|       | associated with an input pin, regardless of  |

|       | the actual voltage level on that pin.        |

#### 13.7.6 PORTC FUNCTIONS AND OUTPUT PRIORITIES

Each PORTC pin is multiplexed with other functions. The pins, their combined functions and their output priorities are shown in Table 13-7.

When multiple outputs are enabled, the actual pin control goes to the peripheral with the highest priority.

Analog input and some digital input functions are not included in the list below. These input functions can remain active when the pin is configured as an output. Certain digital input functions override other port functions and are included in the priority list.

| Pin Name | Function Priority <sup>(1)</sup> |

|----------|----------------------------------|

| RC0      | T1OSO<br>PSMC1A<br>RC0           |

| RC1      | PSMC1B<br>CCP2<br>RC1            |

| RC2      | PSMC1C<br>CCP1<br>RC2            |

| RC3      | PSMC1D<br>SCL<br>SCK<br>RC3      |

| RC4      | PSMC1E<br>SDA<br>RC4             |

| RC5      | PSMC1F<br>SDO<br>RC5             |

| RC6      | PSMC2A<br>TX/CK<br>CCP3<br>RC6   |

| RC7      | PSMC2B<br>DT<br>RC7              |

TABLE 13-7: PORTC OUTPUT PRIORITY

Note 1: Priority listed from highest to lowest.

# 13.10 Register Definitions: PORTD

#### REGISTER 13-26: PORTD: PORTD REGISTER

| R/W-x/u                       | R/W-x/u | R/W-x/u            | R/W-x/u | R/W-x/u                                               | R/W-x/u          | R/W-x/u | R/W-x/u     |

|-------------------------------|---------|--------------------|---------|-------------------------------------------------------|------------------|---------|-------------|

| RD7                           | RD6     | RD5                | RD4     | RD3                                                   | RD2              | RD1     | RD0         |

| bit 7                         |         |                    |         |                                                       |                  | bit 0   |             |

|                               |         |                    |         |                                                       |                  |         |             |

| Legend:                       |         |                    |         |                                                       |                  |         |             |

| R = Readable bit W = Writable |         | W = Writable       | bit     | U = Unimpler                                          | mented bit, read | as '0'  |             |

| u = Bit is unchanged          |         | x = Bit is unknown |         | -n/n = Value at POR and BOR/Value at all other Resets |                  |         | ther Resets |

| '1' = Bit is set              |         | '0' = Bit is clea  | ared    |                                                       |                  |         |             |

|                               |         |                    |         |                                                       |                  |         |             |

bit 7-0 **RD<7:0>**: PORTD General Purpose I/O Pin bits<sup>(1)</sup> 1 = Port pin is ≥ VIH 0 = Port pin is ≤ VIL

**Note 1:** Writes to PORTD are actually written to corresponding LATD register. Reads from PORTD register is return of actual I/O pin values.

#### REGISTER 13-27: TRISD: PORTD TRI-STATE REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| TRISD7  | TRISD6  | TRISD5  | TRISD4  | TRISD3  | TRISD2  | TRISD1  | TRISD0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

**TRISD<7:0>:** PORTD Tri-State Control bits 1 = PORTD pin configured as an input (tri-stated)

0 = PORTD pin configured as an output

#### REGISTER 13-28: LATD: PORTD DATA LATCH REGISTER

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

| LATD7   | LATD6   | LATD5   | LATD4   | LATD3   | LATD2   | LATD1   | LATD0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-0 LATD<7:0>: PORTD Output Latch Value bits<sup>(1)</sup>

**Note 1:** Writes to PORTD are actually written to corresponding LATD register. Reads from PORTD register is return of actual I/O pin values.

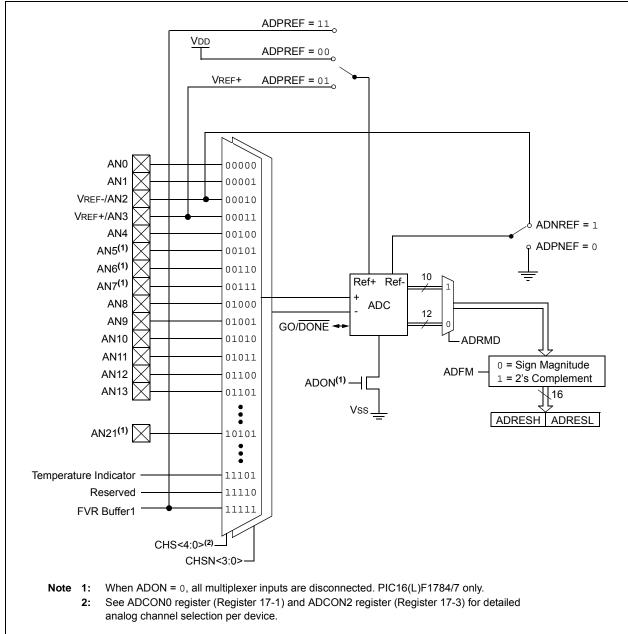

# 17.0 ANALOG-TO-DIGITAL CONVERTER (ADC) MODULE

The Analog-to-Digital Converter (ADC) allows conversion of a single-ended and differential analog input signals to a 12-bit binary representation of that signal. This device uses analog inputs, which are multiplexed into a single sample and hold circuit. The output of the sample and hold is connected to the input of the converter. The converter generates a 12-bit binary result via successive approximation and stores

#### FIGURE 17-1: ADC BLOCK DIAGRAM

the conversion result into the ADC result registers (ADRESH:ADRESL register pair). Figure 17-1 shows the block diagram of the ADC.

The ADC voltage reference is software selectable to be either internally generated or externally supplied.

The ADC can generate an interrupt upon completion of a conversion. This interrupt can be used to wake-up the device from Sleep.

# 23.1 Timer2 Operation

The clock input to the Timer2 modules is the system instruction clock (Fosc/4).

A 4-bit counter/prescaler on the clock input allows direct input, divide-by-4 and divide-by-16 prescale options. These options are selected by the prescaler control bits, T2CKPS<1:0> of the T2CON register. The value of TMR2 is compared to that of the Period register, PR2, on each clock cycle. When the two values match, the comparator generates a match signal as the timer output. This signal also resets the value of TMR2 to 00h on the next cycle and drives the output counter/postscaler (see Section 23.2 "Timer2 Interrupt").

The TMR2 and PR2 registers are both directly readable and writable. The TMR2 register is cleared on any device Reset, whereas the PR2 register initializes to FFh. Both the prescaler and postscaler counters are cleared on the following events:

- a write to the TMR2 register

- a write to the T2CON register

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- MCLR Reset

- Watchdog Timer (WDT) Reset

- · Stack Overflow Reset

- Stack Underflow Reset

- RESET Instruction

Note: TMR2 is not cleared when T2CON is written.

# 23.2 Timer2 Interrupt

Timer2 can also generate an optional device interrupt. The Timer2 output signal (TMR2-to-PR2 match) provides the input for the 4-bit counter/postscaler. This counter generates the TMR2 match interrupt flag which is latched in TMR2IF of the PIR1 register. The interrupt is enabled by setting the TMR2 Match Interrupt Enable bit, TMR2IE, of the PIE1 register.

A range of 16 postscale options (from 1:1 through 1:16 inclusive) can be selected with the postscaler control bits, T2OUTPS<3:0>, of the T2CON register.

## 23.3 Timer2 Output

The unscaled output of TMR2 is available primarily to the CCP modules, where it is used as a time base for operations in PWM mode.

Timer2 can be optionally used as the shift clock source for the MSSP module operating in SPI mode. Additional information is provided in Section 26.0 "Master Synchronous Serial Port (MSSP) Module"

# 23.4 Timer2 Operation During Sleep

The Timer2 timers cannot be operated while the processor is in Sleep mode. The contents of the TMR2 and PR2 registers will remain unchanged while the processor is in Sleep mode.

#### 24.2.6 CLOCK PRESCALER

There are four prescaler choices available to be applied to the selected clock:

- Divide by 1

- Divide by 2

- Divide by 4

- Divide by 8

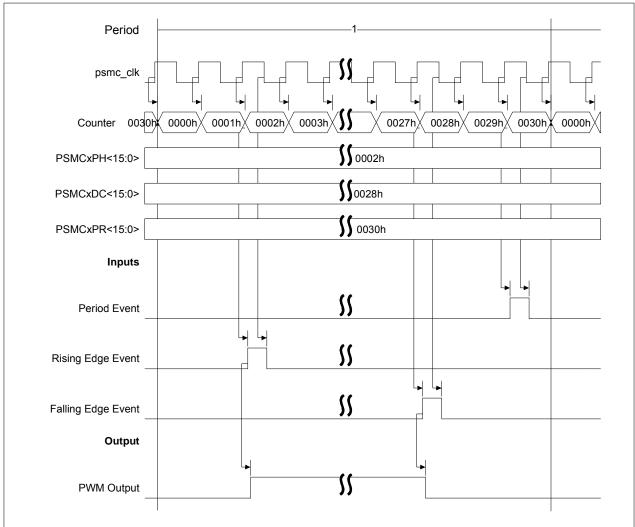

#### FIGURE 24-3: TIME BASE WAVEFORM GENERATION

The clock source is selected with the PxCPRE<1:0> bits of the PSMCx Clock Control (PSMCxCLK) register

The prescaler output is psmc\_clk, which is the clock

used by all of the other portions of the PSMC module.

(Register 24-6).

| FFA number | Output Frequency (kHz) | Step Size (Hz) |  |

|------------|------------------------|----------------|--|

| 0          | 125.000                | 0              |  |

| 1          | 124.970                | -30.4          |  |

| 2          | 124.939                | -60.8          |  |

| 3          | 124.909                | -91.2          |  |

| 4          | 124.878                | -121.6         |  |

| 5          | 124.848                | -152.0         |  |

| 6          | 124.818                | -182.4         |  |

| 7          | 124.787                | -212.8         |  |

| 8          | 124.757                | -243.2         |  |

| 9          | 124.726                | -273.6         |  |

| 10         | 124.696                | -304.0         |  |

| 11         | 124.666                | -334.4         |  |

| 12         | 124.635                | -364.8         |  |

| 13         | 124.605                | -395.2         |  |

| 14         | 124.574                | -425.6         |  |

| 15         | 124.544                | -456.0         |  |

### TABLE 24-4: SAMPLE FFA OUTPUT PERIODS/FREQUENCIES

# 25.0 CAPTURE/COMPARE/PWM MODULES

The Capture/Compare/PWM module is a peripheral that allows the user to time and control different events, and to generate Pulse-Width Modulation (PWM) signals. In Capture mode, the peripheral allows the timing of the duration of an event. The Compare mode allows the user to trigger an external event when a predetermined amount of time has expired. The PWM mode can generate Pulse-Width Modulated signals of varying frequency and duty cycle.

This family of devices contains two standard Capture/Compare/PWM modules (CCP1, CCP2 and CCP3).

The Capture and Compare functions are identical for all CCP modules.

- Note 1: In devices with more than one CCP module, it is very important to pay close attention to the register names used. A number placed after the module acronym is used to distinguish between separate modules. For example, the CCP1CON and CCP2CON control the same operational aspects of two completely different CCP modules.

- 2: Throughout this section, generic references to a CCP module in any of its operating modes may be interpreted as being equally applicable to CCPx module. Register names, module signals, I/O pins, and bit names may use the generic designator 'x' to indicate the use of a numeral to distinguish a particular module, when required.

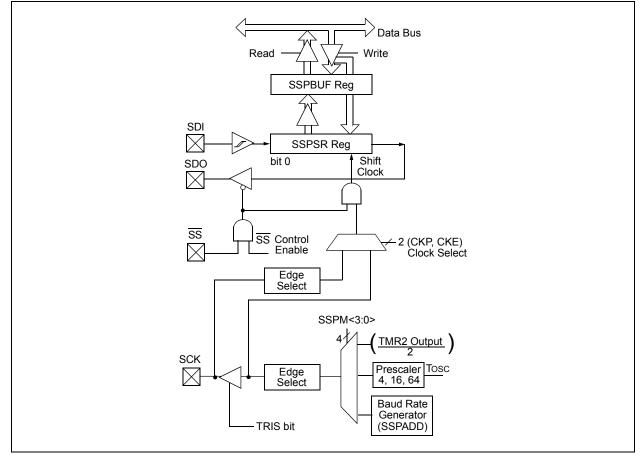

# 26.0 MASTER SYNCHRONOUS SERIAL PORT (MSSP) MODULE

### 26.1 Master SSP (MSSP) Module Overview

The Master Synchronous Serial Port (MSSP) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D converters, etc. The MSSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C<sup>™</sup>)

The SPI interface supports the following modes and features:

- Master mode

- · Slave mode

- · Clock Parity

- Slave Select Synchronization (Slave mode only)

- · Daisy-chain connection of slave devices

Figure 26-1 is a block diagram of the SPI interface module.

#### FIGURE 26-1: MSSP BLOCK DIAGRAM (SPI MODE)

# PIC16(L)F1784/6/7

| TRIS             | Load TRIS Register with W                                                                                                                            |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] TRIS f                                                                                                                                       |

| Operands:        | $5 \leq f \leq 7$                                                                                                                                    |

| Operation:       | (W) $\rightarrow$ TRIS register 'f'                                                                                                                  |

| Status Affected: | None                                                                                                                                                 |

| Description:     | Move data from W register to<br>TRIS register.<br>When 'f' = 5, TRISA is loaded.<br>When 'f' = 6, TRISB is loaded.<br>When 'f' = 7, TRISC is loaded. |

| XORLW            | Exclusive OR literal with W                                                                                            |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] XORLW k                                                                                               |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                    |  |  |  |

| Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                          |  |  |  |

| Status Affected: | Z                                                                                                                      |  |  |  |

| Description:     | The contents of the W register<br>are XOR'ed with the 8-bit<br>literal 'k'. The result is placed in<br>the W register. |  |  |  |

| XORWF            | Exclusive OR W with f                                                                                                                                                           |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [label] XORWF f,d                                                                                                                                                               |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                               |  |  |

| Operation:       | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                       |  |  |

| Status Affected: | Z                                                                                                                                                                               |  |  |

| Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' is '0', the result is stored in the W register. If 'd' is '1', the result is stored back in register 'f'. |  |  |

# 30.5 AC Characteristics

Timing Parameter Symbology has been created with one of the following formats:

1. TppS2ppS

2. TppS

| 2. TPp0 |                                       |     |                |

|---------|---------------------------------------|-----|----------------|

| т       |                                       |     |                |

| F       | Frequency                             | Т   | Time           |

| Lowerc  | case letters (pp) and their meanings: |     |                |

| рр      |                                       |     |                |

| сс      | CCP1                                  | OSC | OSC1           |

| ck      | CLKOUT                                | rd  | RD             |

| CS      | CS                                    | rw  | RD or WR       |

| di      | SDI                                   | SC  | SCK            |

| do      | SDO                                   | SS  | SS             |

| dt      | Data in                               | tO  | TOCKI          |

| io      | I/O PORT                              | t1  | T1CKI          |

| mc      | MCLR                                  | wr  | WR             |

| Upperc  | case letters and their meanings:      |     |                |

| S       |                                       |     |                |

| F       | Fall                                  | Р   | Period         |

| н       | High                                  | R   | Rise           |

| I       | Invalid (High-impedance)              | V   | Valid          |

| L       | Low                                   | Z   | High-impedance |

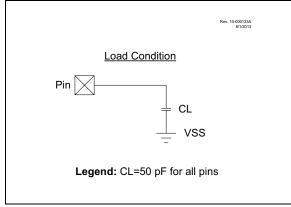

# FIGURE 30-4: LOAD CONDITIONS

# PIC16(L)F1784/6/7

Note: Unless otherwise noted, VIN = 5V, Fosc = 300 kHz, CIN = 0.1  $\mu$ F, TA = 25°C.

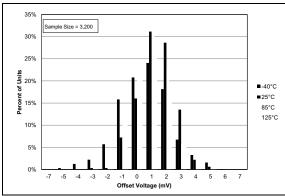

**FIGURE 31-109:** Op Amp, Output Voltage Histogram, VDD = 3.0V, VCM = VDD/2.

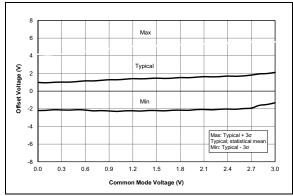

**FIGURE 31-110:** Op Amp, Offset Over Common Mode Voltage, VDD = 3.0V, Temp. = 25°C.

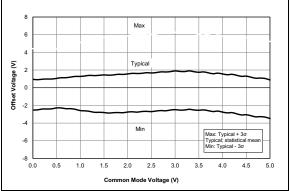

**FIGURE 31-111:** Op Amp, Offset Over Common Mode Voltage, VDD = 5.0V, Temp. = 25°C, PIC16F1784/6/7 Only.

FIGURE 31-113: Op Amp, Output Slew Rate, Falling Edge, PIC16LF1784/6/7 Only.

FIGURE 31-112: Op Amp, Output Slew Rate, Rising Edge, PIC16LF1784/6/7 Only.

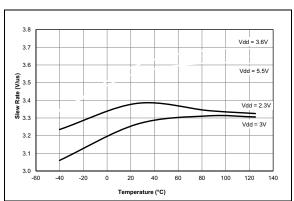

FIGURE 31-114: Op Amp, Output Slew Rate, Rising Edge, PIC16F1784/6/7 Only.