Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PSMC, PWM, WDT                                |

| Number of I/O              | 35                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 14x12b; D/A 1x8b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 44-QFN (8x8)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1784t-i-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                  | BANK 8                                |              | BANK 9                                |              | BANK 10                               |              | BANK 11                               |                   | BANK 12                                    |              | BANK 13                               |              | BANK 14                               |               | BANK 15                               |

|------------------|---------------------------------------|--------------|---------------------------------------|--------------|---------------------------------------|--------------|---------------------------------------|-------------------|--------------------------------------------|--------------|---------------------------------------|--------------|---------------------------------------|---------------|---------------------------------------|

| 00h<br>0Bh       | Core Registers<br>(Table 3-2)         | 480h<br>48Bh | Core Registers<br>(Table 3-2)         | 500h<br>50Bh | Core Registers<br>(Table 3-2)         | 580h<br>58Bh | Core Registers<br>(Table 3-2)         | 600h<br>60Bh      | Core Registers<br>(Table 3-2)              | 680h<br>68Bh | Core Registers<br>(Table 3-2)         | 700h<br>70Bh | Core Registers<br>(Table 3-2)         | 780h<br>78Bh  | Core Registers<br>(Table 3-2)         |

| 0Ch              | Unimplemented<br>Read as '0'          | 48Ch         | Unimplemented<br>Read as '0'          | 50Ch         |                                       | 58Ch         | Unimplemented<br>Read as '0'          | 60Ch              | Unimplemented<br>Read as '0'               | 68Ch         |                                       | 70Ch         |                                       | 78Ch          |                                       |

| 41F<br>420       | General                               | 49F<br>4A0   | General                               |              | See Table 3-8                         | 59F<br>5A0   | General                               | 61F<br>620<br>64F | General<br>Purpose<br>Register<br>48 Bytes |              | Unimplemented<br>Read as '0'          |              | Unimplemented<br>Read as '0'          |               | Unimplemented<br>Read as '0'          |

|                  | Purpose<br>Register<br>80 Bytes       |              | Purpose<br>Register<br>80 Bytes       |              |                                       |              | Purpose<br>Register<br>80 Bytes       | 650               | Unimplemented<br>Read as '0'               |              |                                       |              |                                       |               |                                       |

| 46Fh             |                                       | 4EFh         |                                       | 56Fh         |                                       | 5EFh         |                                       | 66Fh              |                                            | 6EFh         |                                       | 76Fh         |                                       | 7EFh          |                                       |

| 470h<br>47Fh     | Common RAM<br>(Accesses<br>70h – 7Fh) | 4F0h<br>4FFh | Common RAM<br>(Accesses<br>70h – 7Fh) | 570h<br>57Fh | Common RAM<br>(Accesses<br>70h – 7Fh) | 5F0h<br>5FFh | Common RAM<br>(Accesses<br>70h – 7Fh) | 670h<br>67Fh      | Common RAM<br>(Accesses<br>70h – 7Fh)      | 6F0h<br>6FFh | Common RAM<br>(Accesses<br>70h – 7Fh) | 770h<br>77Fh | Common RAM<br>(Accesses<br>70h – 7Fh) | 7F0h<br>7FFh  | Common RAM<br>(Accesses<br>70h – 7Fh) |

| •/• • • <u> </u> | BANK 16                               |              | BANK 17                               |              | BANK 18                               | - OF TH      | BANK 19                               | 0/111             | BANK 20                                    | John         | BANK 21                               | , ,,,,,,     | BANK 22                               | , , , , , , , | BANK 23                               |

| 800h<br>30Bh     | Core Registers<br>(Table 3-2)         | 880h<br>88Bh | Core Registers<br>(Table 3-2)         | 900h<br>90Bh | Core Registers<br>(Table 3-2)         | 980h<br>98Bh | Core Registers<br>(Table 3-2)         | A00h<br>A0Bh      | Core Registers<br>(Table 3-2)              | A80h<br>A8Bh | Core Registers<br>(Table 3-2)         | B00h<br>B0Bh | Core Registers<br>(Table 3-2)         | B80h<br>B8Bh  | Core Registers<br>(Table 3-2)         |

| 30Ch             | See Table 3-10                        | 88Ch         | Unimplemented<br>Read as '0'          | 90Ch         | Unimplemented<br>Read as '0'          | 98Ch         | Unimplemented<br>Read as '0'          | A0Ch              | Unimplemented<br>Read as '0'               | A8Ch         | Unimplemented<br>Read as '0'          | B0Ch         | Unimplemented<br>Read as '0'          | B8Ch          | Unimplemente<br>Read as '0'           |

| 86Fh             |                                       | 8EFh         |                                       | 96Fh         |                                       | 9EFh         |                                       | A6Fh              |                                            | AEFh         |                                       | B6Fh         |                                       | BEFh          |                                       |

| 370h             | Common RAM<br>(Accesses<br>70h – 7Fh) | 8F0h         | Common RAM<br>(Accesses<br>70h – 7Fh) | 970h         | Common RAM<br>(Accesses<br>70h – 7Fh) | 9F0h         | Common RAM<br>(Accesses<br>70h – 7Fh) | A70h              | Common RAM<br>(Accesses<br>70h – 7Fh)      | AF0h         | Common RAM<br>(Accesses<br>70h – 7Fh) | B70h         | Common RAM<br>(Accesses<br>70h – 7Fh) | BF0h          | Common RAM<br>(Accesses<br>70h – 7Fh) |

| 87Fh             |                                       | 8FFh         |                                       | 97Fh         |                                       | 9FFh         |                                       | A7Fh              |                                            | AFFh         |                                       | B7Fh         |                                       | BFFh          |                                       |

| 2005             | BANK 24                               |              | BANK 25                               | 1            | BANK 26                               | n            | BANK 27                               | 1                 | BANK 28                                    | ı            | BANK 29                               | n            | BANK 30                               | ו ו           | BANK 31                               |

| C00h<br>C0Bh     | Core Registers<br>(Table 3-2)         | C80h<br>C8Bh | Core Registers<br>(Table 3-2)         | D00h<br>D0Bh | Core Registers<br>(Table 3-2)         | D80h<br>D8Bh | Core Registers<br>(Table 3-2)         | E00h<br>E0Bh      | Core Registers<br>(Table 3-2)              | E80h<br>E8Bh | Core Registers<br>(Table 3-2)         | F00h<br>F0Bh | Core Registers<br>(Table 3-2)         | F80h<br>F8Bh  | Core Registers<br>(Table 3-2)         |

| C0Ch             | Unimplemented<br>Read as '0'          | C8Ch         | Unimplemented<br>Read as '0'          | D0Ch         | Unimplemented<br>Read as '0'          | D8Ch         | Unimplemented<br>Read as '0'          | E0Ch              | Unimplemented<br>Read as '0'               | E8Ch         | Unimplemented<br>Read as '0'          | F0Ch         | Unimplemented<br>Read as '0'          | F8Ch          | See Table 3-9                         |

| C6Fh<br>C70h     | Common RAM                            | CEFh<br>CF0h | Common RAM                            | D6Fh<br>D70h | Common RAM                            | DEFh<br>DF0h | Common RAM                            | E6Fh<br>E70h      | Common RAM                                 | EEFh<br>EF0h | Common RAM                            | F6Fh<br>F70h | Common RAM                            | FEFh<br>FF0h  | Common RAM                            |

|                  | (Accesses                             |              | (Accesses<br>70h – 7Fh)               |              | (Accesses<br>70h – 7Fh)               |              | (Accesses<br>70h – 7Fh)               |                   | (Accesses<br>70h – 7Fh)                    |              | (Accesses<br>70h – 7Fh)               |              | (Accesses<br>70h – 7Fh)               |               | (Accesses<br>70h – 7Fh)               |

# TABLE 3-7: PIC16(L)F1786/7 MEMORY MAP (BANKS 8-31)

= Unimplemented data memory locations, read as '0'

## REGISTER 4-1: CONFIG1: CONFIGURATION WORD 1 (CONTINUED)

- bit 2-0 FOSC<2:0>: Oscillator Selection bits

- 111 = ECH: External Clock, High-Power mode (4-20 MHz): device clock supplied to CLKIN pin

- 110 = ECM: External Clock, Medium-Power mode (0.5-4 MHz): device clock supplied to CLKIN pin

- 101 = ECL: External Clock, Low-Power mode (0-0.5 MHz): device clock supplied to CLKIN pin

- 100 = INTOSC oscillator: I/O function on CLKIN pin

- 011 = EXTRC oscillator: External RC circuit connected to CLKIN pin

- 010 = HS oscillator: High-speed crystal/resonator connected between OSC1 and OSC2 pins

- 001 = XT oscillator: Crystal/resonator connected between OSC1 and OSC2 pins

- 000 = LP oscillator: Low-power crystal connected between OSC1 and OSC2 pins

- **Note 1:** The entire data EEPROM will be erased when the code protection is turned off during an erase.Once the Data Code Protection bit is enabled, (CPD = 0), the Bulk Erase Program Memory Command (through ICSP) can disable the Data Code Protection (CPD =1). When a Bulk Erase Program Memory Command is executed, the entire Program Flash Memory, Data EEPROM and configuration memory will be erased.

# 8.1 Operation

Interrupts are disabled upon any device Reset. They are enabled by setting the following bits:

- · GIE bit of the INTCON register

- Interrupt Enable bit(s) for the specific interrupt event(s)

- PEIE bit of the INTCON register (if the Interrupt Enable bit of the interrupt event is contained in the PIE1 or PIE2 registers)

The INTCON, PIR1 and PIR2 registers record individual interrupts via interrupt flag bits. Interrupt flag bits will be set, regardless of the status of the GIE, PEIE and individual interrupt enable bits.

The following events happen when an interrupt event occurs while the GIE bit is set:

- Current prefetched instruction is flushed

- · GIE bit is cleared

- Current Program Counter (PC) is pushed onto the stack

- Critical registers are automatically saved to the shadow registers (See "Section 8.5 "Automatic Context Saving".")

- PC is loaded with the interrupt vector 0004h

The firmware within the Interrupt Service Routine (ISR) should determine the source of the interrupt by polling the interrupt flag bits. The interrupt flag bits must be cleared before exiting the ISR to avoid repeated interrupts. Because the GIE bit is cleared, any interrupt that occurs while executing the ISR will be recorded through its interrupt flag, but will not cause the processor to redirect to the interrupt vector.

The RETFIE instruction exits the ISR by popping the previous address from the stack, restoring the saved context from the shadow registers and setting the GIE bit.

For additional information on a specific interrupt's operation, refer to its peripheral chapter.

| Note 1: | Individual  | inte | rrupt | flag  | bits | s are | set,  |

|---------|-------------|------|-------|-------|------|-------|-------|

|         | regardless  | of   | the   | state | of   | any   | other |

|         | enable bits |      |       |       |      |       |       |

2: All interrupts will be ignored while the GIE bit is cleared. Any interrupt occurring while the GIE bit is clear will be serviced when the GIE bit is set again.

# 8.2 Interrupt Latency

Interrupt latency is defined as the time from when the interrupt event occurs to the time code execution at the interrupt vector begins. The latency for synchronous interrupts is three or four instruction cycles. For asynchronous interrupts, the latency is three to five instruction cycles, depending on when the interrupt occurs. See Figure 8-2 and Figure 8.3 for more details.

| U-0              | U-0                                | U-0               | R/W-0/0  | U-0          | U-0              | U-0    | U-0   |

|------------------|------------------------------------|-------------------|----------|--------------|------------------|--------|-------|

| _                | —                                  | —                 | CCP3IF   | —            | —                |        | —     |

| bit 7            |                                    |                   |          |              |                  |        | bit 0 |

| <b></b>          |                                    |                   |          |              |                  |        |       |

| Legend:          |                                    |                   |          |              |                  |        |       |

| R = Readable     | e bit                              | W = Writable      | bit      | U = Unimpler | mented bit, read | as '0' |       |

| u = Bit is uncl  | hanged                             | x = Bit is unkn   | iown     | ther Resets  |                  |        |       |

| '1' = Bit is set |                                    | '0' = Bit is clea | ared     |              |                  |        |       |

| bit 7-5          | Unimplemen                         | ted: Read as 'o   | ר,       |              |                  |        |       |

| bit 4            | -                                  | P3 Interrupt Flag |          |              |                  |        |       |

|                  |                                    | •                 | y bit    |              |                  |        |       |

|                  | 1 = Interrupt i<br>0 = Interrupt i |                   |          |              |                  |        |       |

| h:+ 0 0          | -                                  |                   | <u>.</u> |              |                  |        |       |

| bit 3-0          | Unimplemen                         | ted: Read as 'o   | J.       |              |                  |        |       |

# REGISTER 8-8: PIR3: PERIPHERAL INTERRUPT REQUEST REGISTER 3

# 9.1.1 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs **before** the execution of a SLEEP instruction

- SLEEP instruction will execute as a NOP.

- WDT and WDT prescaler will not be cleared

- TO bit of the STATUS register will not be set

- PD bit of the STATUS register will not be cleared.

- If the interrupt occurs **during or after** the execution of a **SLEEP** instruction

- SLEEP instruction will be completely executed

- Device will immediately wake-up from Sleep

- WDT and WDT prescaler will be cleared

- TO bit of the STATUS register will be set

- PD bit of the STATUS register will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the PD bit. If the PD bit is set, the SLEEP instruction was executed as a NOP.

| FIGURE 9-1                                    | I. WAN                                                                                      |                                         |                             | INKO                |                      | INUF I             |                      |                                       |

|-----------------------------------------------|---------------------------------------------------------------------------------------------|-----------------------------------------|-----------------------------|---------------------|----------------------|--------------------|----------------------|---------------------------------------|

| CLKIN <sup>(1)</sup><br>CLKOUT <sup>(2)</sup> | ;                                                                                           | Q1   Q2   Q3   Q4<br>                   |                             | T1osc <sup>(3</sup> |                      | 01 02 03 0<br>     | 4 Q1 Q2 Q3 Q4<br>    | Q1 Q2 Q3 Q4<br>                       |

| Interrupt flag                                |                                                                                             |                                         | /                           |                     | Interrupt Laten      | ncy <sup>(4)</sup> | ·<br>·<br>·          | 1 1<br><del>1</del><br>1 1<br>1 1     |

| GIE bit<br>(INTCON reg.)                      | ; <u> </u>                                                                                  |                                         | Processor in<br>Sleep       | i                   |                      | <u>.</u><br>       | <u> </u>             | · · · · · · · · · · · · · · · · · · · |

| Instruction Flow<br>PC                        | Х <u>РС</u> У                                                                               | PC + 1                                  | X PC                        | + 2                 | X PC + 2             | X PC + 2           | X 0004h              | X 0005h                               |

| Instruction {                                 | Inst(PC) = Sleep                                                                            | Inst(PC + 1)                            | 1<br>1<br>1                 |                     | Inst(PC + 2)         | 1<br>1<br>1        | Inst(0004h)          | Inst(0005h)                           |

| Instruction {<br>Executed {                   | Inst(PC - 1)                                                                                | Sleep                                   | 1<br>1<br>1                 | 1                   | Inst(PC + 1)         | Forced NOP         | Forced NOP           | Inst(0004h)                           |

| 2: 0<br>3:                                    | External clock. High<br>CLKOUT is shown l<br>T1osc; See <b>Sectio</b><br>GIE = 1 assumed. I | here for timing re<br>n 30.0 "Electrica | ference.<br>al Specificatio | ons".               | r calls the ISR at ( | 0004h. lf GIE = 0  | , execution will con | tinue in-line.                        |

#### FIGURE 9-1: WAKE-UP FROM SLEEP THROUGH INTERRUPT

# 13.2 Register Definitions: Alternate Pin Function Control

## REGISTER 13-1: APFCON1: ALTERNATE PIN FUNCTION CONTROL 1 REGISTER

| R/W-0/0          | R/W-0/0                | R/W-0/0                            | R/W-0/0         | R/W-0/0         | R/W-0/0          | R/W-0/0          | R/W-0/0      |  |

|------------------|------------------------|------------------------------------|-----------------|-----------------|------------------|------------------|--------------|--|

| C2OUTSEL         | CCP1SEL                | SDOSEL                             | SCKSEL          | SDISEL          | TXSEL            | RXSEL            | CCP2SEL      |  |

| bit 7            |                        |                                    | •               | ·               |                  |                  | bit 0        |  |

|                  |                        |                                    |                 |                 |                  |                  |              |  |

| Legend:          |                        |                                    | L:4             |                 | nonted bit rece  |                  |              |  |

| R = Readable     |                        | W = Writable                       |                 | •               | nented bit, read |                  |              |  |

| u = bit is uncha | -                      |                                    |                 | -n/n = value a  | at POR and BO    | R/value at all o | other Resets |  |

| '1' = Bit is set |                        | '0' = Bit is clea                  | ared            |                 |                  |                  |              |  |

| bit 7            | C2OUTSEL ·             | C2OUT Pin Se                       | lection bit     |                 |                  |                  |              |  |

|                  | 1 = C2OUT i            |                                    |                 |                 |                  |                  |              |  |

|                  | 0 = C2OUT i            |                                    |                 |                 |                  |                  |              |  |

| bit 6            | CCP1SEL: C             | CP1 Input/Outp                     | out Pin Selecti | on bit          |                  |                  |              |  |

|                  | 1 = CCP1 is            |                                    |                 |                 |                  |                  |              |  |

|                  | 0 = CCP1 is on pin RC2 |                                    |                 |                 |                  |                  |              |  |

| bit 5            |                        | SSP SDO Pin S                      | election bit    |                 |                  |                  |              |  |

|                  | 1 = SDO is c           | •                                  |                 |                 |                  |                  |              |  |

|                  | 0 = SDO is c           | •                                  |                 |                 |                  |                  |              |  |

| bit 4            |                        | SSP Serial Cloc                    | ,               | Pin Selection t | Dit              |                  |              |  |

|                  |                        | K is on pin RB7<br>K is on pin RC3 |                 |                 |                  |                  |              |  |

| bit 3            |                        | SP Serial Data                     |                 | Itout Din Soloo | tion hit         |                  |              |  |

| bit 5            |                        | l is on pin RB6                    | (30A/301) 00    |                 |                  |                  |              |  |

|                  |                        | l is on pin RC4                    |                 |                 |                  |                  |              |  |

| bit 2            |                        | in Selection bit                   |                 |                 |                  |                  |              |  |

|                  | 1 = TX is on           |                                    |                 |                 |                  |                  |              |  |

|                  | 0 = TX is on           | •                                  |                 |                 |                  |                  |              |  |

| bit 1            | RXSEL: RX F            | Pin Selection bi                   | t               |                 |                  |                  |              |  |

|                  | 1 = RX is on           | pin RB7                            |                 |                 |                  |                  |              |  |

|                  | 0 = RX is on           | pin RC7                            |                 |                 |                  |                  |              |  |

| bit 0            | CCP2SEL: C             | CP2 Input/Outp                     | out Pin Selecti | on bit          |                  |                  |              |  |

|                  | 1 = CCP2 is            |                                    |                 |                 |                  |                  |              |  |

|                  | 0 = CCP2 is            | on pin RC1                         |                 |                 |                  |                  |              |  |

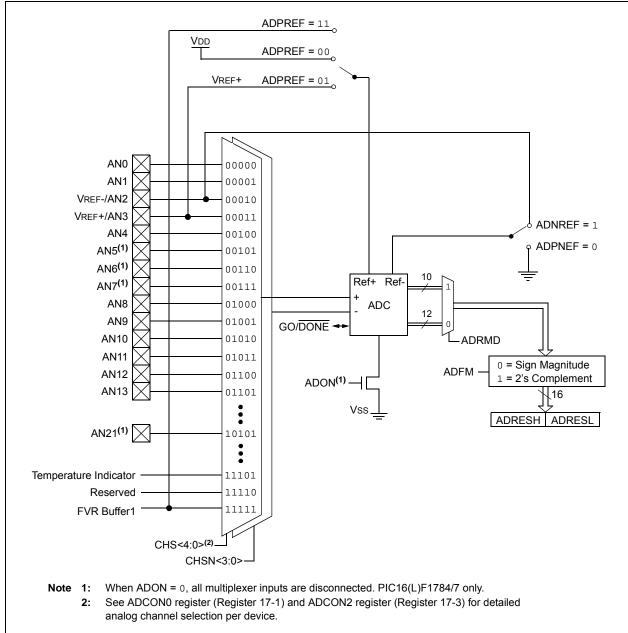

# 17.0 ANALOG-TO-DIGITAL CONVERTER (ADC) MODULE

The Analog-to-Digital Converter (ADC) allows conversion of a single-ended and differential analog input signals to a 12-bit binary representation of that signal. This device uses analog inputs, which are multiplexed into a single sample and hold circuit. The output of the sample and hold is connected to the input of the converter. The converter generates a 12-bit binary result via successive approximation and stores

# FIGURE 17-1: ADC BLOCK DIAGRAM

the conversion result into the ADC result registers (ADRESH:ADRESL register pair). Figure 17-1 shows the block diagram of the ADC.

The ADC voltage reference is software selectable to be either internally generated or externally supplied.

The ADC can generate an interrupt upon completion of a conversion. This interrupt can be used to wake-up the device from Sleep.

| Name    | Bit 7                                        | Bit 6                | Bit 5    | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|---------|----------------------------------------------|----------------------|----------|-------|--------|--------|--------|--------|---------------------|

| CCP2CON | —                                            | DC2B<1:0> CCP2M<3:0> |          |       |        |        |        | 280    |                     |

| INTCON  | GIE                                          | PEIE                 | TMR0IE   | INTE  | IOCIE  | TMR0IF | INTF   | IOCIF  | 93                  |

| PIE1    | TMR1GIE                                      | ADIE                 | RCIE     | TXIE  | SSP1IE | CCP1IE | TMR2IE | TMR1IE | 94                  |

| PIR1    | TMR1GIF                                      | ADIF                 | RCIF     | TXIF  | SSP1IF | CCP1IF | TMR2IF | TMR1IF | 98                  |

| PR2     | Timer2 Mod                                   | dule Period          | Register |       |        |        |        |        | 210*                |

| T2CON   | —                                            |                      |          |       |        |        |        | 212    |                     |

| TMR2    | Holding Register for the 8-bit TMR2 Register |                      |          |       |        |        |        | 210*   |                     |

TABLE 23-1: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER2

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for Timer2 module.

\* Page provides register information.

# 24.0 PROGRAMMABLE SWITCH MODE CONTROL (PSMC)

The Programmable Switch Mode Controller (PSMC) is a high-performance Pulse Width Modulator (PWM) that can be configured to operate in one of several modes to support single or multiple phase applications.

A simplified block diagram indicating the relationship between inputs, outputs, and controls is shown in Figure 24-1.

This section begins with the fundamental aspects of the PSMC operation. A more detailed description of operation for each mode is located later in **Section 24.3** "**Modes of Operation**"

Modes of operation include:

- Single-phase

- · Complementary Single-phase

- Push-Pull

- Push-Pull 4-Bridge

- · Complementary Push-Pull 4-Bridge

- · Pulse Skipping

- Variable Frequency Fixed Duty Cycle

- Complementary Variable Frequency Fixed Duty

Cycle

- · ECCP Compatible modes

- Full-Bridge

- Full-Bridge Reverse

- · 3-Phase 6-Step PWM

#### 24.3.9 ECCP COMPATIBLE FULL-BRIDGE PWM

This mode of operation is designed to match the Full-Bridge mode from the ECCP module. It is called ECCP compatible as the term "full-bridge" alone has different connotations in regards to the output waveforms.

Full-Bridge Compatible mode uses the same waveform events as the single PWM mode to generate the output waveforms.

There are both Forward and Reverse modes available for this operation, again to match the ECCP implementation. Direction is selected with the mode control bits.

### 24.3.9.1 Mode Features

- · Dead-band control available on direction switch

- Changing from forward to reverse uses the falling edge dead-band counters.

- Changing from reverse to forward uses the rising edge dead-band counters.

- No steering control available

- PWM is output on the following four pins only:

- PSMCxA

- PSMCxB

- PSMCxC

- PSMCxD

# 24.3.9.2 Waveform Generation - Forward

In this mode of operation, three of the four pins are static. PSMCxA is the only output that changes based on rising edge and falling edge events.

#### Static Signal Assignment

- · Outputs set to active state

- PSMCxD

- · Outputs set to inactive state

- PSMCxB

- PSMCxC

Rising Edge Event

· PSMCxA is set active

Falling Edge Event

· PSMCxA is set inactive

#### 24.3.9.3 Waveform Generation – Reverse

In this mode of operation, three of the four pins are static. Only PSMCxB toggles based on rising edge and falling edge events.

#### Static Signal Assignment

- Outputs set to active state

- PSMCxC

- · Outputs set to inactive state

- PSMCxA

- PSMCxD

#### Rising Edge Event

· PSMCxB is set active

#### Falling Edge Event

· PSMCxB is set inactive

#### FIGURE 24-12: ECCP COMPATIBLE FULL-BRIDGE PWM WAVEFORM – PSMCXSTR0 = 0FH

| PWM Period Number  | 1        | 2       | 3      | 4         | 5 | 6         | 7        | 8        | 9        | 10           | —11—         | -12 |

|--------------------|----------|---------|--------|-----------|---|-----------|----------|----------|----------|--------------|--------------|-----|

|                    | <b>∢</b> | Forward | mode o | peration- |   | <b> ⊲</b> | Reverse  | e mode c | peration |              |              | ٦   |

| Period Event       |          |         |        |           |   |           |          |          |          |              |              | L   |

| Falling Edge Event |          |         |        |           |   |           |          |          |          |              |              | _   |

| PSMCxA             |          |         |        |           |   |           |          |          |          |              |              | _   |

| PSMCxB             |          |         |        |           |   |           |          |          |          |              |              | _   |

| PSMCxC             |          |         |        |           |   |           |          |          |          |              |              | _   |

|                    |          |         |        |           | - | Fallir    | g Edge I | Dead Ba  |          | Edge De<br>→ | ad Band<br>∖ |     |

| PSMCxD             |          |         |        |           |   |           |          |          |          |              |              |     |

# 25.0 CAPTURE/COMPARE/PWM MODULES

The Capture/Compare/PWM module is a peripheral that allows the user to time and control different events, and to generate Pulse-Width Modulation (PWM) signals. In Capture mode, the peripheral allows the timing of the duration of an event. The Compare mode allows the user to trigger an external event when a predetermined amount of time has expired. The PWM mode can generate Pulse-Width Modulated signals of varying frequency and duty cycle.

This family of devices contains two standard Capture/Compare/PWM modules (CCP1, CCP2 and CCP3).

The Capture and Compare functions are identical for all CCP modules.

- Note 1: In devices with more than one CCP module, it is very important to pay close attention to the register names used. A number placed after the module acronym is used to distinguish between separate modules. For example, the CCP1CON and CCP2CON control the same operational aspects of two completely different CCP modules.

- 2: Throughout this section, generic references to a CCP module in any of its operating modes may be interpreted as being equally applicable to CCPx module. Register names, module signals, I/O pins, and bit names may use the generic designator 'x' to indicate the use of a numeral to distinguish a particular module, when required.

# 26.2 SPI Mode Overview

The Serial Peripheral Interface (SPI) bus is a synchronous serial data communication bus that operates in Full-Duplex mode. Devices communicate in a master/slave environment where the master device initiates the communication. A slave device is controlled through a Chip Select known as Slave Select.

The SPI bus specifies four signal connections:

- Serial Clock (SCK)

- Serial Data Out (SDO)

- Serial Data In (SDI)

- Slave Select (SS)

Figure 26-1 shows the block diagram of the MSSP module when operating in SPI mode.

The SPI bus operates with a single master device and one or more slave devices. When multiple slave devices are used, an independent Slave Select connection is required from the master device to each slave device.

Figure 26-4 shows a typical connection between a master device and multiple slave devices.

The master selects only one slave at a time. Most slave devices have tri-state outputs so their output signal appears disconnected from the bus when they are not selected.

Transmissions involve two shift registers, 8 bits in size, one in the master and one in the slave. With either the master or the slave device, data is always shifted out one bit at a time, with the Most Significant bit (MSb) shifted out first. At the same time, a new Least Significant bit (LSb) is shifted into the same register.

Figure 26-5 shows a typical connection between two processors configured as master and slave devices.

Data is shifted out of both shift registers on the programmed clock edge and latched on the opposite edge of the clock.

The master device transmits information out on its SDO output pin which is connected to, and received by, the slave's SDI input pin. The slave device transmits information out on its SDO output pin, which is connected to, and received by, the master's SDI input pin.

To begin communication, the master device first sends out the clock signal. Both the master and the slave devices should be configured for the same clock polarity.

The master device starts a transmission by sending out the MSb from its shift register. The slave device reads this bit from that same line and saves it into the LSb position of its shift register. During each SPI clock cycle, a full-duplex data transmission occurs. This means that while the master device is sending out the MSb from its shift register (on its SDO pin) and the slave device is reading this bit and saving it as the LSb of its shift register, that the slave device is also sending out the MSb from its shift register (on its SDO pin) and the master device is reading this bit and saving it as the LSb of its shift register.

After 8 bits have been shifted out, the master and slave have exchanged register values.

If there is more data to exchange, the shift registers are loaded with new data and the process repeats itself.

Whether the data is meaningful or not (dummy data), depends on the application software. This leads to three scenarios for data transmission:

- Master sends useful data and slave sends dummy data.

- Master sends useful data and slave sends useful data.

- Master sends dummy data and slave sends useful data.

Transmissions may involve any number of clock cycles. When there is no more data to be transmitted, the master stops sending the clock signal and it deselects the slave.

Every slave device connected to the bus that has not been selected through its slave select line must disregard the clock and transmission signals and must not transmit out any data of its own.

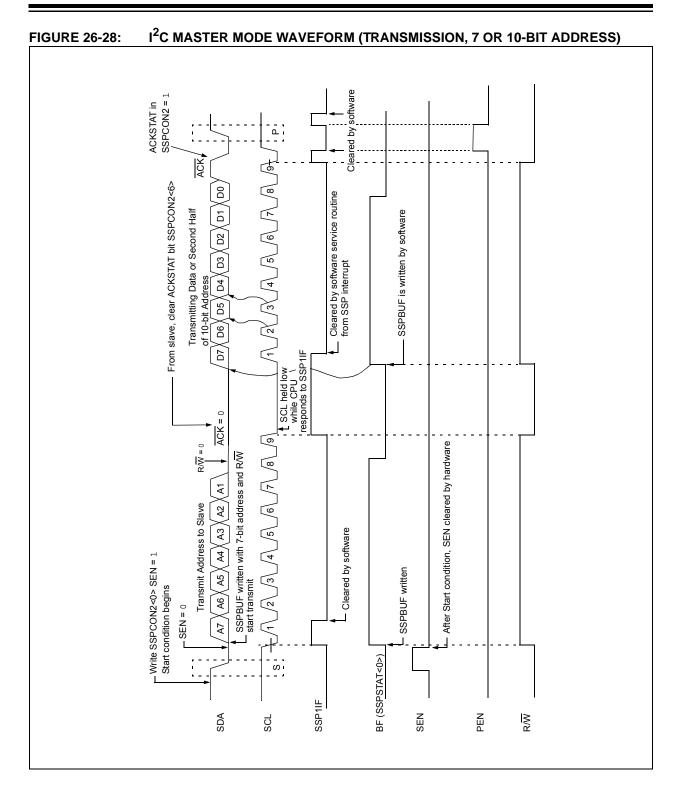

#### 26.4.9 ACKNOWLEDGE SEQUENCE

The 9th SCL pulse for any transferred byte in  $I^2C$  is dedicated as an Acknowledge. It allows receiving devices to respond back to the transmitter by pulling the SDA line low. The transmitter must release control of the line during this time to shift in the response. The Acknowledge (ACK) is an active-low signal, pulling the SDA line low indicated to the transmitter that the device has received the transmitted data and is ready to receive more.

The result of an  $\overline{\text{ACK}}$  is placed in the ACKSTAT bit of the SSPCON2 register.

Slave software, when the AHEN and DHEN bits are set, allow the user to set the ACK value sent back to the transmitter. The ACKDT bit of the SSPCON2 register is set/cleared to determine the response.

Slave hardware will generate an ACK response if the AHEN and DHEN bits of the SSPCON3 register are clear.

There are certain conditions where an  $\overline{ACK}$  will not be sent by the slave. If the BF bit of the SSPSTAT register or the SSPOV bit of the SSPCON1 register are set when a byte is received.

When the module is addressed, after the 8th falling edge of SCL on the bus, the ACKTIM bit of the SSP-CON3 register is set. The ACKTIM bit indicates the acknowledge time of the active bus. The ACKTIM Status bit is only active when the AHEN bit or DHEN bit is enabled.

# 26.5 I<sup>2</sup>C SLAVE MODE OPERATION

The MSSP Slave mode operates in one of four modes selected in the SSPM bits of SSPCON1 register. The modes can be divided into 7-bit and 10-bit Addressing mode. 10-bit Addressing modes operate the same as 7-bit with some additional overhead for handling the larger addresses.

Modes with Start and Stop bit interrupts operated the same as the other modes with SSP1IF additionally getting set upon detection of a Start, Restart, or Stop condition.

#### 26.5.1 SLAVE MODE ADDRESSES

The SSPADD register (Register 26-6) contains the Slave mode address. The first byte received after a Start or Restart condition is compared against the value stored in this register. If the byte matches, the value is loaded into the SSPBUF register and an interrupt is generated. If the value does not match, the module goes idle and no indication is given to the software that anything happened.

The SSP Mask register (Register 26-5) affects the address matching process. See **Section 26.5.9** "**SSP Mask Register**" for more information.

26.5.1.1 I<sup>2</sup>C Slave 7-bit Addressing Mode

In 7-bit Addressing mode, the LSb of the received data byte is ignored when determining if there is an address match.

26.5.1.2 I<sup>2</sup>C Slave 10-bit Addressing Mode

In 10-bit Addressing mode, the first received byte is compared to the binary value of '1 1 1 1 0 A9 A8 0'. A9 and A8 are the two MSb of the 10-bit address and stored in bits 2 and 1 of the SSPADD register.

After the acknowledge of the high byte the UA bit is set and SCL is held low until the user updates SSPADD with the low address. The low address byte is clocked in and all 8 bits are compared to the low address value in SSPADD. Even if there is not an address match; SSP1IF and UA are set, and SCL is held low until SSPADD is updated to receive a high byte again. When SSPADD is updated the UA bit is cleared. This ensures the module is ready to receive the high address byte on the next communication.

A high and low address match as a write request is required at the start of all 10-bit addressing communication. A transmission can be initiated by issuing a Restart once the slave is addressed, and clocking in the high address with the R/W bit set. The slave hardware will then acknowledge the read request and prepare to clock out data. This is only valid for a slave after it has received a complete high and low address byte match.

| N4:0 0 100    | ania |                                             | Cuala      |          | 14-Bit | Opcod        | е            | Status       |       |

|---------------|------|---------------------------------------------|------------|----------|--------|--------------|--------------|--------------|-------|

| Mnem<br>Opera | -    | Description                                 | Cycle<br>s | MS<br>b  |        |              | LSb          | Affecte<br>d | Notes |

|               |      | BYTE-ORIENTED FILE REGI                     | STER OF    | PERAT    | TIONS  |              |              |              |       |

| ADDWF         | f,d  | Add W and f                                 | 1          | 00       | 0111   | dfff         | ffff         | C, DC, Z     | 2     |

| ADDWF         | f, d | Add with Carry W and $f$                    | 1          | 11       | 1101   | dfff         | ffff         | C, DC, Z     | 2     |

| С             | f,d  | AND W with f                                | 1          | 00       |        | dfff         |              | Z            | 2     |

| ANDWF         | f,d  | Arithmetic Right Shift                      | 1          | 11       |        | dfff         |              | C, Z         | 2     |

| ASRF          | f,d  | Logical Left Shift                          | 1          | 11       |        | dfff         |              | C, Z         | 2     |

| LSLF          | f, d | Logical Right Shift                         | 1          | 11       |        | dfff         |              | C, Z         | 2     |

| LSRF          | f    | Clear f                                     | 1          | 00<br>00 |        | lfff         | iiii<br>00xx | Ž            | 2     |

| CLRF          |      |                                             |            | 00       |        | 0000<br>dfff |              | Z            |       |

| CLRW          |      |                                             |            | 00       |        | dfff         |              | Z            | 2     |

| COMF          | f, d | Decrement f                                 | 1          | 00       | 1010   | dfff         |              | Z            | 2     |

| DECF          | £, ⊄ | Increment £                                 | 1          | 00       |        | dfff         |              | Z            | 2     |

| INCF          | f, d | Inclusive OR W with f                       | 1          | 00       |        | dfff         |              | Z            | 2     |

| IORWF         | f, d | Move f                                      | 1          | 00       | 0000   | 1fff         |              | Z            | 2     |

| MOVF          | f, u | Move W to f                                 | 1          | 00       | 1101   | dfff         | ffff         | 2            | 2     |

| MOVWF         | f, d | Rotate Left f through Carry                 | 1          | 00       | 1100   | dfff         | ffff         | С            | 2     |

| RLF           | f, d | Rotate Right f through Carry                | 1          | 00       | 0010   | dfff         | ffff         | c            | 2     |

| RRF           | -    | Subtract W from £                           | 1          | 11       |        | dfff         |              | C, DC, Z     | 2     |

|               | f,d  |                                             | -          | 00       |        | dfff         |              |              | 2     |

| SUBWF         | f,d  | Subtract with Borrow W from f               | 1          | 00       | 0110   | dfff         | ffff         | C, DC, Z     | 2     |

| SUB-          | f,d  | Swap nibbles in f                           | 1          |          |        |              |              | 7            |       |

| WFB           | f,d  | Exclusive OR W with $f$                     | 1          |          |        |              |              | Z            | 2     |

| SWAPF         |      |                                             |            |          |        |              |              |              |       |

| XORWF         |      |                                             |            |          |        |              |              |              |       |

|               |      | BYTE ORIENTED SKIP                          | OPERAT     | TIONS    |        |              |              |              |       |

| DECFSZ        | f,d  | Decrement f, Skip if 0                      | 1(2)       | 00       | 1011   | dfff         | ffff         |              | 1, 2  |

| INCFSZ        | f,d  | Increment f, Skip if 0                      | 1(2)       | 00       | 1111   | dfff         | ffff         |              | 1, 2  |

|               |      | BIT-ORIENTED FILE REGIS                     | TER OPE    | ERATI    | ONS    |              |              |              |       |

| BCF           | f, b | Bit Clear £                                 | 1          | 01       | 00bb   | bfff         | ffff         |              | 2     |

| BSF           | f, b | Bit Set f                                   | 1          | 01       | 01bb   | bfff         | ffff         |              | 2     |

|               |      | BIT-ORIENTED SKIP                           | OPERATI    | ONS      |        |              | 1            | 1            |       |

| BTFSC         | f, b | Bit Test £, Skip if Clear                   | 1 (2)      | 01       | 10bb   | bfff         | ffff         |              | 1, 2  |

| BTFSS         | f, b | Bit Test f, Skip if Set                     | 1 (2)      | 01       | 11bb   | bfff         | ffff         |              | 1, 2  |

|               |      | LITERAL OPER/                               | ATIONS     | T        |        |              |              |              |       |

| ADDLW         | k    | Add literal and W                           | 1          | 11       | 1110   | kkkk         | kkkk         | C, DC, Z     |       |

| ANDLW         | k    | AND literal with W                          | 1          | 11       | 1001   | kkkk         | kkkk         | Z            |       |

| IORLW         | k    | Inclusive OR literal with W                 | 1          | 11       | 1000   | kkkk         | kkkk         | Z            |       |

| MOVLB         | k    | Move literal to BSR                         | 1          | 00       | 0000   | 001k         | kkkk         |              |       |

| MOVLP         | k    | Move literal to PCLATH                      | 1          | 11       | 0001   | 1kkk         | kkkk         |              |       |

| MOVLW         | k    | Move literal to W                           | 1          | 11       | 0000   | kkkk         | kkkk         |              |       |

| SUBLW         | k    | Subtract W from literal                     | 1          | 11       | 1100   | kkkk         | kkkk         | C, DC, Z     |       |

| XORLW         | k    | Exclusive OR literal with W                 | 1          | 11       | 1010   | kkkk         | kkkk         | Z            |       |

|               |      | gram Counter (PC) is modified, or a conditi | -          | I        |        |              |              |              |       |

# TABLE 29-3: ENHANCED MID-RANGE INSTRUCTION SET

**Note 1:** If the Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

2: If this instruction addresses an INDF register and the MSb of the corresponding FSR is set, this instruction will require one additional instruction cycle.

# PIC16(L)F1784/6/7

## TABLE 30-4: I/O PORTS (CONTINUED)

Standard Operating Conditions (unless otherwise stated)

| Param<br>No. | Sym.  | Characteristic                                   | Min.               | Тур† | Max. | Units | Conditions                                                             |

|--------------|-------|--------------------------------------------------|--------------------|------|------|-------|------------------------------------------------------------------------|

|              |       | <b>Capacitive Loading Specs on</b>               | <b>Output Pins</b> | ;    |      |       |                                                                        |

| D101*        | COSC2 | OSC2 pin                                         | _                  | —    | 15   | pF    | In XT, HS and LP modes when<br>external clock is used to drive<br>OSC1 |

| D101A*       | Сю    | All I/O pins                                     | —                  | _    | 50   | pF    |                                                                        |

|              |       | VCAP Capacitor Charging                          |                    |      |      |       |                                                                        |

| D102         |       | Charging current                                 | _                  | 200  |      | μΑ    |                                                                        |

| D102A        |       | Source/sink capability when<br>charging complete | _                  | 0.0  | _    | mA    |                                                                        |

These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended to use an external clock in RC mode.

**2:** Negative current is defined as current sourced by the pin.

3: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

**4:** Including OSC2 in CLKOUT mode.

# TABLE 30-8: PLL CLOCK TIMING SPECIFICATIONS

| Standar      | Standard Operating Conditions (unless otherwise stated) |                               |        |      |        |       |            |  |  |

|--------------|---------------------------------------------------------|-------------------------------|--------|------|--------|-------|------------|--|--|

| Param<br>No. | Sym.                                                    | Characteristic                | Min.   | Тур† | Max.   | Units | Conditions |  |  |

| F10          | Fosc                                                    | Oscillator Frequency Range    | 4      |      | 8      | MHz   |            |  |  |

| F11          | Fsys                                                    | On-Chip VCO System Frequency  | 16     | _    | 32     | MHz   |            |  |  |

| F12          | TRC                                                     | PLL Start-up Time (Lock Time) | —      | _    | 2      | ms    |            |  |  |

| F13*         | $\Delta \text{CLK}$                                     | CLKOUT Stability (Jitter)     | -0.25% | _    | +0.25% | %     |            |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

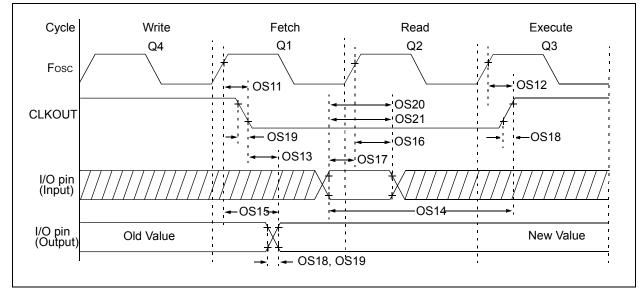

## FIGURE 30-7: CLKOUT AND I/O TIMING

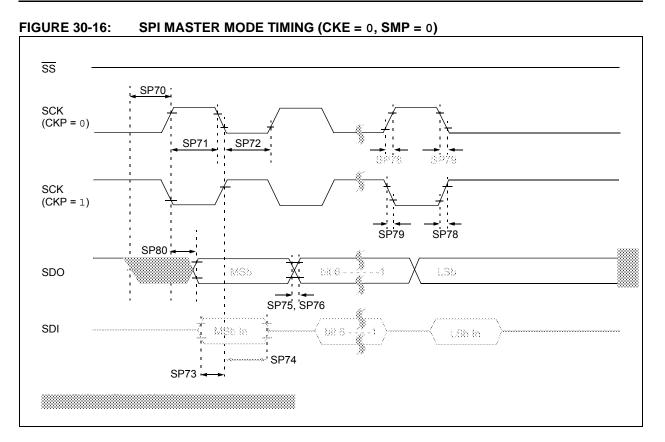

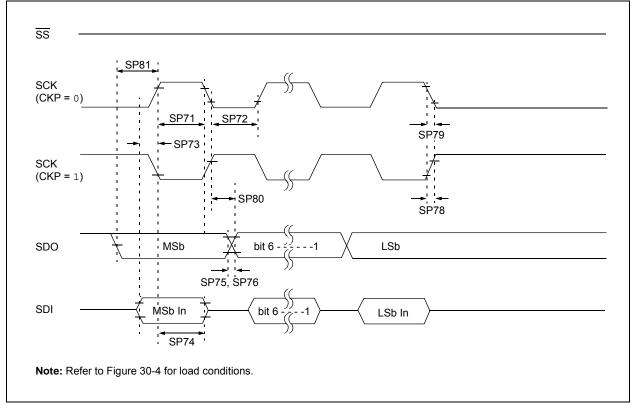

FIGURE 30-17: SPI MASTER MODE TIMING (CKE = 1, SMP = 1)

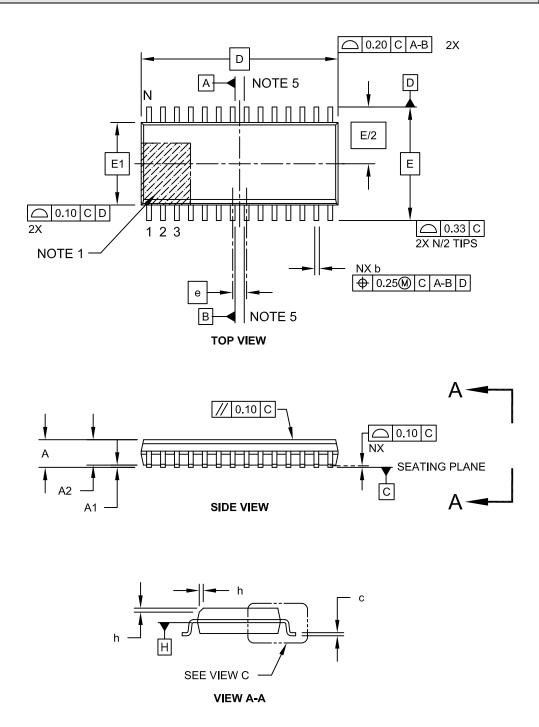

# 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-052C Sheet 1 of 2

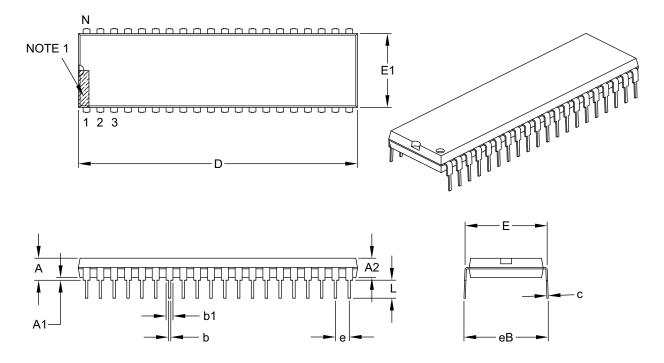

# 40-Lead Plastic Dual In-Line (P) – 600 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units                   |       | INCHES   |       |

|----------------------------|-------------------------|-------|----------|-------|

|                            | <b>Dimension Limits</b> | MIN   | NOM      | MAX   |

| Number of Pins             | N                       |       | 40       |       |

| Pitch                      | e                       |       | .100 BSC |       |

| Top to Seating Plane       | A                       | -     | -        | .250  |

| Molded Package Thickness   | A2                      | .125  | -        | .195  |

| Base to Seating Plane      | A1                      | .015  | -        | _     |

| Shoulder to Shoulder Width | E                       | .590  | -        | .625  |

| Molded Package Width       | E1                      | .485  | -        | .580  |

| Overall Length             | D                       | 1.980 | -        | 2.095 |

| Tip to Seating Plane       | L                       | .115  | -        | .200  |

| Lead Thickness             | С                       | .008  | -        | .015  |

| Upper Lead Width           | b1                      | .030  | -        | .070  |

| Lower Lead Width           | b                       | .014  | -        | .023  |

| Overall Row Spacing §      | eB                      | -     | -        | .700  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-016B