Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PSMC, PWM, WDT                               |

| Number of I/O              | 24                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 1K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 11x12b; D/A 1x8b                                                      |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-VQFN Exposed Pad                                                       |

| Supplier Device Package    | 28-QFN (6x6)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1786-e-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

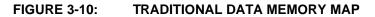

## 3.6.1 TRADITIONAL DATA MEMORY

The traditional data memory is a region from FSR address 0x000 to FSR address 0xFFF. The addresses correspond to the absolute addresses of all SFR, GPR and common registers.

# PIC16(L)F1784/6/7

| Name   | Bit 7  | Bit 6  | Bit 5 | Bit 4 | Bit 3     | Bit 2 | Bit 1 | Bit 0  | Register<br>on Page |

|--------|--------|--------|-------|-------|-----------|-------|-------|--------|---------------------|

| BORCON | SBOREN | BORFS  | _     |       | _         |       |       | BORRDY | 61                  |

| PCON   | STKOVF | STKUNF | _     | RWDT  | RMCLR     | RI    | POR   | BOR    | 65                  |

| STATUS |        |        | _     | TO    | PD        | Z     | DC    | С      | 27                  |

| WDTCON | —      | —      |       | V     | VDTPS<4:0 | >     |       | SWDTEN | 110                 |

## TABLE 5-5: SUMMARY OF REGISTERS ASSOCIATED WITH RESETS

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by Resets.

# 11.6 Register Definitions: Watchdog Control

## REGISTER 11-1: WDTCON: WATCHDOG TIMER CONTROL REGISTER

| U-0              | U-0                  | R/W-0/0                                                          | R/W-1/1        | R/W-0/0         | R/W-1/1          | R/W-1/1         | R/W-0/0      |

|------------------|----------------------|------------------------------------------------------------------|----------------|-----------------|------------------|-----------------|--------------|

| _                | —                    |                                                                  |                | WDTPS<4:02      | >                |                 | SWDTEN       |

| bit 7            |                      |                                                                  |                |                 |                  |                 | bit C        |

|                  |                      |                                                                  |                |                 |                  |                 |              |

| Legend:          |                      |                                                                  |                |                 |                  |                 |              |

| R = Readable     |                      | W = Writable                                                     | bit            | •               | mented bit, read |                 |              |

| u = Bit is unc   | hanged               | x = Bit is unkı                                                  | nown           | -m/n = Value    | at POR and BC    | OR/Value at all | other Resets |

| '1' = Bit is set | t                    | '0' = Bit is cle                                                 | ared           |                 |                  |                 |              |

| bit 7-6          | Unimpleme            | nted: Read as '                                                  | 0'             |                 |                  |                 |              |

| bit 5-1          | -                    | D>: Watchdog Ti                                                  |                | elect bits(1)   |                  |                 |              |

|                  |                      | Prescale Rate                                                    |                |                 |                  |                 |              |

|                  |                      | eserved. Result                                                  | s in minimum   | interval (1:32) |                  |                 |              |

|                  | •                    |                                                                  |                | (1.02)          |                  |                 |              |

|                  | •                    |                                                                  |                |                 |                  |                 |              |

|                  | • _                  |                                                                  |                |                 |                  |                 |              |

|                  | 10011 = R            | eserved. Result                                                  | s in minimum   | interval (1:32) |                  |                 |              |

|                  | 10010 = <b>1</b> :   | .8388608 (2 <sup>23</sup> ) (                                    | Interval 256s  | nominal)        |                  |                 |              |

|                  |                      | 4194304 (2 <sup>22</sup> ) (                                     |                |                 |                  |                 |              |

|                  | 10000 = 1:           | :2097152 (2 <sup>21</sup> ) (                                    | Interval 64s n | ominal)         |                  |                 |              |

|                  | 01111 = 1:           | 1048576 (2 <sup>20</sup> ) (<br>524288 (2 <sup>19</sup> ) (Ir    | Interval 32s n | ominal)         |                  |                 |              |

|                  | 01110 = 1:           | :524288 (2 <sup>+s</sup> ) (Ir<br>:262144 (2 <sup>18</sup> ) (Ir | iterval 16s no | minal)          |                  |                 |              |

|                  |                      | :262144 (2 <sup>13</sup> ) (Ir<br>:131072 (2 <sup>17</sup> ) (Ir |                |                 |                  |                 |              |

|                  |                      | :65536 (Interval                                                 |                |                 |                  |                 |              |

|                  |                      | 32768 (Interval                                                  |                |                 |                  |                 |              |

|                  |                      | 16384 (Interval                                                  |                | nal)            |                  |                 |              |

|                  |                      | 8192 (Interval 2                                                 |                | ,               |                  |                 |              |

|                  |                      | 4096 (Interval 1                                                 |                |                 |                  |                 |              |

|                  |                      | 2048 (Interval 6                                                 |                |                 |                  |                 |              |

|                  |                      | :1024 (Interval 3<br>:512 (Interval 16                           |                | )               |                  |                 |              |

|                  |                      | :256 (Interval 8 r                                               | ,              |                 |                  |                 |              |

|                  |                      | 128 (Interval 4 r                                                | ,              |                 |                  |                 |              |

|                  | 00001 = <b>1</b> :   | 64 (Interval 2 m                                                 | s nominal)     |                 |                  |                 |              |

|                  | 00000 = 1:           | :32 (Interval 1 m                                                | s nominal)     |                 |                  |                 |              |

| bit 0            | SWDTEN: S            | Software Enable                                                  | /Disable for W | /atchdog Timer  | bit              |                 |              |

|                  | <u>If WDTE&lt;1:</u> | 0> = 1x:                                                         |                |                 |                  |                 |              |

|                  | This bit is ig       |                                                                  |                |                 |                  |                 |              |

|                  | If WDTE<1:           |                                                                  |                |                 |                  |                 |              |

|                  | 1 = WDT is           |                                                                  |                |                 |                  |                 |              |

|                  | 0 = WDT is           |                                                                  |                |                 |                  |                 |              |

|                  | If WDTE<1:0          | 0 > = 0 0                                                        |                |                 |                  |                 |              |

Note 1: Times are approximate. WDT time is based on 31 kHz LFINTOSC.

# PIC16(L)F1784/6/7

## EXAMPLE 12-3: FLASH PROGRAM MEMORY READ

```

* This code block will read 1 word of program

* memory at the memory address:

PROG_ADDR_HI : PROG_ADDR_LO

data will be returned in the variables;

*

PROG_DATA_HI, PROG_DATA_LO

MOVLW PROG_ADDR_LO ;

MOVWF EEADRL ; Select Bank for EEPROM registers

MOVWF EEADRL ; Store LSB of address

MOVLW PROG_ADDR_HI ;

MOVWL EEADRH

EECON1,CFGS ; Do not select Configuration Space

EECON1,EEPGD ; Select Program Memory

BCF

EECON1,CFGS

BSF

INTCON,GIE ; Disable interrupts

BCF

; Initiate read

; Executed (Figure 12-1)

BSF

EECON1,RD

NOP

; Ignored (Figure 12-1)

NOP

INTCON,GIE

; Restore interrupts

BSF

MOVF

EEDATL,W

; Get LSB of word

MOVWF PROG_DATA_LO ; Store in user location

; Get MSB of word

MOVE

EEDATH,W

PROG_DATA_HI

MOVWF

; Store in user location

```

# REGISTER 13-40: SLRCONE: PORTE SLEW RATE CONTROL REGISTER<sup>(1)</sup>

| U-0              | U-0       | U-0               | U-0 | U-0                                | R/W-0/0       | R/W-0/0           | R/W-0/0   |  |  |

|------------------|-----------|-------------------|-----|------------------------------------|---------------|-------------------|-----------|--|--|

| _                | _         | _                 | _   | _                                  | SLRE2         | SLRE1             | SLRE0     |  |  |

| bit 7            |           | ·                 |     | ·                                  |               | •                 | bit 0     |  |  |

|                  |           |                   |     |                                    |               |                   |           |  |  |

| Legend:          |           |                   |     |                                    |               |                   |           |  |  |

| R = Readable     | bit       | W = Writable b    | it  | U = Unimplemented bit, read as '0' |               |                   |           |  |  |

| u = Bit is uncha | anged     | x = Bit is unkno  | own | -n/n = Value a                     | t POR and BOR | Value at all othe | er Resets |  |  |

| '1' = Bit is set |           | '0' = Bit is clea | red |                                    |               |                   |           |  |  |

|                  |           |                   |     |                                    |               |                   |           |  |  |

| bit 7-3          | Unimpleme | nted: Read as '0' |     |                                    |               |                   |           |  |  |

| bit 2-0 | SLRE<2:0>: PORTE Slew Rate Enable bits |

|---------|----------------------------------------|

|         | For RE<2:0> pins, respectively         |

|         | 1 = Port pin slew rate is limited      |

|         | 0 = Port pin slews at maximum rate     |

Note 1: SLRE<2:0> are available on PIC16(L)F1784/7 only.

## REGISTER 13-41: INLVLE: PORTE INPUT LEVEL CONTROL REGISTER

| U-0   | U-0 | U-0 | U-0 | R/W-1/1 | R/W-1/1                | R/W-1/1                | R/W-1/1                |

|-------|-----|-----|-----|---------|------------------------|------------------------|------------------------|

| —     | _   | _   | _   | INLVLE3 | INLVLE2 <sup>(1)</sup> | INLVLE1 <sup>(1)</sup> | INLVLE0 <sup>(1)</sup> |

| bit 7 | •   |     |     |         |                        |                        | bit 0                  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| 0' |

|----|

|    |

bit 3-0 INLVLE<3:0>: PORTE Input Level Select bit<sup>(1)</sup>

1 = ST input used for PORT reads and interrupt-on-change

0 = TTL input used for PORT reads and interrupt-on-change

**Note 1:** INLVLE<2:0> are available on PIC16(L)F1784/7 only.

|                        |       |       |       |          | •       |                        | —                      |                        |                     |

|------------------------|-------|-------|-------|----------|---------|------------------------|------------------------|------------------------|---------------------|

| Name                   | Bit 7 | Bit 6 | Bit 5 | Bit 4    | Bit 3   | Bit 2                  | Bit 1                  | Bit 0                  | Register<br>on Page |

| ADCON0                 | ADRMD |       |       | CHS<4:0> | •       |                        | GO/DONE                | ADON                   | 172                 |

| ANSELE                 | _     | _     | _     | _        |         | ANSE2                  | ANSE1                  | ANSE0                  | 153                 |

| INLVLE                 | —     | _     | —     | _        | INLVLE3 | INLVLE2 <sup>(2)</sup> | INLVLE1 <sup>(2)</sup> | INLVLE0 <sup>(2)</sup> | 155                 |

| LATE <sup>(2)</sup>    | _     | _     | _     | _        |         | LATE2                  | LATE1                  | LATE0                  | 153                 |

| ODCONE <sup>(2)</sup>  | _     | _     | _     | _        |         | ODE2                   | ODE1                   | ODE0                   | 154                 |

| PORTE                  | —     | _     | —     | _        | RE3     | RE2 <sup>(2)</sup>     | RE1 <sup>(2)</sup>     | RE0 <sup>(2)</sup>     | 152                 |

| SLRCONE <sup>(2)</sup> | _     | _     | _     | _        |         | SLRE2                  | SLRE1                  | SLRE0                  | 155                 |

| TRISE                  | _     | _     | _     | _        | (1)     | TRISE2 <sup>(2)</sup>  | TRISE1 <sup>(2)</sup>  | TRISE0 <sup>(2)</sup>  | 152                 |

| WPUE                   | _     | _     | _     | _        | WPUE3   | WPUE2 <sup>(2)</sup>   | WPUE1 <sup>(2)</sup>   | WPUE0 <sup>(2)</sup>   | 154                 |

## TABLE 13-12: SUMMARY OF REGISTERS ASSOCIATED WITH PORTE

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTE.

Note 1: Unimplemented, read as '1'.

2: PIC16(L)F1784/7 only

# 14.0 INTERRUPT-ON-CHANGE

All pins on all ports can be configured to operate as Interrupt-On-Change (IOC) pins. An interrupt can be generated by detecting a signal that has either a rising edge or a falling edge. Any individual pin, or combination of pins, can be configured to generate an interrupt. The interrupt-on-change module has the following features:

- Interrupt-on-Change enable (Master Switch)

- Individual pin configuration

- Rising and falling edge detection

- Individual pin interrupt flags

Figure 14-1 is a block diagram of the IOC module.

# 14.1 Enabling the Module

To allow individual pins to generate an interrupt, the IOCIE bit of the INTCON register must be set. If the IOCIE bit is disabled, the edge detection on the pin will still occur, but an interrupt will not be generated.

# 14.2 Individual Pin Configuration

For each pin, a rising edge detector and a falling edge detector are present. To enable a pin to detect a rising edge, the associated bit of the IOCxP register is set. To enable a pin to detect a falling edge, the associated bit of the IOCxN register is set.

A pin can be configured to detect rising and falling edges simultaneously by setting the associated bits in both of the IOCxP and IOCxN registers.

## 14.3 Interrupt Flags

The bits located in the IOCxF registers are status flags that correspond to the Interrupt-on-change pins of each port. If an expected edge is detected on an appropriately enabled pin, then the status flag for that pin will be set, and an interrupt will be generated if the IOCIE bit is set. The IOCIF bit of the INTCON register reflects the status of all IOCxF bits.

# 14.4 Clearing Interrupt Flags

The individual status flags, (IOCxF register bits), can be cleared by resetting them to zero. If another edge is detected during this clearing operation, the associated status flag will be set at the end of the sequence, regardless of the value actually being written.

In order to ensure that no detected edge is lost while clearing flags, only AND operations masking out known changed bits should be performed. The following sequence is an example of what should be performed.

## EXAMPLE 14-1: CLEARING INTERRUPT FLAGS (PORTA EXAMPLE)

MOVLW 0xff XORWF IOCAF, W ANDWF IOCAF, F

# 14.5 Operation in Sleep

The interrupt-on-change interrupt sequence will wake the device from Sleep mode, if the IOCIE bit is set.

If an edge is detected while in Sleep mode, the affected IOCxF register will be updated prior to the first instruction executed out of Sleep.

# 17.3 Register Definitions: ADC Control

## REGISTER 17-1: ADCON0: ADC CONTROL REGISTER 0

| R/W-0/0                   | R/W-0/0                                   | R/W-0/0                                                                                                          | R/W-0/0                             | R/W-0/0           | R/W-0/0         | R/W-0/0            | R/W-0/0 |

|---------------------------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------|-------------------------------------|-------------------|-----------------|--------------------|---------|

| ADRMD                     |                                           |                                                                                                                  | CHS<4:0>                            |                   |                 | GO/DONE            | ADON    |

| bit 7                     | 1                                         |                                                                                                                  |                                     |                   |                 |                    | bit (   |

| l agandi                  |                                           |                                                                                                                  |                                     |                   |                 |                    |         |

| Legend:<br>D - Doodabla k |                                           | )// - )//ritabla bit                                                                                             |                                     | LI – Unimploma    | ntad hit raad a | a (O)              |         |

| R = Readable b            |                                           | W = Writable bit                                                                                                 |                                     | U = Unimpleme     |                 |                    | -       |

| u = Bit is uncha          | inged                                     | x = Bit is unkno                                                                                                 |                                     | -n/n = Value at   | POR and BOR/    | Value at all other | Resets  |

| '1' = Bit is set          |                                           | '0' = Bit is cleare                                                                                              | ed                                  |                   |                 |                    |         |

| bit 7                     | 1 = ADRESL                                | Result Mode bit<br>and ADRESH pro<br>and ADRESH pro                                                              |                                     |                   |                 |                    |         |

|                           | See Figure 17                             | -3 for details                                                                                                   |                                     |                   |                 |                    |         |

| bit 6-2                   | 11111 = FVF<br>11110 = DAG<br>11101 = Ten | ositive Differential<br>R (Fixed Voltage R<br>C_output <sup>(2)</sup><br>nperature Indicato<br>served. No channe | eference) Buffe<br>r <sup>(4)</sup> |                   |                 |                    |         |

|                           | •                                         |                                                                                                                  |                                     |                   |                 |                    |         |

|                           | 10101 = AN2                               | served. No channe<br>21 <sup>(1)</sup><br>served. No channe                                                      |                                     |                   |                 |                    |         |

|                           | •                                         |                                                                                                                  |                                     |                   |                 |                    |         |

|                           | •                                         |                                                                                                                  |                                     |                   |                 |                    |         |

|                           | 01110 = Res                               | erved. No channe                                                                                                 | l connected.                        |                   |                 |                    |         |

|                           | 01101 = AN                                |                                                                                                                  |                                     |                   |                 |                    |         |

|                           | 01100 = AN                                |                                                                                                                  |                                     |                   |                 |                    |         |

|                           | $01011 = AN^{2}$                          |                                                                                                                  |                                     |                   |                 |                    |         |

|                           | $01010 = AN^{2}$                          |                                                                                                                  |                                     |                   |                 |                    |         |

|                           | 01001 = ANS<br>01000 = ANS                |                                                                                                                  |                                     |                   |                 |                    |         |

|                           | 00111 = AN7                               |                                                                                                                  |                                     |                   |                 |                    |         |

|                           | 00110 = AN6                               | <sub>3</sub> (1)                                                                                                 |                                     |                   |                 |                    |         |

|                           | 00101 = AN                                |                                                                                                                  |                                     |                   |                 |                    |         |

|                           | 00100 = AN4                               |                                                                                                                  |                                     |                   |                 |                    |         |

|                           | 00011 = AN3                               | 3                                                                                                                |                                     |                   |                 |                    |         |

|                           | 00010 = AN2                               | 2                                                                                                                |                                     |                   |                 |                    |         |

|                           | 00001 = AN <sup>2</sup>                   | 1                                                                                                                |                                     |                   |                 |                    |         |

|                           | 00000 = AN0                               | )                                                                                                                |                                     |                   |                 |                    |         |

| bit 1                     | 1 = ADC conv<br>This bit is               | DC Conversion Sta<br>ersion cycle in pro<br>automatically clea<br>ersion completed/                              | ogress. Setting<br>red by hardwar   | e when the ADC    |                 |                    |         |

| bit 0                     | ADON: ADC                                 | •                                                                                                                | 1 3 2 5 6                           |                   |                 |                    |         |

|                           | 1 = ADC is en                             |                                                                                                                  | nes no operatir                     | ig current        |                 |                    |         |

| 2: See<br>3: See          | e <b>Section 15.0</b> "                   | <sup>nly.</sup><br>'Digital-to-Analog<br>'Fixed Voltage Re<br>'Temperature Ind                                   | eference (FVR)                      | " for more inform | ation.          | n.                 |         |

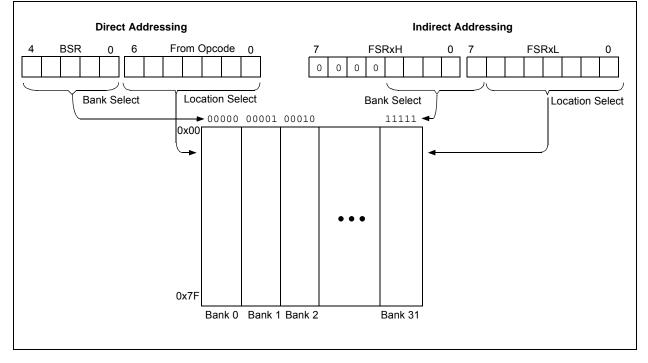

## 24.3.10 VARIABLE FREQUENCY – FIXED DUTY CYCLE PWM

This mode of operation is quite different from all of the other modes. It uses only the period event for waveform generation. At each period event, the PWM output is toggled.

The rising edge and falling edge events are unused in this mode.

## 24.3.10.1 Mode Features

- · No dead-band control available

- · No steering control available

- Fractional Frequency Adjust

- Fine period adjustments are made with the PSMC Fractional Frequency Adjust (PSMCxFFA) register (Register 24-28)

- PWM is output on the following pin only:

- PSMCxA

# 24.3.10.2 Waveform Generation

#### Period Event

- · Output of PSMCxA is toggled

- FFA counter is incremented by the 4-bit value in PSMCxF FA

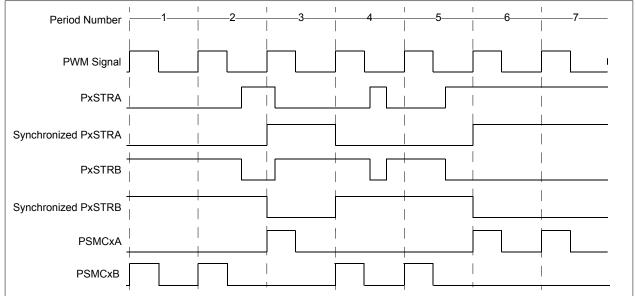

# FIGURE 24-13: VARIABLE FREQUENCY – FIXED DUTY CYCLE PWM WAVEFORM

### 24.5.4 SYNCHRONIZED PWM STEERING

In Single, Complementary and 3-phase PWM modes, it is possible to synchronize changes to steering selections with the period event. This is so that PWM outputs do not change in the middle of a cycle and therefore, disrupt operation of the application.

Steering synchronization is enabled by setting the PxSSYNC bit of the PSMC Steering Control 1 (PSMCxSTR1) register (Register 24-32).

When synchronized steering is enabled while the PSMC module is enabled, steering changes do not take effect until the first period event after the PSMCxLD bit is set.

Examples of synchronized steering are shown in Figure 24-18.

#### 24.5.5 INITIALIZING SYNCHRONIZED STEERING

If synchronized steering is to be used, special care should be taken to initialize the PSMC Steering Control 0 (PSMCxSTR0) register (Register 24-31) in a safe configuration before setting either the PSMCxEN or PSMCxLD bits. When either of those bits are set, the PSMCxSTR0 value at that time is loaded into the synchronized steering output buffer. The buffer load occurs even if the PxSSYNC bit is low. When the PxSSYNC bit is set, the outputs will immediately go to the drive states in the preloaded buffer.

FIGURE 24-18: PWM STEERING WITH SYNCHRONIZATION WAVEFORM

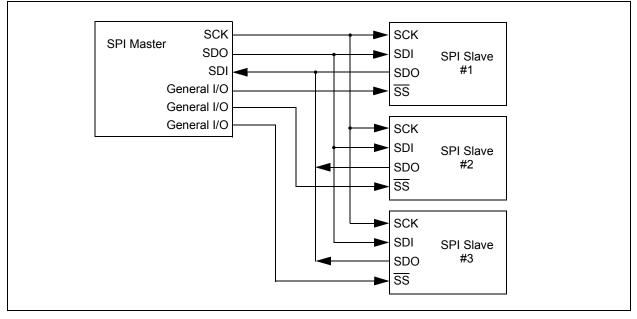

#### 26.2.1 SPI MODE REGISTERS

The MSSP module has five registers for SPI mode operation. These are:

- MSSP STATUS register (SSPSTAT)

- MSSP Control register 1 (SSPCON1)

- MSSP Control register 3 (SSPCON3)

- MSSP Data Buffer register (SSPBUF)

- MSSP Address register (SSPADD)

- MSSP Shift register (SSPSR) (Not directly accessible)

SSPCON1 and SSPSTAT are the control and STATUS registers in SPI mode operation. The SSPCON1 register is readable and writable. The lower 6 bits of the SSPSTAT are read-only. The upper 2 bits of the SSPSTAT are read/write.

In one SPI master mode, SSPADD can be loaded with a value used in the Baud Rate Generator. More information on the Baud Rate Generator is available in **Section 26.7 "Baud Rate Generator"**.

SSPSR is the shift register used for shifting data in and out. SSPBUF provides indirect access to the SSPSR register. SSPBUF is the buffer register to which data bytes are written, and from which data bytes are read.

In receive operations, SSPSR and SSPBUF together create a buffered receiver. When SSPSR receives a complete byte, it is transferred to SSPBUF and the SSP1IF interrupt is set.

During transmission, the SSPBUF is not buffered. A write to SSPBUF will write to both SSPBUF and SSPSR.

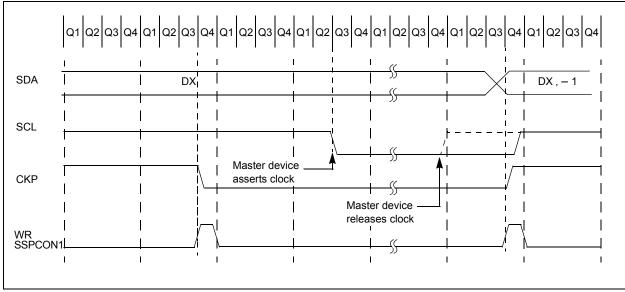

#### 26.5.6 CLOCK STRETCHING

Clock stretching occurs when a device on the bus holds the SCL line low effectively pausing communication. The slave may stretch the clock to allow more time to handle data or prepare a response for the master device. A master device is not concerned with stretching as anytime it is active on the bus and not transferring data it is stretching. Any stretching done by a slave is invisible to the master software and handled by the hardware that generates SCL.

The CKP bit of the SSPCON1 register is used to control stretching in software. Any time the CKP bit is cleared, the module will wait for the SCL line to go low and then hold it. Setting CKP will release SCL and allow more communication.

#### 26.5.6.1 Normal Clock Stretching

Following an  $\overline{ACK}$  if the  $R/\overline{W}$  bit of SSPSTAT is set, a read request, the slave hardware will clear CKP. This allows the slave time to update SSPBUF with data to transfer to the master. If the SEN bit of SSPCON2 is set, the slave hardware will always stretch the clock after the  $\overline{ACK}$  sequence. Once the slave is ready; CKP is set by software and communication resumes.

- Note 1: The BF bit has no effect on if the clock will be stretched or not. This is different than previous versions of the module that would not stretch the clock, clear CKP, if SSPBUF was read before the 9th falling edge of SCL.

- 2: Previous versions of the module did not stretch the clock for a transmission if SSPBUF was loaded before the 9th falling edge of SCL. It is now always cleared for read requests.

#### 26.5.6.2 10-bit Addressing Mode

In 10-bit Addressing mode, when the UA bit is set the clock is always stretched. This is the only time the SCL is stretched without CKP being cleared. SCL is released immediately after a write to SSPADD.

| Note: | Previous versions of the module did not      |

|-------|----------------------------------------------|

|       | stretch the clock if the second address byte |

|       | did not match.                               |

#### 26.5.6.3 Byte NACKing

When AHEN bit of SSPCON3 is set; CKP is cleared by hardware after the 8th falling edge of SCL for a received matching address byte. When DHEN bit of SSPCON3 is set; CKP is cleared after the 8th falling edge of SCL for received data.

Stretching after the 8th falling edge of SCL allows the slave to look at the received address or data and decide if it wants to ACK the received data.

# 26.5.7 CLOCK SYNCHRONIZATION AND THE CKP BIT

Any time the CKP bit is cleared, the module will wait for the SCL line to go low and then hold it. However, clearing the CKP bit will not assert the SCL output low until the SCL output is already sampled low. Therefore, the CKP bit will not assert the SCL line until an external  $I^2C$  master device has already asserted the SCL line. The SCL output will remain low until the CKP bit is set and all other devices on the  $I^2C$  bus have released SCL. This ensures that a write to the CKP bit will not violate the minimum high time requirement for SCL (see Figure 26-22).

#### FIGURE 26-23: CLOCK SYNCHRONIZATION TIMING

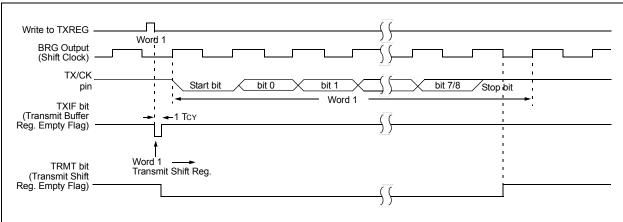

## 27.1.1.5 TSR Status

The TRMT bit of the TXSTA register indicates the status of the TSR register. This is a read-only bit. The TRMT bit is set when the TSR register is empty and is cleared when a character is transferred to the TSR register from the TXREG. The TRMT bit remains clear until all bits have been shifted out of the TSR register. No interrupt logic is tied to this bit, so the user has to poll this bit to determine the TSR status.

| Note: | The TSR register is not mapped in data      |

|-------|---------------------------------------------|

|       | memory, so it is not available to the user. |

## 27.1.1.6 Transmitting 9-Bit Characters

The EUSART supports 9-bit character transmissions. When the TX9 bit of the TXSTA register is set, the EUSART will shift nine bits out for each character transmitted. The TX9D bit of the TXSTA register is the ninth, and Most Significant, data bit. When transmitting 9-bit data, the TX9D data bit must be written before writing the eight Least Significant bits into the TXREG. All nine bits of data will be transferred to the TSR shift register immediately after the TXREG is written.

A special 9-bit Address mode is available for use with multiple receivers. See **Section 27.1.2.7** "Address **Detection**" for more information on the address mode.

- 27.1.1.7 Asynchronous Transmission Set-up:

- 1. Initialize the SPBRGH, SPBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 27.4 "EUSART Baud Rate Generator (BRG)").

- 2. Enable the asynchronous serial port by clearing the SYNC bit and setting the SPEN bit.

- 3. If 9-bit transmission is desired, set the TX9 control bit. A set ninth data bit will indicate that the eight Least Significant data bits are an address when the receiver is set for address detection.

- 4. Set SCKP bit if inverted transmit is desired.

- 5. Enable the transmission by setting the TXEN control bit. This will cause the TXIF interrupt bit to be set.

- If interrupts are desired, set the TXIE interrupt enable bit of the PIE1 register. An interrupt will occur immediately provided that the GIE and PEIE bits of the INTCON register are also set.

- 7. If 9-bit transmission is selected, the ninth bit should be loaded into the TX9D data bit.

- 8. Load 8-bit data into the TXREG register. This will start the transmission.

#### FIGURE 27-3: ASYNCHRONOUS TRANSMISSION

|        | SYNC = 0, BRGH = 1, BRG16 = 0 |            |                             |                  |            |                             |                |            |                             |                |            |                             |

|--------|-------------------------------|------------|-----------------------------|------------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|

| BAUD   | Fosc = 8.000 MHz              |            |                             | Fosc = 4.000 MHz |            | Fosc = 3.6864 MHz           |                |            | Fosc = 1.000 MHz            |                |            |                             |

| RATE   | Actual<br>Rate                | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | —                             | _          | _                           |                  | _          | _                           |                | _          | _                           | 300            | 0.16       | 207                         |

| 1200   | —                             | —          | —                           | 1202             | 0.16       | 207                         | 1200           | 0.00       | 191                         | 1202           | 0.16       | 51                          |

| 2400   | 2404                          | 0.16       | 207                         | 2404             | 0.16       | 103                         | 2400           | 0.00       | 95                          | 2404           | 0.16       | 25                          |

| 9600   | 9615                          | 0.16       | 51                          | 9615             | 0.16       | 25                          | 9600           | 0.00       | 23                          | _              | _          | _                           |

| 10417  | 10417                         | 0.00       | 47                          | 10417            | 0.00       | 23                          | 10473          | 0.53       | 21                          | 10417          | 0.00       | 5                           |

| 19.2k  | 19231                         | 0.16       | 25                          | 19.23k           | 0.16       | 12                          | 19.2k          | 0.00       | 11                          | _              | _          | _                           |

| 57.6k  | 55556                         | -3.55      | 8                           | —                | _          | _                           | 57.60k         | 0.00       | 3                           | —              | _          | _                           |

| 115.2k | —                             | _          | —                           |                  | _          | —                           | 115.2k         | 0.00       | 1                           |                | _          | —                           |

# TABLE 27-5: BAUD RATES FOR ASYNCHRONOUS MODES (CONTINUED)

|        |                   | SYNC = 0, BRGH = 0, BRG16 = 1 |                             |                   |            |                             |                |            |                             |                |            |                             |  |

|--------|-------------------|-------------------------------|-----------------------------|-------------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|--|

| BAUD   | Fosc = 32.000 MHz |                               |                             | Fosc = 20.000 MHz |            | Fosc = 18.432 MHz           |                |            | Fosc = 11.0592 MHz          |                |            |                             |  |

| RATE   | Actual<br>Rate    | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) |  |

| 300    | 300.0             | 0.00                          | 6666                        | 300.0             | -0.01      | 4166                        | 300.0          | 0.00       | 3839                        | 300.0          | 0.00       | 2303                        |  |

| 1200   | 1200              | -0.02                         | 3332                        | 1200              | -0.03      | 1041                        | 1200           | 0.00       | 959                         | 1200           | 0.00       | 575                         |  |

| 2400   | 2401              | -0.04                         | 832                         | 2399              | -0.03      | 520                         | 2400           | 0.00       | 479                         | 2400           | 0.00       | 287                         |  |

| 9600   | 9615              | 0.16                          | 207                         | 9615              | 0.16       | 129                         | 9600           | 0.00       | 119                         | 9600           | 0.00       | 71                          |  |

| 10417  | 10417             | 0.00                          | 191                         | 10417             | 0.00       | 119                         | 10378          | -0.37      | 110                         | 10473          | 0.53       | 65                          |  |

| 19.2k  | 19.23k            | 0.16                          | 103                         | 19.23k            | 0.16       | 64                          | 19.20k         | 0.00       | 59                          | 19.20k         | 0.00       | 35                          |  |

| 57.6k  | 57.14k            | -0.79                         | 34                          | 56.818            | -1.36      | 21                          | 57.60k         | 0.00       | 19                          | 57.60k         | 0.00       | 11                          |  |

| 115.2k | 117.6k            | 2.12                          | 16                          | 113.636           | -1.36      | 10                          | 115.2k         | 0.00       | 9                           | 115.2k         | 0.00       | 5                           |  |

|        | SYNC = 0, BRGH = 0, BRG16 = 1 |            |                             |                  |            |                             |                |            |                             |                |            |                             |

|--------|-------------------------------|------------|-----------------------------|------------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|

| BAUD   | Fosc = 8.000 MHz              |            |                             | Fosc = 4.000 MHz |            | Fosc = 3.6864 MHz           |                |            | Fosc = 1.000 MHz            |                |            |                             |

| RATE   | Actual<br>Rate                | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | 299.9                         | -0.02      | 1666                        | 300.1            | 0.04       | 832                         | 300.0          | 0.00       | 767                         | 300.5          | 0.16       | 207                         |

| 1200   | 1199                          | -0.08      | 416                         | 1202             | 0.16       | 207                         | 1200           | 0.00       | 191                         | 1202           | 0.16       | 51                          |

| 2400   | 2404                          | 0.16       | 207                         | 2404             | 0.16       | 103                         | 2400           | 0.00       | 95                          | 2404           | 0.16       | 25                          |

| 9600   | 9615                          | 0.16       | 51                          | 9615             | 0.16       | 25                          | 9600           | 0.00       | 23                          | _              | _          | _                           |

| 10417  | 10417                         | 0.00       | 47                          | 10417            | 0.00       | 23                          | 10473          | 0.53       | 21                          | 10417          | 0.00       | 5                           |

| 19.2k  | 19.23k                        | 0.16       | 25                          | 19.23k           | 0.16       | 12                          | 19.20k         | 0.00       | 11                          | _              | _          | _                           |

| 57.6k  | 55556                         | -3.55      | 8                           | —                | —          | _                           | 57.60k         | 0.00       | 3                           | —              | _          | _                           |

| 115.2k | —                             | _          | _                           | _                | _          | _                           | 115.2k         | 0.00       | 1                           | _              | _          | _                           |

# 27.4.2 AUTO-BAUD OVERFLOW

During the course of automatic baud detection, the ABDOVF bit of the BAUDCON register will be set if the baud rate counter overflows before the fifth rising edge is detected on the RX pin. The ABDOVF bit indicates that the counter has exceeded the maximum count that can fit in the 16 bits of the SPBRGH:SPBRGL register pair. After the ABDOVF bit has been set, the counter continues to count until the fifth rising edge is detected on the RX pin. Upon detecting the fifth RX edge, the hardware will set the RCIF interrupt flag and clear the ABDEN bit of the BAUDCON register. The RCIF flag can be subsequently cleared by reading the RCREG register. The ABDOVF flag of the BAUDCON register can be cleared by software directly.

To terminate the auto-baud process before the RCIF flag is set, clear the ABDEN bit then clear the ABDOVF bit of the BAUDCON register. The ABDOVF bit will remain set if the ABDEN bit is not cleared first.

## 27.4.3 AUTO-WAKE-UP ON BREAK

During Sleep mode, all clocks to the EUSART are suspended. Because of this, the Baud Rate Generator is inactive and a proper character reception cannot be performed. The Auto-Wake-up feature allows the controller to wake-up due to activity on the RX/DT line. This feature is available only in Asynchronous mode.

The Auto-Wake-up feature is enabled by setting the WUE bit of the BAUDCON register. Once set, the normal receive sequence on RX/DT is disabled, and the EUSART remains in an Idle state, monitoring for a wake-up event independent of the CPU mode. A wake-up event consists of a high-to-low transition on the RX/DT line. (This coincides with the start of a Sync Break or a wake-up signal character for the LIN protocol.)

The EUSART module generates an RCIF interrupt coincident with the wake-up event. The interrupt is generated synchronously to the Q clocks in normal CPU operating modes (Figure 27-7), and asynchronously if the device is in Sleep mode (Figure 27-8). The interrupt condition is cleared by reading the RCREG register.

The WUE bit is automatically cleared by the low-to-high transition on the RX line at the end of the Break. This signals to the user that the Break event is over. At this point, the EUSART module is in Idle mode waiting to receive the next character.

# 27.4.3.1 Special Considerations

#### Break Character

To avoid character errors or character fragments during a wake-up event, the wake-up character must be all zeros.

When the wake-up is enabled the function works independent of the low time on the data stream. If the WUE bit is set and a valid non-zero character is received, the low time from the Start bit to the first rising edge will be interpreted as the wake-up event. The remaining bits in the character will be received as a fragmented character and subsequent characters can result in framing or overrun errors.

Therefore, the initial character in the transmission must be all '0's. This must be ten or more bit times, 13-bit times recommended for LIN bus, or any number of bit times for standard RS-232 devices.

#### Oscillator Start-up Time

Oscillator start-up time must be considered, especially in applications using oscillators with longer start-up intervals (i.e., LP, XT or HS/PLL mode). The Sync Break (or wake-up signal) character must be of sufficient length, and be followed by a sufficient interval, to allow enough time for the selected oscillator to start and provide proper initialization of the EUSART.

#### WUE Bit

The wake-up event causes a receive interrupt by setting the RCIF bit. The WUE bit is cleared in hardware by a rising edge on RX/DT. The interrupt condition is then cleared in software by reading the RCREG register and discarding its contents.

To ensure that no actual data is lost, check the RCIDL bit to verify that a receive operation is not in process before setting the WUE bit. If a receive operation is not occurring, the WUE bit may then be set just prior to entering the Sleep mode.

# 27.5 EUSART Synchronous Mode

Synchronous serial communications are typically used in systems with a single master and one or more slaves. The master device contains the necessary circuitry for baud rate generation and supplies the clock for all devices in the system. Slave devices can take advantage of the master clock by eliminating the internal clock generation circuitry.

There are two signal lines in Synchronous mode: a bidirectional data line and a clock line. Slaves use the external clock supplied by the master to shift the serial data into and out of their respective receive and transmit shift registers. Since the data line is bidirectional, synchronous operation is half-duplex only. Half-duplex refers to the fact that master and slave devices can receive and transmit data but not both simultaneously. The EUSART can operate as either a master or slave device.

Start and Stop bits are not used in synchronous transmissions.

#### 27.5.1 SYNCHRONOUS MASTER MODE

The following bits are used to configure the EUSART for synchronous master operation:

- SYNC = 1

- CSRC = 1

- SREN = 0 (for transmit); SREN = 1 (for receive)

- CREN = 0 (for transmit); CREN = 1 (for receive)

- SPEN = 1

Setting the SYNC bit of the TXSTA register configures the device for synchronous operation. Setting the CSRC bit of the TXSTA register configures the device as a master. Clearing the SREN and CREN bits of the RCSTA register ensures that the device is in the Transmit mode, otherwise the device will be configured to receive. Setting the SPEN bit of the RCSTA register enables the EUSART.

## 27.5.1.1 Master Clock

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a master transmits the clock on the TX/CK line. The TX/CK pin output driver is automatically enabled when the EUSART is configured for synchronous transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One clock cycle is generated for each data bit. Only as many clock cycles are generated as there are data bits.

#### 27.5.1.2 Clock Polarity

A clock polarity option is provided for Microwire compatibility. Clock polarity is selected with the SCKP bit of the BAUDCON register. Setting the SCKP bit sets the clock Idle state as high. When the SCKP bit is set, the data changes on the falling edge of each clock. Clearing the SCKP bit sets the Idle state as low. When the SCKP bit is cleared, the data changes on the rising edge of each clock.

## 27.5.1.3 Synchronous Master Transmission

Data is transferred out of the device on the RX/DT pin. The RX/DT and TX/CK pin output drivers are automatically enabled when the EUSART is configured for synchronous master transmit operation.

A transmission is initiated by writing a character to the TXREG register. If the TSR still contains all or part of a previous character the new character data is held in the TXREG until the last bit of the previous character has been transmitted. If this is the first character, or the previous character has been completely flushed from the TSR, the data in the TXREG is immediately transferred to the TSR. The transmission of the character commences immediately following the transfer of the data to the TSR from the TXREG.

Each data bit changes on the leading edge of the master clock and remains valid until the subsequent leading clock edge.

Note: The TSR register is not mapped in data memory, so it is not available to the user.

- 27.5.1.4 Synchronous Master Transmission Set-up:

- Initialize the SPBRGH, SPBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 27.4 "EUSART Baud Rate Generator (BRG)").

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 3. Disable Receive mode by clearing bits SREN and CREN.

- 4. Enable Transmit mode by setting the TXEN bit.

- 5. If 9-bit transmission is desired, set the TX9 bit.

- If interrupts are desired, set the TXIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 7. If 9-bit transmission is selected, the ninth bit should be loaded in the TX9D bit.

- 8. Start transmission by loading data to the TXREG register.

# PIC16(L)F1784/6/7

| BCF              | Bit Clear f                                                         |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ label ] BCF f,b                                                   |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $0 \rightarrow (f \le b >)$                                         |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |

| BSF              | Bit Set f                                                           |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ]BSF f,b                                             |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $1 \rightarrow (f \le b >)$                                         |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is set.                                     |

| BRA              | Relative Branch                                                                                                                                                                                                                                 |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ]BRA label<br>[ <i>label</i> ]BRA \$+k                                                                                                                                                                                           |

| Operands:        | -256 $\leq$ label - PC + 1 $\leq$ 255 -256 $\leq$ k $\leq$ 255                                                                                                                                                                                  |

| Operation:       | $(PC) + 1 + k \rightarrow PC$                                                                                                                                                                                                                   |

| Status Affected: | None                                                                                                                                                                                                                                            |

| Description:     | Add the signed 9-bit literal 'k' to<br>the PC. Since the PC will have<br>incremented to fetch the next<br>instruction, the new address will<br>be PC + 1 + k. This instruction is<br>a 2-cycle instruction. This branch<br>has a limited range. |

**Relative Branch with W**

Add the contents of W (unsigned) to the PC. Since the PC will have incremented to fetch the next instruction, the new address will be PC + 1 + (W). This instruction

[label] BRW

$(PC) + (W) \rightarrow PC$

is a 2-cycle instruction.

None

None

| BTFSC            | Bit Test f, Skip if Clear                                                                                                                                                                                         |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BTFSC f,b                                                                                                                                                                                               |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                               |

| Operation:       | skip if (f <b>) = 0</b>                                                                                                                                                                                           |

| Status Affected: | None                                                                                                                                                                                                              |

| Description:     | If bit 'b' in register 'f' is '1', the next instruction is executed.<br>If bit 'b', in register 'f', is '0', the next instruction is discarded, and a NOP is executed instead, making this a 2-cycle instruction. |

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                                         |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BTFSS f,b                                                                                                                                                                                             |

| Operands:        | $0 \le f \le 127$<br>$0 \le b < 7$                                                                                                                                                                              |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                                                                                         |

| Status Affected: | None                                                                                                                                                                                                            |

| Description:     | If bit 'b' in register 'f' is '0', the next<br>instruction is executed.<br>If bit 'b' is '1', then the next<br>instruction is discarded and a NOP<br>is executed instead, making this a<br>2-cycle instruction. |

BRW

Syntax:

Operands:

Operation:

Description:

Status Affected:

# PIC16(L)F1784/6/7

Note: Unless otherwise noted, VIN = 5V, Fosc = 300 kHz, CIN = 0.1  $\mu$ F, TA = 25°C.

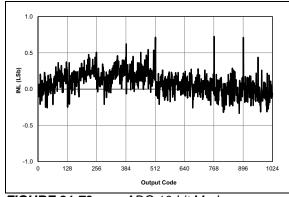

**FIGURE 31-79:** ADC 10-bit Mode, Single-Ended INL, VDD = 3.0V, TAD =  $1 \mu$ S,  $25^{\circ}$ C.

**FIGURE 31-80:** ADC 10-bit Mode, Single-Ended INL, VDD = 3.0V, TAD =  $4 \mu$ S,  $25^{\circ}$ C.

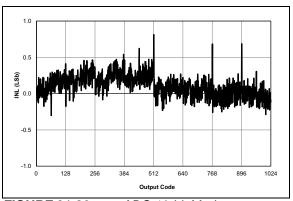

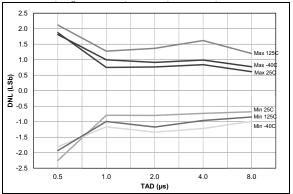

FIGURE 31-81: ADC 10-bit Mode, Single-Ended DNL, VDD = 3.0V, VREF = 3.0V.

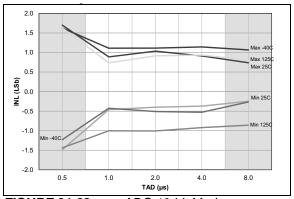

**FIGURE 31-83:** ADC 10-bit Mode, Single-Ended DNL, VDD = 3.0V,  $TAD = 1 \mu S$ .

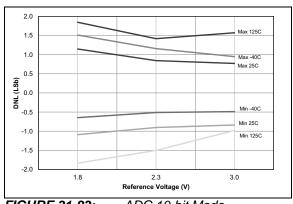

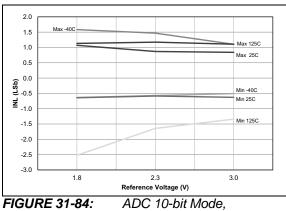

FIGURE 31-82: ADC 10-bit Mode, Single-Ended INL, VDD = 3.0V, VREF = 3.0V.

Single-Ended INL, VDD = 3.0V,  $TaD = 1 \ \mu$ S.

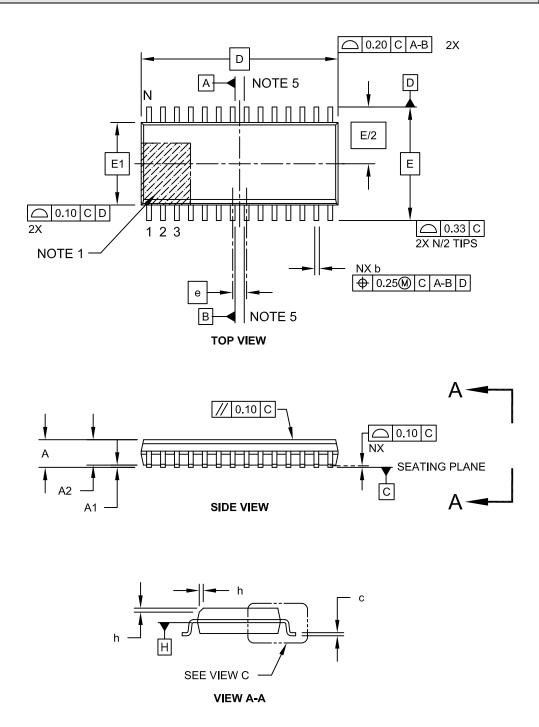

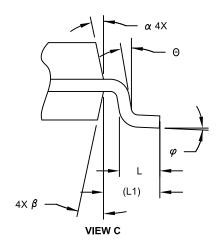

# 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-052C Sheet 1 of 2

# 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |           |           |      |  |  |  |

|--------------------------|-------------|-----------|-----------|------|--|--|--|

| Dimension                | Limits      | MIN       | NOM       | MAX  |  |  |  |

| Number of Pins           | N           |           | 28        |      |  |  |  |

| Pitch                    | е           |           | 1.27 BSC  |      |  |  |  |

| Overall Height           | A           | -         | -         | 2.65 |  |  |  |

| Molded Package Thickness | A2          | 2.05      | -         | -    |  |  |  |

| Standoff §               | A1          | 0.10      | -         | 0.30 |  |  |  |

| Overall Width            | E           |           | 10.30 BSC |      |  |  |  |

| Molded Package Width     | E1          | 7.50 BSC  |           |      |  |  |  |

| Overall Length           | D           | 17.90 BSC |           |      |  |  |  |

| Chamfer (Optional)       | h           | 0.25      | -         | 0.75 |  |  |  |

| Foot Length              | L           | 0.40      | -         | 1.27 |  |  |  |

| Footprint                | L1          | 1.40 REF  |           |      |  |  |  |

| Lead Angle               | Θ           | 0°        | -         | -    |  |  |  |

| Foot Angle               | φ           | 0°        | -         | 8°   |  |  |  |

| Lead Thickness           | С           | 0.18      | -         | 0.33 |  |  |  |

| Lead Width               | b           | 0.31      | -         | 0.51 |  |  |  |

| Mold Draft Angle Top     | α           | 5°        | -         | 15°  |  |  |  |

| Mold Draft Angle Bottom  | β           | 5°        | _         | 15°  |  |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.

- Dimensioning and tolerancing per ASME Y14.5M BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

- 5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing C04-052C Sheet 2 of 2

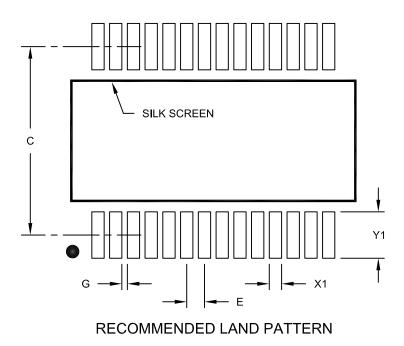

28-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |      |          |      |

|--------------------------|-------------|------|----------|------|

| Dimensior                | MIN         | NOM  | MAX      |      |

| Contact Pitch            |             |      | 0.65 BSC |      |

| Contact Pad Spacing      | С           |      | 7.20     |      |

| Contact Pad Width (X28)  | X1          |      |          | 0.45 |

| Contact Pad Length (X28) | Y1          |      |          | 1.75 |

| Distance Between Pads    | G           | 0.20 |          |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2073A