Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PSMC, PWM, WDT                               |

| Number of I/O              | 24                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 1K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 11x12b; D/A 1x8b                                                      |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

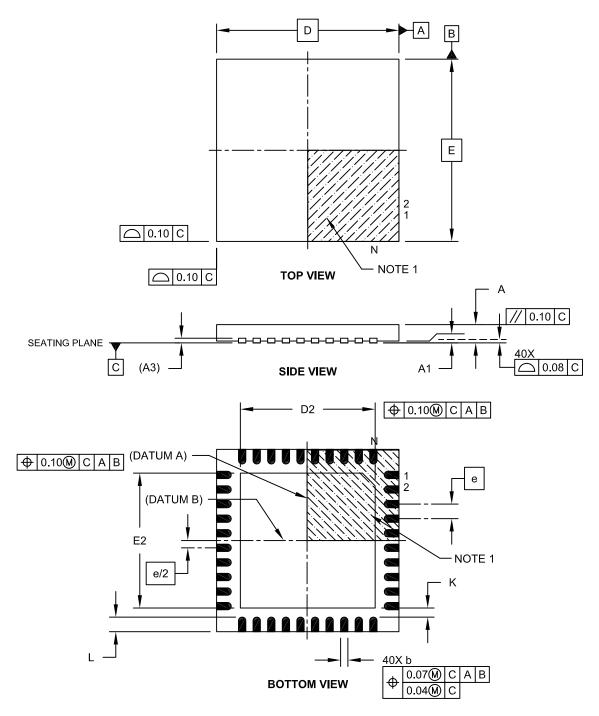

| Package / Case             | 28-VQFN Exposed Pad                                                       |

| Supplier Device Package    | 28-QFN (6x6)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1786-i-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 1: 28-PIN ALLOCATION TABLE (PIC16(L)F1786) (Continued)

| 0/1 | 28-Pin SPDIP,<br>SOIC, SSOP | 28-Pin QFN, | ADC | Reference | Comparator | Operation<br>Amplifiers | 8-bit DAC | Timers         | PSMC             | ссь  | EUSART                                 | MSSP                                     | Interrupt | Pull-up | Basic       |

|-----|-----------------------------|-------------|-----|-----------|------------|-------------------------|-----------|----------------|------------------|------|----------------------------------------|------------------------------------------|-----------|---------|-------------|

| RB7 | 28                          | 25          | _   | _         | _          | _                       | DAC1OUT2  | —              | —                | —    | RX <sup>(1)</sup><br>DT <sup>(1)</sup> | SCK <sup>(1)</sup><br>SCL <sup>(1)</sup> | IOC       | Y       | ICSPDAT     |

| RC0 | 11                          | 8           | —   | _         |            |                         | _         | T1OSO<br>T1CKI | PSMC1A           | _    |                                        | _                                        | IOC       | Y       |             |

| RC1 | 12                          | 9           | —   | _         | _          |                         | —         | T10SI          | PSMC1B           | CCP2 | _                                      | —                                        | IOC       | Y       | _           |

| RC2 | 13                          | 10          |     |           |            | _                       | —         | -              | PSMC1C<br>PSMC3B | CCP1 |                                        | -                                        | IOC       | Y       | _           |

| RC3 | 14                          | 11          | -   |           | -          | —                       | —         | -              | PSMC1D           | —    | -                                      | SCK<br>SCL                               | IOC       | Y       | —           |

| RC4 | 15                          | 12          | _   | —         | -          | _                       | —         | -              | PSMC1E           | -    | —                                      | SDI<br>SDA                               | IOC       | Y       | _           |

| RC5 | 16                          | 13          | _   | —         | —          | _                       | —         | —              | PSMC1F<br>PSMC3A | —    | _                                      | SDO                                      | IOC       | Y       | —           |

| RC6 | 17                          | 14          | _   | —         | —          | _                       | —         | -              | PSMC2A           | CCP3 | TX<br>CK                               | —                                        | IOC       | Y       | —           |

| RC7 | 18                          | 15          | -   | _         | C4OUT      | —                       | —         | —              | PSMC2B           | —    | RX<br>DT                               | -                                        | IOC       | Y       | _           |

| RE3 | 1                           | 26          | -   | —         | —          | —                       | —         | —              | -                | —    | —                                      | —                                        | IOC       | Y       | MCLR<br>VPP |

| Vdd | 20                          | 17          | —   | _         | _          |                         | —         | —              | —                |      | _                                      | —                                        |           | _       | Vdd         |

| Vss | 8,<br>19                    | 5, 16       | —   |           | _          | _                       | -         | —              | _                | —    |                                        | —                                        |           | _       | Vss         |

PIC16(L)F1784/6/7

Note 1: Alternate pin function selected with the APFCON1 (Register 13-1) and APFCON2 (Register 13-2) registers.

# TABLE 3-4: PIC16(L)F1786 MEMORY MAP (BANKS 0-7)

|      | BANK 0                                     |      | BANK 1                                     |              | BANK 2                                     |      | BANK 3                                     |      | BANK 4                                     |      | BANK 5                                     |      | BANK 6                                     |      | BANK 7                                     |

|------|--------------------------------------------|------|--------------------------------------------|--------------|--------------------------------------------|------|--------------------------------------------|------|--------------------------------------------|------|--------------------------------------------|------|--------------------------------------------|------|--------------------------------------------|

| 000h |                                            | 080h |                                            | 100h         |                                            | 180h |                                            | 200h |                                            | 280h |                                            | 300h |                                            | 380h |                                            |

|      | Core Registers<br>(Table 3-2)              |      | Core Registers<br>(Table 3-2)              |              | Core Registers<br>(Table 3-2)              |      | Core Registers<br>(Table 3-2)              |      | Core Registers<br>(Table 3-2)              |      | Core Registers<br>(Table 3-2)              |      | Core Registers<br>(Table 3-2)              |      | Core Registers<br>(Table 3-2)              |

| 00Bh |                                            | 08Bh |                                            | 10Bh         |                                            | 18Bh |                                            | 20Bh |                                            | 28Bh |                                            | 30Bh |                                            | 38Bh |                                            |

| 00Ch | PORTA                                      | 08Ch | TRISA                                      | 10Ch         | LATA                                       | 18Ch | ANSELA                                     | 20Ch | WPUA                                       | 28Ch | ODCONA                                     | 30Ch | SLRCONA                                    | 38Ch | INLVLA                                     |

| 00Dh | PORTB                                      | 08Dh | TRISB                                      | 10Dh         | LATB                                       | 18Dh | ANSELB                                     | 20Dh | WPUB                                       | 28Dh | ODCONB                                     | 30Dh | SLRCONB                                    | 38Dh | INLVLB                                     |

| 00Eh | PORTC                                      | 08Eh | TRISC                                      | 10Eh         | LATC                                       | 18Eh |                                            | 20Eh | WPUC                                       | 28Eh | ODCONC                                     | 30Eh | SLRCONC                                    | 38Eh | INLVLC                                     |

| 00Fh | —                                          | 08Fh | —                                          | 10Fh         | —                                          | 18Fh | —                                          | 20Fh | —                                          | 28Fh | —                                          | 30Fh | —                                          | 38Fh | —                                          |

| 010h | PORTE                                      | 090h | TRISE                                      | 110h         | —                                          | 190h | _                                          | 210h | WPUE                                       | 290h | —                                          | 310h | —                                          | 390h | INLVLE                                     |

| 011h | PIR1                                       | 091h | PIE1                                       | 111h         | CM1CON0                                    | 191h | EEADRL                                     | 211h | SSP1BUF                                    | 291h | CCPR1L                                     | 311h | —                                          | 391h | IOCAP                                      |

| 012h | PIR2                                       | 092h | PIE2                                       | 112h         | CM1CON1                                    | 192h | EEADRH                                     | 212h | SSP1ADD                                    | 292h | CCPR1H                                     | 312h | —                                          | 392h | IOCAN                                      |

| 013h |                                            | 093h | —                                          | 113h         | CM2CON0                                    | 193h | EEDATL                                     | 213h | SSP1MSK                                    | 293h | CCP1CON                                    | 313h |                                            | 393h | IOCAF                                      |

| 014h | PIR4                                       | 094h | PIE4                                       | 114h         | CM2CON1                                    | 194h | EEDATH                                     | 214h | SSP1STAT                                   | 294h | —                                          | 314h |                                            | 394h | IOCBP                                      |

| 015h | TMR0                                       | 095h | OPTION_REG                                 | 115h         | CMOUT                                      | 195h | EECON1                                     | 215h | SSP1CON1                                   | 295h | —                                          | 315h |                                            | 395h | IOCBN                                      |

| 016h | TMR1L                                      | 096h | PCON                                       | 116h         | BORCON                                     | 196h | EECON2                                     | 216h | SSP1CON2                                   | 296h | —                                          | 316h | —                                          | 396h | IOCBF                                      |

| 017h | TMR1H                                      | 097h | WDTCON                                     | 117h         | FVRCON                                     | 197h | VREGCON <sup>(1)</sup>                     | 217h | SSP1CON3                                   | 297h | —                                          | 317h | —                                          | 397h | IOCCP                                      |

| 018h | T1CON                                      | 098h | OSCTUNE                                    | 118h         | DAC1CON0                                   | 198h |                                            | 218h | _                                          | 298h | CCPR2L                                     | 318h |                                            | 398h | IOCCN                                      |

| 019h | T1GCON                                     | 099h | OSCCON                                     | 119h         | DAC1CON1                                   | 199h | RCREG                                      | 219h | —                                          | 299h | CCPR2H                                     | 319h | _                                          | 399h | IOCCF                                      |

| 01Ah | TMR2                                       | 09Ah | OSCSTAT                                    | 11Ah         | CM4CON0                                    | 19Ah | TXREG                                      | 21Ah | —                                          | 29Ah | CCP2CON                                    | 31Ah | —                                          | 39Ah | _                                          |

| 01Bh | PR2                                        | 09Bh | ADRESL                                     | 11Bh         | CM4CON1                                    | 19Bh | SPBRGL                                     | 21Bh | _                                          | 29Bh | —                                          | 31Bh | —                                          | 39Bh | _                                          |

| 01Ch | T2CON                                      | 09Ch | ADRESH                                     | 11Ch         | APFCON2                                    | 19Ch | SPBRGH                                     | 21Ch | _                                          | 29Ch | —                                          | 31Ch |                                            | 39Ch | _                                          |

| 01Dh | —                                          | 09Dh | ADCON0                                     | 11Dh         | APFCON1                                    | 19Dh | RCSTA                                      | 21Dh | —                                          | 29Dh | —                                          | 31Dh | —                                          | 39Dh | IOCEP                                      |

| 01Eh |                                            | 09Eh | ADCON1                                     | 11Eh         | CM3CON0                                    | 19Eh | TXSTA                                      | 21Eh | _                                          | 29Eh | —                                          | 31Eh |                                            | 39Eh | IOCEN                                      |

| 01Fh | —                                          | 09Fh | ADCON2                                     | 11Fh         | CM3CON1                                    | 19Fh | BAUDCON                                    | 21Fh | —                                          | 29Fh | —                                          | 31Fh | —                                          | 39Fh | IOCEF                                      |

| 020h |                                            | 0A0h |                                            | 120h         |                                            | 1A0h |                                            | 220h |                                            | 2A0h |                                            | 320h |                                            | 3A0h |                                            |

|      | General<br>Purpose<br>Register<br>80 Bytes |      | General<br>Purpose<br>Register<br>80 Bytes | 13Fh<br>140h | General<br>Purpose<br>Register<br>80 Bytes |      | General<br>Purpose<br>Register<br>80 Bytes |

| 06Fh |                                            | 0EFh |                                            | 16Fh         |                                            | 1EFh |                                            | 26Fh |                                            | 2EFh |                                            | 36Fh |                                            | 3EFh |                                            |

| 070h |                                            | 0F0h |                                            | 170h         |                                            | 1F0h |                                            | 270h |                                            | 2F0h |                                            | 370h |                                            | 3F0h |                                            |

|      | Common RAM<br>70h – 7Fh                    |      | Accesses<br>70h – 7Fh                      |              | Accesses<br>70h – 7Fh                      |      | Accesses<br>70h – 7Fh                      |      | Accesses<br>70h – 7Fh                      |      | Accesses<br>70h – 7Fh                      |      | Accesses<br>70h – 7Fh                      |      | Accesses<br>70h – 7Fh                      |

| 07Fh |                                            | 0FFh |                                            | 17Fh         |                                            | 1FFh |                                            | 27Fh |                                            | 2FFh |                                            | 37Fh |                                            | 3FFh |                                            |

Legend: = Unimplemented data memory locations, read as '0'.

Note 1: PIC16F1786 only.

## 13.4 Register Definitions: PORTA

## REGISTER 13-3: PORTA: PORTA REGISTER

| R/W-x/x          | R/W-x/x                                 | R/W-x/x           | R/W-x/x | R/W-x/x                            | R/W-x/x                                               | R/W-x/x | R/W-x/x |  |  |  |  |

|------------------|-----------------------------------------|-------------------|---------|------------------------------------|-------------------------------------------------------|---------|---------|--|--|--|--|

| RA7              | RA6                                     | RA5               | RA4     | RA3                                | RA2                                                   | RA1     | RA0     |  |  |  |  |

| bit 7            |                                         |                   |         |                                    |                                                       |         | bit 0   |  |  |  |  |

| Legend:          |                                         |                   |         |                                    |                                                       |         |         |  |  |  |  |

| R = Readable b   | bit                                     | W = Writable b    | oit     | U = Unimplemented bit, read as '0' |                                                       |         |         |  |  |  |  |

| u = Bit is uncha | u = Bit is unchanged x = Bit is unknown |                   |         |                                    | -n/n = Value at POR and BOR/Value at all other Resets |         |         |  |  |  |  |

| '1' = Bit is set |                                         | '0' = Bit is clea | red     |                                    |                                                       |         |         |  |  |  |  |

bit 7-0 RA<7:0>: PORTA I/O Value bits<sup>(1)</sup> 1 = Port pin is ≥ VIH 0 = Port pin is ≤ VIL

## REGISTER 13-4: TRISA: PORTA TRI-STATE REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| TRISA7  | TRISA6  | TRISA5  | TRISA4  | TRISA3  | TRISA2  | TRISA1  | TRISA0  |

| bit 7   | •       |         |         | •       |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

- TRISA<7:0>: PORTA Tri-State Control bits

- 1 = PORTA pin configured as an input (tri-stated)

0 = PORTA pin configured as an output

## REGISTER 13-5: LATA: PORTA DATA LATCH REGISTER

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

| LATA7   | LATA6   | LATA5   | LATA4   | LATA3   | LATA2   | LATA1   | LATA0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-4 LATA<7:0>: PORTA Output Latch Value bits<sup>(1)</sup>

**Note 1:** Writes to PORTA are actually written to corresponding LATA register. Reads from PORTA register is return of actual I/O pin values.

**Note 1:** Writes to PORTA are actually written to corresponding LATA register. Reads from PORTA register is return of actual I/O pin values.

# 13.8 Register Definitions: PORTC

## **REGISTER 13-19: PORTC: PORTC REGISTER**

| R/W-x/u                                 | R/W-x/u           | R/W-x/u                                  | R/W-x/u                                               | R/W-x/u                                                                   | R/W-x/u                                                                                                 | R/W-x/u                                                                                                                     |  |  |

|-----------------------------------------|-------------------|------------------------------------------|-------------------------------------------------------|---------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--|--|

| RC6                                     | RC5               | RC4                                      | RC3                                                   | RC2                                                                       | RC1                                                                                                     | RC0                                                                                                                         |  |  |

|                                         |                   |                                          |                                                       |                                                                           |                                                                                                         | bit 0                                                                                                                       |  |  |

|                                         |                   |                                          |                                                       |                                                                           |                                                                                                         |                                                                                                                             |  |  |

|                                         |                   |                                          |                                                       |                                                                           |                                                                                                         |                                                                                                                             |  |  |

| t                                       | W = Writable I    | oit                                      | U = Unimplemented bit, read as '0'                    |                                                                           |                                                                                                         |                                                                                                                             |  |  |

| u = Bit is unchanged x = Bit is unknown |                   |                                          | -n/n = Value at POR and BOR/Value at all other Resets |                                                                           |                                                                                                         |                                                                                                                             |  |  |

|                                         | '0' = Bit is clea | ared                                     |                                                       |                                                                           |                                                                                                         |                                                                                                                             |  |  |

|                                         | t                 | t W = Writable I<br>nged x = Bit is unkn | t W = Writable bit                                    | t W = Writable bit U = Unimpler<br>nged x = Bit is unknown -n/n = Value a | t W = Writable bit U = Unimplemented bit, read<br>aged x = Bit is unknown $-n/n = Value at POR and BOI$ | t W = Writable bit U = Unimplemented bit, read as '0'<br>nged x = Bit is unknown -n/n = Value at POR and BOR/Value at all o |  |  |

bit 7-0 RC<7:0>: PORTC General Purpose I/O Pin bits<sup>(1)</sup> 1 = Port pin is ≥ VIH 0 = Port pin is ≤ VIL

#### REGISTER 13-20: TRISC: PORTC TRI-STATE REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| TRISC7  | TRISC6  | TRISC5  | TRISC4  | TRISC3  | TRISC2  | TRISC1  | TRISC0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

**TRISC<7:0>:** PORTC Tri-State Control bits 1 = PORTC pin configured as an input (tri-stated)

0 = PORTC pin configured as an output

#### REGISTER 13-21: LATC: PORTC DATA LATCH REGISTER

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

| LATC7   | LATC6   | LATC5   | LATC4   | LATC3   | LATC2   | LATC1   | LATC0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

### bit 7-0 LATC<7:0>: PORTC Output Latch Value bits<sup>(1)</sup>

**Note 1:** Writes to PORTC are actually written to corresponding LATC register. Reads from PORTC register is return of actual I/O pin values.

**Note 1:** Writes to PORTC are actually written to corresponding LATC register. Reads from PORTC register is return of actual I/O pin values.

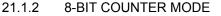

# 21.0 TIMER0 MODULE

The Timer0 module is an 8-bit timer/counter with the following features:

- 8-bit timer/counter register (TMR0)

- 8-bit prescaler (independent of Watchdog Timer)

- Programmable internal or external clock source

- Programmable external clock edge selection

- · Interrupt on overflow

- TMR0 can be used to gate Timer1

Figure 21-1 is a block diagram of the Timer0 module.

## 21.1 Timer0 Operation

The Timer0 module can be used as either an 8-bit timer or an 8-bit counter.

#### 21.1.1 8-BIT TIMER MODE

The Timer0 module will increment every instruction cycle, if used without a prescaler. 8-bit Timer mode is selected by clearing the TMR0CS bit of the OPTION\_REG register.

When TMR0 is written, the increment is inhibited for two instruction cycles immediately following the write.

**Note:** The value written to the TMR0 register can be adjusted, in order to account for the two instruction cycle delay when TMR0 is written.

## FIGURE 21-1: BLOCK DIAGRAM OF THE TIMER0

In 8-Bit Counter mode, the Timer0 module will increment on every rising or falling edge of the T0CKI pin.

8-Bit Counter mode using the T0CKI pin is selected by setting the TMR0CS bit in the OPTION\_REG register to '1'.

The rising or falling transition of the incrementing edge for either input source is determined by the TMR0SE bit in the OPTION\_REG register.

## 24.4 Dead-Band Control

The dead-band control provides non-overlapping PWM signals to prevent shoot-through current in series connected power switches. Dead-band control is available only in modes with complementary drive and when changing direction in the ECCP compatible Full-Bridge modes.

The module contains independent 8-bit dead-band counters for rising edge and falling edge dead-band control.

#### 24.4.1 DEAD-BAND TYPES

There are two separate dead-band generators available, one for rising edge events and the other for falling edge events.

#### 24.4.1.1 Rising Edge Dead Band

Rising edge dead-band control is used to delay the turn-on of the primary switch driver from when the complementary switch driver is turned off.

Rising edge dead band is initiated with the rising edge event.

Rising edge dead-band time is adjusted with the PSMC Rising Edge Dead-Band Time (PSMCxDBR) register (Register 24-26).

If the PSMCxDBR register value is changed when the PSMC is enabled, the new value does not take effect until the first period event after the PSMCxLD bit is set.

#### 24.4.1.2 Falling Edge Dead Band

Falling edge dead-band control is used to delay the turn-on of the complementary switch driver from when the primary switch driver is turned off.

Falling edge dead band is initiated with the falling edge event.

Falling edge dead-band time is adjusted with the PSMC Falling Edge Dead-Band Time (PSMCxDBF) register (Register 24-27).

If the PSMCxDBF register value is changed when the PSMC is enabled, the new value does not take effect until the first period event after the PSMCxLD bit is set.

#### 24.4.2 DEAD-BAND ENABLE

When a mode is selected that may use dead-band control, dead-band timing is enabled by setting one of the enable bits in the PSMC Control (PSMCxCON) register (Register 24-1).

Rising edge dead band is enabled with the PxDBRE bit.

Rising edge dead band is enabled with the PxDBFE bit.

Enable changes take effect immediately.

## 24.4.3 DEAD-BAND CLOCK SOURCE

The dead-band counters are incremented on every rising edge of the psmc\_clk signal.

#### 24.4.4 DEAD-BAND UNCERTAINTY

When the rising and falling edge events that trigger the dead-band counters come from asynchronous inputs, there will be uncertainty in the actual dead-band time of each cycle. The maximum uncertainty is equal to one psmc\_clk period. The one clock of uncertainty may still be introduced, even when the dead-band count time is cleared to zero.

#### 24.4.5 DEAD-BAND OVERLAP

There are two cases of dead-band overlap and each is treated differently due to system requirements.

#### 24.4.5.1 Rising to Falling Overlap

In this case, the falling edge event occurs while the rising edge dead-band counter is still counting. The following sequence occurs:

- 1. Dead-band rising count is terminated.

- 2. Dead-band falling count is initiated.

- 3. Primary output is suppressed.

#### 24.4.5.2 Falling to Rising Overlap

In this case, the rising edge event occurs while the falling edge dead-band counter is still counting. The following sequence occurs:

- 1. Dead-band falling count is terminated.

- 2. Dead-band rising count is initiated.

- 3. Complementary output is suppressed.

#### 24.4.5.3 Rising Edge-to-Rising Edge or Falling Edge-to-Falling Edge

In cases where one of the two dead-band counters is set for a short period, or disabled all together, it is possible to get rising-to-rising or falling-to-falling overlap. When this is the case, the following sequence occurs:

- 1. Dead-band count is terminated.

- 2. Dead-band count is restarted.

- 3. Output waveform control freezes in the present state.

- 4. Restarted dead-band count completes.

- 5. Output control resumes normally.

| U-0                                                                  | U-0                          | R/W-0/0          | R/W-0/0      | U-0            | U-0              | R/W-0/0          | R/W-0/0      |  |  |  |

|----------------------------------------------------------------------|------------------------------|------------------|--------------|----------------|------------------|------------------|--------------|--|--|--|

|                                                                      | —                            | PxCPRE<1:0>      |              | —              | —                | PxCSR            | C<1:0>       |  |  |  |

| bit 7                                                                |                              |                  |              |                |                  |                  | bit 0        |  |  |  |

|                                                                      |                              |                  |              |                |                  |                  |              |  |  |  |

| Legend:                                                              |                              |                  |              |                |                  |                  |              |  |  |  |

| R = Readable                                                         | e bit                        | W = Writable     | bit          | U = Unimpler   | mented bit, read | as '0'           |              |  |  |  |

| u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/ |                              |                  |              |                |                  | R/Value at all c | other Resets |  |  |  |

| '1' = Bit is set                                                     | t                            | '0' = Bit is cle | ared         |                |                  |                  |              |  |  |  |

|                                                                      |                              |                  |              |                |                  |                  |              |  |  |  |

| bit 7-6                                                              | Unimplemen                   | ted: Read as '   | 0'           |                |                  |                  |              |  |  |  |

| bit 5-4                                                              | PxCPRE<1:0                   | >: PSMCx Clo     | ck Prescaler | Selection bits |                  |                  |              |  |  |  |

|                                                                      | 11 = PSMCx                   | Clock frequen    | cy/8         |                |                  |                  |              |  |  |  |

|                                                                      | 10 = PSMCx Clock frequency/4 |                  |              |                |                  |                  |              |  |  |  |

|                                                                      | 01 = PSMCx Clock frequency/2 |                  |              |                |                  |                  |              |  |  |  |

|                                                                      | 00 = PSMCx Clock frequency/1 |                  |              |                |                  |                  |              |  |  |  |

| bit 3-2                                                              | Unimplemen                   | ted: Read as '   | 0'           |                |                  |                  |              |  |  |  |

## REGISTER 24-6: PSMCxCLK: PSMC CLOCK CONTROL REGISTER

bit 1-0 **PxCSRC<1:0>:** PSMCx Clock Source Selection bits

- 11 = Reserved

- 10 = PSMCxCLK pin

- 01 = 64 MHz clock in from PLL

- 00 = Fosc system clock

## REGISTER 24-7: PSMCxOEN: PSMC OUTPUT ENABLE CONTROL REGISTER

| U-0   | U-0 | R/W-0/0              | R/W-0/0              | R/W-0/0              | R/W-0/0              | R/W-0/0 | R/W-0/0 |

|-------|-----|----------------------|----------------------|----------------------|----------------------|---------|---------|

| —     | —   | PxOEF <sup>(1)</sup> | PxOEE <sup>(1)</sup> | PxOED <sup>(1)</sup> | PxOEC <sup>(1)</sup> | PxOEB   | PxOEA   |

| bit 7 |     |                      |                      |                      |                      |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **PxOEy:** PSMCx Output y Enable bit<sup>(1)</sup>

1 = PWM output is active on PSMCx output y pin

0 = PWM output is not active, normal port functions in control of pin

**Note 1:** These bits are not implemented on PSMC2.

| R/W-0/0                                                                                                                              | U-0                                                               | U-0                                                                                                                                       | R/W-0/0        | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0     |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------|------------------|------------------|-------------|--|--|--|

| PxPHSIN                                                                                                                              | —                                                                 | —                                                                                                                                         | PxPHSC4        | PxPHSC3        | PxPHSC2          | PxPHSC1          | PxPHST      |  |  |  |

| bit 7                                                                                                                                |                                                                   |                                                                                                                                           |                |                |                  |                  | bit (       |  |  |  |

|                                                                                                                                      |                                                                   |                                                                                                                                           |                |                |                  |                  |             |  |  |  |

| Legend:                                                                                                                              |                                                                   |                                                                                                                                           |                |                |                  | (2)              |             |  |  |  |

| R = Readable                                                                                                                         |                                                                   | W = Writable                                                                                                                              |                | •              | mented bit, read |                  |             |  |  |  |

| u = Bit is uncl                                                                                                                      | •                                                                 | x = Bit is unki                                                                                                                           |                | -n/n = Value a | at POR and BO    | R/Value at all o | ther Resets |  |  |  |

| '1' = Bit is set                                                                                                                     |                                                                   | '0' = Bit is cle                                                                                                                          | ared           |                |                  |                  |             |  |  |  |

| bit 7                                                                                                                                |                                                                   | MCx Rising F                                                                                                                              | dae Event occ  | urs on PSMCx   | /IN nin          |                  |             |  |  |  |

| bit i                                                                                                                                |                                                                   | •                                                                                                                                         | •              |                |                  |                  |             |  |  |  |

|                                                                                                                                      | 0                                                                 | <ul> <li>1 = Rising edge event will occur when PSMCxIN pin goes true</li> <li>0 = PSMCxIN pin will not cause rising edge event</li> </ul> |                |                |                  |                  |             |  |  |  |

| bit 6-5                                                                                                                              | Unimplemen                                                        | Unimplemented: Read as '0'                                                                                                                |                |                |                  |                  |             |  |  |  |

| bit 4                                                                                                                                | PxPHSC4: P                                                        | SMCx Rising E                                                                                                                             | dge Event oco  | curs on sync_C | C4OUT output     |                  |             |  |  |  |

|                                                                                                                                      | 0                                                                 | <b>Q</b>                                                                                                                                  |                |                | itput goes true  |                  |             |  |  |  |

|                                                                                                                                      |                                                                   | 40UT will not o                                                                                                                           | •              | •              |                  |                  |             |  |  |  |

| bit 3                                                                                                                                |                                                                   | -                                                                                                                                         | -              | curs on sync_C |                  |                  |             |  |  |  |

|                                                                                                                                      | 0                                                                 | dge event will<br>30UT will not c                                                                                                         |                |                | itput goes true  |                  |             |  |  |  |

| bit 2                                                                                                                                |                                                                   |                                                                                                                                           | •              | curs on sync ( |                  |                  |             |  |  |  |

|                                                                                                                                      |                                                                   | •                                                                                                                                         | •              |                | itput goes true  |                  |             |  |  |  |

|                                                                                                                                      | 0                                                                 | 20UT will not o                                                                                                                           |                | _              | ilput good li uo |                  |             |  |  |  |

| bit 1                                                                                                                                | PxPHSC1: P                                                        | SMCx Rising E                                                                                                                             | Edge Event oco | curs on sync C | C1OUT output     |                  |             |  |  |  |

|                                                                                                                                      | 1 = Rising edge event will occur when sync_C1OUT output goes true |                                                                                                                                           |                |                |                  |                  |             |  |  |  |

|                                                                                                                                      | 0 = sync_C                                                        | 10UT will not o                                                                                                                           | ause rising ed | lge event      |                  |                  |             |  |  |  |

| bit 0                                                                                                                                | PxPHST: PSI                                                       | MCx Rising Ed                                                                                                                             | ge Event occu  | irs on Time Ba | se match         |                  |             |  |  |  |

| <ul> <li>1 = Rising edge event will occur when PSMCxTMR = PSMCxPH</li> <li>0 = Time base will not cause rising edge event</li> </ul> |                                                                   |                                                                                                                                           |                |                |                  |                  |             |  |  |  |

|                                                                                                                                      | 0 = Time ba                                                       | se will not cau                                                                                                                           | se rising edge | event          |                  |                  |             |  |  |  |

# **REGISTER 24-12: PSMCxPHS: PSMC PHASE SOURCE REGISTER**<sup>(1)</sup>

Note 1: Sources are not mutually exclusive: more than one source can cause a rising edge event.

# 25.4 Register Definitions: CCP Control

# REGISTER 25-1: CCPxCON: CCPx CONTROL REGISTER

| U-0                | U-0                                                                                                                                  | R/W-0/0                 | R/W-0/0         | R/W-0/0           | R/W-0/0          | R/W-0/0        | R/W-0/0     |  |  |  |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-----------------|-------------------|------------------|----------------|-------------|--|--|--|

| _                  | _                                                                                                                                    | DCxB                    | <1:0>           |                   | CCPxN            | /<3:0>         |             |  |  |  |

| bit 7              |                                                                                                                                      |                         |                 |                   |                  |                | bit 0       |  |  |  |

|                    |                                                                                                                                      |                         |                 |                   |                  |                |             |  |  |  |

| Legend:            |                                                                                                                                      |                         |                 |                   |                  |                |             |  |  |  |

| R = Readable       |                                                                                                                                      | W = Writable            |                 |                   | nented bit, read |                |             |  |  |  |

| u = Bit is unch    | -                                                                                                                                    | x = Bit is unkr         |                 | -n/n = Value a    | t POR and BO     | R/Value at all | other Reset |  |  |  |

| '1' = Bit is set   |                                                                                                                                      | '0' = Bit is clea       | ared            |                   |                  |                |             |  |  |  |

| bit 7-6            | Unimplomo                                                                                                                            | ntod. Dood oo '         | o'              |                   |                  |                |             |  |  |  |

| bit 7-0<br>bit 5-4 | Unimplemented: Read as '0'<br>DCxB<1:0>: PWM Duty Cycle Least Significant bits                                                       |                         |                 |                   |                  |                |             |  |  |  |

| DIL 5-4            | Capture mo                                                                                                                           |                         | cie Least Sign  |                   |                  |                |             |  |  |  |

|                    | Unused                                                                                                                               | <u>ue.</u>              |                 |                   |                  |                |             |  |  |  |

|                    | Compare me                                                                                                                           | ode:                    |                 |                   |                  |                |             |  |  |  |

|                    | Unused                                                                                                                               |                         |                 |                   |                  |                |             |  |  |  |

|                    | PWM mode:                                                                                                                            |                         |                 |                   |                  |                |             |  |  |  |

|                    |                                                                                                                                      | ire the two LSbs        |                 | luty cycle. The e | eight MSbs are   | found in CCP   | RxL.        |  |  |  |

| bit 3-0            | CCPxM<3:0<br>11xx = PWI                                                                                                              | <b>)&gt;:</b> CCPx Mode | Select bits     |                   |                  |                |             |  |  |  |

|                    |                                                                                                                                      | WI MODE                 |                 |                   |                  |                |             |  |  |  |

|                    | 1011 = Compare mode: Auto-conversion Trigger (sets CCPxIF bit (CCP2), starts ADC conversion if ADC module is enabled) <sup>(1)</sup> |                         |                 |                   |                  |                |             |  |  |  |

|                    |                                                                                                                                      | npare mode: ger         |                 | e interrupt only  |                  |                |             |  |  |  |

|                    |                                                                                                                                      | npare mode: clea        |                 |                   |                  |                |             |  |  |  |

|                    | 1000 <b>= Con</b>                                                                                                                    | npare mode: set         | output on con   | npare match (se   | et CCPxIF)       |                |             |  |  |  |

|                    | 0111 = Capture mode: every 16th rising edge                                                                                          |                         |                 |                   |                  |                |             |  |  |  |

|                    | 0110 = Cap                                                                                                                           | ture mode: ever         | y 4th rising ed |                   |                  |                |             |  |  |  |

|                    |                                                                                                                                      | ture mode: ever         |                 |                   |                  |                |             |  |  |  |

|                    | 0100 <b>= Cap</b>                                                                                                                    | ture mode: ever         | y falling edge  |                   |                  |                |             |  |  |  |

|                    | 0011 = Res                                                                                                                           | erved                   |                 |                   |                  |                |             |  |  |  |

|                    |                                                                                                                                      | npare mode: tog         | gle output on i | match             |                  |                |             |  |  |  |

|                    | 0001 = Res                                                                                                                           |                         |                 |                   |                  |                |             |  |  |  |

|                    | 0000 <b>= Cap</b>                                                                                                                    | oture/Compare/P         | WM off (resets  | s CCPx module     | )                |                |             |  |  |  |

|                    |                                                                                                                                      |                         |                 |                   |                  |                |             |  |  |  |

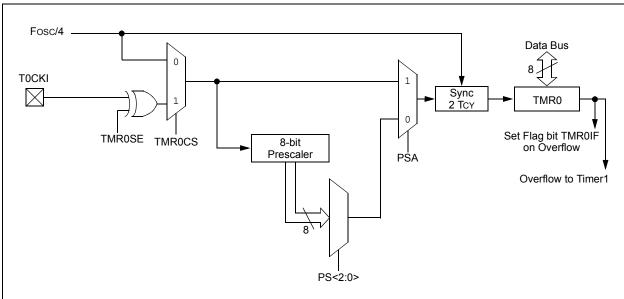

# 26.4 I<sup>2</sup>C MODE OPERATION

All MSSP I<sup>2</sup>C communication is byte oriented and shifted out MSb first. Six SFR registers and two interrupt flags interface the module with the PIC<sup>®</sup> microcontroller and user software. Two pins, SDA and SCL, are exercised by the module to communicate with other external I<sup>2</sup>C devices.

#### 26.4.1 BYTE FORMAT

All communication in  $I^2C$  is done in 9-bit segments. A byte is sent from a master to a slave or vice-versa, followed by an Acknowledge bit sent back. After the 8th falling edge of the SCL line, the device outputting data on the SDA changes that pin to an input and reads in an acknowledge value on the next clock pulse.

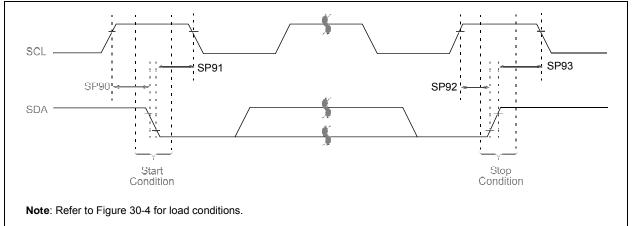

The clock signal, SCL, is provided by the master. Data is valid to change while the SCL signal is low, and sampled on the rising edge of the clock. Changes on the SDA line while the SCL line is high define special conditions on the bus, explained below.

#### 26.4.2 DEFINITION OF I<sup>2</sup>C TERMINOLOGY

There is language and terminology in the description of  $I^2C$  communication that have definitions specific to  $I^2C$ . That word usage is defined below and may be used in the rest of this document without explanation. This table was adapted from the Philips  $I^2C$  specification.

#### 26.4.3 SDA AND SCL PINS

Selection of any  $l^2C$  mode with the SSPEN bit set, forces the SCL and SDA pins to be open-drain. These pins should be set by the user to inputs by setting the appropriate TRIS bits.

Note: Data is tied to output zero when an I<sup>2</sup>C mode is enabled.

#### 26.4.4 SDA HOLD TIME

The hold time of the SDA pin is selected by the SDAHT bit of the SSPCON3 register. Hold time is the time SDA is held valid after the falling edge of SCL. Setting the SDAHT bit selects a longer 300 ns minimum hold time and may help on buses with large capacitance.

## TABLE 26-2:I<sup>2</sup>C BUS TERMS

| TADLE 20-2.         |                                                                                                                                                                                       |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TERM                | Description                                                                                                                                                                           |

| Transmitter         | The device which shifts data out onto the bus.                                                                                                                                        |

| Receiver            | The device which shifts data in from the bus.                                                                                                                                         |

| Master              | The device that initiates a transfer, generates clock signals and terminates a transfer.                                                                                              |

| Slave               | The device addressed by the master.                                                                                                                                                   |

| Multi-master        | A bus with more than one device that can initiate data transfers.                                                                                                                     |

| Arbitration         | Procedure to ensure that only one master at a time controls the bus. Winning arbitration ensures that the message is not corrupted.                                                   |

| Synchronization     | Procedure to synchronize the clocks of two or more devices on the bus.                                                                                                                |

| Idle                | No master is controlling the bus,<br>and both SDA and SCL lines are<br>high.                                                                                                          |

| Active              | Any time one or more master devices are controlling the bus.                                                                                                                          |

| Addressed<br>Slave  | Slave device that has received a matching address and is actively being clocked by a master.                                                                                          |

| Matching<br>Address | Address byte that is clocked into a slave that matches the value stored in SSPADD.                                                                                                    |

| Write Request       | Slave receives a matching address with R/W bit clear, and is ready to clock in data.                                                                                                  |

| Read Request        | Master sends an address byte with the $R/W$ bit set, indicating that it wishes to clock data out of the Slave. This data is the next and all following bytes until a Restart or Stop. |

| Clock Stretching    | When a device on the bus hold SCL low to stall communication.                                                                                                                         |

| Bus Collision       | Any time the SDA line is sampled<br>low by the module while it is out-<br>putting and expected high state.                                                                            |

# PIC16(L)F1784/6/7

# 26.6 I<sup>2</sup>C Master Mode

Master mode is enabled by setting and clearing the appropriate SSPM bits in the SSPCON1 register and by setting the SSPEN bit. In Master mode, the SDA and SCK pins must be configured as inputs. The MSSP peripheral hardware will override the output driver TRIS controls when necessary to drive the pins low.

Master mode of operation is supported by interrupt generation on the detection of the Start and Stop conditions. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the  $I^2C$  bus may be taken when the P bit is set, or the bus is Idle.

In Firmware Controlled Master mode, user code conducts all I<sup>2</sup>C bus operations based on Start and Stop bit condition detection. Start and Stop condition detection is the only active circuitry in this mode. All other communication is done by the user software directly manipulating the SDA and SCL lines.

The following events will cause the SSP Interrupt Flag bit, SSP1IF, to be set (SSP interrupt, if enabled):

- Start condition detected

- · Stop condition detected

- Data transfer byte transmitted/received

- Acknowledge transmitted/received

- Repeated Start generated

- Note 1: The MSSP module, when configured in I<sup>2</sup>C Master mode, does not allow queueing of events. For instance, the user is not allowed to initiate a Start condition and immediately write the SSPBUF register to initiate transmission before the Start condition is complete. In this case, the SSPBUF will not be written to and the WCOL bit will be set, indicating that a write to the SSPBUF did not occur

- 2: When in Master mode, Start/Stop detection is masked and an interrupt is generated when the SEN/PEN bit is cleared and the generation is complete.

#### 26.6.1 I<sup>2</sup>C MASTER MODE OPERATION

The master device generates all of the serial clock pulses and the Start and Stop conditions. A transfer is ended with a Stop condition or with a Repeated Start condition. Since the Repeated Start condition is also the beginning of the next serial transfer, the I<sup>2</sup>C bus will not be released.

In Master Transmitter mode, serial data is output through SDA, while SCL outputs the serial clock. The first byte transmitted contains the slave address of the receiving device (7 bits) and the Read/Write (R/W) bit. In this case, the R/W bit will be logic '0'. Serial data is transmitted 8 bits at a time. After each byte is transmitted, an Acknowledge bit is received. Start and Stop conditions are output to indicate the beginning and the end of a serial transfer.

In Master Receive mode, the first byte transmitted contains the slave address of the transmitting device (7 bits) and the R/W bit. In this case, the R/W bit will be logic '1'. Thus, the first byte transmitted is a 7-bit slave address followed by a '1' to indicate the receive bit. Serial data is received via SDA, while SCL outputs the serial clock. Serial data is received 8 bits at a time. After each byte is received, an Acknowledge bit is transmitted. Start and Stop conditions indicate the beginning and end of transmission.

A Baud Rate Generator is used to set the clock frequency output on SCL. See **Section 26.7 "Baud Rate Generator"** for more detail.

#### 26.6.2 CLOCK ARBITRATION

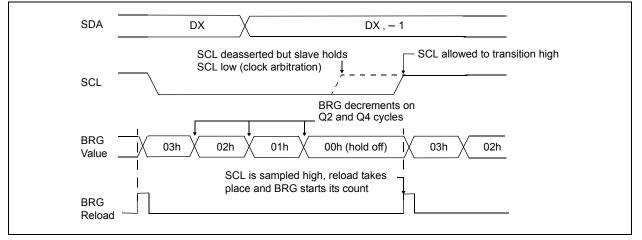

Clock arbitration occurs when the master, during any receive, transmit or Repeated Start/Stop condition, releases the SCL pin (SCL allowed to float high). When the SCL pin is allowed to float high, the Baud Rate Generator (BRG) is suspended from counting until the SCL pin is actually sampled high. When the SCL pin is sampled high, the Baud Rate Generator is reloaded with the contents of SSPADD<7:0> and begins counting. This ensures that the SCL high time will always be at least one BRG rollover count in the event that the clock is held low by an external device (Figure 26-25).

#### FIGURE 26-25: BAUD RATE GENERATOR TIMING WITH CLOCK ARBITRATION

#### 26.6.3 WCOL STATUS FLAG

If the user writes the SSPBUF when a Start, Restart, Stop, Receive or Transmit sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write does not occur). Any time the WCOL bit is set it indicates that an action on SSPBUF was attempted while the module was not idle.

| Note: | Because queueing of events is not       |

|-------|-----------------------------------------|

|       | allowed, writing to the lower 5 bits of |

|       | SSPCON2 is disabled until the Start     |

|       | condition is complete.                  |

|        |                  |            |                             |                | SYNC       | <b>C</b> = 0, BRGH          | l = 1, BRC     | <b>616 =</b> 0 |                             |                  |            |                             |

|--------|------------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|----------------|-----------------------------|------------------|------------|-----------------------------|

| BAUD   | Fosc = 8.000 MHz |            | ) MHz                       | Fos            | c = 4.000  | ) MHz                       | Fosc           | : = 3.686      | 4 MHz                       | Fosc = 1.000 MHz |            |                             |

| RATE   | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error     | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | —                | _          | _                           |                | _          |                             | _              | _              | _                           | 300              | 0.16       | 207                         |

| 1200   | —                | —          | —                           | 1202           | 0.16       | 207                         | 1200           | 0.00           | 191                         | 1202             | 0.16       | 51                          |

| 2400   | 2404             | 0.16       | 207                         | 2404           | 0.16       | 103                         | 2400           | 0.00           | 95                          | 2404             | 0.16       | 25                          |

| 9600   | 9615             | 0.16       | 51                          | 9615           | 0.16       | 25                          | 9600           | 0.00           | 23                          | _                | _          | _                           |

| 10417  | 10417            | 0.00       | 47                          | 10417          | 0.00       | 23                          | 10473          | 0.53           | 21                          | 10417            | 0.00       | 5                           |

| 19.2k  | 19231            | 0.16       | 25                          | 19.23k         | 0.16       | 12                          | 19.2k          | 0.00           | 11                          | _                | _          | _                           |

| 57.6k  | 55556            | -3.55      | 8                           | —              | _          | _                           | 57.60k         | 0.00           | 3                           | —                | _          | _                           |

| 115.2k | —                | _          | —                           |                | _          | _                           | 115.2k         | 0.00           | 1                           | _                | _          | —                           |

# TABLE 27-5: BAUD RATES FOR ASYNCHRONOUS MODES (CONTINUED)

|        |                | SYNC = 0, BRGH = 0, BRG16 = 1                        |                             |                |            |                             |                |            |                             |                |            |                             |

|--------|----------------|------------------------------------------------------|-----------------------------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|

| BAUD   | Fosc           | Fosc = 32.000 MHz Fosc = 20.000 MHz Fosc = 18.432 MI |                             |                |            | 2 MHz                       | Fosc           | = 11.059   | 92 MHz                      |                |            |                             |

| RATE   | Actual<br>Rate | %<br>Error                                           | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) |