Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PSMC, PWM, WDT                               |

| Number of I/O              | 35                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 1K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 14x12b; D/A 1x8b                                                      |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-VQFN Exposed Pad                                                       |

| Supplier Device Package    | 44-QFN (8x8)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1787-e-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 7.5 Register Definition: Reference Clock Control

# REGISTER 7-1: CLKRCON: REFERENCE CLOCK CONTROL REGISTER

| R/W-0/0                                     | R/W-0/0                                                                                                | R/W-1/1                                                        | R/W-1/1         | R/W-0/0          | R/W-0/0          | R/W-0/0        | R/W-0/0       |

|---------------------------------------------|--------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|-----------------|------------------|------------------|----------------|---------------|

| CLKREN                                      | CLKROE                                                                                                 | CLKRSLR                                                        | CLKRE           | DC<1:0>          | (                | CLKRDIV<2:0>   | >             |

| bit 7                                       |                                                                                                        |                                                                |                 |                  |                  |                | bit 0         |

|                                             |                                                                                                        |                                                                |                 |                  |                  |                |               |

| Legend:                                     |                                                                                                        |                                                                |                 |                  |                  |                |               |

| R = Readable                                |                                                                                                        | W = Writable                                                   |                 | •                | mented bit, read |                |               |

| u = Bit is unc                              | •                                                                                                      | x = Bit is unkr                                                |                 | -n/n = Value a   | at POR and BC    | R/Value at all | other Resets  |

| '1' = Bit is set                            | t                                                                                                      | '0' = Bit is clea                                              | ared            |                  |                  |                |               |

| bit 7                                       | <b>CLKREN:</b> Re                                                                                      | eference Clock                                                 | Module Enabl    | e bit            |                  |                |               |

|                                             | 1 = Referen                                                                                            | ce clock module                                                | e is enabled    |                  |                  |                |               |

|                                             | 0 = Referen                                                                                            | ce clock module                                                | e is disabled   |                  |                  |                |               |

| bit 6                                       | CLKROE: R                                                                                              | eference Clock                                                 | Output Enable   | e bit            |                  |                |               |

|                                             | 1 = Reference clock output is enabled on CLKR pin                                                      |                                                                |                 |                  |                  |                |               |

|                                             | 0 = Reference clock output disabled on CLKR pin                                                        |                                                                |                 |                  |                  |                |               |

| bit 5                                       | CLKRSLR:                                                                                               | CLKRSLR: Reference Clock Slew Rate Control Limiting Enable bit |                 |                  |                  |                |               |

|                                             | <ul> <li>1 = Slew rate limiting is enabled</li> <li>0 = Slew rate limiting is disabled</li> </ul>      |                                                                |                 |                  |                  |                |               |

|                                             |                                                                                                        | •                                                              |                 |                  |                  |                |               |

| bit 4-3                                     |                                                                                                        | 0>: Reference                                                  |                 | cle bits         |                  |                |               |

|                                             | 11 = Clock outputs duty cycle of $75\%$                                                                |                                                                |                 |                  |                  |                |               |

|                                             | <ul> <li>10 = Clock outputs duty cycle of 50%</li> <li>01 = Clock outputs duty cycle of 25%</li> </ul> |                                                                |                 |                  |                  |                |               |

|                                             |                                                                                                        | outputs duty cyc                                               |                 |                  |                  |                |               |

| bit 2-0                                     | CLKRDIV<2                                                                                              | :0> Reference (                                                | Clock Divider b | oits             |                  |                |               |

|                                             | 111 = Base clock value divided by 128                                                                  |                                                                |                 |                  |                  |                |               |

|                                             | 110 = Base clock value divided by 64                                                                   |                                                                |                 |                  |                  |                |               |

|                                             | 101 = Base clock value divided by 32<br>100 = Base clock value divided by 16                           |                                                                |                 |                  |                  |                |               |

|                                             |                                                                                                        | clock value divi                                               |                 |                  |                  |                |               |

| 010 = Base clock value divided by 4         |                                                                                                        |                                                                |                 |                  |                  |                |               |

| 001 = Base clock value divided by $2^{(1)}$ |                                                                                                        |                                                                |                 |                  |                  |                |               |

|                                             |                                                                                                        | clock value <sup>(2)</sup>                                     | -               |                  |                  |                |               |

| Note 1: In                                  | this mode. the                                                                                         | 25% and 75% (                                                  | dutv cvcle acc  | uracv will be de | ependent on the  | e source clock | dutv cvcle.   |

|                                             | ,                                                                                                      |                                                                | , .,            | .,               |                  |                | · · · · · · · |

- 2: In this mode, the duty cycle will always be equal to the source clock duty cycle, unless a duty cycle of 0% is selected.

- **3:** To route CLKR to pin, CLKOUTEN of Configuration Words = 1 is required. CLKOUTEN of Configuration Words = 0 will result in Fosc/4. See Section 7.3 "Conflicts with the CLKR Pin" for details.

# REGISTER 13-36: LATE: PORTE DATA LATCH REGISTER<sup>(2)</sup>

| U-0     | U-0 | U-0 | U-0 | U-0 | R/W-x/u | R/W-x/u | R/W-x/u |

|---------|-----|-----|-----|-----|---------|---------|---------|

| —       | _   | _   | —   | _   | LATE2   | LATE1   | LATE0   |

| bit 7   |     |     |     |     |         |         | bit 0   |

|         |     |     |     |     |         |         |         |

| Legend: |     |     |     |     |         |         |         |

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

|----------------------|----------------------|-------------------------------------------------------|

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-3 Unimplemented: Read as '0'

bit 2-0 LATE<2:0>: PORTE Output Latch Value bits<sup>(2)</sup>

- **Note 1:** Writes to PORTE are actually written to corresponding LATE register. Reads from PORTE register is return of actual I/O pin values.

- 2: LATE<2:0> are available on PIC16(L)F1784/7 only.

# REGISTER 13-37: ANSELE: PORTE ANALOG SELECT REGISTER<sup>(2)</sup>

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|-------|-----|-----|-----|-----|---------|---------|---------|

| —     | —   | —   | —   | —   | ANSE2   | ANSE1   | ANSE0   |

| bit 7 |     |     |     |     |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

- bit 2-0 **ANSE<2:0>**: Analog Select between Analog or Digital Function on pins RE<2:0>, respectively

- 0 = Digital I/O. Pin is assigned to port or digital special function.

- 1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.

- **Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

- 2: ANSELE<2:0> are available on PIC16(L)F1784/7 only.

#### 17.4 **ADC Acquisition Requirements**

For the ADC to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The Analog Input model is shown in Figure 17-4. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), refer to Figure 17-4. The maximum recommended impedance for analog sources is 10 k $\Omega$ . As the

source impedance is decreased, the acquisition time may be decreased. After the analog input channel is selected (or changed), an ADC acquisition must be done before the conversion can be started. To calculate the minimum acquisition time, Equation 17-1 may be used. This equation assumes that 1/2 LSb error is used (4,096 steps for the ADC). The 1/2 LSb error is the maximum error allowed for the ADC to meet its specified resolution.

#### EQUATION 17-1: ACQUISITION TIME EXAMPLE

Assumptions: Temperature =

$$50^{\circ}C$$

and external impedance of  $10k\Omega 5.0V$  VDD

$TACQ = Amplifier Settling Time + Hold Capacitor Charging Time + Temperature Coefficient$

$= TAMP + TC + TCOFF$

$= 2\mu s + TC + [(Temperature - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$

The value for TC can be approximated with the following equations:

$$V_{APPLIED}\left(1 - \frac{1}{(2^{n+1}) - 1}\right) = V_{CHOLD} ; [1] V_{CHOLD} charged to within 1/2 lsb$$

$$V_{APPLIED}\left(1 - e^{\frac{-Tc}{RC}}\right) = V_{CHOLD} ; [2] V_{CHOLD} charge response to V_{APPLIED} V_{APPLIED}\left(1 - e^{\frac{-Tc}{RC}}\right) = V_{APPLIED}\left(1 - \frac{1}{(2^{n+1}) - 1}\right) ; combining [1] and [2]$$

Note: Where n = number of bits of the ADC.

Solving for TC:

ł

$$Tc = -C_{HOLD}(RIC + RSS + RS) \ln(1/8191)$$

= -10pF(1k\Omega + 7k\Omega + 10k\Omega) \ln(0.000122)

= 1.62\mus

Therefore:

$$TACQ = 2\mu s + 1.62\mu s + [(50^{\circ}C - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$$

= 4.87\mu s

Note 1: The reference voltage (VREF) has no effect on the equation, since it cancels itself out.

2: Maximum source impedance feeding the input pin should be considered so that the pin leakage does not cause a voltage divider, thereby limiting the absolute accuracy.

# 22.1 Timer1 Operation

The Timer1 module is a 16-bit incrementing counter which is accessed through the TMR1H:TMR1L register pair. Writes to TMR1H or TMR1L directly update the counter.

When used with an internal clock source, the module is a timer and increments on every instruction cycle. When used with an external clock source, the module can be used as either a timer or counter and increments on every selected edge of the external source.

Timer1 is enabled by configuring the TMR1ON and TMR1GE bits in the T1CON and T1GCON registers, respectively. Table 22-1 displays the Timer1 enable selections.

| TABLE 22-1: | TIMER1 ENABLE |

|-------------|---------------|

|             | SELECTIONS    |

| TMR10N | TMR1GE | Timer1<br>Operation |

|--------|--------|---------------------|

| 0      | 0      | Off                 |

| 0      | 1      | Off                 |

| 1      | 0      | Always On           |

| 1      | 1      | Count Enabled       |

# 22.2 Clock Source Selection

The TMR1CS<1:0> and T1OSCEN bits of the T1CON register are used to select the clock source for Timer1. Table 22-2 displays the clock source selections.

#### 22.2.1 INTERNAL CLOCK SOURCE

When the internal clock source is selected, the TMR1H:TMR1L register pair will increment on multiples of Fosc as determined by the Timer1 prescaler.

When the Fosc internal clock source is selected, the Timer1 register value will increment by four counts every instruction clock cycle. Due to this condition, a 2 LSB error in resolution will occur when reading the Timer1 value. To utilize the full resolution of Timer1, an asynchronous input signal must be used to gate the Timer1 clock input.

The following asynchronous sources may be used:

- Asynchronous event on the T1G pin to Timer1 gate

- C1 or C2 comparator input to Timer1 gate

#### 22.2.2 EXTERNAL CLOCK SOURCE

When the external clock source is selected, the Timer1 module may work as a timer or a counter.

When enabled to count, Timer1 is incremented on the rising edge of the external clock input T1CKI, which can be synchronized to the microcontroller system clock or can run asynchronously.

When used as a timer with a clock oscillator, an external 32.768 kHz crystal can be used in conjunction with the dedicated internal oscillator circuit.

- Note: In Counter mode, a falling edge must be registered by the counter prior to the first incrementing rising edge after any one or more of the following conditions:

- Timer1 enabled after POR

- Write to TMR1H or TMR1L

- Timer1 is disabled

- Timer1 is disabled (TMR1ON = 0) when T1CKI is high then Timer1 is enabled (TMR1ON=1) when T1CKI is low.

| TABLE 22-2: CLO | CK SOURCE SELECTIONS |

|-----------------|----------------------|

|-----------------|----------------------|

| TMR1CS<1:0> | T1OSCEN | Clock Source                   |

|-------------|---------|--------------------------------|

| 11          | х       | Reserved                       |

| 10          | 1       | Timer1 Oscillator              |

| 10          | 0       | External Clocking on T1CKI Pin |

| 01          | х       | System Clock (Fosc)            |

| 00          | х       | Instruction Clock (Fosc/4)     |

#### 24.2.1.4 16-bit Duty Cycle Register

The PSMCxDC Duty Cycle register is used to determine a synchronous falling edge event referenced to the 16-bit PSMCxTMR digital counter. A match between the PSMCxTMR and PSMCxDC register values will generate a falling edge event.

The match will generate a duty cycle match interrupt, thereby setting the PxTDCIF bit of the PSMC Time Base Interrupt Control (PSMCxINT) register (Register 24-33).

The 16-bit duty cycle value is accessible to software as two 8-bit registers:

- PSMC Duty Cycle Count Low Byte (PSMCxDCL) register (Register 24-22)

- PSMC Duty Cycle Count High Byte (PSMCxDCH) register (Register 24-23)

The 16-bit duty cycle value is double-buffered before it is presented to the 16-bit time base for comparison. The buffered registers are updated on the first period event Reset after the PSMCxLD bit of the PSMCxCON register is set.

When the period, phase, and duty cycle are all determined from the time base, the effective PWM duty cycle can be expressed as shown in Equation 24-2.

# EQUATION 24-2: PWM DUTY CYCLE

| DUTYCYCLE = | PSMCxDC[15:0] - PSMCxPH[15:0] |

|-------------|-------------------------------|

|             | (PSMCxPR[15:0] + 1)           |

# 24.2.2 0% DUTY CYCLE OPERATION USING TIME BASE

To configure the PWM for 0% duty cycle set PSMCxDC<15:0> = PSMCxPH<15:0>. This will trigger a falling edge event simultaneous with the rising edge event and prevent the PWM from being asserted.

# 24.2.3 100% DUTY CYCLE OPERATION USING TIME BASE

To configure the PWM for 100% duty cycle set PSMCxDC<15:0> > PSMCxPR<15:0>.

This will prevent a falling edge event from occurring as the PSMCxDC<15:0> value and the time base value PSMCxTMR<15:0> will never be equal.

#### 24.2.4 TIME BASE INTERRUPT GENERATION

The Time Base section can generate four unique interrupts:

- Time Base Counter Overflow Interrupt

- Time Base Phase Register Match Interrupt

- Time Base Duty Cycle Register Match Interrupt

- Time Base Period Register Match Interrupt

Each interrupt has an interrupt flag bit and an interrupt enable bit. The interrupt flag bit is set anytime a given event occurs, regardless of the status of the enable bit.

Time base interrupt enables and flags are located in the PSMC Time Base Interrupt Control (PSMCxINT) register (Register 24-33).

PSMC time base interrupts also require that the PSMCxTIE bit in the PIE4 register and the PEIE and GIE bits in the INTCON register be set in order to generate an interrupt. The PSMCxTIF interrupt flag in the PIR4 register will only be set by a time base interrupt when one or more of the enable bits in the PSMCxINT register is set.

The interrupt flag bits need to be cleared in software. However, all PMSCx time base interrupt flags, except PSMCxTIF, are cleared when the PSMCxEN bit is cleared.

Interrupt bits that are set by software will generate an interrupt provided that the corresponding interrupt is enabled.

**Note:** Interrupt flags in both the PIE4 and PSMCxINT registers must be cleared to clear the interrupt. The PSMCxINT flags must be cleared first.

#### 24.2.5 PSMC TIME BASE CLOCK SOURCES

There are three clock sources available to the module:

- Internal 64 MHz clock

- Fosc system clock

- External clock input pin

The clock source is selected with the PxCSRC<1:0> bits of the PSMCx Clock Control (PSMCxCLK) register (Register 24-6).

When the Internal 64 MHz clock is selected as the source, the HFINTOSC continues to operate and clock the PSMC circuitry in Sleep. However, the system clock to other peripherals and the CPU is suppressed.

Note: When the 64 MHz clock is selected, the clock continues to operate in Sleep, even when the PSMC is disabled (PSMCxEN = 0). Select a clock other than the 64 MHz clock to minimize power consumption when the PSMC is not enabled.

The Internal 64 MHz clock utilizes the system clock 4x PLL. When the system clock source is external and the PSMC is using the Internal 64 MHz clock, the 4x PLL should not be used for the system clock.

#### 24.2.7 ASYNCHRONOUS INPUTS

The PSMC module supports asynchronous inputs alone or in combination with the synchronous inputs. asynchronous inputs include:

- Analog

- sync\_C1OUT

- sync\_C2OUT

- sync\_C3OUT

- sync\_C4OUT

- Digital

- PSMCxIN pin

#### 24.2.7.1 Comparator Inputs

The outputs of any combination of the synchronized comparators may be used to trigger any of the three events as well as auto-shutdown.

The event triggers on the rising edge of the comparator output. Except for auto-shutdown, the event input is not level sensitive.

#### 24.2.7.2 PSMCxIN Pin Input

The PSMCxIN pin may be used to trigger PSMC events. Data is passed through straight to the PSMC module without any synchronization to a system clock. This is so that input blanking may be applied to any external circuit using the module.

The event triggers on the rising edge of the PSMCxIN signal.

#### 24.2.7.3 Asynchronous Polarity

Polarity control is available for the period and duty-cycle asynchronous event inputs. Polarity control is necessary when the same signal is used as the source for both events. Inverting the polarity of one event relative to the other enables starting the period on one edge of the signal and terminating the duty-cycle on the opposite edge. Polarity is controlled with the PxPRPOL and PxDCPOL bits of the PSMCxSYNC register. Inverting the asynchronous input with these controls inverts all enabled asynchronous inputs for the corresponding event.

#### 24.2.8 INPUT BLANKING

Input blanking is a function whereby the inputs from any selected asynchronous input may be driven inactive for a short period of time. This is to prevent electrical transients from the turn-on/off of power components from generating a false event.

Blanking is initiated by either or both:

- Rising event

- Falling event

Blanked inputs are suppressed from causing all asynchronous events, including:

- Rising

- Falling

- Period

- Shutdown

Rising edge and falling edge blanking are controlled independently. The following features are available for blanking:

- · Blanking enable

- · Blanking time counters

- · Blanking mode

The following Blanking modes are available:

- Blanking disabled

- Immediate blanking

The Falling Edge Blanking mode is set with the PxFEBM<1:0> bits of the PSMCx Blanking Control (PSMCxBLNK) register (Register 24-9).

The Rising Edge Blanking mode is set with the PxREBM<1:0> bits of the PSMCx Blanking Control (PSMCxBLNK) register (Register 24-9).

#### 24.2.8.1 Blanking Disabled

With blanking disabled, the asynchronous inputs are passed to the PSMC module without any intervention.

#### 24.2.8.2 Immediate Blanking

With Immediate blanking, a counter is used to determine the blanking period. The desired blanking time is measured in psmc\_clk periods. A rising edge event will start incrementing the rising edge blanking counter. A falling edge event will start incrementing the falling edge blanking counter.

The rising edge blanking time is set with the PSMC Rising Edge Blanking Time (PSMCxBLKR) register (Register 24-29). The inputs to be blanked are selected with the PSMC Rising Edge Blanked Source (PSMCxREBS) register (Register 24-10). During rising edge blanking, the selected blanked sources are suppressed for falling edge as well as rising edge, auto-shutdown and period events.

The falling edge blanking time is set with the PSMC Falling Edge Blanking Time (PSMCxBLKF) register (Register 24-30). The inputs to be blanked are selected with the PSMC Falling Edge Blanked Source (PSMCxFEBS) register (Register 24-11). During falling edge blanking, the selected blanked sources are suppressed for rising edge, as well as falling edge, auto-shutdown, and period events.

The blanking counters are incremented on the rising edge of psmc\_clk. Blanked sources are suppressed until the counter value equals the blanking time register causing the blanking to terminate.

As the rising and falling edge events are from asynchronous inputs, there may be some uncertainty in the actual blanking time implemented in each cycle. The maximum uncertainty is equal to one psmc\_clk period.

#### REGISTER 24-20: PSMCxPHL: PSMC PHASE COUNT LOW BYTE REGISTER

| R/W-0/0          | R/W-0/0 | R/W-0/0           | R/W-0/0 | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0     |

|------------------|---------|-------------------|---------|----------------|------------------|------------------|-------------|

|                  |         |                   | PSMCx   | PHL<7:0>       |                  |                  |             |

| bit 7            |         |                   |         |                |                  |                  | bit 0       |

|                  |         |                   |         |                |                  |                  |             |

| Legend:          |         |                   |         |                |                  |                  |             |

| R = Readable     | bit     | W = Writable      | bit     | U = Unimpler   | nented bit, read | l as '0'         |             |

| u = Bit is unch  | anged   | x = Bit is unkr   | nown    | -n/n = Value a | at POR and BO    | R/Value at all c | ther Resets |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                |                  |                  |             |

bit 7-0

**PSMCxPHL<7:0>:** 16-bit Phase Count Least Significant bits = PSMCxPH<7:0>

# REGISTER 24-21: PSMCxPHH: PSMC PHASE COUNT HIGH BYTE REGISTER

| PSMCxPHH<7:0> |  |  |  |  |  |  |  |  |

|---------------|--|--|--|--|--|--|--|--|

| bit 7 bit     |  |  |  |  |  |  |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **PSMCxPHH<7:0>:** 16-bit Phase Count Most Significant bits

= PSMCxPH<15:8>

# REGISTER 24-32: PSMCxSTR1: PSMC STEERING CONTROL REGISTER 1

| I-0 U-0                                                                                                                                                                                                                                                                                                                                                                                          | U-0                              |                                                                                                                |                                                                                                                                  |                                                                                                                                                           |                          |  |  |                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--|--|------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                  | 00                               | U-0                                                                                                            | U-0                                                                                                                              | R/W-0/0                                                                                                                                                   | R/W-0/0                  |  |  |                              |

|                                                                                                                                                                                                                                                                                                                                                                                                  |                                  | —                                                                                                              | _                                                                                                                                | PxLSMEN                                                                                                                                                   | PxHSMEN                  |  |  |                              |

|                                                                                                                                                                                                                                                                                                                                                                                                  |                                  |                                                                                                                |                                                                                                                                  |                                                                                                                                                           | bit (                    |  |  |                              |

|                                                                                                                                                                                                                                                                                                                                                                                                  |                                  |                                                                                                                |                                                                                                                                  |                                                                                                                                                           |                          |  |  |                              |

|                                                                                                                                                                                                                                                                                                                                                                                                  |                                  |                                                                                                                |                                                                                                                                  |                                                                                                                                                           |                          |  |  |                              |

| R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'                                                                                                                                                                                                                                                                                                                               |                                  |                                                                                                                |                                                                                                                                  |                                                                                                                                                           |                          |  |  |                              |

| x = Bit is unki                                                                                                                                                                                                                                                                                                                                                                                  | nown                             | -n/n = Value a                                                                                                 | at POR and BC                                                                                                                    | R/Value at all c                                                                                                                                          | ther Resets              |  |  |                              |

| '0' = Bit is cle                                                                                                                                                                                                                                                                                                                                                                                 | ared                             |                                                                                                                |                                                                                                                                  |                                                                                                                                                           |                          |  |  |                              |

| <b>PxSSYNC</b> : PWM Steering Synchronization bit<br>1 = PWM outputs are updated on period boundary                                                                                                                                                                                                                                                                                              |                                  |                                                                                                                |                                                                                                                                  |                                                                                                                                                           |                          |  |  |                              |

| <ul> <li>0 = PWM outputs are updated immediately</li> <li>Unimplemented: Read as '0'</li> </ul>                                                                                                                                                                                                                                                                                                  |                                  |                                                                                                                |                                                                                                                                  |                                                                                                                                                           |                          |  |  |                              |

| <ul> <li>PxLSMEN: 3-Phase Steering Low Side Modulation Enable bit</li> <li><u>PxMODE = 1100:</u></li> <li>1 = Low side driver PSMCxB, PSMCxD and PSMCxF outputs are modulated according PSMCxMDL when the output is high and driven low without modulation when the output is low.</li> <li>0 = PSMCxB, PSMCxD, and PSMCxF outputs are driven high and low by PSMCxSTR0 contribution.</li> </ul> |                                  |                                                                                                                |                                                                                                                                  |                                                                                                                                                           |                          |  |  |                              |

|                                                                                                                                                                                                                                                                                                                                                                                                  |                                  |                                                                                                                |                                                                                                                                  |                                                                                                                                                           |                          |  |  | DE <> 1100:<br>ect on output |

| PxHSMEN: 3-Phase Steering High Side Modulation Enable bit                                                                                                                                                                                                                                                                                                                                        |                                  |                                                                                                                |                                                                                                                                  |                                                                                                                                                           |                          |  |  |                              |

| PSMCxMDL when the<br>PSMCxA, PSMCxC a<br>without modulation.                                                                                                                                                                                                                                                                                                                                     | output is high                   | n and driven low                                                                                               | without modu                                                                                                                     | lation when the                                                                                                                                           | output is low            |  |  |                              |

|                                                                                                                                                                                                                                                                                                                                                                                                  | SMCxMDL when the SMCxA, PSMCxC a | SMCxMDL when the output is high<br>SMCxA, PSMCxC and PSMCxE<br>vithout modulation.<br><u>DE &lt;&gt; 1100:</u> | SMCxMDL when the output is high and driven low<br>SMCxA, PSMCxC and PSMCxE outputs are dri<br>vithout modulation.<br>DE <> 1100: | SMCxMDL when the output is high and driven low without modu<br>SMCxA, PSMCxC and PSMCxE outputs are driven high and<br>vithout modulation.<br>DE <> 1100: | <u>DE &lt;&gt; 1100:</u> |  |  |                              |

# 25.3 PWM Overview

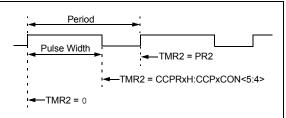

Pulse-Width Modulation (PWM) is a scheme that provides power to a load by switching quickly between fully on and fully off states. The PWM signal resembles a square wave where the high portion of the signal is considered the on state and the low portion of the signal is considered the off state. The high portion, also known as the pulse width, can vary in time and is defined in steps. A larger number of steps applied, which lengthens the pulse width, also supplies more power to the load. Lowering the number of steps applied, which shortens the pulse width, supplies less power. The PWM period is defined as the duration of one complete cycle or the total amount of on and off time combined.

PWM resolution defines the maximum number of steps that can be present in a single PWM period. A higher resolution allows for more precise control of the pulse width time and in turn the power that is applied to the load.

The term duty cycle describes the proportion of the on time to the off time and is expressed in percentages, where 0% is fully off and 100% is fully on. A lower duty cycle corresponds to less power applied and a higher duty cycle corresponds to more power applied.

Figure 25-3 shows a typical waveform of the PWM signal.

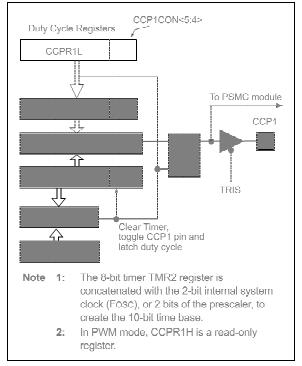

#### 25.3.1 STANDARD PWM OPERATION

The standard PWM function described in this section is available and identical for all CCP modules.

The standard PWM mode generates a Pulse-Width Modulation (PWM) signal on the CCPx pin with up to 10 bits of resolution. The period, duty cycle, and resolution are controlled by the following registers:

- · PR2 registers

- · T2CON registers

- · CCPRxL registers

- · CCPxCON registers

Figure 25-4 shows a simplified block diagram of PWM operation.

- Note 1: The corresponding TRIS bit must be cleared to enable the PWM output on the CCPx pin.

- 2: Clearing the CCPxCON register will relinquish control of the CCPx pin.

#### FIGURE 25-3: CCP PWM OUTPUT SIGNAL

#### SIMPLIFIED PWM BLOCK DIAGRAM

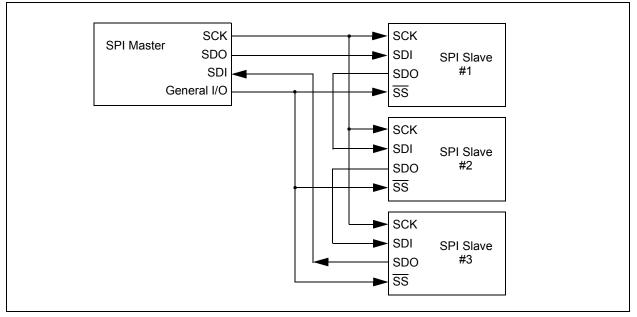

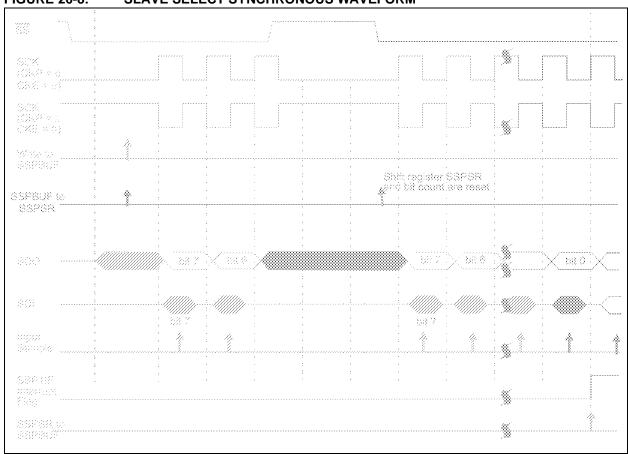

#### FIGURE 26-8: SLAVE SELECT SYNCHRONOUS WAVEFORM

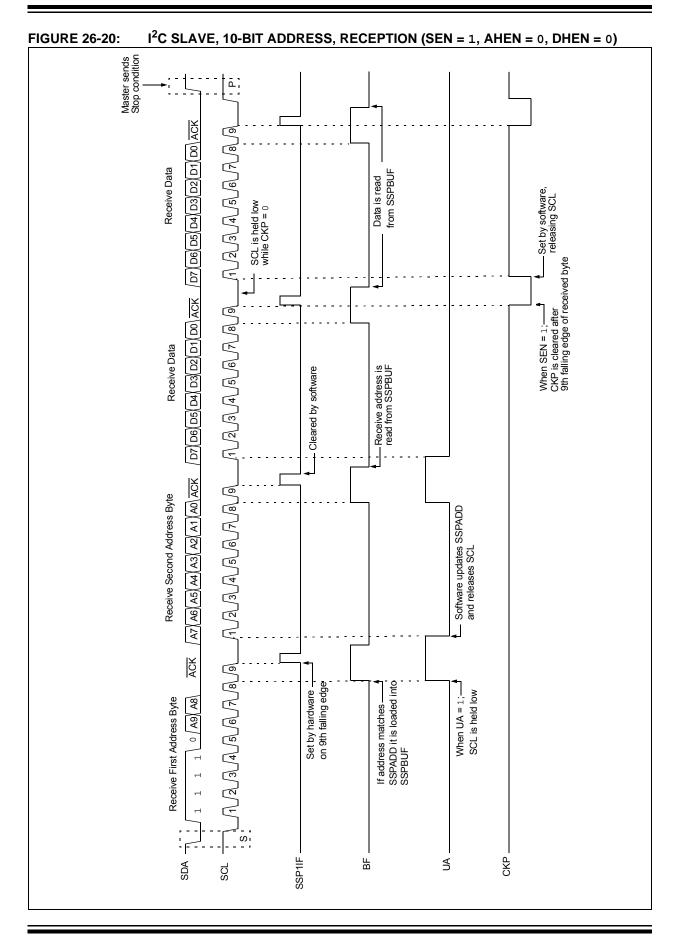

#### REGISTER 26-1: SSPSTAT: SSP STATUS REGISTER (CONTINUED)

bit 0

BF: Buffer Full Status bit

Receive (SPI and I<sup>2</sup>C modes):

1 = Receive complete, SSPBUF is full

0 = Receive not complete, SSPBUF is empty

Transmit (I<sup>2</sup>C mode only):

- 1 = Data transmit in progress (does not include the ACK and Stop bits), SSPBUF is full

- 0 = Data transmit complete (does not include the  $\overline{ACK}$  and Stop bits), SSPBUF is empty

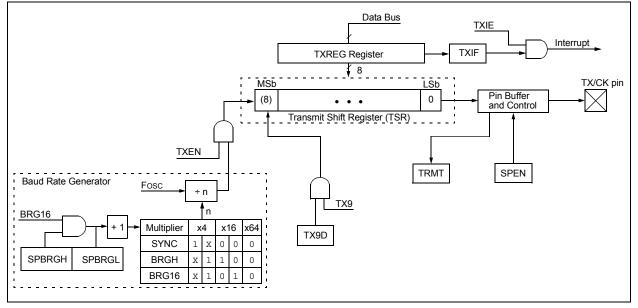

# 27.0 ENHANCED UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (EUSART)

The Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) module is a serial I/O communications peripheral. It contains all the clock generators, shift registers and data buffers necessary to perform an input or output serial data transfer independent of device program execution. The EUSART, also known as a Serial Communications Interface (SCI), can be configured as a full-duplex asynchronous system or half-duplex synchronous system. Full-Duplex mode is useful for communications with peripheral systems, such as CRT terminals and personal computers. Half-Duplex Synchronous mode is intended for communications with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs or other microcontrollers. These devices typically do not have internal clocks for baud rate generation and require the external clock signal provided by a master synchronous device.

The EUSART module includes the following capabilities:

- · Full-duplex asynchronous transmit and receive

- Two-character input buffer

- One-character output buffer

- Programmable 8-bit or 9-bit character length

- · Address detection in 9-bit mode

- · Input buffer overrun error detection

- Received character framing error detection

- Half-duplex synchronous master

- · Half-duplex synchronous slave

- Programmable clock polarity in synchronous modes

- · Sleep operation

The EUSART module implements the following additional features, making it ideally suited for use in Local Interconnect Network (LIN) bus systems:

- · Automatic detection and calibration of the baud rate

- Wake-up on Break reception

- 13-bit Break character transmit

Block diagrams of the EUSART transmitter and receiver are shown in Figure 27-1 and Figure 27-2.

# FIGURE 27-1: EUSART TRANSMIT BLOCK DIAGRAM

| TRIS             | Load TRIS Register with W                                                                                                                            |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] TRIS f                                                                                                                                       |  |  |  |  |  |

| Operands:        | $5 \leq f \leq 7$                                                                                                                                    |  |  |  |  |  |

| Operation:       | (W) $\rightarrow$ TRIS register 'f'                                                                                                                  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                 |  |  |  |  |  |

| Description:     | Move data from W register to<br>TRIS register.<br>When 'f' = 5, TRISA is loaded.<br>When 'f' = 6, TRISB is loaded.<br>When 'f' = 7, TRISC is loaded. |  |  |  |  |  |

| XORLW            | Exclusive OR literal with W                                                                                            |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] XORLW k                                                                                               |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                    |  |  |  |  |

| Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                          |  |  |  |  |

| Status Affected: | Z                                                                                                                      |  |  |  |  |

| Description:     | The contents of the W register<br>are XOR'ed with the 8-bit<br>literal 'k'. The result is placed in<br>the W register. |  |  |  |  |

| XORWF            | Exclusive OR W with f                                                                                                                                                           |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] XORWF f,d                                                                                                                                                               |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                               |  |  |  |  |  |

| Operation:       | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                       |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                               |  |  |  |  |  |

| Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' is '0', the result is stored in the W register. If 'd' is '1', the result is stored back in register 'f'. |  |  |  |  |  |

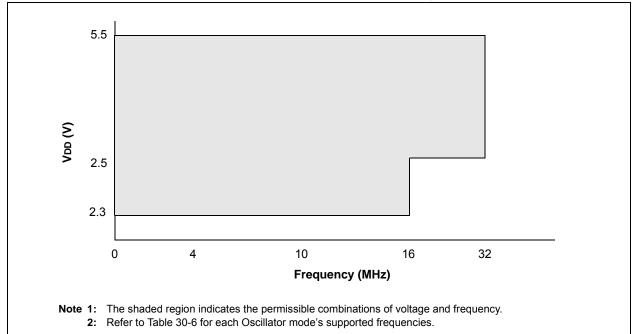

# 30.3 DC Characteristics

# TABLE 30-1: SUPPLY VOLTAGE

| PIC16LF1784/6/7<br>PIC16F1784/6/7 |        |                                                           | Standard Operating Conditions (unless otherwise stated) |      |            |        |                                                     |  |  |

|-----------------------------------|--------|-----------------------------------------------------------|---------------------------------------------------------|------|------------|--------|-----------------------------------------------------|--|--|

|                                   |        |                                                           |                                                         |      |            |        |                                                     |  |  |

| Param.<br>No.                     | Sym.   | Characteristic                                            | Min.                                                    | Тур† | Max.       | Units  | Conditions                                          |  |  |

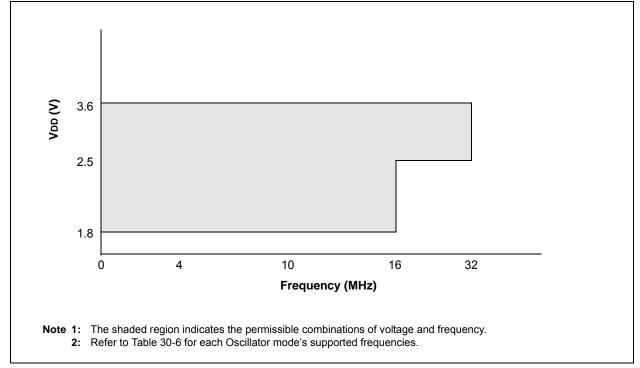

| D001                              | Vdd    | Supply Voltage (VDDMIN, VDDMAX)                           |                                                         |      |            |        |                                                     |  |  |

|                                   |        |                                                           | 1.8<br>2.5                                              |      | 3.6<br>3.6 | V<br>V | Fosc ≤ 16 MHz:<br>Fosc ≤ 32 MHz ( <b>Note 2</b> )   |  |  |

| D001                              |        |                                                           | 2.3<br>2.5                                              | _    | 5.5<br>5.5 | V<br>V | Fosc ≤ 16 MHz:<br>Fosc ≤ 32 MHz ( <b>Note 2</b> )   |  |  |

| D002* VDR                         |        | RAM Data Retention Voltage <sup>(1)</sup>                 |                                                         |      |            |        |                                                     |  |  |

|                                   |        |                                                           | 1.5                                                     | —    | _          | V      | Device in Sleep mode                                |  |  |

| D002*                             |        |                                                           | 1.7                                                     | —    | _          | V      | Device in Sleep mode                                |  |  |

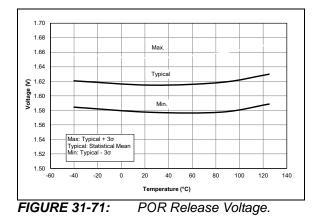

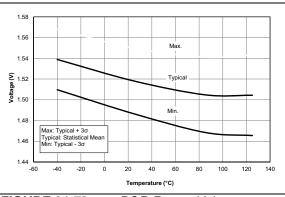

|                                   | VPOR*  | Power-on Reset Release Voltage                            | _                                                       | 1.6  | _          | V      |                                                     |  |  |

|                                   | VPORR* | Power-on Reset Rearm Voltage                              |                                                         |      |            |        |                                                     |  |  |

|                                   |        |                                                           | _                                                       | 0.8  | _          | V      | Device in Sleep mode                                |  |  |

|                                   |        |                                                           | —                                                       | 1.5  | —          | V      | Device in Sleep mode                                |  |  |

| D003                              | VFVR   | Fixed Voltage Reference                                   | -4                                                      | _    | 4          | %      | 1.024V, VDD $\geq$ 2.5V                             |  |  |

|                                   |        | Voltage <sup>(3)</sup>                                    | -4                                                      | —    | 4          | %      | $2.048 \text{V}, \text{VDD} \geq 2.5 \text{V}$      |  |  |

|                                   |        |                                                           | -5                                                      | _    | 5          | %      | 4.096V, VDD ≥ 4.75V                                 |  |  |

| D004*                             | SVDD   | VDD Rise Rate to ensure internal<br>Power-on Reset signal | 0.05                                                    | _    | _          | V/ms   | See Section 5.1 "Power-On Reset (POR)" for details. |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.3V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

2: PLL required for 32 MHz operation.

3: Industrial temperature range only.

| Standa       | Standard Operating Conditions (unless otherwise stated) |                                                              |               |      |      |       |                |  |  |

|--------------|---------------------------------------------------------|--------------------------------------------------------------|---------------|------|------|-------|----------------|--|--|

| Param<br>No. | Sym.                                                    | Characteristic                                               | Min.          | Тур† | Max. | Units | Conditions     |  |  |

| OS11         | TosH2ckL                                                | Fosc↑ to CLKOUT↓ <sup>(1)</sup>                              | —             | —    | 70   | ns    | VDD = 3.3-5.0V |  |  |

| OS12         | TosH2ckH                                                | Fosc↑ to CLKOUT↑ <sup>(1)</sup>                              | —             | _    | 72   | ns    | VDD = 3.3-5.0V |  |  |

| OS13         | TckL2ioV                                                | CLKOUT↓ to Port out valid <sup>(1)</sup>                     | —             | —    | 20   | ns    |                |  |  |

| OS14         | TioV2ckH                                                | Port input valid before CLKOUT <sup>(1)</sup>                | Tosc + 200 ns | _    | _    | ns    |                |  |  |

| OS15         | TosH2ioV                                                | Fosc↑ (Q1 cycle) to Port out valid                           | —             | 50   | 70*  | ns    | VDD = 3.3-5.0V |  |  |

| OS16         | TosH2iol                                                | Fosc↑ (Q2 cycle) to Port input invalid<br>(I/O in hold time) | 50            | _    | —    | ns    | VDD = 3.3-5.0V |  |  |

| OS17         | TioV2osH                                                | Port input valid to Fosc↑ (Q2 cycle)<br>(I/O in setup time)  | 20            | _    | —    | ns    |                |  |  |

| OS18*        | TioR                                                    | Port output rise time                                        | _             | 40   | 72   | ns    | VDD = 1.8V     |  |  |

|              |                                                         |                                                              | —             | 15   | 32   |       | VDD = 3.3-5.0V |  |  |

| OS19*        | TioF                                                    | Port output fall time                                        | —             | 28   | 55   | ns    | VDD = 1.8V     |  |  |

|              |                                                         |                                                              | _             | 15   | 30   |       | VDD = 3.3-5.0V |  |  |

| OS20*        | Tinp                                                    | INT pin input high or low time                               | 25            | —    | —    | ns    |                |  |  |

| OS21*        | Tioc                                                    | Interrupt-on-change new input level time                     | 25            | —    | —    | ns    |                |  |  |

## TABLE 30-9: CLKOUT AND I/O TIMING PARAMETERS

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated.

**Note 1:** Measurements are taken in RC mode where CLKOUT output is 4 x Tosc.

Note: Unless otherwise noted, VIN = 5V, Fosc = 300 kHz, CIN = 0.1  $\mu$ F, TA = 25°C.

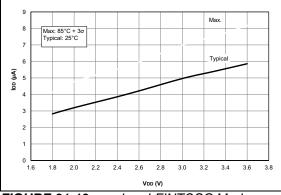

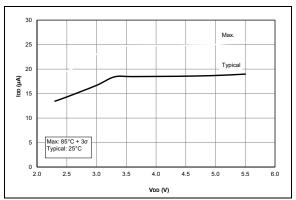

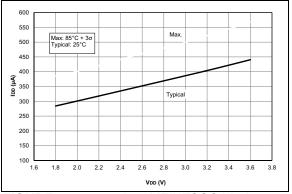

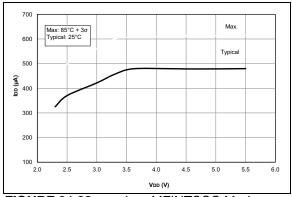

FIGURE 31-19: IDD, LFINTOSC Mode, Fosc = 31 kHz, PIC16LF1784/6/7 Only.

FIGURE 31-20: IDD, LFINTOSC Mode, Fosc = 31 kHz, PIC16F1784/6/7 Only.

FIGURE 31-21: IDD, MFINTOSC Mode, Fosc = 500 kHz, PIC16LF1784/6/7 Only.

FIGURE 31-22: IDD, MFINTOSC Mode, Fosc = 500 kHz, PIC16F1784/6/7 Only.

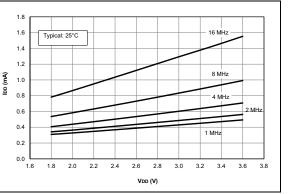

FIGURE 31-23: IDD Typical, HFINTOSC Mode, PIC16LF1784/6/7 Only.

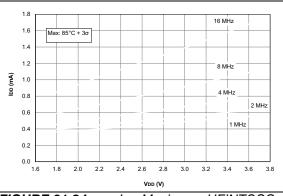

FIGURE 31-24: IDD Maximum, HFINTOSC Mode, PIC16LF1784/6/7 Only.

Note: Unless otherwise noted, VIN = 5V, Fosc = 300 kHz, CIN = 0.1  $\mu$ F, TA = 25°C.

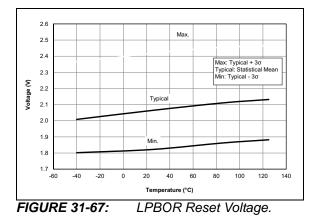

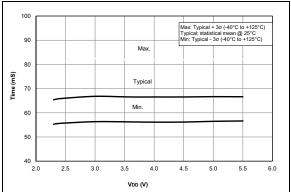

FIGURE 31-69: PWRT Period, PIC16F1784/6/7 Only.

FIGURE 31-72: POR Rearm Voltage, NP Mode (VREGPM = 0), PIC16F1784/6/7 Only.

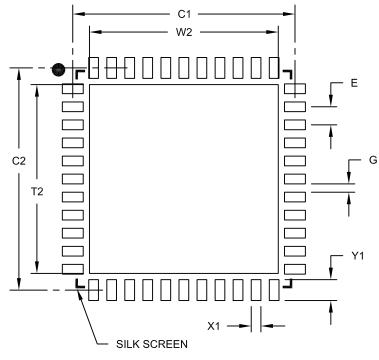

44-Lead Plastic Quad Flat, No Lead Package (ML) - 8x8 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

# RECOMMENDED LAND PATTERN

|                            | MILLIMETERS |      |      |      |  |

|----------------------------|-------------|------|------|------|--|

| Dimensior                  | MIN         | NOM  | MAX  |      |  |

| Contact Pitch              | 0.65 BSC    |      |      |      |  |

| Optional Center Pad Width  | W2          |      |      | 6.60 |  |

| Optional Center Pad Length | T2          |      |      | 6.60 |  |

| Contact Pad Spacing        | C1          |      | 8.00 |      |  |

| Contact Pad Spacing        | C2          |      | 8.00 |      |  |

| Contact Pad Width (X44)    | X1          |      |      | 0.35 |  |

| Contact Pad Length (X44)   | Y1          |      |      | 0.85 |  |

| Distance Between Pads      | G           | 0.25 |      |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2103B