Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2 0 0 0 0 0                |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PSMC, PWM, WDT                               |

| Number of I/O              | 35                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 1K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 14x12b; D/A 1x8b                                                      |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 40-UFQFN Exposed Pad                                                      |

| Supplier Device Package    | 40-UQFN (5x5)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1787-e-mv |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

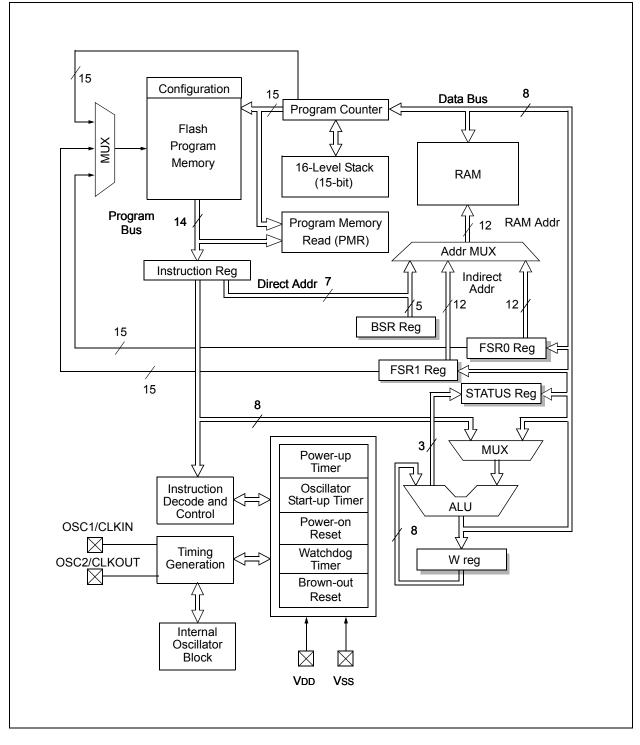

# 2.0 ENHANCED MID-RANGE CPU

This family of devices contain an enhanced mid-range 8-bit CPU core. The CPU has 49 instructions. Interrupt capability includes automatic context saving. The hardware stack is 16 levels deep and has Overflow and Underflow Reset capability. Direct, Indirect, and

FIGURE 2-1: CORE BLOCK DIAGRAM

Relative addressing modes are available. Two File Select Registers (FSRs) provide the ability to read program and data memory.

- · Automatic Interrupt Context Saving

- 16-level Stack with Overflow and Underflow

- File Select Registers

- Instruction Set

# 3.3.5 CORE FUNCTION REGISTERS SUMMARY

The Core Function registers listed in Table 3-11 can be addressed from any Bank.

| TABLE 3-11: | CORE FUNCTION REGISTERS SUMMARY |

|-------------|---------------------------------|

|-------------|---------------------------------|

| Addr            | Name      | Bit 7        | Bit 6                                                                                                    | Bit 5         | Bit 4        | Bit 3       | Bit 2         | Bit 1  | Bit 0 | Value on<br>POR, BOR | Value on all<br>other Resets |

|-----------------|-----------|--------------|----------------------------------------------------------------------------------------------------------|---------------|--------------|-------------|---------------|--------|-------|----------------------|------------------------------|

| Bank            | Bank 0-31 |              |                                                                                                          |               |              |             |               |        |       |                      |                              |

| x00h or<br>x80h | INDF0     |              | Addressing this location uses contents of FSR0H/FSR0L to address data memory<br>not a physical register) |               |              |             |               |        |       |                      | uuuu uuuu                    |

| x01h or<br>x81h | INDF1     |              | this location<br>ical register)                                                                          |               | nts of FSR1H | /FSR1L to a | ddress data i | nemory |       | xxxx xxxx            | uuuu uuuu                    |

| x02h or<br>x82h | PCL       | Program Co   | ounter (PC) I                                                                                            | Least Signifi | cant Byte    |             |               |        |       | 0000 0000            | 0000 0000                    |

| x03h or<br>x83h | STATUS    | -            | -                                                                                                        | -             | TO           | PD          | Z             | DC     | С     | 1 1000               | q quuu                       |

| x04h or<br>x84h | FSR0L     | Indirect Dat | Indirect Data Memory Address 0 Low Pointer                                                               |               |              |             |               |        |       |                      | uuuu uuuu                    |

| x05h or<br>x85h | FSR0H     | Indirect Dat | Indirect Data Memory Address 0 High Pointer                                                              |               |              |             |               |        |       | 0000 0000            | 0000 0000                    |

| x06h or<br>x86h | FSR1L     | Indirect Dat | ta Memory A                                                                                              | ddress 1 Lo   | w Pointer    |             |               |        |       | 0000 0000            | uuuu uuuu                    |

| x07h or<br>x87h | FSR1H     | Indirect Dat | ta Memory A                                                                                              | ddress 1 Hi   | gh Pointer   |             |               |        |       | 0000 0000            | 0000 0000                    |

| x08h or<br>x88h | BSR       |              |                                                                                                          |               | BSR4         | BSR3        | BSR2          | BSR1   | BSR0  | 0 0000               | 0 0000                       |

| x09h or<br>x89h | WREG      | Working Re   | Working Register                                                                                         |               |              |             |               |        |       |                      | uuuu uuuu                    |

| x0Ahor<br>x8Ah  | PCLATH    | _            | Write Buffer for the upper 7 bits of the Program Counter                                                 |               |              |             |               |        |       | -000 0000            | -000 0000                    |

| x0Bhor<br>x8Bh  | INTCON    | GIE          | PEIE                                                                                                     | TMR0IE        | INTE         | IOCIE       | TMR0IF        | INTF   | IOCIF | 0000 0000            | 0000 0000                    |

**Legend:** x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', <math>r = reserved. Shaded locations are unimplemented, read as '0'.

| Name   | Bit 7  | Bit 6  | Bit 5 | Bit 4          | Bit 3 | Bit 2 | Bit 1 | Bit 0  | Register<br>on Page |

|--------|--------|--------|-------|----------------|-------|-------|-------|--------|---------------------|

| BORCON | SBOREN | BORFS  | _     |                | _     |       |       | BORRDY | 61                  |

| PCON   | STKOVF | STKUNF | _     | RWDT           | RMCLR | RI    | POR   | BOR    | 65                  |

| STATUS |        |        | _     | TO             | PD    | Z     | DC    | С      | 27                  |

| WDTCON | —      | —      |       | WDTPS<4:0> SWI |       |       |       |        | 110                 |

### TABLE 5-5: SUMMARY OF REGISTERS ASSOCIATED WITH RESETS

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by Resets.

| R/W-0/0          | R/W-0/0                                                                                                                                                                                                             | R/W-0/0                                                   | R/W-0/0          | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0     |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|------------------|----------------|------------------|------------------|-------------|--|

| OSFIE            | C2IE                                                                                                                                                                                                                | C1IE                                                      | EEIE             | BCL1IE         | C4IE             | C3IE             | CCP2IE      |  |

| bit 7            |                                                                                                                                                                                                                     |                                                           |                  |                |                  |                  | bit 0       |  |

|                  |                                                                                                                                                                                                                     |                                                           |                  |                |                  |                  |             |  |

| Legend:          |                                                                                                                                                                                                                     |                                                           |                  |                |                  |                  |             |  |

| R = Readable     |                                                                                                                                                                                                                     | W = Writable                                              |                  |                | nented bit, read |                  |             |  |

| u = Bit is unch  | anged                                                                                                                                                                                                               | x = Bit is unkr                                           |                  | -n/n = Value a | at POR and BOI   | R/Value at all o | ther Resets |  |

| '1' = Bit is set |                                                                                                                                                                                                                     | '0' = Bit is clea                                         | ared             |                |                  |                  |             |  |

| bit 7            | 1 = Enables f                                                                                                                                                                                                       | ator Fail Interru<br>the Oscillator F<br>the Oscillator F | ail interrupt    |                |                  |                  |             |  |

| bit 6            | <ul> <li>0 = Disables the Oscillator Fail interrupt</li> <li>C2IE: Comparator C2 Interrupt Enable bit</li> <li>1 = Enables the Comparator C2 interrupt</li> <li>0 = Disables the Comparator C2 interrupt</li> </ul> |                                                           |                  |                |                  |                  |             |  |

| bit 5            | <b>C1IE:</b> Comparator C1 Interrupt Enable bit<br>1 = Enables the Comparator C1 interrupt<br>0 = Disables the Comparator C1 interrupt                                                                              |                                                           |                  |                |                  |                  |             |  |

| bit 4            | 1 = Enables t                                                                                                                                                                                                       | OM Write Comp<br>the EEPROM V<br>the EEPROM               | Vrite Complet    | ion interrupt  |                  |                  |             |  |

| bit 3            | 1 = Enables t                                                                                                                                                                                                       | SP Bus Collisio<br>the MSSP Bus<br>the MSSP Bus           | Collision Inter  | rrupt          |                  |                  |             |  |

| bit 2            | 1 = Enables f                                                                                                                                                                                                       | rator C4 Interru<br>the Comparato<br>the Comparato        | r C4 Interrupt   |                |                  |                  |             |  |

| bit 1            | <b>C3IE:</b> Comparator C3 Interrupt Enable bit<br>1 = Enables the Comparator C3 Interrupt<br>0 = Disables the Comparator C3 Interrupt                                                                              |                                                           |                  |                |                  |                  |             |  |

| bit 0            | CCP2IE: CCF<br>1 = Enables f                                                                                                                                                                                        | P2 Interrupt En<br>the CCP2 inter<br>the CCP2 inter       | able bit<br>rupt |                |                  |                  |             |  |

|                  | PEIE of the IN                                                                                                                                                                                                      | •                                                         |                  |                |                  |                  |             |  |

#### **REGISTER 8-3: PIE2: PERIPHERAL INTERRUPT ENABLE REGISTER 2**

set to enable any peripheral interrupt.

| Name       | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|------------|---------|---------|---------|---------|---------|---------|---------|---------|---------------------|

| ANSELA     | ANSA7   | _       | ANSA5   | ANSA4   | ANSA3   | ANSA2   | ANSA1   | ANSA0   | 132                 |

| INLVLA     | INLVLA7 | INLVLA6 | INLVLA5 | INLVLA4 | INLVLA3 | INLVLA2 | INLVLA1 | INLVLA0 | 133                 |

| LATA       | LATA7   | LATA6   | LATA5   | LATA4   | LATA3   | LATA2   | LATA1   | LATA0   | 131                 |

| ODCONA     | ODA7    | ODA6    | ODA5    | ODA4    | ODA3    | ODA2    | ODA1    | ODA0    | 133                 |

| OPTION_REG | WPUEN   | INTEDG  | TMR0CS  | TMR0SE  | PSA     |         | PS<2:0> |         | 198                 |

| PORTA      | RA7     | RA6     | RA5     | RA4     | RA3     | RA2     | RA1     | RA0     | 131                 |

| SLRCONA    | SLRA7   | SLRA6   | SLRA5   | SLRA4   | SLRA3   | SLRA2   | SLRA1   | SLRA0   | 133                 |

| TRISA      | TRISA7  | TRISA6  | TRISA5  | TRISA4  | TRISA3  | TRISA2  | TRISA1  | TRISA0  | 131                 |

| WPUA       | WPUA7   | WPUA6   | WPUA5   | WPUA4   | WPUA3   | WPUA2   | WPUA1   | WPUA0   | 132                 |

#### TABLE 13-3: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

#### TABLE 13-4: SUMMARY OF CONFIGURATION WORD WITH PORTA

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4  | Bit 11/3 | Bit 10/2          | Bit 9/1 | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|-----------|----------|-------------------|---------|---------|---------------------|

|         | 13:8 |         | _       | FCMEN    | IESO      | CLKOUTEN | KOUTEN BOREN<1:0> |         | CPD     | 54                  |

| CONFIG1 | 7:0  | CP      | MCLRE   | PWRTE    | WDTE<1:0> |          | 0> FOSC<2:0>      |         |         |                     |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by PORTA.

# 13.6 Register Definitions: PORTB

#### **REGISTER 13-11: PORTB: PORTB REGISTER**

| R/W-x/u          | R/W-x/u                                 | R/W-x/u           | R/W-x/u | R/W-x/u                                               | R/W-x/u | R/W-x/u | R/W-x/u |  |  |

|------------------|-----------------------------------------|-------------------|---------|-------------------------------------------------------|---------|---------|---------|--|--|

| RB7              | RB6                                     | RB5               | RB4     | RB3                                                   | RB2     | RB1     | RB0     |  |  |

| bit 7 bit        |                                         |                   |         |                                                       |         |         |         |  |  |

|                  |                                         |                   |         |                                                       |         |         |         |  |  |

| Legend:          |                                         |                   |         |                                                       |         |         |         |  |  |

| R = Readable I   | bit                                     | W = Writable      | bit     | U = Unimplemented bit, read as '0'                    |         |         |         |  |  |

| u = Bit is uncha | a = Bit is unchanged x = Bit is unknown |                   |         | -n/n = Value at POR and BOR/Value at all other Resets |         |         |         |  |  |

| '1' = Bit is set |                                         | '0' = Bit is clea | ared    |                                                       |         |         |         |  |  |

bit 7-0 **RB<7:0>**: PORTB General Purpose I/O Pin bits<sup>(1)</sup> 1 = Port pin is ≥ VIH 0 = Port pin is ≤ VIL

### REGISTER 13-12: TRISB: PORTB TRI-STATE REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| TRISB7  | TRISB6  | TRISB5  | TRISB4  | TRISB3  | TRISB2  | TRISB1  | TRISB0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

TRISB<7:0>: PORTB Tri-State Control bits

1 = PORTB pin configured as an input (tri-stated)

0 = PORTB pin configured as an output

#### REGISTER 13-13: LATB: PORTB DATA LATCH REGISTER

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

| LATB7   | LATB6   | LATB5   | LATB4   | LATB3   | LATB2   | LATB1   | LATB0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 LATB<7:0>: PORTB Output Latch Value bits<sup>(1)</sup>

**Note 1:** Writes to PORTB are actually written to corresponding LATB register. Reads from PORTB register is return of actual I/O pin values.

**Note 1:** Writes to PORTB are actually written to corresponding LATB register. Reads from PORTB register is return of actual I/O pin values.

# REGISTER 13-40: SLRCONE: PORTE SLEW RATE CONTROL REGISTER<sup>(1)</sup>

| U-0              | U-0       | U-0               | U-0 | U-0                                                   | R/W-0/0            | R/W-0/0 | R/W-0/0 |

|------------------|-----------|-------------------|-----|-------------------------------------------------------|--------------------|---------|---------|

| _                | _         | _                 | _   | _                                                     | SLRE2              | SLRE1   | SLRE0   |

| bit 7            |           | ·                 |     | ·                                                     |                    | •       | bit 0   |

|                  |           |                   |     |                                                       |                    |         |         |

| Legend:          |           |                   |     |                                                       |                    |         |         |

| R = Readable     | bit       | W = Writable b    | it  | U = Unimplem                                          | nented bit, read a | is '0'  |         |

| u = Bit is uncha | anged     | x = Bit is unkno  | own | -n/n = Value at POR and BOR/Value at all other Resets |                    |         |         |

| '1' = Bit is set |           | '0' = Bit is clea | red |                                                       |                    |         |         |

|                  |           |                   |     |                                                       |                    |         |         |

| bit 7-3          | Unimpleme | nted: Read as '0' |     |                                                       |                    |         |         |

| bit 2-0 | SLRE<2:0>: PORTE Slew Rate Enable bits |

|---------|----------------------------------------|

|         | For RE<2:0> pins, respectively         |

|         | 1 = Port pin slew rate is limited      |

|         | 0 = Port pin slews at maximum rate     |

Note 1: SLRE<2:0> are available on PIC16(L)F1784/7 only.

#### REGISTER 13-41: INLVLE: PORTE INPUT LEVEL CONTROL REGISTER

| U-0   | U-0 | U-0 | U-0 | R/W-1/1 | R/W-1/1                | R/W-1/1                | R/W-1/1                |

|-------|-----|-----|-----|---------|------------------------|------------------------|------------------------|

| —     | _   | _   | _   | INLVLE3 | INLVLE2 <sup>(1)</sup> | INLVLE1 <sup>(1)</sup> | INLVLE0 <sup>(1)</sup> |

| bit 7 | •   |     |     |         |                        |                        | bit 0                  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| 0' |

|----|

|    |

bit 3-0 INLVLE<3:0>: PORTE Input Level Select bit<sup>(1)</sup>

1 = ST input used for PORT reads and interrupt-on-change

0 = TTL input used for PORT reads and interrupt-on-change

**Note 1:** INLVLE<2:0> are available on PIC16(L)F1784/7 only.

|                        |       |       |       |          | •       |                        | —                      |                        |                     |

|------------------------|-------|-------|-------|----------|---------|------------------------|------------------------|------------------------|---------------------|

| Name                   | Bit 7 | Bit 6 | Bit 5 | Bit 4    | Bit 3   | Bit 2                  | Bit 1                  | Bit 0                  | Register<br>on Page |

| ADCON0                 | ADRMD |       |       | CHS<4:0> | •       |                        | GO/DONE                | ADON                   | 172                 |

| ANSELE                 | _     | _     | _     | _        |         | ANSE2                  | ANSE1                  | ANSE0                  | 153                 |

| INLVLE                 | —     | _     | —     | _        | INLVLE3 | INLVLE2 <sup>(2)</sup> | INLVLE1 <sup>(2)</sup> | INLVLE0 <sup>(2)</sup> | 155                 |

| LATE <sup>(2)</sup>    | _     | _     | _     | _        |         | LATE2                  | LATE1                  | LATE0                  | 153                 |

| ODCONE <sup>(2)</sup>  | _     | _     | _     | _        |         | ODE2                   | ODE1                   | ODE0                   | 154                 |

| PORTE                  | —     | _     | —     | _        | RE3     | RE2 <sup>(2)</sup>     | RE1 <sup>(2)</sup>     | RE0 <sup>(2)</sup>     | 152                 |

| SLRCONE <sup>(2)</sup> | _     | _     | _     | _        |         | SLRE2                  | SLRE1                  | SLRE0                  | 155                 |

| TRISE                  | _     | _     | _     | _        | (1)     | TRISE2 <sup>(2)</sup>  | TRISE1 <sup>(2)</sup>  | TRISE0 <sup>(2)</sup>  | 152                 |

| WPUE                   | _     | _     | _     | _        | WPUE3   | WPUE2 <sup>(2)</sup>   | WPUE1 <sup>(2)</sup>   | WPUE0 <sup>(2)</sup>   | 154                 |

# TABLE 13-12: SUMMARY OF REGISTERS ASSOCIATED WITH PORTE

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTE.

Note 1: Unimplemented, read as '1'.

2: PIC16(L)F1784/7 only

#### **REGISTER 17-3:** ADCON2: ADC CONTROL REGISTER 2 R/W-0/0 R/W-0/0 R/W-0/0 R/W-0/0 R/W-0/0 R/W-0/0 R/W-0/0 R/W-0/0 TRIGSEL<3:0> CHSN<3:0> bit 7 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets '1' = Bit is set '0' = Bit is cleared bit 7-4 TRIGSEL<3:0>: ADC Auto-conversion Trigger Source Selection bits 1111 = Reserved. Auto-conversion Trigger disabled. 1110 = Reserved. Auto-conversion Trigger disabled. 1101 = Reserved. Auto-conversion Trigger disabled. 1100 = PSMC3 Falling Match Event<sup>(1)</sup> 1011 = PSMC3 Rising Edge Event<sup>(1)</sup> 1010 = PSMC3 Period Edge Event<sup>(1)</sup> 1001 = PSMC2 Falling Edge Event 1000 = PSMC2 Rising Edge Event 0111 = PSMC2 Period Match Event 0110 = PSMC1 Falling Edge Event 0101 = PSMC1 Rising Edge Event 0100 = PSMC1 Period Match Event 0011 = Reserved. Auto-conversion Trigger disabled. 0010 = CCP2, Auto-conversion Trigger 0001 = CCP1, Auto-conversion Trigger 0000 = Disabled bit 3-0 CHSN<3:0>: Negative Differential Input Channel Select bits When ADON = 0, all multiplexer inputs are disconnected. 1111 = ADC Negative reference - selected by ADNREF $1110 = AN21^{(1)}$ 1101 = AN13 1100 = AN12 1011 = AN11 1010 = AN10 1001 = AN9 1000 = AN8 0111 = AN7<sup>(1)</sup> $0110 = AN6^{(1)}$

Note 1: PIC16(L)F1784/7 only. For PIC16(L)F1786, "Reserved. No channel connected."

0101 = AN5<sup>(1)</sup> 0100 = AN4 0011 = AN3 0010 = AN2 0001 = AN1 0000 = AN0

bit 0

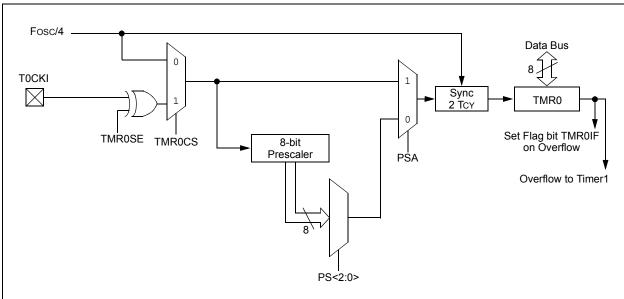

# 21.0 TIMER0 MODULE

The Timer0 module is an 8-bit timer/counter with the following features:

- 8-bit timer/counter register (TMR0)

- 8-bit prescaler (independent of Watchdog Timer)

- Programmable internal or external clock source

- Programmable external clock edge selection

- · Interrupt on overflow

- TMR0 can be used to gate Timer1

Figure 21-1 is a block diagram of the Timer0 module.

# 21.1 Timer0 Operation

The Timer0 module can be used as either an 8-bit timer or an 8-bit counter.

#### 21.1.1 8-BIT TIMER MODE

The Timer0 module will increment every instruction cycle, if used without a prescaler. 8-bit Timer mode is selected by clearing the TMR0CS bit of the OPTION\_REG register.

When TMR0 is written, the increment is inhibited for two instruction cycles immediately following the write.

**Note:** The value written to the TMR0 register can be adjusted, in order to account for the two instruction cycle delay when TMR0 is written.

# FIGURE 21-1: BLOCK DIAGRAM OF THE TIMER0

In 8-Bit Counter mode, the Timer0 module will increment on every rising or falling edge of the T0CKI pin.

8-Bit Counter mode using the T0CKI pin is selected by setting the TMR0CS bit in the OPTION\_REG register to '1'.

The rising or falling transition of the incrementing edge for either input source is determined by the TMR0SE bit in the OPTION\_REG register.

| U-0             | U-0        | R/W-0/0                              | R/W-0/0                | R/W-0/0                | R/W-0/0                | R/W-0/0          | R/W-0/0      |

|-----------------|------------|--------------------------------------|------------------------|------------------------|------------------------|------------------|--------------|

| —               | —          | PxASDLF <sup>(1)</sup>               | PxASDLE <sup>(1)</sup> | PxASDLD <sup>(1)</sup> | PxASDLC <sup>(1)</sup> | PxASDLB          | PxASDLA      |

| bit 7           |            |                                      |                        |                        |                        |                  | bit C        |

|                 |            |                                      |                        |                        |                        |                  |              |

| Legend:         |            |                                      |                        |                        |                        |                  |              |

| R = Readabl     | le bit     | W = Writable                         | bit                    | U = Unimplem           | nented bit, read       | as '0'           |              |

| u = Bit is und  | changed    | x = Bit is unkr                      | iown                   | -n/n = Value a         | t POR and BOP          | R/Value at all o | other Resets |

| '1' = Bit is se | et         | '0' = Bit is clea                    | ared                   |                        |                        |                  |              |

|                 |            |                                      |                        |                        |                        |                  |              |

| bit 7-6         | Unimpleme  | nted: Read as '                      | כי                     |                        |                        |                  |              |

| bit 5           | PxASDLF: F | SMCx Output F                        | Auto-Shutdov           | wn Pin Level bi        | t(1)                   |                  |              |

|                 |            | auto-shutdown is                     |                        |                        |                        |                  |              |

|                 |            | auto-shutdown is                     | •                      |                        | •                      |                  |              |

| bit 4           | PxASDLE: F | PSMCx Output E                       | E Auto-Shutdo          | wn Pin Level b         | it <sup>(1)</sup>      |                  |              |

|                 |            | auto-shutdown is                     |                        |                        | 0                      |                  |              |

|                 |            | auto-shutdown is                     |                        |                        | -                      |                  |              |

| bit 3           |            | PSMCx Output [                       |                        |                        |                        |                  |              |

|                 |            | uto-shutdown is                      |                        |                        |                        |                  |              |

|                 |            | auto-shutdown is                     |                        |                        | •                      |                  |              |

| bit 2           |            | PSMCx Output 0                       |                        |                        |                        |                  |              |

|                 |            | auto-shutdown is                     |                        |                        |                        |                  |              |

|                 |            | auto-shutdown is                     |                        |                        | C C                    |                  |              |

| bit 1           |            | PSMCx Output E                       |                        |                        |                        |                  |              |

|                 |            | auto-shutdown is                     |                        |                        | •                      |                  |              |

|                 |            | auto-shutdown is                     |                        |                        | •                      |                  |              |

| bit 0           |            | PSMCx Output A                       |                        |                        |                        |                  |              |

|                 |            | auto-shutdown is<br>auto-shutdown is |                        |                        |                        |                  |              |

|                 |            |                                      | s assence, pin         |                        |                        |                  |              |

### REGISTER 24-16: PSMCxASDL: PSMC AUTO-SHUTDOWN OUTPUT LEVEL REGISTER

**Note 1:** These bits are not implemented on PSMC2.

# 26.2 SPI Mode Overview

The Serial Peripheral Interface (SPI) bus is a synchronous serial data communication bus that operates in Full-Duplex mode. Devices communicate in a master/slave environment where the master device initiates the communication. A slave device is controlled through a Chip Select known as Slave Select.

The SPI bus specifies four signal connections:

- Serial Clock (SCK)

- Serial Data Out (SDO)

- Serial Data In (SDI)

- Slave Select (SS)

Figure 26-1 shows the block diagram of the MSSP module when operating in SPI mode.

The SPI bus operates with a single master device and one or more slave devices. When multiple slave devices are used, an independent Slave Select connection is required from the master device to each slave device.

Figure 26-4 shows a typical connection between a master device and multiple slave devices.

The master selects only one slave at a time. Most slave devices have tri-state outputs so their output signal appears disconnected from the bus when they are not selected.

Transmissions involve two shift registers, 8 bits in size, one in the master and one in the slave. With either the master or the slave device, data is always shifted out one bit at a time, with the Most Significant bit (MSb) shifted out first. At the same time, a new Least Significant bit (LSb) is shifted into the same register.

Figure 26-5 shows a typical connection between two processors configured as master and slave devices.

Data is shifted out of both shift registers on the programmed clock edge and latched on the opposite edge of the clock.

The master device transmits information out on its SDO output pin which is connected to, and received by, the slave's SDI input pin. The slave device transmits information out on its SDO output pin, which is connected to, and received by, the master's SDI input pin.

To begin communication, the master device first sends out the clock signal. Both the master and the slave devices should be configured for the same clock polarity.

The master device starts a transmission by sending out the MSb from its shift register. The slave device reads this bit from that same line and saves it into the LSb position of its shift register. During each SPI clock cycle, a full-duplex data transmission occurs. This means that while the master device is sending out the MSb from its shift register (on its SDO pin) and the slave device is reading this bit and saving it as the LSb of its shift register, that the slave device is also sending out the MSb from its shift register (on its SDO pin) and the master device is reading this bit and saving it as the LSb of its shift register.

After 8 bits have been shifted out, the master and slave have exchanged register values.

If there is more data to exchange, the shift registers are loaded with new data and the process repeats itself.

Whether the data is meaningful or not (dummy data), depends on the application software. This leads to three scenarios for data transmission:

- Master sends useful data and slave sends dummy data.

- Master sends useful data and slave sends useful data.

- Master sends dummy data and slave sends useful data.

Transmissions may involve any number of clock cycles. When there is no more data to be transmitted, the master stops sending the clock signal and it deselects the slave.

Every slave device connected to the bus that has not been selected through its slave select line must disregard the clock and transmission signals and must not transmit out any data of its own.

# 26.6 I<sup>2</sup>C Master Mode

Master mode is enabled by setting and clearing the appropriate SSPM bits in the SSPCON1 register and by setting the SSPEN bit. In Master mode, the SDA and SCK pins must be configured as inputs. The MSSP peripheral hardware will override the output driver TRIS controls when necessary to drive the pins low.

Master mode of operation is supported by interrupt generation on the detection of the Start and Stop conditions. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the  $I^2C$  bus may be taken when the P bit is set, or the bus is Idle.

In Firmware Controlled Master mode, user code conducts all I<sup>2</sup>C bus operations based on Start and Stop bit condition detection. Start and Stop condition detection is the only active circuitry in this mode. All other communication is done by the user software directly manipulating the SDA and SCL lines.

The following events will cause the SSP Interrupt Flag bit, SSP1IF, to be set (SSP interrupt, if enabled):

- Start condition detected

- · Stop condition detected

- Data transfer byte transmitted/received

- Acknowledge transmitted/received

- Repeated Start generated

- Note 1: The MSSP module, when configured in I<sup>2</sup>C Master mode, does not allow queueing of events. For instance, the user is not allowed to initiate a Start condition and immediately write the SSPBUF register to initiate transmission before the Start condition is complete. In this case, the SSPBUF will not be written to and the WCOL bit will be set, indicating that a write to the SSPBUF did not occur

- 2: When in Master mode, Start/Stop detection is masked and an interrupt is generated when the SEN/PEN bit is cleared and the generation is complete.

#### 26.6.1 I<sup>2</sup>C MASTER MODE OPERATION

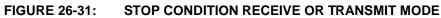

The master device generates all of the serial clock pulses and the Start and Stop conditions. A transfer is ended with a Stop condition or with a Repeated Start condition. Since the Repeated Start condition is also the beginning of the next serial transfer, the I<sup>2</sup>C bus will not be released.

In Master Transmitter mode, serial data is output through SDA, while SCL outputs the serial clock. The first byte transmitted contains the slave address of the receiving device (7 bits) and the Read/Write (R/W) bit. In this case, the R/W bit will be logic '0'. Serial data is transmitted 8 bits at a time. After each byte is transmitted, an Acknowledge bit is received. Start and Stop conditions are output to indicate the beginning and the end of a serial transfer.

In Master Receive mode, the first byte transmitted contains the slave address of the transmitting device (7 bits) and the R/W bit. In this case, the R/W bit will be logic '1'. Thus, the first byte transmitted is a 7-bit slave address followed by a '1' to indicate the receive bit. Serial data is received via SDA, while SCL outputs the serial clock. Serial data is received 8 bits at a time. After each byte is received, an Acknowledge bit is transmitted. Start and Stop conditions indicate the beginning and end of transmission.

A Baud Rate Generator is used to set the clock frequency output on SCL. See **Section 26.7 "Baud Rate Generator"** for more detail.

# 26.6.10 SLEEP OPERATION

While in Sleep mode, the I<sup>2</sup>C slave module can receive addresses or data and when an address match or complete byte transfer occurs, wake the processor from Sleep (if the MSSP interrupt is enabled).

# 26.6.11 EFFECTS OF A RESET

A Reset disables the MSSP module and terminates the current transfer.

# 26.6.12 MULTI-MASTER MODE

In Multi-Master mode, the interrupt generation on the detection of the Start and Stop conditions allows the determination of when the bus is free. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the I<sup>2</sup>C bus may be taken when the P bit of the SSPSTAT register is set, or the bus is Idle, with both the S and P bits clear. When the bus is busy, enabling the SSP interrupt will generate the interrupt when the Stop condition occurs.

In multi-master operation, the SDA line must be monitored for arbitration to see if the signal level is the expected output level. This check is performed by hardware with the result placed in the BCL1IF bit.

The states where arbitration can be lost are:

- Address Transfer

- Data Transfer

- A Start Condition

- A Repeated Start Condition

- An Acknowledge Condition

### 26.6.13 MULTI -MASTER COMMUNICATION, BUS COLLISION AND BUS ARBITRATION

Multi-Master mode support is achieved by bus arbitration. When the master outputs address/data bits onto the SDA pin, arbitration takes place when the master outputs a '1' on SDA, by letting SDA float high and another master asserts a '0'. When the SCL pin floats high, data should be stable. If the expected data on SDA is a '1' and the data sampled on the SDA pin is '0', then a bus collision has taken place. The master will set the Bus Collision Interrupt Flag, BCL1IF and reset the I<sup>2</sup>C port to its Idle state (Figure 26-31).

If a transmit was in progress when the bus collision occurred, the transmission is halted, the BF flag is cleared, the SDA and SCL lines are deasserted and the SSPBUF can be written to. When the user services the bus collision Interrupt Service Routine and if the  $I^2C$  bus is free, the user can resume communication by asserting a Start condition.

If a Start, Repeated Start, Stop or Acknowledge condition was in progress when the bus collision occurred, the condition is aborted, the SDA and SCL lines are deasserted and the respective control bits in the SSPCON2 register are cleared. When the user services the bus collision Interrupt Service Routine and if the I<sup>2</sup>C bus is free, the user can resume communication by asserting a Start condition.

The master will continue to monitor the SDA and SCL pins. If a Stop condition occurs, the SSP1IF bit will be set.

A write to the SSPBUF will start the transmission of data at the first data bit, regardless of where the transmitter left off when the bus collision occurred.

In Multi-Master mode, the interrupt generation on the detection of Start and Stop conditions allows the determination of when the bus is free. Control of the  $I^2C$  bus can be taken when the P bit is set in the SSPSTAT register, or the bus is Idle and the S and P bits are cleared.

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                                   |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                                                       |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                                                                                                                                                                              |

| Operation:       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                                                               |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                     |

| Description:     | The contents of register 'f' are<br>decremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'.<br>If the result is '1', the next<br>instruction is executed. If the<br>result is '0', then a NOP is<br>executed instead, making it a<br>2-cycle instruction. |

| GOTO             | Unconditional Branch                                                                                                                                                                       |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                    |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                       |

| Operation:       | $k \rightarrow PC<10:0>$<br>PCLATH<6:3> $\rightarrow$ PC<14:11>                                                                                                                            |

| Status Affected: | None                                                                                                                                                                                       |

| Description:     | GOTO is an unconditional branch.<br>The 11-bit immediate value is<br>loaded into PC bits <10:0>. The<br>upper bits of PC are loaded from<br>PCLATH<4:3>. GOTO is a 2-cycle<br>instruction. |

| INCF             | Increment f                                                                                                                                                                |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] INCF f,d                                                                                                                                                           |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                            |

| Operation:       | (f) + 1 $\rightarrow$ (destination)                                                                                                                                        |

| Status Affected: | Z                                                                                                                                                                          |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'. |

| INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                              |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] INCFSZ f,d                                                                                                                                                                                                                                                                                                                  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                                                                                                                                     |

| Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                                                          |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'.<br>If the result is '1', the next<br>instruction is executed. If the<br>result is '0', a NOP is executed<br>instead, making it a 2-cycle<br>instruction. |

| IORLW                | Inclusive OR literal with W                                                                                                   |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------|

|                      |                                                                                                                               |

| Syntax:              | [ <i>label</i> ] IORLW k                                                                                                      |

| Operands:            | $0 \le k \le 255$                                                                                                             |

| Operation:           | (W) .OR. $k \rightarrow$ (W)                                                                                                  |

| Status Affected:     | Z                                                                                                                             |

| Description:         | The contents of the W register are OR'ed with the 8-bit literal 'k'. The result is placed in the W register.                  |

|                      |                                                                                                                               |

| IORWF                | Inclusive OR W with f                                                                                                         |

| IORWF<br>Syntax:     | Inclusive OR W with f [ label ] IORWF f,d                                                                                     |

|                      | $[ \textit{label} ]  \text{IORWF}  f,d \\ 0 \le f \le 127$                                                                    |

| Syntax:              | [ <i>label</i> ] IORWF f,d                                                                                                    |

| Syntax:              | $[ \textit{label} ]  \text{IORWF}  f,d \\ 0 \le f \le 127$                                                                    |

| Syntax:<br>Operands: | $ \begin{array}{l} \mbox{[label]} & \mbox{IORWF} & \mbox{f,d} \\ \mbox{0} \leq f \leq 127 \\ \mbox{d} \in [0,1] \end{array} $ |

| MOVIW      | Move INDFn to W                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:    | [ <i>label</i> ] MOVIW ++FSRn<br>[ <i>label</i> ] MOVIWFSRn<br>[ <i>label</i> ] MOVIW FSRn++<br>[ <i>label</i> ] MOVIW FSRn<br>[ <i>label</i> ] MOVIW k[FSRn]                                                                                                                                                                                                                                                                                           |

| Operands:  | $\begin{array}{l} n \in [0,1] \\ mm \in [00,01,10,11] \\ -32 \leq k \leq 31 \end{array}$                                                                                                                                                                                                                                                                                                                                                                |

| Operation: | $\begin{split} &\text{INDFn} \rightarrow W \\ &\text{Effective address is determined by} \\ &\text{•} \ &\text{FSR + 1 (preincrement)} \\ &\text{•} \ &\text{FSR - 1 (predecrement)} \\ &\text{•} \ &\text{FSR + k (relative offset)} \\ &\text{After the Move, the FSR value will} \\ &\text{be either:} \\ &\text{•} \ &\text{FSR + 1 (all increments)} \\ &\text{•} \ &\text{FSR - 1 (all decrements)} \\ &\text{•} \ &\text{Unchanged} \end{split}$ |

Status Affected: Ζ

| Mode          | Syntax | mm |

|---------------|--------|----|

| Preincrement  | ++FSRn | 00 |

| Predecrement  | FSRn   | 01 |

| Postincrement | FSRn++ | 10 |

| Postdecrement | FSRn   | 11 |

Description:

This instruction is used to move data between W and one of the indirect registers (INDFn). Before/ after this move, the pointer (FSRn) is updated by pre/post incrementing/decrementing it.

**Note:** The INDFn registers are not physical registers. Any instruction that accesses an INDFn register actually accesses the register at the address specified by the FSRn.

FSRn is limited to the range 0000h - FFFFh. Incrementing/ decrementing it beyond these bounds will cause it to wraparound.

| MOVLB                | Move literal to BSR                                                  |

|----------------------|----------------------------------------------------------------------|

| Syntax:              | [ <i>label</i> ] MOVLB k                                             |

| Operands:            | $0 \le k \le 31$                                                     |

| Operation:           | $k \rightarrow BSR$                                                  |

| Status Affected:     | None                                                                 |

| Description:         | The 5-bit literal 'k' is loaded into the Bank Select Register (BSR). |

| MOVLP                | Move literal to PCLATH                                               |

|                      |                                                                      |

| Syntax:              | [ <i>label</i> ]MOVLP k                                              |

| Syntax:<br>Operands: | [ <i>label</i> ] MOVLP   k<br>0 ≤ k ≤ 127                            |

| 5                    |                                                                      |

| Operands:            | $0 \le k \le 127$                                                    |

| MOVLW            | Move literal to W                                                                         |

|------------------|-------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVLW k                                                                  |

| Operands:        | $0 \le k \le 255$                                                                         |

| Operation:       | $k \rightarrow (W)$                                                                       |

| Status Affected: | None                                                                                      |

| Description:     | The 8-bit literal 'k' is loaded into W register. The "don't cares" will assemble as '0's. |

| Words:           | 1                                                                                         |

| Cycles:          | 1                                                                                         |

| Example:         | MOVLW 0x5A                                                                                |

|                  | After Instruction<br>W = 0x5A                                                             |

| MOVWF            | Move W to f                                                                                               |

|------------------|-----------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] MOVWF f                                                                                           |

| Operands:        | $0 \leq f \leq 127$                                                                                       |

| Operation:       | $(W) \rightarrow (f)$                                                                                     |

| Status Affected: | None                                                                                                      |

| Description:     | Move data from W register to register 'f'.                                                                |

| Words:           | 1                                                                                                         |

| Cycles:          | 1                                                                                                         |

| Example:         | MOVWF OPTION_REG                                                                                          |

|                  | Before Instruction<br>OPTION_REG = 0xFF<br>W = 0x4F<br>After Instruction<br>OPTION_REG = 0x4F<br>W = 0x4F |

#### TABLE 30-4: I/O PORTS

| Param<br>No. | Sym. | Characteristic                            | Min.              | Тур† | Max.     | Units | Conditions                                                              |  |  |

|--------------|------|-------------------------------------------|-------------------|------|----------|-------|-------------------------------------------------------------------------|--|--|

|              | VIL  | Input Low Voltage                         |                   |      |          |       |                                                                         |  |  |

|              |      | I/O PORT:                                 |                   |      |          |       |                                                                         |  |  |

| D034         |      | with TTL buffer                           | —                 | _    | 0.8      | V     | $4.5V \leq V\text{DD} \leq 5.5V$                                        |  |  |

| D034A        |      |                                           |                   | _    | 0.15 VDD | V     | $1.8V \leq V\text{DD} \leq 4.5V$                                        |  |  |

| D035         |      | with Schmitt Trigger buffer               |                   | _    | 0.2 VDD  | V     | $2.0V \le V\text{DD} \le 5.5V$                                          |  |  |

|              |      | with I <sup>2</sup> C <sup>™</sup> levels |                   | _    | 0.3 VDD  | V     |                                                                         |  |  |

|              |      | with SMBus levels                         |                   | _    | 0.8      | V     | $2.7V \le V\text{DD} \le 5.5V$                                          |  |  |

| D036         |      | MCLR, OSC1 (RC mode) <sup>(1)</sup>       | _                 | _    | 0.2 VDD  | V     |                                                                         |  |  |

| D036A        |      | OSC1 (HS mode)                            | —                 | _    | 0.3 Vdd  | V     |                                                                         |  |  |

|              | VIH  | Input High Voltage                        |                   |      | •        | •     | •                                                                       |  |  |

|              |      | I/O ports:                                |                   |      |          |       |                                                                         |  |  |

| D040         |      | with TTL buffer                           | 2.0               | _    | _        | V     | $4.5V \leq V\text{DD} \leq 5.5V$                                        |  |  |

| D040A        |      |                                           | 0.25 VDD +<br>0.8 | _    | —        | V     | $1.8V \leq V\text{DD} \leq 4.5V$                                        |  |  |

| D041         |      | with Schmitt Trigger buffer               | 0.8 VDD           |      |          | V     | $2.0V \le V\text{DD} \le 5.5V$                                          |  |  |

|              |      | with I <sup>2</sup> C <sup>™</sup> levels | 0.7 Vdd           | _    | _        | V     |                                                                         |  |  |

|              |      | with SMBus levels                         | 2.1               | _    | —        | V     | $2.7V \le V\text{DD} \le 5.5V$                                          |  |  |

| D042         |      | MCLR                                      | 0.8 Vdd           | _    | —        | V     |                                                                         |  |  |

| D043A        |      | OSC1 (HS mode)                            | 0.7 Vdd           | _    | —        | V     |                                                                         |  |  |

| D043B        |      | OSC1 (RC mode)                            | 0.9 Vdd           | _    | —        | V     | (Note 1)                                                                |  |  |

|              | lı∟  | Input Leakage Current <sup>(2)</sup>      |                   |      |          |       |                                                                         |  |  |

| D060         |      | I/O ports                                 | —                 | ± 5  | ± 125    | nA    | $Vss \le VPIN \le VDD$ , Pin at high-impedance @ 85°C                   |  |  |

|              |      |                                           |                   | ± 5  | ± 1000   | nA    | 125°C                                                                   |  |  |

| D061         |      | MCLR <sup>(3)</sup>                       | —                 | ± 50 | ± 200    | nA    | $Vss \le Vpin \le Vdd @ 85^{\circ}C$                                    |  |  |

|              | IPUR | Weak Pull-up Current                      |                   |      |          | -     |                                                                         |  |  |

| D070*        |      |                                           | 25                | 100  | 200      |       | VDD = 3.3V, VPIN = VSS                                                  |  |  |

|              |      |                                           | 25                | 140  | 300      | μA    | VDD = 5.0V, VPIN = VSS                                                  |  |  |

|              | Vol  | Output Low Voltage <sup>(4)</sup>         |                   |      |          |       |                                                                         |  |  |

| D080         |      | I/O ports                                 | —                 | _    | 0.6      | v     | IOL = 8mA, VDD = 5V<br>IOL = 6mA, VDD = 3.3V<br>IOL = 1.8mA, VDD = 1.8V |  |  |

|              | Voн  | Output High Voltage <sup>(4)</sup>        | 1 1               |      | 1        | 1     | 1                                                                       |  |  |

| D090         |      | I/O ports                                 | VDD - 0.7         | _    | _        | V     | ІОН = 3.5mA, VDD = 5V<br>ІОН = 3mA, VDD = 3.3V<br>ІОН = 1mA, VDD = 1.8V |  |  |

These parameters are characterized but not tested.

t Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended to use an external clock in RC mode.

2: Negative current is defined as current sourced by the pin.

3: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

4: Including OSC2 in CLKOUT mode.

Note: Unless otherwise noted, VIN = 5V, Fosc = 300 kHz, CIN = 0.1  $\mu$ F, TA = 25°C.

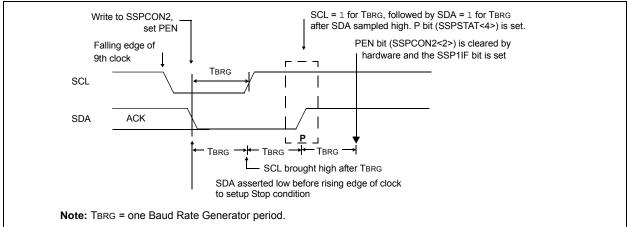

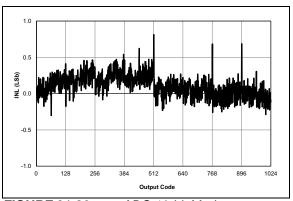

**FIGURE 31-79:** ADC 10-bit Mode, Single-Ended INL, VDD = 3.0V, TAD =  $1 \mu$ S,  $25^{\circ}$ C.

**FIGURE 31-80:** ADC 10-bit Mode, Single-Ended INL, VDD = 3.0V, TAD =  $4 \mu$ S,  $25^{\circ}$ C.

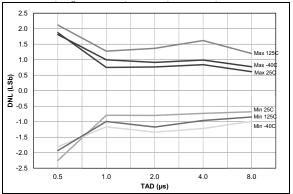

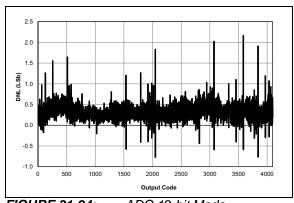

FIGURE 31-81: ADC 10-bit Mode, Single-Ended DNL, VDD = 3.0V, VREF = 3.0V.

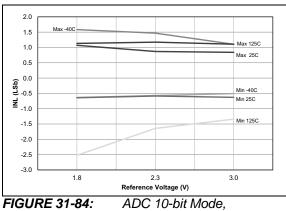

**FIGURE 31-83:** ADC 10-bit Mode, Single-Ended DNL, VDD = 3.0V,  $TAD = 1 \mu S$ .

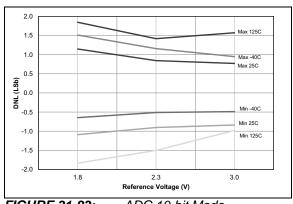

FIGURE 31-82: ADC 10-bit Mode, Single-Ended INL, VDD = 3.0V, VREF = 3.0V.

Single-Ended INL, VDD = 3.0V,  $TaD = 1 \ \mu$ S.

Note: Unless otherwise noted, VIN = 5V, Fosc = 300 kHz, CIN = 0.1  $\mu$ F, TA = 25°C.

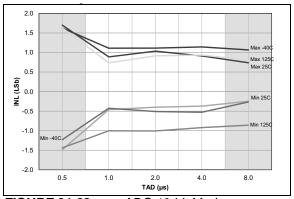

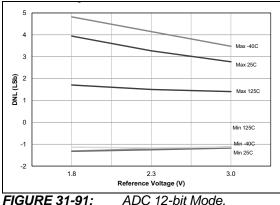

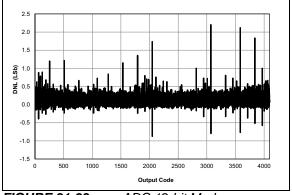

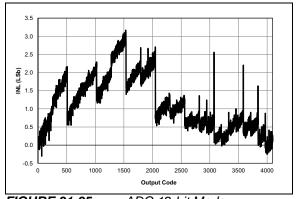

**FIGURE 31-91:** ADC 12-bit Mode, Single-Ended DNL, VDD = 3.0V,  $TAD = 1 \ \mu$ S.

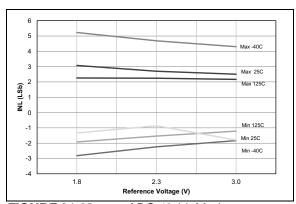

**FIGURE 31-92:** ADC 12-bit Mode, Single-Ended INL, VDD = 3.0V, TAD =  $1 \mu S$ .

**FIGURE 31-93:** ADC 12-bit Mode, Single-Ended DNL, VDD = 5.5V, TAD = 1  $\mu$ S, 25°C.

**FIGURE 31-94:** ADC 12-bit Mode, Single-Ended DNL, VDD = 5.5V, TAD =  $4 \mu$ S, 25°C.

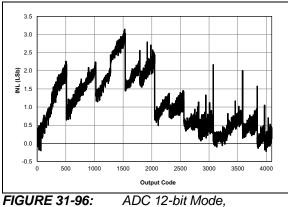

**FIGURE 31-95:** ADC 12-bit Mode, Single-Ended INL, VDD = 5.5V, TAD = 1  $\mu$ S, 25°C.

**FIGURE 31-96:** ADC 12-bit Mode, Single-Ended INL, VDD = 5.5V, TAD = 4  $\mu$ S, 25°C.

# APPENDIX A: DATA SHEET REVISION HISTORY

# Revision A (06/2012)

Initial release.

# **Revision B (11/2012)**

Minor updates.

# Revision C (08/2014)

Change from Preliminary to Final data sheet.

Corrected the following Tables: Family Types Table on page 3, Table 3-3, Table 3-8, Table 20-3, Table 22-2, Table 22-3, Table 23-1, Table 25-3, Table 30-1, Table 30-2, Table 30-3, Table 30-6, Table 30-7, Table 30-13, Table 30-14, Table 30-15, Table 30-16, Table 30-20.

Corrected the following Sections: Section 3.2, Section 9.2, Section 13.3, Section 17.1.6, Section 15.1, Section 15.3, Section 17.2.5, Section 18.2, Section 18.3, Section 19.0, Section 22.6.5, Section 22.9, Section 23.0, Section 23.1, Section 24.2.4, Section 24.2.5, Section 24.2.7, Section 24.8, Section 25.0, Section 26.6.7.4, Section 30.3.

Corrected the following Registers: Register 4-2, Register 8-2, Register 8-5, Register 17-3, Register 18-1, Register 24-3, Register 24-4.

Corrected Equation 17-1.

Corrected Figure 30-9. Removed Figure 24-21.