#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 32MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, POR, PSMC, PWM, WDT                              |

| Number of I/O              | 35                                                                       |

| Program Memory Size        | 14KB (8K x 14)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 1K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                              |

| Data Converters            | A/D 14x12b; D/A 1x8b                                                     |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                 |

| Supplier Device Package    | 40-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1787-e-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| IADE |             |             |             |            |      |           | · ·                                  | - ( )   | , , ,     |        | /      |      |          |            |           |         |             |

|------|-------------|-------------|-------------|------------|------|-----------|--------------------------------------|---------|-----------|--------|--------|------|----------|------------|-----------|---------|-------------|

| Q    | 40-Pin PDIP | 40-Pin UQFN | 44-Pin TQFP | 44-Pin QFN | ADC  | Reference | Comparator                           | Op Amps | 8-bit DAC | Timers | PSMC   | ССР  | EUSART   | MSSP       | Interrupt | dn-IInd | Basic       |

| RC1  | 16          | 31          | 35          | 35         | —    |           |                                      | —       | —         | T10SI  | PSMC1B | CCP2 | —        | —          | IOC       | Y       | _           |

| RC2  | 17          | 32          | 36          | 36         | —    | —         |                                      | _       | —         | _      | PSMC1C | CCP1 | —        | _          | IOC       | Y       |             |

| RC3  | 18          | 33          | 37          | 37         | —    | —         |                                      | -       | —         | _      | PSMC1D | _    | _        | SCL<br>SCK | IOC       | Y       | —           |

| RC4  | 23          | 38          | 42          | 42         | -    | —         | -                                    | -       | _         | -      | PSMC1E | —    |          | SDI<br>SDA | IOC       | Y       | —           |

| RC5  | 24          | 39          | 43          | 43         | —    | —         | —                                    | —       | _         | —      | PSMC1F | —    | —        | SDO        | IOC       | Y       | —           |

| RC6  | 25          | 40          | 44          | 44         | —    | —         | -                                    | -       | —         |        | PSMC2A | -    | TX<br>CK | —          | IOC       | Y       | —           |

| RC7  | 26          | 1           | 1           | 1          | -    | —         |                                      | —       | _         | —      | PSMC2B | —    | RX<br>DT | —          | IOC       | Y       | —           |

| RD0  | 19          | 34          | 38          | 38         | —    | —         | -                                    | OPA3IN+ | _         | —      | —      | _    | _        | _          | —         | Y       | —           |

| RD1  | 20          | 35          | 39          | 39         | AN21 | _         | C1IN4-<br>C2IN4-<br>C3IN4-<br>C4IN4- | OPA3OUT | _         |        | _      | _    | _        | _          | _         | Y       | _           |

| RD2  | 21          | 36          | 40          | 40         | —    | —         | -                                    | OPA3IN- | _         | —      | —      | —    | —        | _          | —         | Y       | _           |

| RD3  | 22          | 37          | 41          | 41         | —    | _         | _                                    | —       | _         | —      | —      | _    | —        | —          | _         | Y       |             |

| RD4  | 27          | 2           | 2           | 2          | —    | —         | _                                    |         | _         | —      | PSMC3F | —    | —        |            | —         | Y       | —           |

| RD5  | 28          | 3           | 3           | 3          | —    |           | _                                    | —       | _         | —      | PSMC3E | —    | —        |            | —         | Y       |             |

| RD6  | 29          | 4           | 4           | 4          |      | —         | C3OUT                                | —       | _         | —      | PSMC3D | —    | —        | —          |           | Y       | —           |

| RD7  | 30          | 5           | 5           | 5          | —    | —         | C4OUT                                | -       | _         | -      | PSMC3C | _    | _        | _          |           | Y       | _           |

| RE0  | 8           | 23          | 25          | 25         | AN5  | —         | —                                    | _       | _         | —      | —      | CCP3 | —        | _          | —         | Y       | —           |

| RE1  | 9           | 24          | 26          | 26         | AN6  |           | _                                    | -       | _         | -      | PSMC3B | _    | _        | _          |           | Y       | _           |

| RE2  | 10          | 25          | 27          | 27         | AN7  | —         | —                                    |         |           | —      | PSMC3A | —    | -        | —          | —         | Y       | —           |

| RE3  | 1           | 16          | 18          | 18         | —    | —         | -                                    | —       | —         | —      | —      | —    | —        | —          | IOC       | Y       | MCLR<br>VPP |

| VDD  | 11,32       | 7,26        | 7,28        | 7,8,<br>28 | -    | —         |                                      | —       | —         | —      | —      | —    | -        | —          | -         |         | Vdd         |

| Vss  | 12,31       | 6,27        | 6,29        | 6,30,      | —    | _         | -                                    | —       | _         | —      | —      | —    | —        | _          | —         | _       | Vss         |

|      |             |             |             |            |      |           |                                      |         |           |        |        |      |          |            |           |         |             |

## TABLE 2: 40/44-PIN ALLOCATION TABLE (PIC16(L)F1784/7) (Continued)

Note 1: Alternate pin function selected with the APFCON1 (Register 13-1) and APFCON2 (Register 13-2) registers.

## 3.1.1 READING PROGRAM MEMORY AS DATA

There are two methods of accessing constants in program memory. The first method is to use tables of RETLW instructions. The second method is to set an FSR to point to the program memory.

### 3.1.1.1 RETLW Instruction

The RETLW instruction can be used to provide access to tables of constants. The recommended way to create such a table is shown in Example 3-1.

EXAMPLE 3-1: RETLW INSTRUCTION

| constants         |                     |

|-------------------|---------------------|

| BRW               | ;Add Index in W to  |

|                   | ;program counter to |

|                   | ;select data        |

| RETLW DATA0       | ;Index0 data        |

| RETLW DATA1       | ;Index1 data        |

| RETLW DATA2       |                     |

| RETLW DATA3       |                     |

|                   |                     |

|                   |                     |

| my_function       |                     |

| ; LOTS OF CODE    |                     |

| MOVLW DATA_IN     | DEX                 |

| call constants    |                     |

| ; THE CONSTANT IS | IN W                |

|                   |                     |

The BRW instruction makes this type of table very simple to implement. If your code must remain portable with previous generations of microcontrollers, then the BRW instruction is not available so the older table read method must be used.

## 3.1.1.2 Indirect Read with FSR

The program memory can be accessed as data by setting bit 7 of the FSRxH register and reading the matching INDFx register. The MOVIW instruction will place the lower 8 bits of the addressed word in the W register. Writes to the program memory cannot be performed via the INDF registers. Instructions that access the program memory via the FSR require one extra instruction cycle to complete. Example 3-2 demonstrates accessing the program memory via an FSR.

The high directive will set bit<7> if a label points to a location in program memory.

### EXAMPLE 3-2: ACCESSING PROGRAM MEMORY VIA FSR

| constants   |              |         |      |

|-------------|--------------|---------|------|

| RETLW I     | DATA0        | ;Index0 | data |

| RETLW I     | DATA1        | ;Index1 | data |

| RETLW I     | DATA2        |         |      |

| RETLW I     | DATA3        |         |      |

| my_functio  | n            |         |      |

| ; LOTS      | S OF CODE    |         |      |

| MOVLW       | LOW constan  | ts      |      |

| MOVWF       | FSR1L        |         |      |

| MOVLW       | HIGH consta  | nts     |      |

| MOVWF       | FSR1H        |         |      |

| MOVIW       | 0[FSR1]      |         |      |

| ; THE PROGR | AM MEMORY IS | IN W    |      |

## TABLE 3-12: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

| Addr       | Name    | Bit 7        | Bit 6         | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|------------|---------|--------------|---------------|-------|-------|-------|-------|-------|-------|----------------------|---------------------------------|

| Bank       | c 11-15 |              |               |       |       |       |       |       |       |                      |                                 |

| x0Ch       |         |              |               |       |       |       |       |       |       |                      |                                 |

| or<br>x8Ch |         |              |               |       |       |       |       |       |       |                      |                                 |

| to         | _       | Unimplemente | Inimplemented |       |       |       |       |       |       | _                    | _                               |

| x6Fh       |         |              |               |       |       |       |       |       |       |                      |                                 |

| or<br>xEFh |         |              |               |       |       |       |       |       |       |                      |                                 |

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

**1:** These registers can be addressed from any bank.

**2:** Unimplemented, read as '1'.

3: PIC16(L)F1784/7 only.

Note

4: PIC16F1784/6/7 only.

## REGISTER 4-1: CONFIG1: CONFIGURATION WORD 1 (CONTINUED)

- bit 2-0 FOSC<2:0>: Oscillator Selection bits

- 111 = ECH: External Clock, High-Power mode (4-20 MHz): device clock supplied to CLKIN pin

- 110 = ECM: External Clock, Medium-Power mode (0.5-4 MHz): device clock supplied to CLKIN pin

- 101 = ECL: External Clock, Low-Power mode (0-0.5 MHz): device clock supplied to CLKIN pin

- 100 = INTOSC oscillator: I/O function on CLKIN pin

- 011 = EXTRC oscillator: External RC circuit connected to CLKIN pin

- 010 = HS oscillator: High-speed crystal/resonator connected between OSC1 and OSC2 pins

- 001 = XT oscillator: Crystal/resonator connected between OSC1 and OSC2 pins

- 000 = LP oscillator: Low-power crystal connected between OSC1 and OSC2 pins

- **Note 1:** The entire data EEPROM will be erased when the code protection is turned off during an erase.Once the Data Code Protection bit is enabled, (CPD = 0), the Bulk Erase Program Memory Command (through ICSP) can disable the Data Code Protection (CPD =1). When a Bulk Erase Program Memory Command is executed, the entire Program Flash Memory, Data EEPROM and configuration memory will be erased.

| FIGURE 5-3:               | RESET START-UP SEQUENCE                                |

|---------------------------|--------------------------------------------------------|

| VDD                       |                                                        |

| Internal POR              |                                                        |

| Power-up Timer            |                                                        |

| MCLR                      |                                                        |

| Internal RESET            |                                                        |

|                           | Oscillator Modes – – – – – – – – – – – – – – – – – – – |

| External Crystal          | <b>◄</b> Tost►                                         |

| Oscillator Start-up Timer |                                                        |

| Oscillator                |                                                        |

| Fosc_                     |                                                        |

| Internal Oscillator       |                                                        |

| Oscillator                |                                                        |

| Fosc                      |                                                        |

| External Clock (EC)       |                                                        |

| CLKIN                     |                                                        |

| Fosc -                    |                                                        |

|                           |                                                        |

| Name       | Bit 7   | Bit 6    | Bit 5    | Bit 4    | Bit 3  | Bit 2    | Bit 1    | Bit 0    | Register<br>on Page |

|------------|---------|----------|----------|----------|--------|----------|----------|----------|---------------------|

| INTCON     | GIE     | PEIE     | TMR0IE   | INTE     | IOCIE  | TMR0IF   | INTF     | IOCIF    | 93                  |

| OPTION_REG | WPUEN   | INTEDG   | TMR0CS   | TMR0SE   | PSA    | PS<2:0>  |          |          | 198                 |

| PIE1       | TMR1GIE | ADIE     | RCIE     | TXIE     | SSP1IE | CCP1IE   | TMR2IE   | TMR1IE   | 94                  |

| PIE2       | OSFIE   | C2IE     | C1IE     | EEIE     | BCL1IE | C4IE     | C3IE     | CCP2IE   | 95                  |

| PIE3       | _       | _        | _        | CCP3IE   |        |          | _        |          | 96                  |

| PIE4       | _       | PSMC3TIE | PSMC2TIE | PSMC1TIE | —      | PSMC3SIE | PSMC2SIE | PSMC1SIE | 97                  |

| PIR1       | TMR1GIF | ADIF     | RCIF     | TXIF     | SSP1IF | CCP1IF   | TMR2IF   | TMR1IF   | 98                  |

| PIR2       | OSFIF   | C2IF     | C1IF     | EEIF     | BCL1IF | C4IF     | C3IF     | CCP2IF   | 99                  |

| PIR3       |         | _        | _        | CCP3IF   |        |          | _        |          | 100                 |

| PIR4       |         | PSMC3TIF | PSMC2TIF | PSMC1TIF | _      | PSMC3SIF | PSMC2SIF | PSMC1SIF | 101                 |

## TABLE 8-1: SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPTS

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by interrupts.

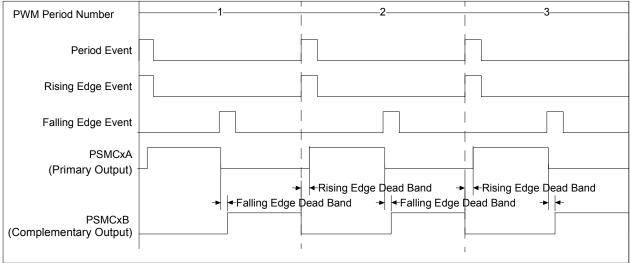

## 24.3.2 COMPLEMENTARY PWM

The complementary PWM uses the same events as the single PWM, but two waveforms are generated instead of only one.

The two waveforms are opposite in polarity to each other. The two waveforms may also have dead-band control as well.

### 24.3.2.1 Mode Features and Controls

- · Dead-band control available

- PWM primary output can be steered to the following pins:

- PSMCxA

- PSMCxC

- PSMCxE

- PWM complementary output can be steered to the following pins:

- PSMCxB

- PSMCxD

- PSMCxE

## 24.3.2.2 Waveform Generation

#### Rising Edge Event

- Complementary output is set inactive

- · Optional rising edge dead band is activated

- · Primary output is set active

## Falling Edge Event

- · Primary output is set inactive

- · Optional falling edge dead band is activated

- Complementary output is set active

Code for setting up the PSMC generate the complementary single-phase waveform shown in Figure 24-5, and given in Example 24-2.

## EXAMPLE 24-2: COMPLEMENTARY SINGLE-PHASE SETUP

Complementary Single-phase PWM PSMC setup ; ; Fully synchronous operation ; Period = 10 us ; Duty cycle = 50% ; Deadband = 93.75 +15.6/-0 ns BANKSEL PSMC1CON MOVLW 0x02 ; set period MOVWF PSMC1PRH MOVLW 0x7FMOVWE PSMC1PRL ; set duty cycle MOVLW 0x01 MOVWF PSMC1DCH MOVLW 0x3F MOVWF PSMC1DCL CLRE PSMC1PHH ; no phase offset CLRF PSMC1PHL MOVLW 0x01 ; PSMC clock=64 MHz MOVWF PSMC1CLK ; output on A, normal polarity MOVLW B'00000011'; A and B enables MOVWF PSMC10EN MOVWF PSMC1STR0 CLRF PSMC1POL ; set time base as source for all events BSF PSMC1PRS, P1PRST BSF PSMC1PHS, P1PHST PSMC1DCS, P1DCST BSF ; set rising and falling dead-band times MOVLW D'6' MOVWF PSMC1DBR MOVWF PSMC1DBF ; enable PSMC in Complementary Single Mode ; this also loads steering and time buffers ; and enables rising and falling deadbands MOVLW B'11110001' PSMC1CON MOVWF BANKSEL TRISC BCF TRISC, 0 ; enable pin drivers BCF TRISC, 1

## FIGURE 24-5: COMPLEMENTARY PWM WAVEFORM – PSMCXSTR0 = 03H

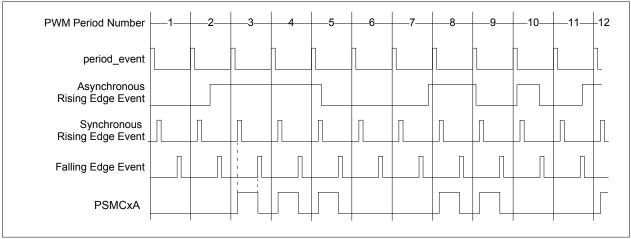

## 24.3.7 PULSE-SKIPPING PWM

The pulse-skipping PWM is used to generate a series of fixed-length pulses that can be triggered at each period event. A rising edge event will be generated when any enabled asynchronous rising edge input is active when the period event occurs, otherwise no event will be generated.

The rising edge event occurs based upon the value in the PSMCxPH register pair.

The falling edge event always occurs according to the enabled event inputs without qualification between any two inputs.

#### 24.3.7.1 Mode Features

- · No dead-band control available

- No steering control available

- PWM is output to only one pin:

- PSMCxA

## 24.3.7.2 Waveform Generation

#### Rising Edge Event

If any enabled asynchronous rising edge event = 1 when there is a period event, then upon the next synchronous rising edge event:

PSMCxA is set active

Falling Edge Event

PSMCxA is set inactive

**Note:** To use this mode, an external source must be used for the determination of whether or not to generate the set pulse. If the phase time base is used, it will either always generate a pulse or never generate a pulse based on the PSMCxPH value.

#### FIGURE 24-10: PULSE-SKIPPING PWM WAVEFORM

| 3-Phase State      | 1   | 2   | 3   | 4   | 5   | 6   |

|--------------------|-----|-----|-----|-----|-----|-----|

| PSMCxSTR0          | 01h | 02h | 04h | 08h | 10h | 20h |

| Period Event       |     |     |     |     |     |     |

| Rising Edge Event  |     |     |     |     |     |     |

| Falling Edge Event |     |     |     |     |     |     |

| PSMCxA (1H)        |     |     |     |     |     |     |

| PSMCxB (1L)        |     |     |     |     |     |     |

| PSMCxC (2H)        |     |     |     |     |     |     |

| PSMCxD (2L)        |     |     |     |     |     |     |

| PSMCxE (3H)        |     |     |     |     |     |     |

| PSMCxF (3L)        |     |     |     |     |     |     |

|                    |     |     |     |     |     |     |

## FIGURE 24-15: 3-PHASE PWM STEERING WAVEFORM (PXHSMEN = 0 AND PXLSMEN = 1)

| R/W-0/0          | U-0          | U-0                               | R/W-0/0        | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0     |  |  |  |

|------------------|--------------|-----------------------------------|----------------|----------------|------------------|------------------|-------------|--|--|--|

| PxPHSIN          | —            | —                                 | PxPHSC4        | PxPHSC3        | PxPHSC2          | PxPHSC1          | PxPHST      |  |  |  |

| bit 7            |              |                                   |                |                |                  |                  | bit (       |  |  |  |

|                  |              |                                   |                |                |                  |                  |             |  |  |  |

| Legend:          |              |                                   |                |                |                  | (2)              |             |  |  |  |

| R = Readable     |              | W = Writable                      |                | •              | mented bit, read |                  |             |  |  |  |

| u = Bit is uncl  | •            | x = Bit is unki                   |                | -n/n = Value a | at POR and BO    | R/Value at all o | ther Resets |  |  |  |

| '1' = Bit is set |              | '0' = Bit is cle                  | ared           |                |                  |                  |             |  |  |  |

| bit 7            |              | MCx Rising F                      | dae Event occ  | urs on PSMCx   | /IN nin          |                  |             |  |  |  |

| bit i            |              | •                                 | •              | SMCxIN pin go  |                  |                  |             |  |  |  |

|                  | 0            | N pin will not o                  |                | , Ç            |                  |                  |             |  |  |  |

| bit 6-5          | Unimplemen   | Unimplemented: Read as '0'        |                |                |                  |                  |             |  |  |  |

| bit 4            | PxPHSC4: P   | SMCx Rising E                     | dge Event oco  | curs on sync_C | C4OUT output     |                  |             |  |  |  |

|                  | 0            | <b>Q</b>                          |                |                | itput goes true  |                  |             |  |  |  |

|                  |              | 40UT will not o                   | •              | •              |                  |                  |             |  |  |  |

| bit 3            |              | -                                 | -              | curs on sync_C |                  |                  |             |  |  |  |

|                  | 0            | dge event will<br>30UT will not c |                |                | itput goes true  |                  |             |  |  |  |

| bit 2            |              |                                   | •              | curs on sync ( |                  |                  |             |  |  |  |

|                  |              | •                                 | •              |                | itput goes true  |                  |             |  |  |  |

|                  | 0            | 20UT will not o                   |                | _              | ilput good li uo |                  |             |  |  |  |

| bit 1            |              |                                   |                |                |                  |                  |             |  |  |  |

|                  | 1 = Rising e |                                   |                |                |                  |                  |             |  |  |  |

|                  | 0 = sync_C   | 10UT will not o                   | ause rising ed | lge event      |                  |                  |             |  |  |  |

| bit 0            | PxPHST: PSI  | MCx Rising Ed                     | ge Event occu  | irs on Time Ba | se match         |                  |             |  |  |  |

|                  | 0            | <b>U</b>                          |                | SMCxTMR = F    | SMCxPH           |                  |             |  |  |  |

|                  | 0 = Time ba  | se will not cau                   | se rising edge | event          |                  |                  |             |  |  |  |

## **REGISTER 24-12: PSMCxPHS: PSMC PHASE SOURCE REGISTER**<sup>(1)</sup>

Note 1: Sources are not mutually exclusive: more than one source can cause a rising edge event.

The 8-bit timer TMR2 register is concatenated with either the 2-bit internal system clock (FOSC), or 2 bits of the prescaler, to create the 10-bit time base. The system clock is used if the Timer2 prescaler is set to 1:1.

When the 10-bit time base matches the CCPRxH and 2-bit latch, then the CCPx pin is cleared (see Figure 25-4).

## 25.3.6 PWM RESOLUTION

The resolution determines the number of available duty cycles for a given period. For example, a 10-bit resolution will result in 1024 discrete duty cycles, whereas an 8-bit resolution will result in 256 discrete duty cycles.

The maximum PWM resolution is 10 bits when PR2 is 255. The resolution is a function of the PR2 register value as shown by Equation 25-4.

## EQUATION 25-4: PWM RESOLUTION

Resolution =

$$\frac{\log[4(PR2 + 1)]}{\log(2)}$$

bits

Note: If the pulse width value is greater than the period the assigned PWM pin(s) will remain unchanged.

| PWM Frequency             | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|---------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescale            | 16       | 4        | 1         | 1         | 1         | 1         |

| PR2 Value                 | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8         | 7         | 6.6       |

| TABLE 25-2: | EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 8 MHz) |

|-------------|--------------------------------------------------------|

|-------------|--------------------------------------------------------|

| PWM Frequency             | 1.22 kHz | 4.90 kHz | 19.61 kHz | 76.92 kHz | 153.85 kHz | 200.0 kHz |

|---------------------------|----------|----------|-----------|-----------|------------|-----------|

| Timer Prescale            | 16       | 4        | 1         | 1         | 1          | 1         |

| PR2 Value                 | 0x65     | 0x65     | 0x65      | 0x19      | 0x0C       | 0x09      |

| Maximum Resolution (bits) | 8        | 8        | 8         | 6         | 5          | 5         |

© 2012-2014 Microchip Technology Inc.

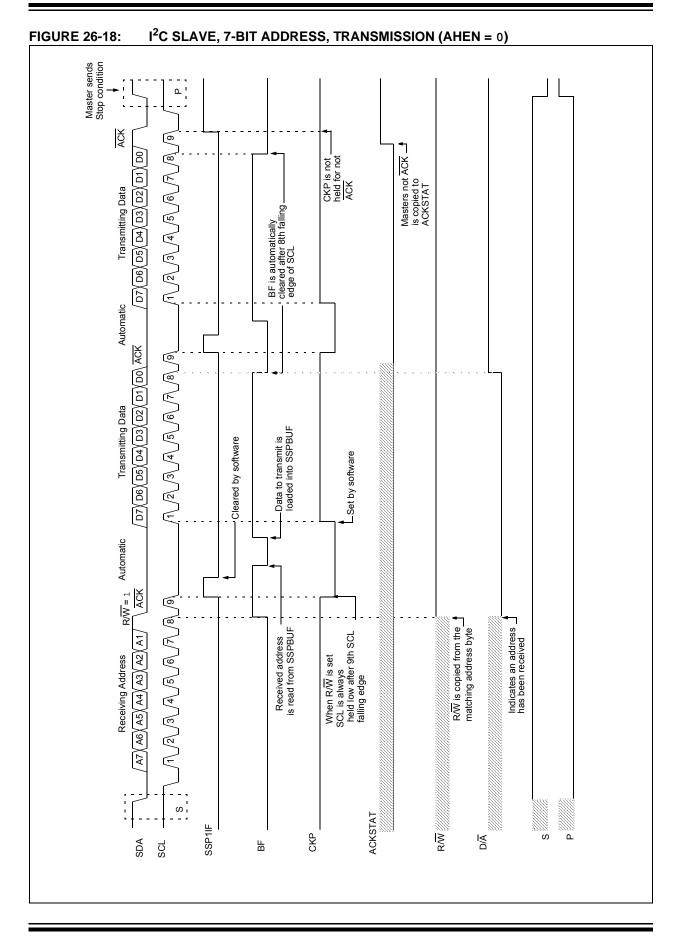

## REGISTER 26-2: SSPCON1: SSP CONTROL REGISTER 1

| R/C/HS-0/0              | R/C/HS-0/0                                                                                                                                                                                                                                                                                                         | R/W-0/0                                                                                                                                   | R/W-0/0                                                                                                                                           | R/W-0/0                                                                                           | R/W-0/0                                                                                      | R/W-0/0                                            | R/W-0/0                                   |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|----------------------------------------------------|-------------------------------------------|

| WCOL                    | SSPOV                                                                                                                                                                                                                                                                                                              | SSPEN                                                                                                                                     | CKP                                                                                                                                               |                                                                                                   | SSPM                                                                                         | I<3:0>                                             |                                           |

| bit 7                   |                                                                                                                                                                                                                                                                                                                    |                                                                                                                                           |                                                                                                                                                   |                                                                                                   |                                                                                              |                                                    | bit C                                     |

|                         |                                                                                                                                                                                                                                                                                                                    |                                                                                                                                           |                                                                                                                                                   |                                                                                                   |                                                                                              |                                                    |                                           |

| Legend:                 |                                                                                                                                                                                                                                                                                                                    |                                                                                                                                           |                                                                                                                                                   |                                                                                                   | ted bit read as (O)                                                                          |                                                    |                                           |

| R = Readable bit        |                                                                                                                                                                                                                                                                                                                    | W = Writable bit                                                                                                                          | -                                                                                                                                                 | •                                                                                                 | ted bit, read as '0'                                                                         | et ell ether Decete                                |                                           |

| u = Bit is unchan       | gea                                                                                                                                                                                                                                                                                                                | x = Bit is unknow                                                                                                                         |                                                                                                                                                   |                                                                                                   | OR and BOR/Value                                                                             |                                                    |                                           |

| 1' = Bit is set         |                                                                                                                                                                                                                                                                                                                    | '0' = Bit is cleared                                                                                                                      | 1                                                                                                                                                 | HS = Bit is set by                                                                                | / hardware                                                                                   | C = User cleared                                   |                                           |

| bit 7                   | 0 = No collision<br><u>Slave mode:</u>                                                                                                                                                                                                                                                                             | ne SSPBUF registe                                                                                                                         |                                                                                                                                                   |                                                                                                   | ions were not valid f<br>vord (must be cleared                                               |                                                    | be started                                |

| bit 6                   | In SPI mode:<br>1 = A new byte<br>Overflow ca<br>setting overflow<br>SSPBUF re<br>0 = No overflow<br>In I <sup>2</sup> C mode:<br>1 = A byte is re                                                                                                                                                                 | n only occur in Slav<br>flow. In Master mode<br>gister (must be clea<br>v<br>eceived while the S<br>eared in software).                   | e SSPBUF registe<br>e mode. In Slave<br>e, the overflow bit i<br>red in software).                                                                | mode, the user musi<br>s not set since each                                                       | revious data. In case<br>t read the SSPBUF, e<br>new reception (and tr<br>revious byte. SSPC | even if only transmitti<br>ansmission) is initiate | ng data, to avoid<br>ed by writing to the |

| bit 5                   | In both modes, w<br>In <u>SPI mode:</u><br>1 = Enables ser<br>0 = Disables se<br><u>In I<sup>2</sup>C mode:</u><br>1 = Enables the                                                                                                                                                                                 | ial port and configur<br>rial port and config                                                                                             | e pins must be proves SCK, SDO, SE<br>ures these pins a<br>igures the SDA an                                                                      | is I/O port pins<br>id SCL pins as the so                                                         | s input or output<br>irce of the serial port<br>purce of the serial por                      | (2)                                                |                                           |

| bit 4                   | 0 = Idle state for<br>In I <sup>2</sup> C Slave mod<br>SCL release cont<br>1 = Enable clock                                                                                                                                                                                                                        | clock is a high leve<br>clock is a low level<br><u>e:</u><br>rol<br>ow (clock stretch). (<br><u>de:</u>                                   |                                                                                                                                                   | lata setup time.)                                                                                 |                                                                                              |                                                    |                                           |

| bit 3-0                 | 0000 = SPI Mast<br>0001 = SPI Mast<br>0010 = SPI Mast<br>0010 = SPI Mast<br>0100 = SPI Slave<br>0101 = SPI Slave<br>0110 = I <sup>2</sup> C Slave<br>1000 = I <sup>2</sup> C Slave<br>1000 = Reservec<br>1010 = Reservec<br>1011 = I <sup>2</sup> C firmw<br>1001 = Reservec<br>1101 = Reservec<br>1101 = Reservec | e mode, 7-bit addre<br>e mode, 10-bit addr<br>er mode, clock = Fo<br>er mode, clock = F<br>are controlled Mas<br>i<br>e mode, 7-bit addre | osc/4<br>osc/16<br>osc/64<br>MR2 output/2<br>K pin, <u>SS</u> pin cor<br>SS<br>ess<br>osc / (4 * (SSPAD<br>ter mode (Slave i<br>ss with Start and | ntrol enabled<br>htrol disabled, <del>SS</del> c<br>DD+1)) <sup>(4)</sup><br>D+1)) <sup>(5)</sup> | an be used as I/O pi<br>enabled<br>enabled                                                   | n                                                  |                                           |

| 2: Wh<br>3: Wh<br>4: SS | Master mode, the over<br>nen enabled, these pi<br>nen enabled, the SDA<br>PADD values of 0, 1<br>PADD value of '0' is                                                                                                                                                                                              | ins must be properl<br>A and SCL pins mu<br>or 2 are not suppo                                                                            | y configured as ir<br>st be configured a<br>rted for I <sup>2</sup> C mode                                                                        | nput or output.<br>as inputs.                                                                     | mission) is initiated                                                                        | by writing to the SS                               | PBUF register.                            |

## REGISTER 26-5: SSPMSK: SSP MASK REGISTER

| R/W-1/1                                 | R/W-1/1                                                                                                                                                                                         | R/W-1/1                                                                                  | R/W-1/1                                               | R/W-1/1                                           | R/W-1/1                      | R/W-1/1 | R/W-1/1 |  |

|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-------------------------------------------------------|---------------------------------------------------|------------------------------|---------|---------|--|

|                                         |                                                                                                                                                                                                 |                                                                                          | MSK                                                   | <7:0>                                             |                              |         |         |  |

| bit 7                                   |                                                                                                                                                                                                 |                                                                                          |                                                       |                                                   |                              |         | bit 0   |  |

|                                         |                                                                                                                                                                                                 |                                                                                          |                                                       |                                                   |                              |         |         |  |

| Legend:                                 |                                                                                                                                                                                                 |                                                                                          |                                                       |                                                   |                              |         |         |  |

| R = Readable                            | e bit                                                                                                                                                                                           | W = Writable                                                                             | bit                                                   | U = Unimplemented bit, read as '0'                |                              |         |         |  |

| u = Bit is unchanged x = Bit is unknown |                                                                                                                                                                                                 | nown                                                                                     | -n/n = Value at POR and BOR/Value at all other Resets |                                                   |                              |         |         |  |

| '1' = Bit is set '0' = Bit is cleared   |                                                                                                                                                                                                 | ared                                                                                     |                                                       |                                                   |                              |         |         |  |

| bit 7-1                                 | MSK<7:1>:                                                                                                                                                                                       | Mask bits                                                                                |                                                       |                                                   |                              |         |         |  |

|                                         | 1 = The received address bit n is compared to SSPADD <n> to detect <math>I^2C</math> address match<br/>0 = The received address bit n is not used to detect <math>I^2C</math> address match</n> |                                                                                          |                                                       |                                                   |                              |         |         |  |

| bit 0                                   | I <sup>2</sup> C Slave me<br>1 = The rec<br>0 = The rec                                                                                                                                         | ask bit for I <sup>2</sup> C S<br>ode, 10-bit addr<br>eived address b<br>eived address b | ess (SSPM<3<br>it 0 is compar<br>it 0 is not use      | 0 = 0111 or<br>ed to SSPADD<br>d to detect $I^2C$ | <0> to detect l <sup>2</sup> |         | tch     |  |

I<sup>2</sup>C Slave mode, 7-bit address, the bit is ignored

'0' = Bit is cleared

## REGISTER 26-6: SSPADD: MSSP ADDRESS AND BAUD RATE REGISTER (I<sup>2</sup>C MODE)

| R/W-0/0                                 | R/W-0/0   | R/W-0/0   | R/W-0/0                            | R/W-0/0       | R/W-0/0          | R/W-0/0      | R/W-0/0  |

|-----------------------------------------|-----------|-----------|------------------------------------|---------------|------------------|--------------|----------|

| 10,00-070                               | 10/00-0/0 | 10,00-0/0 | 10/07-0/0                          | 10,00-0/0     | 10,00-070        | 10,00-0/0    | 10/0/0/0 |

|                                         |           |           | ADD                                | <7:0>         |                  |              |          |

| bit 7                                   |           |           |                                    |               |                  |              | bit 0    |

|                                         |           |           |                                    |               |                  |              |          |

| Legend:                                 |           |           |                                    |               |                  |              |          |

| R = Readable bit W = Writable bit       |           | bit       | U = Unimplemented bit, read as '0' |               |                  |              |          |

| u = Bit is unchanged x = Bit is unknown |           | iown      | -n/n = Value a                     | at POR and BO | R/Value at all o | other Resets |          |

| Master | mode: |  |

|--------|-------|--|

1' = Bit is set

| bit 7-0 | ADD<7:0>: Baud Rate Clock Divider bits          |

|---------|-------------------------------------------------|

|         | SCL pin clock period = ((ADD<7:0> + 1) *4)/Fosc |

## <u>10-Bit Slave mode — Most Significant Address Byte:</u>

- bit 7-3 **Not used:** Unused for Most Significant Address byte. Bit state of this register is a "don't care". Bit pattern sent by master is fixed by I<sup>2</sup>C specification and must be equal to '11110'. However, those bits are compared by hardware and are not affected by the value in this register.

- bit 2-1 ADD<2:1>: Two Most Significant bits of 10-bit address

- bit 0 Not used: Unused in this mode. Bit state is a "don't care".

## <u>10-Bit Slave mode — Least Significant Address Byte:</u>

bit 7-0 ADD<7:0>: Eight Least Significant bits of 10-bit address

## 7-Bit Slave mode:

bit 0 Not used: Unused in this mode. Bit state is a "don't care".

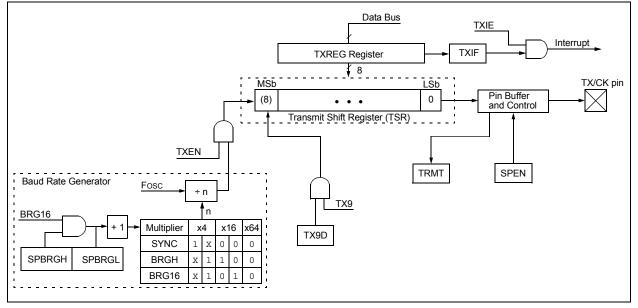

## 27.0 ENHANCED UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (EUSART)

The Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) module is a serial I/O communications peripheral. It contains all the clock generators, shift registers and data buffers necessary to perform an input or output serial data transfer independent of device program execution. The EUSART, also known as a Serial Communications Interface (SCI), can be configured as a full-duplex asynchronous system or half-duplex synchronous system. Full-Duplex mode is useful for communications with peripheral systems, such as CRT terminals and personal computers. Half-Duplex Synchronous mode is intended for communications with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs or other microcontrollers. These devices typically do not have internal clocks for baud rate generation and require the external clock signal provided by a master synchronous device.

The EUSART module includes the following capabilities:

- · Full-duplex asynchronous transmit and receive

- Two-character input buffer

- One-character output buffer

- Programmable 8-bit or 9-bit character length

- · Address detection in 9-bit mode

- · Input buffer overrun error detection

- Received character framing error detection

- Half-duplex synchronous master

- · Half-duplex synchronous slave

- Programmable clock polarity in synchronous modes

- · Sleep operation

The EUSART module implements the following additional features, making it ideally suited for use in Local Interconnect Network (LIN) bus systems:

- · Automatic detection and calibration of the baud rate

- Wake-up on Break reception

- 13-bit Break character transmit

Block diagrams of the EUSART transmitter and receiver are shown in Figure 27-1 and Figure 27-2.

## FIGURE 27-1: EUSART TRANSMIT BLOCK DIAGRAM

| ΜΟΥΨΙ      | Move W to INDFn                                                                                                                                                                                                                                                                                                                                                                                           |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:    | [ <i>label</i> ] MOVWI ++FSRn<br>[ <i>label</i> ] MOVWIFSRn<br>[ <i>label</i> ] MOVWI FSRn++<br>[ <i>label</i> ] MOVWI FSRn<br>[ <i>label</i> ] MOVWI k[FSRn]                                                                                                                                                                                                                                             |

| Operands:  | $\begin{array}{l} n \in [0,1] \\ mm \in [00,01,10,11] \\ -32 \leq k \leq 31 \end{array}$                                                                                                                                                                                                                                                                                                                  |

| Operation: | $\label{eq:statestarding} \begin{split} W &\to INDFn \\ Effective \ address \ is \ determined \ by \\ \bullet \ FSR + 1 \ (preincrement) \\ \bullet \ FSR - 1 \ (predecrement) \\ \bullet \ FSR + k \ (relative \ offset) \\ After \ the \ Move, \ the \ FSR \ value \ will \\ be \ either: \\ \bullet \ FSR + 1 \ (all \ increments) \\ \bullet \ FSR + 1 \ (all \ decrements) \\ Unchanged \end{split}$ |

| Status | Affected: | None |

|--------|-----------|------|

| olulus | / mcolou. |      |

| Mode          | Syntax | mm |

|---------------|--------|----|

| Preincrement  | ++FSRn | 00 |

| Predecrement  | FSRn   | 01 |

| Postincrement | FSRn++ | 10 |

| Postdecrement | FSRn   | 11 |

Description:

This instruction is used to move data between W and one of the indirect registers (INDFn). Before/ after this move, the pointer (FSRn) is updated by pre/post incrementing/decrementing it.

**Note:** The INDFn registers are not physical registers. Any instruction that accesses an INDFn register actually accesses the register at the address specified by the FSRn.

FSRn is limited to the range 0000h - FFFFh. Incrementing/ decrementing it beyond these bounds will cause it to wraparound.

The increment/decrement operation on FSRn WILL NOT affect any Status bits.

| NOP              | No Operation  |

|------------------|---------------|

| Syntax:          | [label] NOP   |

| Operands:        | None          |

| Operation:       | No operation  |

| Status Affected: | None          |

| Description:     | No operation. |

| Words:           | 1             |

| Cycles:          | 1             |

| Example:         | NOP           |

| OPTION           | Load OPTION_REG Register<br>with W                   |

|------------------|------------------------------------------------------|

| Syntax:          | [label] OPTION                                       |

| Operands:        | None                                                 |

| Operation:       | $(W) \to OPTION\_REG$                                |

| Status Affected: | None                                                 |

| Description:     | Move data from W register to<br>OPTION_REG register. |

| RESET            | Software Reset                                                           |  |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [label] RESET                                                            |  |  |  |  |  |  |

| Operands:        | None                                                                     |  |  |  |  |  |  |

| Operation:       | Execute a device Reset. Resets the RI flag of the PCON register.         |  |  |  |  |  |  |

| Status Affected: | None                                                                     |  |  |  |  |  |  |

| Description:     | This instruction provides a way to execute a hardware Reset by software. |  |  |  |  |  |  |

## TABLE 30-3: POWER-DOWN CURRENTS (IPD)<sup>(1,2,4)</sup> (CONTINUED)

| PIC16LF1                                     | 784/6/7                | Operating Conditions: (unless otherwise stated)<br>Low-Power Sleep Mode |      |               |                |       |            |                                 |  |  |  |

|----------------------------------------------|------------------------|-------------------------------------------------------------------------|------|---------------|----------------|-------|------------|---------------------------------|--|--|--|

| PIC16F17                                     | 84/6/7                 | Low-Power Sleep Mode, VREGPM = 1                                        |      |               |                |       |            |                                 |  |  |  |

| Param                                        | Device Characteristics | Min.                                                                    | Тур† | Max.<br>+85°C | Max.<br>+125°C | Units | Conditions |                                 |  |  |  |

| No.                                          |                        |                                                                         |      |               |                |       | Vdd        | Note                            |  |  |  |

| Power-down Base Current (IPD) <sup>(2)</sup> |                        |                                                                         |      |               |                |       |            |                                 |  |  |  |

| D029                                         |                        |                                                                         | 0.05 | 2             | 9              | μA    | 1.8        | ADC Current (Note 3),           |  |  |  |

|                                              |                        | _                                                                       | 0.08 | 3             | 10             | μA    | 3.0        | no conversion in progress       |  |  |  |

| D029                                         |                        |                                                                         | 0.3  | 4             | 12             | μA    | 2.3        | ADC Current (Note 3),           |  |  |  |

|                                              |                        | _                                                                       | 0.4  | 5             | 13             | μA    | 3.0        | no conversion in progress       |  |  |  |

|                                              |                        |                                                                         | 0.5  | 7             | 16             | μA    | 5.0        |                                 |  |  |  |

| D030                                         |                        |                                                                         | 250  | —             | —              | μA    | 1.8        | ADC Current (Note 3),           |  |  |  |

|                                              |                        |                                                                         | 280  | _             | _              | μA    | 3.0        | conversion in progress          |  |  |  |

| D030                                         |                        |                                                                         | 230  | —             | —              | μA    | 2.3        | ADC Current (Note 3, Note 4,    |  |  |  |

|                                              |                        |                                                                         | 250  | —             | —              | μA    | 3.0        | Note 5), conversion in progress |  |  |  |

|                                              |                        | _                                                                       | 350  | —             | —              | μA    | 5.0        |                                 |  |  |  |

| D031                                         |                        |                                                                         | 250  | 650           | —              | μA    | 3.0        | Op Amp (High power)             |  |  |  |

| D031                                         |                        |                                                                         | 250  | 650           | —              | μA    | 3.0        | Op Amp (High power) (Note 5)    |  |  |  |

|                                              |                        |                                                                         | 350  | 850           | —              | μA    | 5.0        |                                 |  |  |  |

| D032                                         |                        | _                                                                       | 250  | 650           | _              | μA    | 1.8        | Comparator, Normal-Power mode   |  |  |  |

|                                              |                        | —                                                                       | 300  | 700           | _              | μA    | 3.0        |                                 |  |  |  |

| D032                                         |                        | _                                                                       | 280  | 650           | —              | μA    | 2.3        | Comparator, Normal-Power mode   |  |  |  |

|                                              |                        |                                                                         | 300  | 700           | _              | μA    | 3.0        | (Note 5)                        |  |  |  |

|                                              |                        |                                                                         | 310  | 700           | —              | μA    | 5.0        |                                 |  |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The peripheral current is the sum of the base IPD and the additional current consumed when this peripheral is enabled. The peripheral △ current can be determined by subtracting the base IDD or IPD current from this limit. Max values should be used when calculating total current consumption.

2: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to Vss.

3: ADC oscillator source is FRC.

4: 0.1 μF capacitor on VCAP.

5: VREGPM = 0.

Note: Unless otherwise noted, VIN = 5V, Fosc = 300 kHz, CIN = 0.1 µF, TA = 25°C.

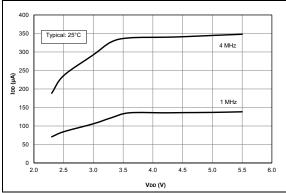

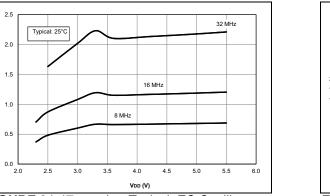

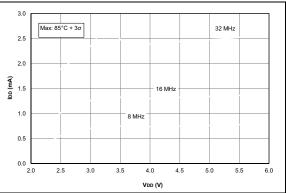

FIGURE 31-13: IDD Typical, EC Oscillator MP Mode, PIC16F1784/6/7 Only.

FIGURE 31-14: IDD Maximum, EC Oscillator MP Mode, PIC16F1784/6/7 Only.

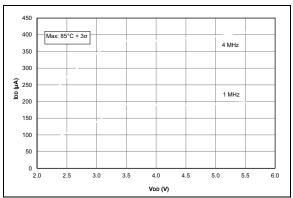

FIGURE 31-15: IDD Typical, EC Oscillator HP Mode, PIC16LF1784/6/7 Only.

FIGURE 31-16: IDD Maximum, EC Oscillator HP Mode, PIC16LF1784/6/7 Only.

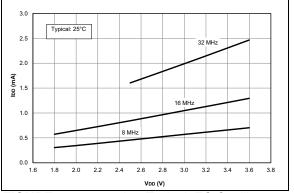

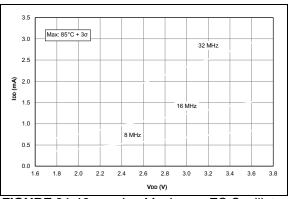

FIGURE 31-17: IDD Typical, EC Oscillator HP Mode, PIC16F1784/6/7 Only.

IDD Maximum, EC Oscillator FIGURE 31-18: HP Mode, PIC16F1784/6/7 Only.

2.5

2.0

1.5 (WA)

0.5

8 1.0

Note: Unless otherwise noted, VIN = 5V, Fosc = 300 kHz, CIN = 0.1  $\mu$ F, TA = 25°C.

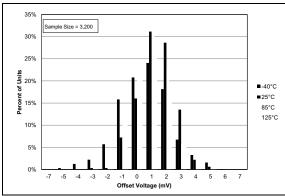

**FIGURE 31-109:** Op Amp, Output Voltage Histogram, VDD = 3.0V, VCM = VDD/2.

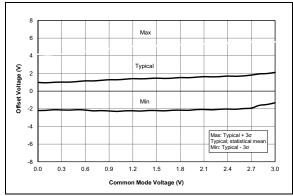

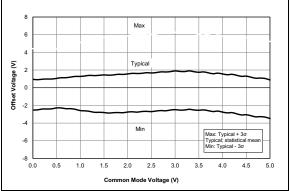

**FIGURE 31-110:** Op Amp, Offset Over Common Mode Voltage, VDD = 3.0V, Temp. = 25°C.

**FIGURE 31-111:** Op Amp, Offset Over Common Mode Voltage, VDD = 5.0V, Temp. = 25°C, PIC16F1784/6/7 Only.

FIGURE 31-113: Op Amp, Output Slew Rate, Falling Edge, PIC16LF1784/6/7 Only.

FIGURE 31-112: Op Amp, Output Slew Rate, Rising Edge, PIC16LF1784/6/7 Only.

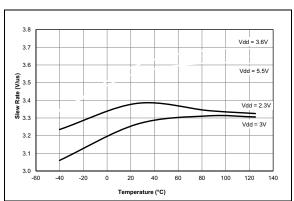

FIGURE 31-114: Op Amp, Output Slew Rate, Rising Edge, PIC16F1784/6/7 Only.

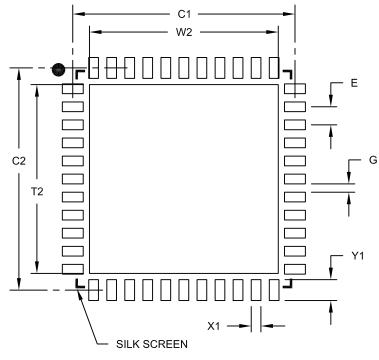

44-Lead Plastic Quad Flat, No Lead Package (ML) - 8x8 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

## RECOMMENDED LAND PATTERN

|                            | MILLIMETERS |          |      |      |  |  |

|----------------------------|-------------|----------|------|------|--|--|

| Dimensior                  | MIN         | NOM      | MAX  |      |  |  |

| Contact Pitch              | E           | 0.65 BSC |      |      |  |  |

| Optional Center Pad Width  | W2          |          |      | 6.60 |  |  |

| Optional Center Pad Length | T2          |          |      | 6.60 |  |  |

| Contact Pad Spacing        | C1          |          | 8.00 |      |  |  |

| Contact Pad Spacing        | C2          |          | 8.00 |      |  |  |

| Contact Pad Width (X44)    | X1          |          |      | 0.35 |  |  |

| Contact Pad Length (X44)   | Y1          |          |      | 0.85 |  |  |

| Distance Between Pads      | G           | 0.25     |      |      |  |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2103B