Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 32MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, POR, PSMC, PWM, WDT                              |

| Number of I/O              | 35                                                                       |

| Program Memory Size        | 14KB (8K x 14)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 1K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                              |

| Data Converters            | A/D 14x12b; D/A 1x8b                                                     |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                 |

| Supplier Device Package    | 40-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1787-i-p |

## 3.1.1 READING PROGRAM MEMORY AS DATA

There are two methods of accessing constants in program memory. The first method is to use tables of RETLW instructions. The second method is to set an FSR to point to the program memory.

#### 3.1.1.1 RETLW Instruction

The RETLW instruction can be used to provide access to tables of constants. The recommended way to create such a table is shown in Example 3-1.

#### EXAMPLE 3-1: RETLW INSTRUCTION

```

constants

BRW

;Add Index in W to

;program counter to

;select data

RETLW DATAO

;Index0 data

RETLW DATA1

;Index1 data

RETLW DATA2

RETLW DATA3

my_function

;... LOTS OF CODE ...

MOVLW DATA_INDEX

call constants

;... THE CONSTANT IS IN W

```

The BRW instruction makes this type of table very simple to implement. If your code must remain portable with previous generations of microcontrollers, then the BRW instruction is not available so the older table read method must be used.

#### 3.1.1.2 Indirect Read with FSR

The program memory can be accessed as data by setting bit 7 of the FSRxH register and reading the matching INDFx register. The MOVIW instruction will place the lower 8 bits of the addressed word in the W register. Writes to the program memory cannot be performed via the INDF registers. Instructions that access the program memory via the FSR require one extra instruction cycle to complete. Example 3-2 demonstrates accessing the program memory via an FSR.

The high directive will set bit<7> if a label points to a location in program memory.

# EXAMPLE 3-2: ACCESSING PROGRAM MEMORY VIA FSR

```

constants

RETLW DATA0

;Index0 data

RETLW DATA1

;Index1 data

RETIW DATA2

RETLW DATA3

my_function

;... LOTS OF CODE...

MOVLW LOW constants

MOVWF FSR1L

MOVLW

HIGH constants

MOVWF

FSR1H

MOVIW

0[FSR1]

;THE PROGRAM MEMORY IS IN W

```

**TABLE 3-4:**

|      | BANK 0                        | •    | BANK 1                        |      | BANK 2                        |      | BANK 3                        |      | BANK 4                        |      | BANK 5                        |      | BANK 6                        |      | BANK 7                        |

|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|

| 000h |                               | 080h |                               | 100h |                               | 180h |                               | 200h |                               | 280h |                               | 300h |                               | 380h |                               |

|      | Core Registers<br>(Table 3-2) |

| 00Bh |                               | 08Bh |                               | 10Bh |                               | 18Bh |                               | 20Bh |                               | 28Bh |                               | 30Bh |                               | 38Bh |                               |

| 00Ch | PORTA                         | 08Ch | TRISA                         | 10Ch | LATA                          | 18Ch | ANSELA                        | 20Ch | WPUA                          | 28Ch | ODCONA                        | 30Ch | SLRCONA                       | 38Ch | INLVLA                        |

| 00Dh | PORTB                         | 08Dh | TRISB                         | 10Dh | LATB                          | 18Dh | ANSELB                        | 20Dh | WPUB                          | 28Dh | ODCONB                        | 30Dh | SLRCONB                       | 38Dh | INLVLB                        |

| 00Eh | PORTC                         | 08Eh | TRISC                         | 10Eh | LATC                          | 18Eh |                               | 20Eh | WPUC                          | 28Eh | ODCONC                        | 30Eh | SLRCONC                       | 38Eh | INLVLC                        |

| 00Fh | _                             | 08Fh | _                             | 10Fh |                               | 18Fh |                               | 20Fh | _                             | 28Fh |                               | 30Fh | _                             | 38Fh | _                             |

| 010h | PORTE                         | 090h | TRISE                         | 110h |                               | 190h |                               | 210h | WPUE                          | 290h |                               | 310h | _                             | 390h | INLVLE                        |

| 011h | PIR1                          | 091h | PIE1                          | 111h | CM1CON0                       | 191h | EEADRL                        | 211h | SSP1BUF                       | 291h | CCPR1L                        | 311h | _                             | 391h | IOCAP                         |

| 012h | PIR2                          | 092h | PIE2                          | 112h | CM1CON1                       | 192h | EEADRH                        | 212h | SSP1ADD                       | 292h | CCPR1H                        | 312h | _                             | 392h | IOCAN                         |

| 013h | _                             | 093h |                               | 113h | CM2CON0                       | 193h | EEDATL                        | 213h | SSP1MSK                       | 293h | CCP1CON                       | 313h | _                             | 393h | IOCAF                         |

| 014h | PIR4                          | 094h | PIE4                          | 114h | CM2CON1                       | 194h | EEDATH                        | 214h | SSP1STAT                      | 294h |                               | 314h | _                             | 394h | IOCBP                         |

| 015h | TMR0                          | 095h | OPTION_REG                    | 115h | CMOUT                         | 195h | EECON1                        | 215h | SSP1CON1                      | 295h | _                             | 315h | _                             | 395h | IOCBN                         |

| 016h | TMR1L                         | 096h | PCON                          | 116h | BORCON                        | 196h | EECON2                        | 216h | SSP1CON2                      | 296h |                               | 316h | _                             | 396h | IOCBF                         |

| 017h | TMR1H                         | 097h | WDTCON                        | 117h | FVRCON                        | 197h | VREGCON <sup>(1)</sup>        | 217h | SSP1CON3                      | 297h | _                             | 317h | _                             | 397h | IOCCP                         |

| 018h | T1CON                         | 098h | OSCTUNE                       | 118h | DAC1CON0                      | 198h | _                             | 218h | _                             | 298h | CCPR2L                        | 318h |                               | 398h | IOCCN                         |

| 019h | T1GCON                        | 099h | OSCCON                        | 119h | DAC1CON1                      | 199h | RCREG                         | 219h | _                             | 299h | CCPR2H                        | 319h |                               | 399h | IOCCF                         |

| 01Ah | TMR2                          | 09Ah | OSCSTAT                       | 11Ah | CM4CON0                       | 19Ah | TXREG                         | 21Ah | _                             | 29Ah | CCP2CON                       | 31Ah |                               | 39Ah |                               |

| 01Bh | PR2                           | 09Bh | ADRESL                        | 11Bh | CM4CON1                       | 19Bh | SPBRGL                        | 21Bh | _                             | 29Bh | _                             | 31Bh | _                             | 39Bh |                               |

| 01Ch | T2CON                         | 09Ch | ADRESH                        | 11Ch | APFCON2                       | 19Ch | SPBRGH                        | 21Ch | _                             | 29Ch | _                             | 31Ch | _                             | 39Ch | I                             |

| 01Dh |                               | 09Dh | ADCON0                        | 11Dh | APFCON1                       | 19Dh | RCSTA                         | 21Dh | _                             | 29Dh | _                             | 31Dh | -                             | 39Dh | IOCEP                         |

| 01Eh | _                             | 09Eh | ADCON1                        | 11Eh | CM3CON0                       | 19Eh | TXSTA                         | 21Eh | _                             | 29Eh | _                             | 31Eh | _                             | 39Eh | IOCEN                         |

| 01Fh | 1                             | 09Fh | ADCON2                        | 11Fh | CM3CON1                       | 19Fh | BAUDCON                       | 21Fh | _                             | 29Fh | _                             | 31Fh | 1                             | 39Fh | IOCEF                         |

| 020h |                               | 0A0h |                               | 120h |                               | 1A0h |                               | 220h |                               | 2A0h |                               | 320h |                               | 3A0h |                               |

General

Purpose

Register

80 Bytes

Accesses

70h – 7Fh

26Fh

270h

27Fh

General

Purpose

Register

80 Bytes

Accesses

70h - 7Fh

2EFh

2F0h

2FFh

General

Purpose

Register

80 Bytes

Accesses

70h – 7Fh

General

Purpose

Register

80 Bytes

Accesses

70h - 7Fh

36Fh

370h

37Fh

General

Purpose

Register

80 Bytes

Accesses

70h – 7Fh

3EFh

3F0h

3FFh

**Legend:** = Unimplemented data memory locations, read as '0'.

0EFh

0F0h

0FFh

General

Purpose

Register

80 Bytes

Accesses

70h – 7Fh

PIC16(L)F1786 MEMORY MAP (BANKS 0-7)

General

Purpose

Register

80 Bytes

Accesses

70h - 7Fh

1EFh

1F0h

1FFh

13Fh

140h

16Fh

170h

17Fh

Note 1: PIC16F1786 only.

General

Purpose

Register

80 Bytes

Common RAM

70h – 7Fh

06Fh

070h

07Fh

## 4.0 DEVICE CONFIGURATION

Device configuration consists of Configuration Words, Code Protection and Device ID.

## 4.1 Configuration Words

There are several Configuration Word bits that allow different oscillator and memory protection options. These are implemented as Configuration Word 1 at 8007h and Configuration Word 2 at 8008h.

Note: The DEBUG bit in Configuration Words is managed automatically by device development tools including debuggers and programmers. For normal device operation, this bit should be maintained as a '1'.

#### 6.2.1.4 4x PLL

The oscillator module contains a 4x PLL that can be used with both external and internal clock sources to provide a system clock source. The input frequency for the 4x PLL must fall within specifications. See the PLL Clock Timing Specifications in Section 30.0 "Electrical Specifications".

The 4x PLL may be enabled for use by one of two methods:

- Program the PLLEN bit in Configuration Words to a '1'.

- Write the SPLLEN bit in the OSCCON register to a '1'. If the PLLEN bit in Configuration Words is programmed to a '1', then the value of SPLLEN is ignored.

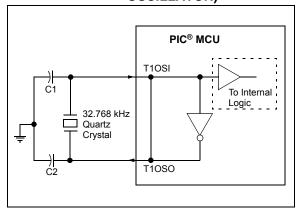

#### 6.2.1.5 TIMER1 Oscillator

The Timer1 oscillator is a separate crystal oscillator that is associated with the Timer1 peripheral. It is optimized for timekeeping operations with a 32.768 kHz crystal connected between the T1OSO and T1OSI device pins.

The Timer1 oscillator can be used as an alternate system clock source and can be selected during run-time using clock switching. Refer to **Section 6.3** "Clock Switching" for more information.

FIGURE 6-5: QUARTZ CRYSTAL OPERATION (TIMER1 OSCILLATOR)

- Note 1: Quartz crystal characteristics vary according to type, package and manufacturer. The user should consult the manufacturer data sheets for specifications and recommended application.

- **2:** Always verify oscillator performance over the VDD and temperature range that is expected for the application.

- **3:** For oscillator design assistance, reference the following Microchip Applications Notes:

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>®</sup> and PIC<sup>®</sup> Devices" (DS00826)

- AN849, "Basic PIC® Oscillator Design" (DS00849)

- AN943, "Practical PIC<sup>®</sup> Oscillator Analysis and Design" (DS00943)

- AN949, "Making Your Oscillator Work" (DS00949)

- TB097, "Interfacing a Micro Crystal MS1V-T1K 32.768 kHz Tuning Fork Crystal to a PIC16F690/SS" (DS91097)

- AN1288, "Design Practices for Low-Power External Oscillators" (DS01288)

## 9.3 Register Definitions: Voltage Regulator Control

## REGISTER 9-1: VREGCON: VOLTAGE REGULATOR CONTROL REGISTER<sup>(1)</sup>

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0/0 | R/W-1/1  |

|-------|-----|-----|-----|-----|-----|---------|----------|

| _     | _   | _   | _   | _   | _   | VREGPM  | Reserved |

| bit 7 |     |     |     |     |     |         | bit 0    |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-2 **Unimplemented:** Read as '0'

bit 1 **VREGPM:** Voltage Regulator Power Mode Selection bit

1 = Low-Power Sleep mode enabled in Sleep<sup>(2)</sup>

Draws lowest current in Sleep, slower wake-up

0 = Normal-Power mode enabled in Sleep<sup>(2)</sup>

Draws higher current in Sleep, faster wake-up

bit 0 Reserved: Read as '1'. Maintain this bit set.

Note 1: "F" devices only.

2: See Section 30.0 "Electrical Specifications".

TABLE 9-1: SUMMARY OF REGISTERS ASSOCIATED WITH POWER-DOWN MODE

| Name    | Bit 7   | Bit 6    | Bit 5    | Bit 4    | Bit 3  | Bit 2    | Bit 1    | Bit 0    | Register on<br>Page |

|---------|---------|----------|----------|----------|--------|----------|----------|----------|---------------------|

| INTCON  | GIE     | PEIE     | TMR0IE   | INTE     | IOCIE  | TMR0IF   | INTF     | RAIF     | 93                  |

| IOCBF   | IOCBF7  | IOCBF6   | IOCBF5   | IOCBF4   | IOCBF3 | IOCBF2   | IOCBF1   | IOCBF0   | 159                 |

| IOCBN   | IOCBN7  | IOCBN6   | IOCBN5   | IOCBN4   | IOCBN3 | IOCBN2   | IOCBN1   | IOCBN0   | 158                 |

| IOCBP   | IOCBP7  | IOCBP6   | IOCBP5   | IOCBP4   | IOCBP3 | IOCBP2   | IOCBP1   | IOCBP0   | 158                 |

| PIE1    | TMR1GIE | ADIE     | RCIE     | TXIE     | SSP1IE | CCP1IE   | TMR2IE   | TMR1IE   | 94                  |

| PIE2    | OSFIE   | C2IE     | C1IE     | EEIE     | BCL1IE | C4IE     | C3IE     | CCP2IE   | 95                  |

| PIE3    | _       | _        | _        | CCP3IE   | _      | _        | _        | _        | 96                  |

| PIE4    | _       | PSMC3TIE | PSMC2TIE | PSMC1TIE | _      | PSMC3SIE | PSMC2SIE | PSMC1SIE | 97                  |

| PIR1    | TMR1GIF | ADIF     | RCIF     | TXIF     | SSP1IF | CCP1IF   | TMR2IF   | TMR1IF   | 94                  |

| PIR2    | OSFIF   | C2IF     | C1IF     | EEIF     | BCL1IF | C4IF     | C3IF     | CCP2IF   | 99                  |

| PIR3    | _       | _        | _        | CCP3IF   | _      | _        | _        | _        | 100                 |

| PIR4    | _       | PSMC3TIF | PSMC2TIF | PSMC1TIF | _      | PSMC3SIF | PSMC2SIF | PSMC1SIF | 101                 |

| STATUS  | _       | _        | _        | TO       | PD     | Z        | DC       | С        | 27                  |

| VREGCON | _       | _        | _        | _        | _      | _        | VREGPM   | Reserved | 106                 |

| WDTCON  | _       | _        |          | 1        | SWDTEN | 110      |          |          |                     |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used in Power-Down mode.

#### 17.2.6 A/D CONVERSION PROCEDURE

This is an example procedure for using the ADC to perform an Analog-to-Digital conversion:

- 1. Configure Port:

- Disable pin output driver (Refer to the TRIS register)

- Configure pin as analog (Refer to the ANSEL register)

- 2. Configure the ADC module:

- · Select ADC conversion clock

- · Configure voltage reference

- · Select ADC input channel

- · Turn on ADC module

- 3. Configure ADC interrupt (optional):

- · Clear ADC interrupt flag

- · Enable ADC interrupt

- Enable peripheral interrupt

- Enable global interrupt<sup>(1)</sup>

- 4. Wait the required acquisition time<sup>(2)</sup>.

- 5. Start conversion by setting the GO/DONE bit.

- 6. Wait for ADC conversion to complete by one of the following:

- Polling the GO/DONE bit

- Waiting for the ADC interrupt (interrupts enabled)

- 7. Read ADC Result.

- 8. Clear the ADC interrupt flag (required if interrupt is enabled).

- **Note 1:** The global interrupt can be disabled if the user is attempting to wake-up from Sleep and resume in-line code execution.

- 2: Refer to Section 17.4 "ADC Acquisition Requirements".

#### **EXAMPLE 17-1: A/D CONVERSION**

```

; This code block configures the ADC

; for polling, Vdd and Vss references, Frc

; clock and ANO input.

;Conversion start & polling for completion

; are included.

BANKSEL

ADCON1

B'11110000' ;2's complement, Frc

MOVLW

;clock

MOVWF

ADCON1

;Vdd and Vss Vref

B'00001111' ;set negative input

MOVLW

MOVWF

ADCON2

;to negative

reference

BANKSEL

TRISA

TRISA,0

;Set RAO to input

BANKSEL

ANSEL

ANSEL.0

BSF

;Set RAO to analog

BANKSEL

ADCONO

B'00000001' ;Select channel ANO

MOVLW

MOVWF

ADCON0

;Turn ADC On

CALL

SampleTime ;Acquisiton delay

BSF

ADCON0,ADGO ;Start conversion

ADCON0, ADGO ; Is conversion done?

BTFSC

GOTO

$-1

;No, test again

BANKSEL

ADRESH

MOVF

ADRESH, W

Read upper 2 bits

MOVWE

RESULTHI

store in GPR space

```

### 18.4 Register Definitions: Op Amp Control

### REGISTER 18-1: OPAXCON: OPERATIONAL AMPLIFIERS (OPAX) CONTROL REGISTERS

| R/W-0/0 | R/W-0/0 | U-0 | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 |

|---------|---------|-----|-----|-----|-----|---------|---------|

| OPAxEN  | OPAxSP  | _   | _   | _   | _   | OPAxC   | H<1:0>  |

| bit 7   |         |     |     |     |     |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared q = Value depends on condition

bit 7 **OPAXEN:** Op Amp Enable bit

1 = Op amp is enabled

0 = Op amp is disabled and consumes no active power

bit 6 **OPAxSP:** Op Amp Speed/Power Select bit

1 = Comparator operates in high GBWP mode

0 = Reserved. Do not use.

bit 5-2 **Unimplemented:** Read as '0'

bit 1-0 **OPAxCH<1:0>:** Non-inverting Channel Selection bits

11 = Non-inverting input connects to FVR Buffer 2 output

10 = Non-inverting input connects to DAC\_output

0x = Non-inverting input connects to OPAxIN+ pin

#### TABLE 18-1: SUMMARY OF REGISTERS ASSOCIATED WITH OP AMPS

| Name     | Bit 7  | Bit 6  | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1  | Bit 0   | Register on Page |

|----------|--------|--------|---------|---------|---------|---------|--------|---------|------------------|

| ANSELA   | ANSA7  | _      | ANSA5   | ANSA4   | ANSA3   | ANSA2   | ANSA1  | ANSA0   | 132              |

| ANSELB   | _      | ANSB6  | ANSB5   | ANSB4   | ANSB3   | ANSB2   | ANSB1  | ANSB0   | 138              |

| DAC1CON0 | DAC1EN | _      | DAC10E1 | DAC10E2 | DAC1PS  | SS<1:0> | _      | DAC1NSS | 186              |

| DAC1CON1 |        |        |         | DAC′    | IR<7:0> |         |        |         | 186              |

| OPA1CON  | OPA1EN | OPA1SP | _       | _       | _       | _       | OPA1P0 | CH<1:0> | 182              |

| OPA2CON  | OPA2EN | OPA2SP | _       | _       | _       | _       | OPA2P0 | CH<1:0> | 182              |

| TRISA    | TRISA7 | TRISA6 | TRISA5  | TRISA4  | TRISA3  | TRISA2  | TRISA1 | TRISA0  | 131              |

| TRISB    | TRISB7 | TRISB6 | TRISB5  | TRISB4  | TRISB3  | TRISB2  | TRISB1 | TRISB0  | 137              |

| TRISC    | TRISC7 | TRISC6 | TRISC5  | TRISC4  | TRISC3  | TRISC2  | TRISC1 | TRISC0  | 142              |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by op amps.

Note 1: PIC16(L)F1784/7 only

## 19.4 Operation During Sleep

When the device wakes up from Sleep through an interrupt or a Watchdog Timer time-out, the contents of the DAC1CON0 register are not affected. To minimize current consumption in Sleep mode, the voltage reference should be disabled.

#### 19.5 Effects of a Reset

A device Reset affects the following:

- · DAC is disabled.

- DAC output voltage is removed from the DAC1OUT pin.

- The DAC1R<7:0> range select bits are cleared.

#### 20.0 COMPARATOR MODULE

Comparators are used to interface analog circuits to a digital circuit by comparing two analog voltages and providing a digital indication of their relative magnitudes. Comparators are very useful mixed signal building blocks because they provide analog functionality independent of program execution. The analog comparator module includes the following features:

- · Independent comparator control

- · Programmable input selection

- · Comparator output is available internally/externally

- · Programmable output polarity

- · Interrupt-on-change

- · Wake-up from Sleep

- · Programmable Speed/Power optimization

- · PWM shutdown

- · Programmable and fixed voltage reference

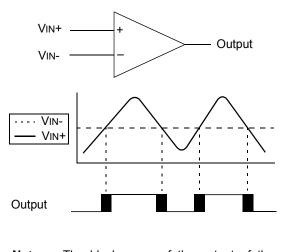

## 20.1 Comparator Overview

A single comparator is shown in Figure 20-1 along with the relationship between the analog input levels and the digital output. When the analog voltage at VIN+ is less than the analog voltage at VIN-, the output of the comparator is a digital low level. When the analog voltage at VIN+ is greater than the analog voltage at VIN-, the output of the comparator is a digital high level.

The comparators available for this device are located in Table 20-1.

TABLE 20-1: COMPARATOR AVAILABILITY PER DEVICE

| Device            | C1 | C2 | <b>C</b> 3 | C4 |

|-------------------|----|----|------------|----|

| PIC16(L)F1784/6/7 | •  | •  | •          | •  |

## FIGURE 20-1: SINGLE COMPARATOR

**Note:** The black areas of the output of the comparator represents the uncertainty due to input offsets and response time.

### 23.5 Register Definitions: Timer2 Control

#### REGISTER 23-1: T2CON: TIMER2 CONTROL REGISTER

| U-0   | R/W-0/0 |

|-------|---------|---------|---------|---------|---------|---------|---------|

| _     |         | T2OUTF  | PS<3:0> |         | TMR2ON  | T2CKP   | S<1:0>  |

| bit 7 |         |         |         |         |         |         | bit 0   |

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'u = Bit is unchangedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other Resets'1' = Bit is set'0' = Bit is cleared

bit 7 **Unimplemented:** Read as '0'

bit 6-3 **T2OUTPS<3:0>:** Timer2 Output Postscaler Select bits

1111 = 1:16 Postscaler 1110 = 1:15 Postscaler 1101 = 1:14 Postscaler 1100 = 1:13 Postscaler 1011 = 1:12 Postscaler 1010 = 1:11 Postscaler 1001 = 1:10 Postscaler 1000 = 1:9 Postscaler 1011 = 1:8 Postscaler 1110 = 1:7 Postscaler 1101 = 1:6 Postscaler 1102 = 1:5 Postscaler 1103 = 1:4 Postscaler 1104 = 1:4 Postscaler 1105 = 1:4 Postscaler 1106 = 1:5 Postscaler 1107 = 1:4 Postscaler 1108 = 1:4 Postscaler 1109 = 1:5 Postscaler

0000 = 1:1 Postscalerbit 2 TMR2ON: Timer2 On bit

1 = Timer2 is on 0 = Timer2 is off

bit 1-0 T2CKPS<1:0>: Timer2 Clock Prescale Select bits

11 = Prescaler is 64 10 = Prescaler is 16 01 = Prescaler is 4 00 = Prescaler is 1

#### REGISTER 24-26: PSMCxDBR: PSMC RISING EDGE DEAD-BAND TIME REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | PSMCxD  | BR<7:0> |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-0 **PSMCxDBR<7:0>:** Rising Edge Dead-Band Time bits

= Unsigned number of PSMCx psmc\_clk clock periods in rising edge dead band

#### REGISTER 24-27: PSMCxDBF: PSMC FALLING EDGE DEAD-BAND TIME REGISTER

| R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0  | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|---------|---------|---------|---------|----------|---------|---------|---------|

|         |         |         | PSMCxE  | )BF<7:0> |         |         |         |

| bit 7   |         |         |         |          |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

1' = Bit is set '0' = Bit is cleared

bit 7-0 **PSMCxDBF<7:0>:** Falling Edge Dead-Band Time bits

= Unsigned number of PSMCx psmc\_clk clock periods in falling edge dead band

#### REGISTER 24-28: PSMCxFFA: PSMC FRACTIONAL FREQUENCY ADJUST REGISTER

| U-0   | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|-----|---------|---------|---------|---------|

| _     | _   | _   | _   |         | PSMCxF  | FA<3:0> |         |

| bit 7 |     |     |     |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-4 Unimplemented: Read as '0'

bit 3-0 **PSMCxFFA<3:0>:** Fractional Frequency Adjustment bits

= Unsigned number of fractional PSMCx psmc\_clk clock periods to add to each period event time.

The fractional time period = 1/(16\*semc\_clk)

The fractional time period = 1/(16\*psmc\_clk)

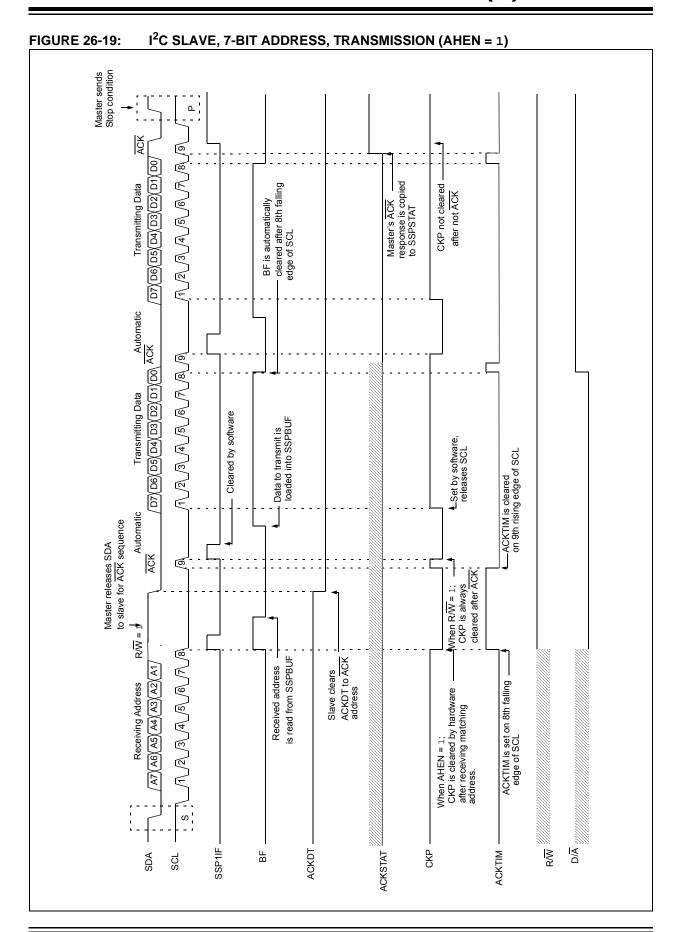

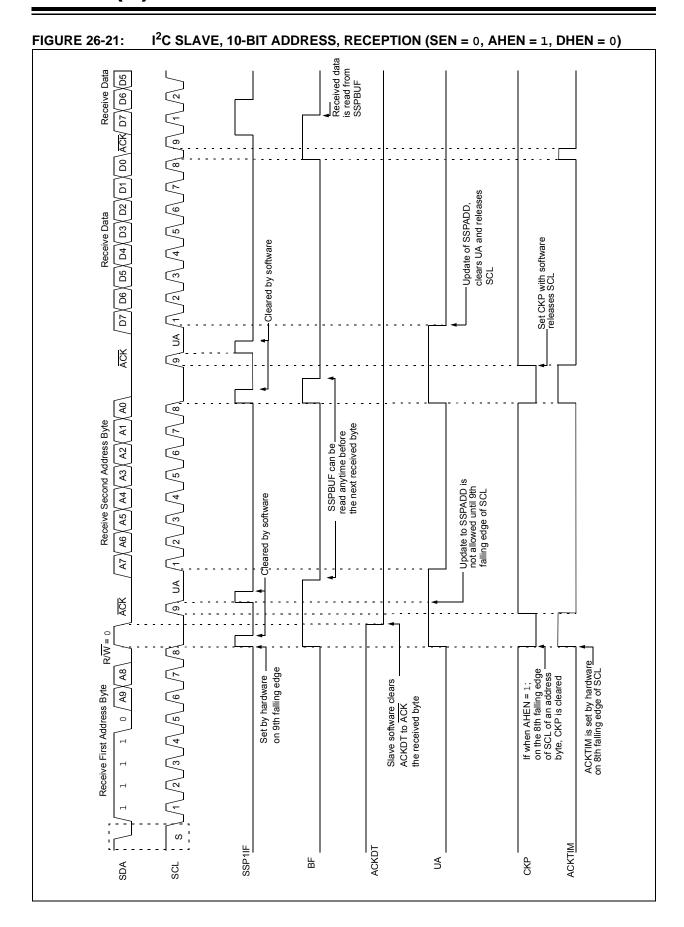

#### 26.5.2 SLAVE RECEPTION

When the  $R/\overline{W}$  bit of a matching received address byte is clear, the  $R/\overline{W}$  bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register and acknowledged.

When the overflow condition exists for a received address, then not Acknowledge is given. An overflow condition is defined as either bit BF of the SSPSTAT register is set, or bit SSPOV of the SSPCON1 register is set. The BOEN bit of the SSPCON3 register modifies this operation. For more information see Register 26-4.

An MSSP interrupt is generated for each transferred data byte. Flag bit, SSP1IF, must be cleared by software.

When the SEN bit of the SSPCON2 register is set, SCL will be held low (clock stretch) following each received byte. The clock must be released by setting the CKP bit of the SSPCON1 register, except sometimes in 10-bit mode. See **Section 26.2.3 "SPI Master Mode"** for more detail.

#### 26.5.2.1 7-bit Addressing Reception

This section describes a standard sequence of events for the MSSP module configured as an I<sup>2</sup>C Slave in 7-bit Addressing mode. All decisions made by hardware or software and their effect on reception. Figure 26-13 and Figure 26-14 is used as a visual reference for this description.

This is a step by step process of what typically must be done to accomplish I<sup>2</sup>C communication.

- 1. Start bit detected.

- 2. S bit of SSPSTAT is set; SSP1IF is set if interrupt on Start detect is enabled.

- 3. Matching address with R/W bit clear is received.

- 4. The slave pulls SDA low sending an ACK to the master, and sets SSP1IF bit.

- 5. Software clears the SSP1IF bit.

- Software reads received address from SSPBUF clearing the BF flag.

- 7. If SEN = 1; Slave software sets CKP bit to release the SCL line.

- 8. The master clocks out a data byte.

- Slave drives SDA low sending an ACK to the master, and sets SSP1IF bit.

- 10. Software clears SSP1IF.

- Software reads the received byte from SSPBUF clearing BF.

- 12. Steps 8-12 are repeated for all received bytes from the master.

- 13. Master sends Stop condition, setting P bit of SSPSTAT, and the bus goes idle.

#### 26.5.2.2 7-bit Reception with AHEN and DHEN

Slave device reception with AHEN and DHEN set operate the same as without these options with extra interrupts and clock stretching added after the 8th falling edge of SCL. These additional interrupts allow the slave software to decide whether it wants to ACK the receive address or data byte, rather than the hardware. This functionality adds support for PMBus™ that was not present on previous versions of this module.

This list describes the steps that need to be taken by slave software to use these options for I<sup>2</sup>C communication. Figure 26-15 displays a module using both address and data holding. Figure 26-16 includes the operation with the SEN bit of the SSPCON2 register set

- S bit of SSPSTAT is set; SSP1IF is set if interrupt on Start detect is enabled.

- 2. Matching address with R/W bit clear is clocked in. SSP1IF is set and CKP cleared after the 8th falling edge of SCL.

- 3. Slave clears the SSP1IF.

- Slave can look at the ACKTIM bit of the SSP-CON3 register to determine if the SSP1IF was after or before the ACK.

- 5. Slave reads the address value from SSPBUF, clearing the BF flag.

- Slave sets ACK value clocked out to the master by setting ACKDT.

- 7. Slave releases the clock by setting CKP.

- 8. SSP1IF is set after an ACK, not after a NACK.

- 9. If SEN = 1 the slave hardware will stretch the clock after the ACK.

- 10. Slave clears SSP1IF.

Note: SSP1IF is still set after the 9th falling edge of SCL even if there is no clock stretching and BF has been cleared. Only if NACK is sent to master is SSP1IF not set

- 11. SSP1IF set and CKP cleared after 8th falling edge of SCL for a received data byte.

- 12. Slave looks at ACKTIM bit of SSPCON3 to determine the source of the interrupt.

- 13. Slave reads the received data from SSPBUF clearing BF.

- 14. Steps 7-14 are the same for each received data byte.

- 15. Communication is ended by either the slave sending an ACK = 1, or the master sending a Stop condition. If a Stop is sent and Interrupt on Stop Detect is disabled, the slave will only know by polling the P bit of the SSTSTAT register.

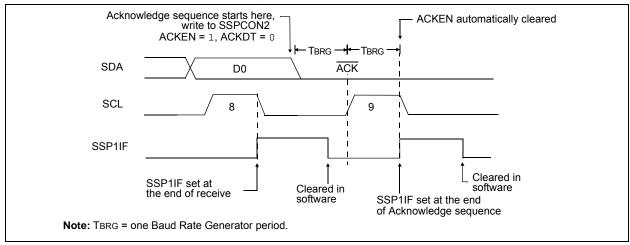

## 26.6.8 ACKNOWLEDGE SEQUENCE TIMING

An Acknowledge sequence is enabled by setting the Acknowledge Sequence Enable bit, ACKEN bit of the SSPCON2 register. When this bit is set, the SCL pin is pulled low and the contents of the Acknowledge data bit are presented on the SDA pin. If the user wishes to generate an Acknowledge, then the ACKDT bit should be cleared. If not, the user should set the ACKDT bit before starting an Acknowledge sequence. The Baud Rate Generator then counts for one rollover period (TBRG) and the SCL pin is deasserted (pulled high). When the SCL pin is sampled high (clock arbitration), the Baud Rate Generator counts for TBRG. The SCL pin is then pulled low. Following this, the ACKEN bit is automatically cleared, the Baud Rate Generator is turned off and the MSSP module then goes into Idle mode (Figure 26-29).

#### 26.6.8.1 WCOL Status Flag

If the user writes the SSPBUF when an Acknowledge sequence is in progress, then WCOL is set and the contents of the buffer are unchanged (the write does not occur).

#### 26.6.9 STOP CONDITION TIMING

A Stop bit is asserted on the SDA pin at the end of a receive/transmit by setting the Stop Sequence Enable bit, PEN bit of the SSPCON2 register. At the end of a receive/transmit, the SCL line is held low after the falling edge of the ninth clock. When the PEN bit is set, the master will assert the SDA line low. When the SDA line is sampled low, the Baud Rate Generator is reloaded and counts down to '0'. When the Baud Rate Generator times out, the SCL pin will be brought high and one TBRG (Baud Rate Generator rollover count) later, the SDA pin will be deasserted. When the SDA pin is sampled high while SCL is high, the P bit of the SSPSTAT register is set. A TBRG later, the PEN bit is cleared and the SSP1IF bit is set (Figure 26-30).

### 26.6.9.1 WCOL Status Flag

If the user writes the SSPBUF when a Stop sequence is in progress, then the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

FIGURE 26-30: ACKNOWLEDGE SEQUENCE WAVEFORM

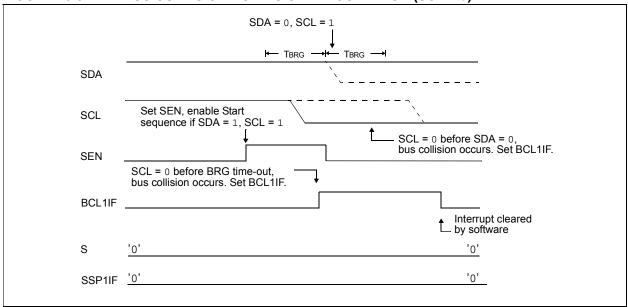

FIGURE 26-34: BUS COLLISION DURING START CONDITION (SCL = 0)

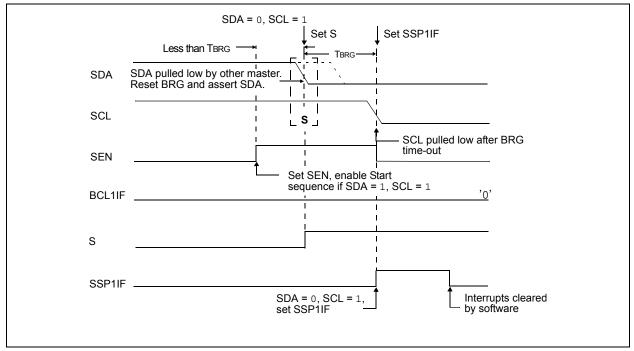

FIGURE 26-35: BRG RESET DUE TO SDA ARBITRATION DURING START CONDITION

#### **REGISTER 26-5: SSPMSK: SSP MASK REGISTER**

| R/W-1/1 | R/W-1/1  | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |  |  |  |  |

|---------|----------|---------|---------|---------|---------|---------|---------|--|--|--|--|

|         | MSK<7:0> |         |         |         |         |         |         |  |  |  |  |

| bit 7   |          |         |         |         |         |         | bit 0   |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-1 **MSK<7:1>:** Mask bits

1 = The received address bit n is compared to SSPADD<n> to detect I<sup>2</sup>C address match

0 = The received address bit n is not used to detect I<sup>2</sup>C address match

bit 0 MSK<0>: Mask bit for I<sup>2</sup>C Slave mode, 10-bit Address

$I^{2}C$  Slave mode, 10-bit address (SSPM<3:0> = 0111 or 1111):

1 = The received address bit 0 is compared to SSPADD<0> to detect  $I^2C$  address match

0 = The received address bit 0 is not used to detect I<sup>2</sup>C address match

I<sup>2</sup>C Slave mode, 7-bit address, the bit is ignored

## REGISTER 26-6: SSPADD: MSSP ADDRESS AND BAUD RATE REGISTER (I<sup>2</sup>C MODE)

| R/W-0/0  | R/W-0/0 R/W-0/0 R/W-0/0 R/W-0/0 |  | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |       |  |  |  |  |  |

|----------|---------------------------------|--|---------|---------|---------|--|-------|--|--|--|--|--|

| ADD<7:0> |                                 |  |         |         |         |  |       |  |  |  |  |  |

| bit 7    |                                 |  |         |         |         |  | bit 0 |  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

#### Master mode:

bit 7-0 ADD<7:0>: Baud Rate Clock Divider bits

SCL pin clock period = ((ADD<7:0> + 1)\*4)/Fosc

#### <u>10-Bit Slave mode — Most Significant Address Byte:</u>

bit 7-3 Not used: Unused for Most Significant Address byte. Bit state of this register is a "don't care". Bit

pattern sent by master is fixed by I<sup>2</sup>C specification and must be equal to '11110'. However, those bits

are compared by hardware and are not affected by the value in this register.

bit 2-1 ADD<2:1>: Two Most Significant bits of 10-bit address

bit 0 **Not used:** Unused in this mode. Bit state is a "don't care".

#### <u>10-Bit Slave mode — Least Significant Address Byte:</u>

bit 7-0 ADD<7:0>: Eight Least Significant bits of 10-bit address

#### 7-Bit Slave mode:

bit 7-1 **ADD<7:1>:** 7-bit address

bit 0 **Not used:** Unused in this mode. Bit state is a "don't care".

### 27.6 EUSART Operation During Sleep

The EUSART will remain active during Sleep only in the Synchronous Slave mode. All other modes require the system clock and therefore cannot generate the necessary signals to run the Transmit or Receive Shift registers during Sleep.

Synchronous Slave mode uses an externally generated clock to run the Transmit and Receive Shift registers.

## 27.6.1 SYNCHRONOUS RECEIVE DURING SLEEP

To receive during Sleep, all the following conditions must be met before entering Sleep mode:

- RCSTA and TXSTA Control registers must be configured for Synchronous Slave Reception (see Section 27.5.2.4 "Synchronous Slave Reception Set-up:").

- If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- The RCIF interrupt flag must be cleared by reading RCREG to unload any pending characters in the receive buffer.

Upon entering Sleep mode, the device will be ready to accept data and clocks on the RX/DT and TX/CK pins, respectively. When the data word has been completely clocked in by the external device, the RCIF interrupt flag bit of the PIR1 register will be set. Thereby, waking the processor from Sleep.

Upon waking from Sleep, the instruction following the SLEEP instruction will be executed. If the Global Interrupt Enable (GIE) bit of the INTCON register is also set, then the Interrupt Service Routine at address 004h will be called.

## 27.6.2 SYNCHRONOUS TRANSMIT DURING SLEEP

To transmit during Sleep, all the following conditions must be met before entering Sleep mode:

- RCSTA and TXSTA Control registers must be configured for synchronous slave transmission (see Section 27.5.2.2 "Synchronous Slave Transmission Set-up:").

- The TXIF interrupt flag must be cleared by writing the output data to the TXREG, thereby filling the TSR and transmit buffer.

- If interrupts are desired, set the TXIE bit of the PIE1 register and the PEIE bit of the INTCON register

- Interrupt enable bits TXIE of the PIE1 register and PEIE of the INTCON register must set.

Upon entering Sleep mode, the device will be ready to accept clocks on TX/CK pin and transmit data on the RX/DT pin. When the data word in the TSR has been completely clocked out by the external device, the pending byte in the TXREG will transfer to the TSR and the TXIF flag will be set. Thereby, waking the processor from Sleep. At this point, the TXREG is available to accept another character for transmission, which will clear the TXIF flag.

Upon waking from Sleep, the instruction following the SLEEP instruction will be executed. If the Global Interrupt Enable (GIE) bit is also set then the Interrupt Service Routine at address 0004h will be called.

#### 27.6.3 ALTERNATE PIN LOCATIONS

This module incorporates I/O pins that can be moved to other locations with the use of the alternate pin function register, APFCON. To determine which pins can be moved and what their default locations are upon a Reset, see **Section 13.1 "Alternate Pin Function"** for more information.

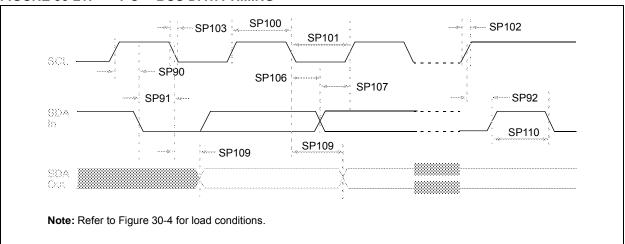

## TABLE 30-21: I<sup>2</sup>C™ BUS START/STOP BITS REQUIREMENTS

## Standard Operating Conditions (unless otherwise stated)

| Param<br>No. | Symbol  | Characteristic  |              | Min. | Тур | Max. | Units | Conditions                                            |  |

|--------------|---------|-----------------|--------------|------|-----|------|-------|-------------------------------------------------------|--|

| SP90*        | Tsu:sta | Start condition | 100 kHz mode | 4700 | _   | _    | ns    | Only relevant for Repeated Start condition            |  |

|              |         | Setup time      | 400 kHz mode | 600  | _   | _    |       |                                                       |  |

| SP91*        | THD:STA | Start condition | 100 kHz mode | 4000 | _   | _    |       | After this period, the first clock pulse is generated |  |

|              |         | Hold time       | 400 kHz mode | 600  | _   | _    |       |                                                       |  |

| SP92*        | Tsu:sto | Stop condition  | 100 kHz mode | 4700 | _   | _    | ns    |                                                       |  |

|              |         | Setup time      | 400 kHz mode | 600  | _   | _    |       |                                                       |  |

| SP93         | THD:STO | Stop condition  | 100 kHz mode | 4000 | _   |      | ns    |                                                       |  |

|              |         | Hold time       | 400 kHz mode | 600  | _   | _    |       |                                                       |  |

<sup>\*</sup> These parameters are characterized but not tested.

## FIGURE 30-21: I<sup>2</sup>C™ BUS DATA TIMING

Note: Unless otherwise noted, VIN = 5V, Fosc = 300 kHz, CIN = 0.1 μF, TA = 25°C.

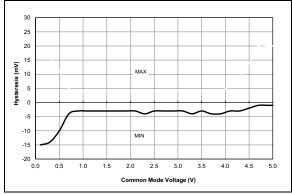

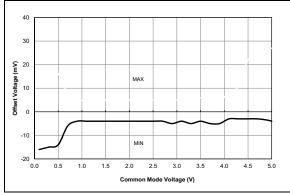

FIGURE 31-120: Comparator Offset, NP Mode (CxSP = 1), VDD = 5.0V, Typical Measured Values at 25°C, PIC16F1784/6/7 Only.

FIGURE 31-121: Comparator Offset, NP Mode (CxSP = 1), VDD = 5.0V, Typical Measured Values From -40°C to 125°C, PIC16F1784/6/7 Only.

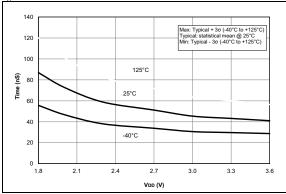

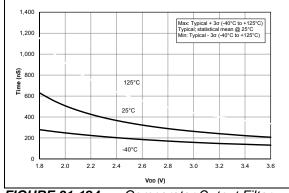

**FIGURE 31-122:** Comparator Response Time Over Voltage, NP Mode (CxSP = 1), Typical Measured Values, PIC16LF1784/6/7 Only.

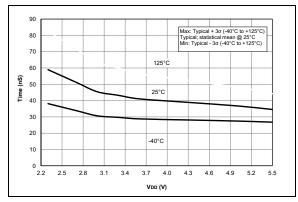

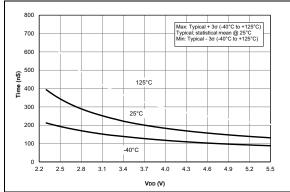

FIGURE 31-123: Comparator Response Time Over Voltage, NP Mode (CxSP = 1), Typical Measured Values, PIC16F1784/6/7 Only.

**FIGURE 31-124:** Comparator Output Filter Delay Time Over Temp., NP Mode (CxSP = 1), Typical Measured Values, PIC16LF1784/6/7 Only.

FIGURE 31-125: Comparator Output Filter

Delay Time Over Temp., NP Mode (CxSP = 1),

Typical Measured Values, PIC16F1784/6/7 Only.