Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PSMC, PWM, WDT                                |

| Number of I/O              | 35                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 14x12b; D/A 1x8b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 44-QFN (8x8)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1784-e-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|      | BANK 16   |      | BANK 16   |      | BANK 16   |

|------|-----------|------|-----------|------|-----------|

| 811h | PSMC1CON  | 831h | PSMC2CON  | 851h | PSMC3CON  |

| 812h | PSMC1MDL  | 832h | PSMC2MDL  | 852h | PSMC3MDL  |

| 813h | PSMC1SYNC | 833h | PSMC2SYNC | 853h | PSMC3SYNC |

| 814h | PSMC1CLK  | 834h | PSMC2CLK  | 854h | PSMC3CLK  |

| 815h | PSMC10EN  | 835h | PSMC2OEN  | 855h | PSMC3OEN  |

| 816h | PSMC1POL  | 836h | PSMC2POL  | 856h | PSMC3POL  |

| 817h | PSMC1BLNK | 837h | PSMC2BLNK | 857h | PSMC3BLNK |

| 818h | PSMC1REBS | 838h | PSMC2REBS | 858h | PSMC3REBS |

| 819h | PSMC1FEBS | 839h | PSMC2FEBS | 859h | PSMC3FEBS |

| 81Ah | PSMC1PHS  | 83Ah | PSMC2PHS  | 85Ah | PSMC3PHS  |

| 81Bh | PSMC1DCS  | 83Bh | PSMC2DCS  | 85Bh | PSMC3DCS  |

| 81Ch | PSMC1PRS  | 83Ch | PSMC2PRS  | 85Ch | PSMC3PRS  |

| 81Dh | PSMC1ASDC | 83Dh | PSMC2ASDC | 85Dh | PSMC3ASDC |

| 81Eh | PSMC1ASDD | 83Eh | PSMC2ASDD | 85Eh | PSMC3ASDD |

| 81Fh | PSMC1ASDS | 83Fh | PSMC2ASDS | 85Fh | PSMC3ASDS |

| 820h | PSMC1INT  | 840h | PSMC2INT  | 860h | PSMC3INT  |

| 821h | PSMC1PHL  | 841h | PSMC2PHL  | 861h | PSMC3PHL  |

| 822h | PSMC1PHH  | 842h | PSMC2PHH  | 862h | PSMC3PHH  |

| 823h | PSMC1DCL  | 843h | PSMC2DCL  | 863h | PSMC3DCL  |

| 824h | PSMC1DCH  | 844h | PSMC2DCH  | 864h | PSMC3DCH  |

| 825h | PSMC1PRL  | 845h | PSMC2PRL  | 865h | PSMC3PRL  |

| 826h | PSMC1PRH  | 846h | PSMC2PRH  | 866h | PSMC3PRH  |

| 827h | PSMC1TMRL | 847h | PSMC2TMRL | 867h | PSMC3TMRL |

| 828h | PSMC1TMRH | 848h | PSMC2TMRH | 868h | PSMC3TMRH |

| 829h | PSMC1DBR  | 849h | PSMC2DBR  | 869h | PSMC3DBR  |

| 82Ah | PSMC1DBF  | 84Ah | PSMC2DBF  | 86Ah | PSMC3DBF  |

| 82Bh | PSMC1BLKR | 84Bh | PSMC2BLKR | 86Bh | PSMC3BLKR |

| 82Ch | PSMC1BLKF | 84Ch | PSMC2BLKF | 86Ch | PSMC3BLKF |

| 82Dh | PSMC1FFA  | 84Dh | PSMC2FFA  | 86Dh | PSMC3FFA  |

| 82Eh | PSMC1STR0 | 84Eh | PSMC2STR0 | 86Eh | PSMC3STR0 |

| 82Fh | PSMC1STR1 | 84Fh | PSMC2STR1 | 86Fh | PSMC3STR1 |

| 830h | _         | 850h |           | 870h | —         |

TABLE 3-10: PIC16(L)F1784/6/7 MEMORY MAP (BANK 16 DETAILS)

Legend: Unimplemented data memory locations, read as '0'.

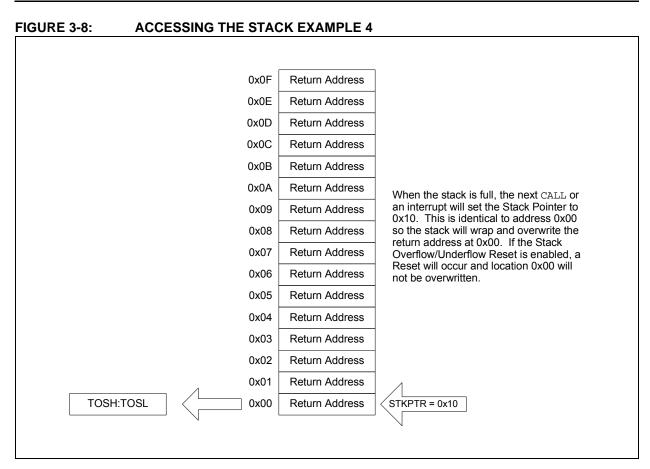

# 3.5.2 OVERFLOW/UNDERFLOW RESET

If the STVREN bit in Configuration Words is programmed to '1', the device will be reset if the stack is PUSHed beyond the sixteenth level or POPed beyond the first level, setting the appropriate bits (STKOVF or STKUNF, respectively) in the PCON register.

### 3.6 Indirect Addressing

The INDFn registers are not physical registers. Any instruction that accesses an INDFn register actually accesses the register at the address specified by the File Select Registers (FSR). If the FSRn address specifies one of the two INDFn registers, the read will return '0' and the write will not occur (though Status bits may be affected). The FSRn register value is created by the pair FSRnH and FSRnL.

The FSR registers form a 16-bit address that allows an addressing space with 65536 locations. These locations are divided into three memory regions:

- · Traditional Data Memory

- Linear Data Memory

- Program Flash Memory

# 5.13 Power Control (PCON) Register

The Power Control (PCON) register contains flag bits to differentiate between a:

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- Reset Instruction Reset (RI)

- MCLR Reset (RMCLR)

- Watchdog Timer Reset (RWDT)

- Stack Underflow Reset (STKUNF)

- Stack Overflow Reset (STKOVF)

# 5.14 Register Definitions: Power Control

#### REGISTER 5-2: PCON: POWER CONTROL REGISTER

| R/W/HS-0/q | R/W/HS-0/q | U-0 | R/W/HC-1/q | R/W/HC-1/q | R/W/HC-1/q | R/W/HC-q/u | R/W/HC-q/u |

|------------|------------|-----|------------|------------|------------|------------|------------|

| STKOVF     | STKUNF     | -   | RWDT       | RMCLR      | RI         | POR        | BOR        |

| bit 7      |            |     |            |            |            | •          | bit 0      |

| Legend:                    |                      |                                                       |

|----------------------------|----------------------|-------------------------------------------------------|

| HC = Bit is cleared by har | dware                | HS = Bit is set by hardware                           |

| R = Readable bit           | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged       | x = Bit is unknown   | -m/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set           | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7 | STKOVF: Stack Overflow Flag bit                                                                   |

|-------|---------------------------------------------------------------------------------------------------|

|       | 1 = A Stack Overflow occurred                                                                     |

|       | 0 = A Stack Overflow has not occurred or cleared by firmware                                      |

| bit 6 | STKUNF: Stack Underflow Flag bit                                                                  |

|       | 1 = A Stack Underflow occurred                                                                    |

|       | 0 = A Stack Underflow has not occurred or cleared by firmware                                     |

| bit 5 | Unimplemented: Read as '0'                                                                        |

| bit 4 | RWDT: Watchdog Timer Reset Flag bit                                                               |

|       | 1 = A Watchdog Timer Reset has not occurred or set to '1' by firmware                             |

|       | 0 = A Watchdog Timer Reset has occurred (cleared by hardware)                                     |

| bit 3 | RMCLR: MCLR Reset Flag bit                                                                        |

|       | 1 = A MCLR Reset has not occurred or set to '1' by firmware                                       |

|       | <ul> <li>A MCLR Reset has occurred (cleared by hardware)</li> </ul>                               |

| bit 2 | RI: RESET Instruction Flag bit                                                                    |

|       | 1 = A RESET instruction has not been executed or set to '1' by firmware                           |

|       | 0 = A RESET instruction has been executed (cleared by hardware)                                   |

| bit 1 | POR: Power-on Reset Status bit                                                                    |

|       | 1 = No Power-on Reset occurred                                                                    |

|       | 0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)             |

| bit 0 | BOR: Brown-out Reset Status bit                                                                   |

|       | 1 = No Brown-out Reset occurred                                                                   |

|       | 0 = A Brown-out Reset occurred (must be set in software after a Power-on Reset or Brown-out Reset |

|       | occurs)                                                                                           |

|       |                                                                                                   |

The PCON register bits are shown in Register 5-2.

#### TABLE 7-1: SUMMARY OF REGISTERS ASSOCIATED WITH REFERENCE CLOCK SOURCES

| Name    | Bit 7                                                                                            | Bit 6  | Bit 5   | Bit 4 | Bit 3   | Bit 2 | Bit 1       | Bit 0 | Register<br>on Page |  |

|---------|--------------------------------------------------------------------------------------------------|--------|---------|-------|---------|-------|-------------|-------|---------------------|--|

| CLKRCON | CLKREN                                                                                           | CLKROE | CLKRSLR | CLKRI | DC<1:0> | C     | LKRDIV<2:0> | >     | 86                  |  |

| Lonondi | Levend: unimplemented leasting read as (a). Cheded calls are not used by reference cleak sources |        |         |       |         |       |             |       |                     |  |

Legend: — = unimplemented locations read as '0'. Shaded cells are not used by reference clock sources.

#### TABLE 7-2: SUMMARY OF CONFIGURATION WORD WITH REFERENCE CLOCK SOURCES

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2  | Bit 9/1 | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|----------|----------|-----------|---------|---------|---------------------|

| CONFIG1 | 13:8 |         |         | FCMEN    | IESO     | CLKOUTEN | BOREI     | N<1:0>  | CPD     | 54                  |

| CONFIGT | 7:0  | CP      | MCLRE   | PWRTE    | WDTE     | E1<:0>   | FOSC<2:0> |         |         | 54                  |

Legend: — = unimplemented locations read as '0'. Shaded cells are not used by reference clock sources.

| U-0             | R/W-0/0            | R/W-0/0                       | R/W-0/0         | U-0             | R/W-0/0          | R/W-0/0          | R/W-0/0     |

|-----------------|--------------------|-------------------------------|-----------------|-----------------|------------------|------------------|-------------|

| 0-0             | PSMC3TIE           | PSMC2TIE                      | PSMC1TIE        | <u> </u>        | PSMC3SIE         | PSMC2SIE         | PSMC1SIE    |

| bit 7           | TOMOUTIL           | TOMOZITE                      | TOMOTHE         |                 | TOMOGOL          | TOMOZOIL         | bit 0       |

|                 |                    |                               |                 |                 |                  |                  |             |

| Legend:         |                    |                               |                 |                 |                  |                  |             |

| R = Readable    |                    | W = Writable                  |                 | •               | mented bit, read |                  |             |

| u = Bit is unc  | •                  | x = Bit is unkr               |                 | -n/n = Value    | at POR and BO    | R/Value at all o | ther Resets |

| '1' = Bit is se | t                  | '0' = Bit is clea             | ared            |                 |                  |                  |             |

| bit 7           | Unimplemen         | ted: Read as '                | כי              |                 |                  |                  |             |

| bit 6           | PSMC3TIE: F        | PSMC3 Time B                  | ase Interrupt E | Enable bit      |                  |                  |             |

|                 |                    | PSMC3 time ba<br>PSMC3 time b |                 |                 |                  |                  |             |

| bit 5           | PSMC2TIE: F        | PSMC2 Time B                  | ase Interrupt E | Enable bit      |                  |                  |             |

|                 |                    | PSMC2 time ba<br>PSMC2 time b |                 |                 |                  |                  |             |

| bit 4           | PSMC1TIE: F        | SMC1 Time B                   | ase Interrupt E | Enable bit      |                  |                  |             |

|                 |                    | PSMC1 time ba                 |                 |                 |                  |                  |             |

|                 | 0 = Disables       | PSMC1 time b                  | ase generated   | d interrupts    |                  |                  |             |

| bit 3           | Unimplemen         | ted: Read as '                | כ'              |                 |                  |                  |             |

| bit 2           | PSMC3SIE: F        | PSMC3 Auto-S                  | hutdown Inter   | rupt Enable bit | t                |                  |             |

|                 |                    | PSMC3 auto-sl                 |                 |                 |                  |                  |             |

|                 |                    | PSMC3 auto-s                  |                 | -               |                  |                  |             |

| bit 1           |                    | PSMC2 Auto-S                  |                 |                 | t                |                  |             |

|                 |                    | PSMC2 auto-sl                 |                 |                 |                  |                  |             |

|                 |                    | PSMC2 auto-s                  |                 | •               |                  |                  |             |

| bit 0           |                    | PSMC1 Auto-S                  |                 | -               | t                |                  |             |

|                 |                    | PSMC1 auto-sl<br>PSMC1 auto-s |                 |                 |                  |                  |             |

|                 |                    | i Givio i auto-s              |                 | ιαριο           |                  |                  |             |

|                 | it PEIE of the IN  |                               |                 |                 |                  |                  |             |

| Se              | et to enable any p | peripheral inter              | rupt.           |                 |                  |                  |             |

#### **REGISTER 8-5: PIE4: PERIPHERAL INTERRUPT ENABLE REGISTER 4**

# 12.6 Write Verify

Depending on the application, good programming practice may dictate that the value written to the data EEPROM or program memory should be verified (see Example 12-7) to the desired value to be written. Example 12-7 shows how to verify a write to EEPROM.

#### EXAMPLE 12-7: EEPROM WRITE VERIFY

| BANKSEI | l eedatl  | ;                    |

|---------|-----------|----------------------|

| MOVF    | EEDATL, W | ;EEDATL not changed  |

|         |           | ;from previous write |

| BSF     | EECON1, R | ) ;YES, Read the     |

|         |           | ;value written       |

| XORWF   | EEDATL, W | ;                    |

| BTFSS   | STATUS, Z | ;Is data the same    |

| GOTO    | WRITE_ERR | ;No, handle error    |

| :       |           | ;Yes, continue       |

| 1       |           |                      |

| Name    | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------------------|

| ANSELB  | —       | ANSB6   | ANSB5   | ANSB4   | ANSB3   | ANSB2   | ANSB1   | ANSB0   | 138                 |

| INLVLB  | INLVLB7 | INLVLB6 | INLVLB5 | INLVLB4 | INLVLB3 | INLVLB2 | INLVLB1 | INLVLB0 | 139                 |

| LATB    | LATB7   | LATB6   | LATB5   | LATB4   | LATB3   | LATB2   | LATB1   | LATB0   | 137                 |

| ODCONB  | ODB7    | ODB6    | ODB5    | ODB4    | ODB3    | ODB2    | ODB1    | ODB0    | 139                 |

| PORTB   | RB7     | RB6     | RB5     | RB4     | RB3     | RB2     | RB1     | RB0     | 137                 |

| SLRCONB | SLRB7   | SLRB6   | SLRB5   | SLRB4   | SLRB3   | SLRB2   | SLRB1   | SLRB0   | 139                 |

| TRISB   | TRISB7  | TRISB6  | TRISB5  | TRISB4  | TRISB3  | TRISB2  | TRISB1  | TRISB0  | 137                 |

| WPUB    | WPUB7   | WPUB6   | WPUB5   | WPUB4   | WPUB3   | WPUB2   | WPUB1   | WPUB0   | 138                 |

### TABLE 13-6: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

**Legend:** x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTB.

# 13.8 Register Definitions: PORTC

#### **REGISTER 13-19: PORTC: PORTC REGISTER**

| R/W-x/u | R/W-x/u           | R/W-x/u                                  | R/W-x/u            | R/W-x/u                                                                   | R/W-x/u                                                                                                 | R/W-x/u                                                                                                                     |

|---------|-------------------|------------------------------------------|--------------------|---------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| RC6     | RC5               | RC4                                      | RC3                | RC2                                                                       | RC1                                                                                                     | RC0                                                                                                                         |

|         |                   |                                          |                    |                                                                           |                                                                                                         | bit 0                                                                                                                       |

|         |                   |                                          |                    |                                                                           |                                                                                                         |                                                                                                                             |

|         |                   |                                          |                    |                                                                           |                                                                                                         |                                                                                                                             |

| t       | W = Writable I    | oit                                      | U = Unimplen       | nented bit, read                                                          | as '0'                                                                                                  |                                                                                                                             |

| nged    | x = Bit is unkn   | own                                      | -n/n = Value a     | at POR and BO                                                             | R/Value at all o                                                                                        | ther Resets                                                                                                                 |

|         | '0' = Bit is clea | ared                                     |                    |                                                                           |                                                                                                         |                                                                                                                             |

|         | t                 | t W = Writable I<br>nged x = Bit is unkn | t W = Writable bit | t W = Writable bit U = Unimpler<br>nged x = Bit is unknown -n/n = Value a | t W = Writable bit U = Unimplemented bit, read<br>aged x = Bit is unknown $-n/n = Value at POR and BOI$ | t W = Writable bit U = Unimplemented bit, read as '0'<br>nged x = Bit is unknown -n/n = Value at POR and BOR/Value at all o |

bit 7-0 RC<7:0>: PORTC General Purpose I/O Pin bits<sup>(1)</sup> 1 = Port pin is ≥ VIH 0 = Port pin is ≤ VIL

#### REGISTER 13-20: TRISC: PORTC TRI-STATE REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| TRISC7  | TRISC6  | TRISC5  | TRISC4  | TRISC3  | TRISC2  | TRISC1  | TRISC0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

**TRISC<7:0>:** PORTC Tri-State Control bits 1 = PORTC pin configured as an input (tri-stated)

0 = PORTC pin configured as an output

#### REGISTER 13-21: LATC: PORTC DATA LATCH REGISTER

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

| LATC7   | LATC6   | LATC5   | LATC4   | LATC3   | LATC2   | LATC1   | LATC0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-0 LATC<7:0>: PORTC Output Latch Value bits<sup>(1)</sup>

**Note 1:** Writes to PORTC are actually written to corresponding LATC register. Reads from PORTC register is return of actual I/O pin values.

**Note 1:** Writes to PORTC are actually written to corresponding LATC register. Reads from PORTC register is return of actual I/O pin values.

# 19.4 Operation During Sleep

When the device wakes up from Sleep through an interrupt or a Watchdog Timer time-out, the contents of the DAC1CON0 register are not affected. To minimize current consumption in Sleep mode, the voltage reference should be disabled.

#### 19.5 Effects of a Reset

A device Reset affects the following:

- DAC is disabled.

- DAC output voltage is removed from the DAC10UT pin.

- The DAC1R<7:0> range select bits are cleared.

| U-0                                     | R/W-0/0           | R/W-0/0               | R/W-0/0                     | R/W-0/0               | R/W-0/0               | R/W-0/0          | R/W-0/0     |

|-----------------------------------------|-------------------|-----------------------|-----------------------------|-----------------------|-----------------------|------------------|-------------|

| —                                       | PxPOLIN           | PxPOLF <sup>(1)</sup> | PxPOLE <sup>(1)</sup>       | PxPOLD <sup>(1)</sup> | PxPOLC <sup>(1)</sup> | PxPOLB           | PxPOLA      |

| bit 7                                   |                   |                       |                             |                       |                       |                  | bit 0       |

|                                         |                   |                       |                             |                       |                       |                  |             |

| Legend:                                 |                   |                       |                             |                       |                       |                  |             |

| R = Readable                            | e bit             | W = Writable          | bit                         | U = Unimpler          | mented bit, read      | as '0'           |             |

| u = Bit is unchanged x = Bit is unknown |                   |                       | nown                        | -n/n = Value a        | at POR and BO         | R/Value at all o | ther Resets |

| '1' = Bit is set '0' = Bit is cleared   |                   |                       |                             |                       |                       |                  |             |

|                                         |                   |                       |                             |                       |                       |                  |             |

| bit 7                                   | Unimplemen        | ted: Read as '        | 0'                          |                       |                       |                  |             |

| bit 6                                   | PxPOLIN: PS       | MCxIN Polarit         | y bit                       |                       |                       |                  |             |

|                                         | 1 = PSMCx         | IN input is activ     | e-low                       |                       |                       |                  |             |

|                                         | 0 = PSMCx         | IN input is activ     | e-high                      |                       |                       |                  |             |

| bit 5-0                                 | PxPOLy: PSI       | MCx Output y F        | Polarity bit <sup>(1)</sup> |                       |                       |                  |             |

|                                         | 1 = PWM P         | SMCx output y         | is active-low               |                       |                       |                  |             |

|                                         | 0 = PWM P         | SMCx output y         | is active-high              |                       |                       |                  |             |

| Note 1: Th                              | hese bits are not | implemented c         | n PSMC2.                    |                       |                       |                  |             |

#### REGISTER 24-8: PSMCxPOL: PSMC POLARITY CONTROL REGISTER

| REGISTER 24-9: | PSMCxBLNK: PSMC BLANKING CONTROL REGISTER |

|----------------|-------------------------------------------|

| U-0   | U-0 | R/W-0/0 | R/W-0/0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 |

|-------|-----|---------|---------|-----|-----|---------|---------|

| —     | —   | PxFEBM1 | PxFEBM0 | —   | —   | PxREBM1 | PxREBM0 |

| bit 7 |     |         |         |     |     |         | bit 0   |

| Legend:              |                   |                      |                                                       |

|----------------------|-------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     |                   | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged |                   | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is :       | set               | '0' = Bit is cleared |                                                       |

| bit 7-6              | Unimplen          | nented: Read as '0'  |                                                       |

| DIL 7-0              | ommpien           | nemeu. Reau as 0     |                                                       |

| bit 5-4              | lanking Mode bits |                      |                                                       |

|                      | 11 = Rese         | erved – do not use   |                                                       |

|                      | 10 = Rese         | erved – do not use   |                                                       |

|                      |                   |                      |                                                       |

- 01 = Immediate blanking

- 00 = No blanking

- bit 3-2 Unimplemented: Read as '0'

- bit 1-0 PxREBM<1:0> PSMC Rising Edge Blanking Mode bits

- 11 = Reserved do not use

- 10 = Reserved do not use

- 01 = Immediate blanking

- 00 = No blanking

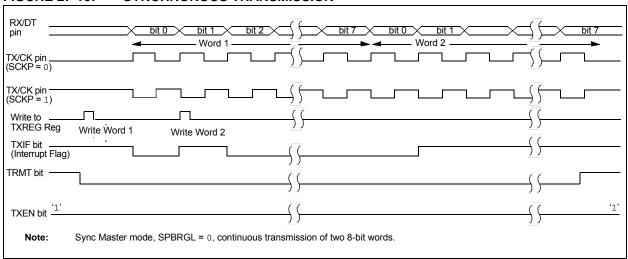

### FIGURE 27-10: SYNCHRONOUS TRANSMISSION

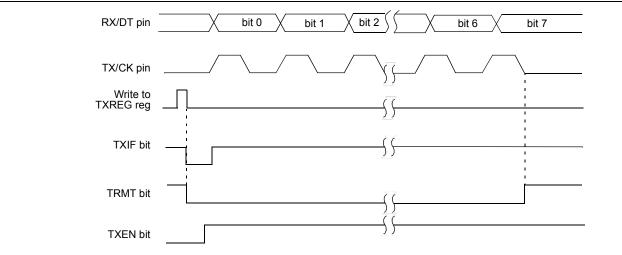

### FIGURE 27-11: SYNCHRONOUS TRANSMISSION (THROUGH TXEN)

# TABLE 27-7:SUMMARY OF REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER<br/>TRANSMISSION

| Name    | Bit 7                         | Bit 6                                                   | Bit 5       | Bit 4        | Bit 3       | Bit 2          | Bit 1       | Bit 0        | Register<br>on Page |

|---------|-------------------------------|---------------------------------------------------------|-------------|--------------|-------------|----------------|-------------|--------------|---------------------|

| APFCON1 | C2OUTSEL                      | CC1PSEL                                                 | SDOSEL      | SCKSEL       | SDISEL      | TXSEL          | RXSEL       | CCP2SEL      | 127                 |

| BAUDCON | ABDOVF                        | RCIDL                                                   | —           | SCKP         | BRG16       | —              | WUE         | ABDEN        | 347                 |

| INTCON  | GIE                           | PEIE                                                    | TMR0IE      | INTE         | IOCIE       | TMR0IF         | INTF        | IOCIF        | 93                  |

| PIE1    | TMR1GIE                       | ADIE                                                    | RCIE        | TXIE         | SSP1IE      | CCP1IE         | TMR2IE      | TMR1IE       | 94                  |

| PIR1    | TMR1GIF                       | ADIF                                                    | RCIF        | TXIF         | SSP1IF      | CCP1IF         | TMR2IF      | TMR1IF       | 98                  |

| RCSTA   | SPEN                          | RX9                                                     | SREN        | CREN         | ADDEN       | FERR           | OERR        | RX9D         | 346                 |

| SPBRGL  |                               | BRG<7:0>                                                |             |              |             |                |             |              | 348                 |

| SPBRGH  |                               |                                                         |             | BRG<         | 15:8>       |                |             |              | 348                 |

| TRISC   | TRISC7                        | TRISC7 TRISC6 TRISC5 TRISC4 TRISC3 TRISC2 TRISC1 TRISC0 |             |              |             |                |             |              |                     |

| TXREG   | EUSART Transmit Data Register |                                                         |             |              |             |                |             |              | 337*                |

| TXSTA   | CSRC                          | TX9                                                     | TXEN        | SYNC         | SENDB       | BRGH           | TRMT        | TX9D         | 345                 |

| Logond  | – unimplomo                   | ated leastion                                           | read as 'o' | Chadad calls | ore not use | d for overebro | nous mostor | tranamiaaian |                     |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for synchronous master transmission.

\* Page provides register information.

# 29.0 INSTRUCTION SET SUMMARY

Each instruction is a 14-bit word containing the operation code (opcode) and all required operands. The opcodes are broken into three broad categories.

- · Byte Oriented

- · Bit Oriented

- · Literal and Control

The literal and control category contains the most varied instruction word format.

Table 29-3 lists the instructions recognized by the MPASM  $^{\rm TM}$  assembler.

All instructions are executed within a single instruction cycle, with the following exceptions, which may take two or three cycles:

- Subroutine takes two cycles (CALL, CALLW)

- Returns from interrupts or subroutines take two cycles (RETURN, RETLW, RETFIE)

- Program branching takes two cycles (GOTO, BRA, BRW, BTFSS, BTFSC, DECFSZ, INCSFZ)

TABLE 29-1: OPCODE FIELD DESCRIPTIONS

| Field | Description                                                                                                                                                                       |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                              |

| W     | Working register (accumulator)                                                                                                                                                    |

| b     | Bit address within an 8-bit file register                                                                                                                                         |

| k     | Literal field, constant data or label                                                                                                                                             |

| x     | Don't care location (= $0$ or 1).<br>The assembler will generate code with x = $0$ .<br>It is the recommended form of use for<br>compatibility with all Microchip software tools. |

| d     | Destination select; d = 0: store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1.                                                                     |

| n     | FSR or INDF number. (0-1)                                                                                                                                                         |

| mm    | Pre-post increment-decrement mode selection                                                                                                                                       |

#### TABLE 29-2: ABBREVIATION DESCRIPTIONS

| Field | Description     |  |  |  |

|-------|-----------------|--|--|--|

| PC    | Program Counter |  |  |  |

| TO    | Time-Out bit    |  |  |  |

| С     | Carry bit       |  |  |  |

| DC    | Digit Carry bit |  |  |  |

| Z     | Zero bit        |  |  |  |

| PD    | Power-Down bit  |  |  |  |

One additional instruction cycle will be used when any instruction references an indirect file register and the file select register is pointing to program memory.

One instruction cycle consists of 4 oscillator cycles; for an oscillator frequency of 4 MHz, this gives a nominal instruction execution rate of 1 MHz.

All instruction examples use the format '0xhh' to represent a hexadecimal number, where 'h' signifies a hexadecimal digit.

### 29.1 Read-Modify-Write Operations

Any instruction that specifies a file register as part of the instruction performs a Read-Modify-Write (R-M-W) operation. The register is read, the data is modified, and the result is stored according to either the instruction, or the destination designator 'd'. A read operation is performed on a register even if the instruction writes to that register.

| Param<br>No. | Sym.   | Characteristic                                                      | Min.   | Тур† | Max.   | Units | Conditions                                    |

|--------------|--------|---------------------------------------------------------------------|--------|------|--------|-------|-----------------------------------------------|

|              |        | Program Memory<br>Programming Specifications                        |        |      |        |       |                                               |

| D110         | VIHH   | Voltage on MCLR/VPP/RE3 pin                                         | 8.0    | —    | 9.0    | V     | (Note 3)                                      |

| D111         | IDDP   | Supply Current during<br>Programming                                | —      | —    | 10     | mA    |                                               |

| D112         |        | VDD for Bulk Erase                                                  | 2.7    | —    | VDDMAX | V     |                                               |

| D113         | VPEW   | VDD for Write or Row Erase                                          | VDDMIN | —    | VDDMAX | V     |                                               |

| D114         | IPPPGM | Current on MCLR/VPP during<br>Erase/Write                           | —      | —    | 1.0    | mA    |                                               |

| D115         | IDDPGM | Current on VDD during Erase/Write                                   | —      |      | 5.0    | mA    |                                               |

|              |        | Data EEPROM Memory                                                  |        |      |        |       |                                               |

| D116         | ED     | Byte Endurance                                                      | 100K   | —    | _      | E/W   | -40°C to +85°C                                |

| D117         | VDRW   | VDD for Read/Write                                                  | VDDMIN | —    | VDDMAX | V     |                                               |

| D118         | TDEW   | Erase/Write Cycle Time                                              | —      | 4.0  | 5.0    | ms    |                                               |

| D119         | TRETD  | Characteristic Retention                                            | —      | 40   | _      | Year  | Provided no other specifications are violated |

| D120         | TREF   | Number of Total Erase/Write<br>Cycles before Refresh <sup>(2)</sup> | 100k   | _    | _      | E/W   | -40°C to +85°C                                |

|              |        | Program Flash Memory                                                |        |      |        |       |                                               |

| D121         | Eр     | Cell Endurance                                                      | 10K    | —    | _      | E/W   | -40°C to +85°C ( <b>Note 1</b> )              |

| D122         | Vpr    | VDD for Read                                                        | VDDMIN | —    | VDDMAX | V     |                                               |

| D123         | Tiw    | Self-timed Write Cycle Time                                         | —      | 2    | 2.5    | ms    |                                               |

| D124         | TRETD  | Characteristic Retention                                            | —      | 40   | -      | Year  | Provided no other specifications are violated |

# Standard Operating Conditions (unless otherwise stated)

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Self-write and Block Erase.

2: Refer to Section 12.2 "Using the Data EEPROM" for a more detailed discussion on data EEPROM endurance.

3: Required only if single-supply programming is disabled.

#### TABLE 30-20: SPI MODE REQUIREMENTS

| Param<br>No. | Symbol                | Characteristic                                                                                 |          | Min.        | Тур† | Max. | Units | Conditions |

|--------------|-----------------------|------------------------------------------------------------------------------------------------|----------|-------------|------|------|-------|------------|

| SP70*        | TssL2scH,<br>TssL2scL | $\overline{\mathrm{SS}}\downarrow$ to $\mathrm{SCK}\downarrow$ or $\mathrm{SCK}\uparrow$ input |          | 2.25*Tcy    |      | —    | ns    |            |

| SP71*        | TscH                  | SCK input high time (Slave mode)                                                               |          | Tcy + 20    | _    | _    | ns    |            |

| SP72*        | TscL                  | SCK input low time (Slave mode)                                                                |          | Tcy + 20    | _    | _    | ns    |            |

| SP73*        | TDIV2scH,<br>TDIV2scL | Setup time of SDI data input to SCK edge                                                       |          | 100         | _    | —    | ns    |            |

| SP74*        | TscH2diL,<br>TscL2diL | Hold time of SDI data input to SCK edge                                                        |          | 100         | _    | —    | ns    |            |

| SP75*        | TDOR                  | SDO data output rise time                                                                      | 3.0-5.5V | _           | 10   | 25   | ns    |            |

|              |                       |                                                                                                | 1.8-5.5V | _           | 25   | 50   | ns    |            |

| SP76*        | TDOF                  | SDO data output fall time                                                                      |          | _           | 10   | 25   | ns    |            |

| SP77*        | TssH2doZ              | SS↑ to SDO output high-impedance                                                               |          | 10          | _    | 50   | ns    |            |

| SP78*        | TscR                  | SCK output rise time<br>(Master mode)                                                          | 3.0-5.5V | _           | 10   | 25   | ns    |            |

|              |                       |                                                                                                | 1.8-5.5V | _           | 25   | 50   | ns    |            |

| SP79*        | TscF                  | SCK output fall time (Master mode)                                                             |          | _           | 10   | 25   | ns    |            |

| SP80*        | TscH2doV,<br>TscL2doV | SDO data output valid after SCK edge                                                           | 3.0-5.5V | _           |      | 50   | ns    |            |

|              |                       |                                                                                                | 1.8-5.5V | —           | _    | 145  | ns    |            |

| SP81*        | TDOV2scH,<br>TDOV2scL | SDO data output setup to SCK edge                                                              |          | Тсу         |      | —    | ns    |            |

| SP82*        | TssL2doV              | SDO data output valid after $\overline{SS}\downarrow$ edge                                     |          | _           |      | 50   | ns    |            |

| SP83*        | TscH2ssH,<br>TscL2ssH | SS ↑ after SCK edge                                                                            |          | 1.5Tcy + 40 |      | -    | ns    |            |

Standard Operating Conditions (unless otherwise stated)

These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

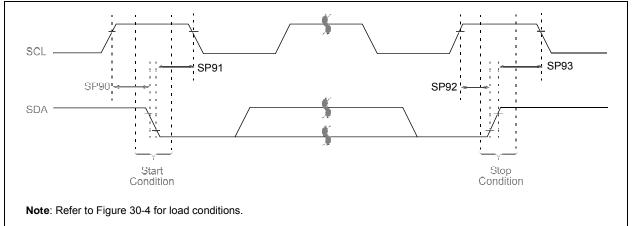

#### FIGURE 30-20: I<sup>2</sup>C<sup>™</sup> BUS START/STOP BITS TIMING

\*

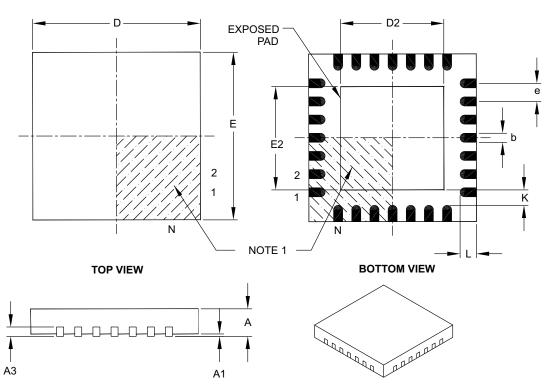

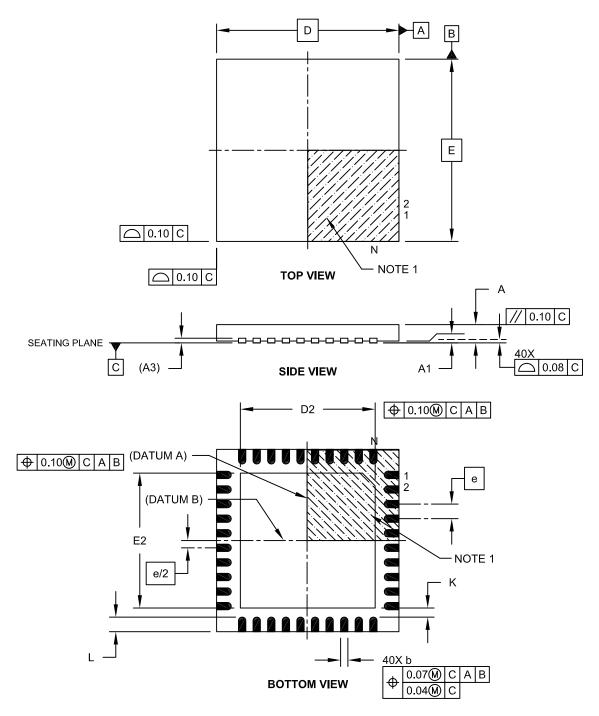

# 28-Lead Plastic Quad Flat, No Lead Package (ML) – 6x6 mm Body [QFN] with 0.55 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units            |          | MILLIMETERS | ;    |  |

|------------------------|------------------|----------|-------------|------|--|

| ]                      | Dimension Limits | MIN      | NOM         | MAX  |  |

| Number of Pins         | N                | 28       |             |      |  |

| Pitch                  | е                |          | 0.65 BSC    |      |  |

| Overall Height         | А                | 0.80     | 0.90        | 1.00 |  |

| Standoff               | A1               | 0.00     | 0.02        | 0.05 |  |

| Contact Thickness      | A3               | 0.20 REF |             |      |  |

| Overall Width          | E                |          | 6.00 BSC    |      |  |

| Exposed Pad Width      | E2               | 3.65     | 3.70        | 4.20 |  |

| Overall Length         | D                | 6.00 BSC |             |      |  |

| Exposed Pad Length     | D2               | 3.65     | 3.70        | 4.20 |  |

| Contact Width          | b                | 0.23     | 0.30        | 0.35 |  |

| Contact Length         | L                | 0.50     | 0.55        | 0.70 |  |

| Contact-to-Exposed Pad |                  | 0.20     | _           | _    |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-105B

40-Lead Ultra Thin Plastic Quad Flat, No Lead Package (MV) – 5x5x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-156A Sheet 1 of 2

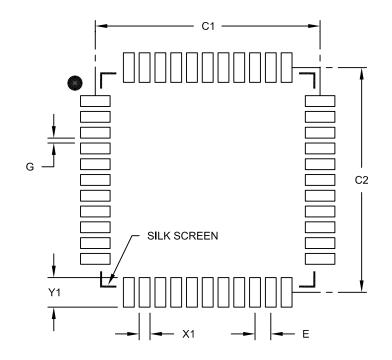

44-Lead Plastic Thin Quad Flatpack (PT) 10X10X1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

# RECOMMENDED LAND PATTERN

|                          | MILLIMETERS |      |          |      |

|--------------------------|-------------|------|----------|------|

| Dimension Limits         |             | MIN  | NOM      | MAX  |

| Contact Pitch            | E           |      | 0.80 BSC |      |

| Contact Pad Spacing      | C1          |      | 11.40    |      |

| Contact Pad Spacing      | C2          |      | 11.40    |      |

| Contact Pad Width (X44)  | X1          |      |          | 0.55 |

| Contact Pad Length (X44) | Y1          |      |          | 1.50 |

| Distance Between Pads    | G           | 0.25 |          |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2076B

# **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.                 | [X] <sup>(1)</sup> - X <u>/XX XXX</u><br>T Tape and Reel Temperature Package Pattern<br>Option Range      | Industrial temperature<br>PDIP package                                                                                                                                                                                                                                                         |

|--------------------------|-----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device:                  | PIC16F1784, PIC16LF1784,<br>PIC16F1786, PIC16LF1786,<br>PIC16F1787, PIC16LF1787                           | b) PIC16F1786- E/SS<br>Extended temperature,<br>SSOP package                                                                                                                                                                                                                                   |

| Tape and Reel<br>Option: | Blank = Standard packaging (tube or tray)<br>T = Tape and Reel <sup>(1)</sup>                             |                                                                                                                                                                                                                                                                                                |

| Temperature<br>Range:    | I = $-40^{\circ}$ C to $+85^{\circ}$ C (Industrial)<br>E = $-40^{\circ}$ C to $+125^{\circ}$ C (Extended) |                                                                                                                                                                                                                                                                                                |

| Package: <sup>(2)</sup>  |                                                                                                           | Note 1: Tape and Reel identifier only appears in<br>the catalog part number description. This<br>identifier is used for ordering purposes and<br>is not printed on the device package.<br>Check with your Microchip Sales Office<br>for package availability with the Tape and<br>Reel option. |

| Pattern:                 | QTP, SQTP, Code or Special Requirements (blank otherwise)                                                 | 2: Small form-factor packaging options may<br>be available. Please check<br><u>www.microchip.com/packaging</u> for<br>small-form factor package availability, or<br>contact your local Sales Office.                                                                                           |