#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PSMC, PWM, WDT                               |

| Number of I/O              | 35                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 512 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                               |

| Data Converters            | A/D 14x12b; D/A 1x8b                                                      |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                  |

| Supplier Device Package    | 40-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1784-e-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| 1.0   | Device Overview                                |     |

|-------|------------------------------------------------|-----|

| 2.0   | Enhanced Mid-Range CPU                         |     |

| 3.0   | Memory Organization                            | 23  |

| 4.0   | Device Configuration                           | 53  |

| 5.0   | Resets                                         | 59  |

| 6.0   | Oscillator Module                              | 67  |

| 7.0   | Reference Clock Module                         | 85  |

| 8.0   | Interrupts                                     |     |

| 9.0   | Power-Down Mode (Sleep)                        | 103 |

|       | Low Dropout (LDO) Voltage Regulator            |     |

| 11.0  | Watchdog Timer (WDT)                           |     |

| 12.0  | Date EEPROM and Flash Program Memory Control   |     |

| 13.0  | I/O Ports                                      | 125 |

| 14.0  | Interrupt-on-Change                            |     |

| 15.0  | Fixed Voltage Reference (FVR)                  |     |

|       | Temperature Indicator                          |     |

| 17.0  | Analog-to-Digital Converter (ADC) Module       |     |

| 18.0  | Operational Amplifier (OPA) Module             |     |

|       | Digital-to-Analog Converter (DAC) Module       |     |

|       | Comparator Module                              |     |

| 21.0  | Timer0 Module                                  | 196 |

|       | Timer1 Module                                  |     |

|       | Timer2 Module                                  |     |

|       | Programmable Switch Mode Control (PSMC) Module |     |

|       | Capture/Compare/PWM Module                     |     |

|       | Master Synchronous Serial Port (MSSP) Module   |     |

|       | · · · · · · · · · · · · · · · · · · ·          |     |

|       | In-Circuit Serial Programming™ (ICSP™)         |     |

|       | Instruction Set Summary                        |     |

|       | Electrical Specifications                      |     |

| 31.0  | DC and AC Characteristics Graphs and Tables    |     |

| 32.0  | Development Support                            |     |

|       | Packaging Information                          |     |

|       | ndix A: Revision History                       |     |

|       | Aicrochip Web Site                             |     |

|       | omer Change Notification Service               |     |

|       | omer Support                                   |     |

| Produ | uct Identification System                      | 462 |

| Addr             | Name                   | Bit 7                       | Bit 6          | Bit 5            | Bit 4           | Bit 3 | Bit 2                  | Bit 1                | Bit 0                | Value on<br>POR, BOR | Value on<br>all other<br>Resets |  |

|------------------|------------------------|-----------------------------|----------------|------------------|-----------------|-------|------------------------|----------------------|----------------------|----------------------|---------------------------------|--|

| Ban              | k 4                    | 1                           | 1              |                  | 1               | 1     | 1                      | 1                    | 1                    | 1                    | 1                               |  |

| 20Ch             | WPUA                   | WPUA7                       | WPUA6          | WPUA5            | WPUA4           | WPUA3 | WPUA2                  | WPUA1                | WPUA0                | 1111 1111            | 1111 1111                       |  |

| 20Dh             | WPUB                   | WPUB7                       | WPUB6          | WPUB5            | WPUB4           | WPUB3 | WPUB2                  | WPUB1                | WPUB0                | 1111 1111            | 1111 1111                       |  |

| 20Eh             | WPUC                   | WPUC7                       | WPUC6          | WPUC5            | WPUC4           | WPUC3 | WPUC2                  | WPUC1                | WPUC0                | 1111 1111            | 1111 1111                       |  |

| 20Fh             | WPUD <sup>(3)</sup>    | WPUD7                       | WPUD6          | WPUD5            | WPUD4           | WPUD3 | WPUD2                  | WPUD1                | WPUD0                | 1111 1111            |                                 |  |

| 210h             | WPUE                   | —                           | —              | —                | —               | WPUE3 | WPUE2 <sup>(3)</sup>   | WPUE1 <sup>(3)</sup> | WPUE0 <sup>(3)</sup> | 1111                 | 1111                            |  |

| 211h             | SSP1BUF                | Synchronous S               | Serial Port Re | ceive Buffer/Tra | ansmit Register |       |                        |                      |                      | XXXX XXXX            |                                 |  |

| 212h             | SSP1ADD                |                             |                |                  | ADD<            | 7:0>  |                        |                      |                      | 0000 0000            | 0000 0000                       |  |

| 213h             | SSP1MSK                |                             |                |                  | MSK<            | 7:0>  | 1                      | 1                    |                      | 1111 1111            | 1111 1111                       |  |

| 214h             | SSP1STAT               | SMP                         | CKE            | D/A              | Р               | S     | R/W                    | UA                   | BF                   | 0000 0000            | 0000 0000                       |  |

| 215h             | SSP1CON1               | WCOL                        | SSPOV          | SSPEN            | CKP             |       | SSPM                   | 1<3:0>               |                      | 0000 0000            | 0000 0000                       |  |

| 216h             | SSP1CON2               | GCEN                        | ACKSTAT        | ACKDT            | ACKEN           | RCEN  | PEN                    | RSEN                 | SEN                  | 0000 0000            | 0000 0000                       |  |

| 217h             | SSP1CON3               | ACKTIM                      | PCIE           | SCIE             | BOEN            | SDAHT | SBCDE                  | AHEN                 | DHEN                 | 0000 0000            | 0000 0000                       |  |

| 218h<br><br>21Fh | _                      | Unimplemente                | d              |                  |                 |       |                        |                      |                      | -                    | _                               |  |

| Ban              | k 5                    |                             |                |                  |                 |       |                        |                      |                      |                      |                                 |  |

| 28Ch             | ODCONA                 | Open Drain Co               | ontrol for POR | TA               |                 |       |                        |                      |                      | 0000 0000            | 0000 0000                       |  |

| 28Dh             | ODCONB                 | Open Drain Co               | ontrol for POR | TB               |                 |       |                        |                      |                      | 0000 0000            | 0000 0000                       |  |

| 28Eh             | ODCONC                 | Open Drain Co               | ontrol for POR | TC               |                 |       |                        |                      |                      | 0000 0000            | 0000 0000                       |  |

| 28Fh             | ODCOND <sup>(3)</sup>  | Open Drain Co               | ontrol for POR | TD               |                 |       |                        |                      |                      | 0000 0000            | 0000 0000                       |  |

| 290h             | ODCONE <sup>(3)</sup>  | _                           | —              | —                | —               | _     | ODE2                   | ODE1                 | ODE0                 | 000                  | uuu                             |  |

| 291h             | CCPR1L                 | Capture/Comp                | are/PWM Reg    | gister 1 (LSB)   |                 |       |                        |                      |                      | xxxx xxxx            | uuuu uuuu                       |  |

| 292h             | CCPR1H                 | Capture/Comp                | are/PWM Reg    | gister 1 (MSB)   |                 |       |                        |                      |                      | xxxx xxxx            | uuuu uuuu                       |  |

| 293h             | CCP1CON                | —                           | —              | DC1E             | 3<1:0>          |       | CCP1                   | M<3:0>               |                      | 00 0000              | 00 0000                         |  |

| 294h<br><br>297h | _                      | Unimplemente                | d              |                  |                 |       |                        |                      |                      | _                    | _                               |  |

| 298h             | CCPR2L                 | Capture/Comp                | are/PWM Reg    | gister 2 (LSB)   |                 |       |                        |                      |                      | xxxx xxxx            | uuuu uuuu                       |  |

| 299h             | CCPR2H                 | Capture/Comp                | are/PWM Reg    | gister 2 (MSB)   |                 |       |                        |                      |                      | xxxx xxxx            | uuuu uuuu                       |  |

| 29Ah             | CCP2CON                | _                           | _              | DC2E             | 3<1:0>          |       | CCP2                   | M<3:0>               |                      | 00 0000              | 00 0000                         |  |

| 29Bh             |                        |                             |                |                  |                 |       |                        |                      |                      |                      |                                 |  |

| 29Fh             | _                      | Unimplemente                | a              |                  |                 |       |                        |                      |                      | _                    | _                               |  |

| Ban              | k 6                    |                             |                |                  |                 |       |                        |                      |                      |                      | •                               |  |

| 30Ch             | SLRCONA                | Slew Rate Cor               | ntrol for PORT | A                |                 |       |                        |                      |                      | 0000 0000            | 0000 0000                       |  |

| 30Dh             | SLRCONB                | Slew Rate Control for PORTB |                |                  |                 |       |                        |                      |                      | 0000 0000            | 0000 0000                       |  |

| 30Eh             | SLRCONC                | Slew Rate Control for PORTC |                |                  |                 |       |                        | 0000 0000            | 0000 0000            |                      |                                 |  |

| 30Fh             | SLRCOND <sup>(3)</sup> | Slew Rate Cor               | ntrol for PORT | D                |                 |       |                        |                      |                      | 0000 0000            | 0000 0000                       |  |

| 310h             | SLRCONE <sup>(3)</sup> | -                           | —              | —                | —               | —     | SLRE2                  | SLRE1                | SLRE0                | 111                  | 111                             |  |

| 311h             | CCPR3L                 | Capture/Comp                | are/PWM Reg    | gister 3 (LSB)   |                 |       |                        |                      |                      | xxxx xxxx            | uuuu uuuu                       |  |

| 312h             | CCPR3H                 | Capture/Comp                | are/PWM Re     | gister 3 (MSB)   |                 |       |                        |                      |                      | xxxx xxxx            | uuuu uuuu                       |  |

| 313h             | CCP3CON                | -                           | —              | DC3E             | 3<1:0>          |       | CCP3                   | M<3:0>               |                      | 00 0000              | 00 0000                         |  |

| 314h<br>31Fh     | _                      | Unimplemente                | d              |                  |                 |       | - DC3B<1:0> CCP3M<3:0> |                      |                      |                      |                                 |  |

#### TABLE 3-12 SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

x = unknown, u = unchanged, q = value depends of Shaded locations are unimplemented, read as '0'. These registers can be addressed from any bank. Unimplemented, read as '1'. PIC16(L)F1784/7 only.

Note 1:

2:

3:

PIC16F1784/6/7 only. 4:

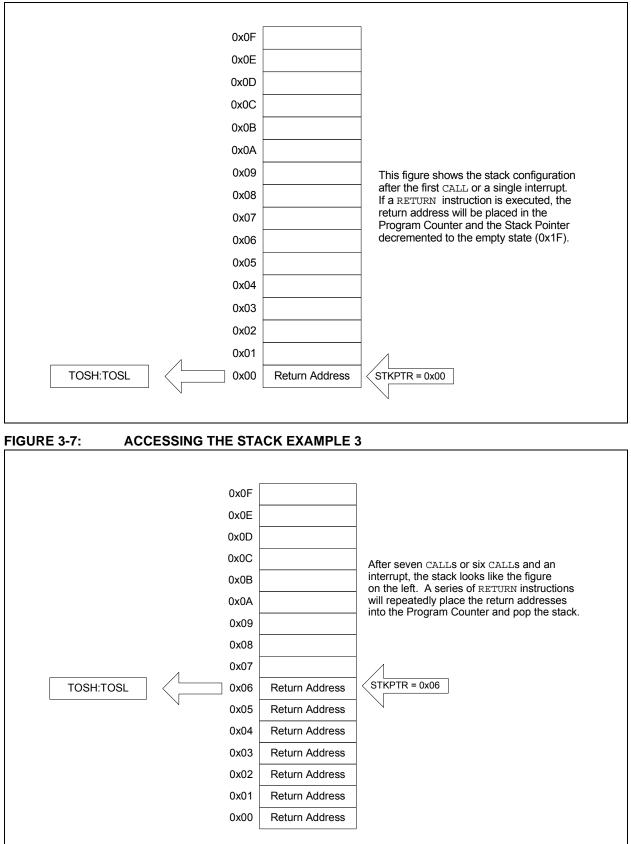

FIGURE 3-6: ACCESSING THE STACK EXAMPLE 2

## 6.3 Clock Switching

The system clock source can be switched between external and internal clock sources via software using the System Clock Select (SCS) bits of the OSCCON register. The following clock sources can be selected using the SCS bits:

- Default system oscillator determined by FOSC bits in Configuration Words

- Timer1 32 kHz crystal oscillator

- Internal Oscillator Block (INTOSC)

### 6.3.1 SYSTEM CLOCK SELECT (SCS) BITS

The System Clock Select (SCS) bits of the OSCCON register selects the system clock source that is used for the CPU and peripherals.

- When the SCS bits of the OSCCON register = 00, the system clock source is determined by the value of the FOSC<2:0> bits in the Configuration Words.

- When the SCS bits of the OSCCON register = 01, the system clock source is the Timer1 oscillator.

- When the SCS bits of the OSCCON register = 1x, the system clock source is chosen by the internal oscillator frequency selected by the IRCF<3:0> bits of the OSCCON register. After a Reset, the SCS bits of the OSCCON register are always cleared.

- Note: Any automatic clock switch, which may occur from Two-Speed Start-up or Fail-Safe Clock Monitor, does not update the SCS bits of the OSCCON register. The user can monitor the OSTS bit of the OSCSTAT register to determine the current system clock source.

When switching between clock sources, a delay is required to allow the new clock to stabilize. These oscillator delays are shown in Table 6-1.

## 6.3.2 OSCILLATOR START-UP TIMER STATUS (OSTS) BIT

The Oscillator Start-up Timer Status (OSTS) bit of the OSCSTAT register indicates whether the system clock is running from the external clock source, as defined by the FOSC<2:0> bits in the Configuration Words, or from the internal clock source. In particular, OSTS indicates that the Oscillator Start-up Timer (OST) has timed out for LP, XT or HS modes. The OST does not reflect the status of the Timer1 oscillator.

## 6.3.3 TIMER1 OSCILLATOR

The Timer1 oscillator is a separate crystal oscillator associated with the Timer1 peripheral. It is optimized for timekeeping operations with a 32.768 kHz crystal connected between the T1OSO and T1OSI device pins.

The Timer1 oscillator is enabled using the T1OSCEN control bit in the T1CON register. See **Section 22.0** "**Timer1 Module with Gate Control**" for more information about the Timer1 peripheral.

### 6.3.4 TIMER1 OSCILLATOR READY (T1OSCR) BIT

The user must ensure that the Timer1 oscillator is ready to be used before it is selected as a system clock source. The Timer1 Oscillator Ready (T1OSCR) bit of the OSCSTAT register indicates whether the Timer1 oscillator is ready to be used. After the T1OSCR bit is set, the SCS bits can be configured to select the Timer1 oscillator.

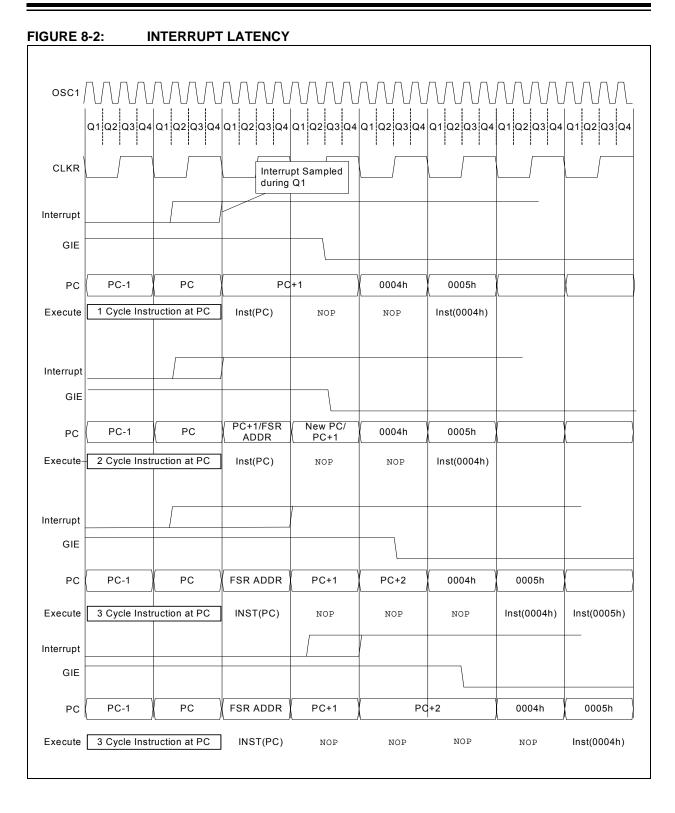

## 8.3 Interrupts During Sleep

Some interrupts can be used to wake from Sleep. To wake from Sleep, the peripheral must be able to operate without the system clock. The interrupt source must have the appropriate Interrupt Enable bit(s) set prior to entering Sleep.

On waking from Sleep, if the GIE bit is also set, the processor will branch to the interrupt vector. Otherwise, the processor will continue executing instructions after the SLEEP instruction. The instruction directly after the SLEEP instruction will always be executed before branching to the ISR. Refer to **Section 9.0** "**Power-Down Mode (Sleep)**" for more details.

## 8.4 INT Pin

The INT pin can be used to generate an asynchronous edge-triggered interrupt. This interrupt is enabled by setting the INTE bit of the INTCON register. The INTEDG bit of the OPTION\_REG register determines on which edge the interrupt will occur. When the INTEDG bit is set, the rising edge will cause the interrupt. When the INTEDG bit is clear, the falling edge will cause the interrupt. The INTF bit of the INTCON register will be set when a valid edge appears on the INT pin. If the GIE and INTE bits are also set, the processor will redirect program execution to the interrupt vector.

## 8.5 Automatic Context Saving

Upon entering an interrupt, the return PC address is saved on the stack. Additionally, the following registers are automatically saved in the shadow registers:

- W register

- STATUS register (except for TO and PD)

- · BSR register

- FSR registers

- PCLATH register

Upon exiting the Interrupt Service Routine, these registers are automatically restored. Any modifications to these registers during the ISR will be lost. If modifications to any of these registers are desired, the corresponding shadow register should be modified and the value will be restored when exiting the ISR. The shadow registers are available in Bank 31 and are readable and writable. Depending on the user's application, other registers may also need to be saved.

## 12.4 Modifying Flash Program Memory

When modifying existing data in a program memory row, and data within that row must be preserved, it must first be read and saved in a RAM image. Program memory is modified using the following steps:

- 1. Load the starting address of the row to be modified.

- 2. Read the existing data from the row into a RAM image.

- 3. Modify the RAM image to contain the new data to be written into program memory.

- 4. Load the starting address of the row to be rewritten.

- 5. Erase the program memory row.

- 6. Load the write latches with data from the RAM image.

- 7. Initiate a programming operation.

- 8. Repeat steps 6 and 7 as many times as required to reprogram the erased row.

## 12.5 User ID, Device ID and Configuration Word Access

Instead of accessing program memory or EEPROM data memory, the User ID's, Device ID/Revision ID and Configuration Words can be accessed when CFGS = 1 in the EECON1 register. This is the region that would be pointed to by PC<15> = 1, but not all addresses are accessible. Different access may exist for reads and writes. Refer to Table 12-2.

When read access is initiated on an address outside the parameters listed in Table 12-2, the EEDATH:EEDATL register pair is cleared.

| Address     | Function                    | Read Access | Write Access |

|-------------|-----------------------------|-------------|--------------|

| 8000h-8003h | User IDs                    | Yes         | Yes          |

| 8006h       | Device ID/Revision ID       | Yes         | No           |

| 8007h-8008h | Configuration Words 1 and 2 | Yes         | No           |

## TABLE 12-2: USER ID, DEVICE ID AND CONFIGURATION WORD ACCESS (CFGS = 1)

#### EXAMPLE 12-6: CONFIGURATION WORD AND DEVICE ID ACCESS

\* This code block will read 1 word of program memory at the memory address:

```

* PROG_ADDR_LO (must be 00h-08h) data will be returned in the variables;

```

\* PROG\_DATA\_HI, PROG\_DATA\_LO

| BANKSEL | EEADRL       | ; | Select correct Bank        |

|---------|--------------|---|----------------------------|

| MOVLW   | PROG_ADDR_LO | ; |                            |

| MOVWF   | EEADRL       | ; | Store LSB of address       |

| CLRF    | EEADRH       | ; | Clear MSB of address       |

|         |              |   |                            |

| BSF     | EECON1,CFGS  | ; | Select Configuration Space |

| BCF     | INTCON,GIE   | ; | Disable interrupts         |

| BSF     | EECON1,RD    | ; | Initiate read              |

| NOP     |              | ; | Executed (See Figure 12-1) |

| NOP     |              | ; | Ignored (See Figure 12-1)  |

| BSF     | INTCON,GIE   | ; | Restore interrupts         |

|         |              |   |                            |

| MOVF    | EEDATL,W     | ; | Get LSB of word            |

| MOVWF   | PROG_DATA_LO | ; | Store in user location     |

| MOVF    | EEDATH,W     | ; | Get MSB of word            |

| MOVWF   | PROG_DATA_HI | ; | Store in user location     |

|         |              |   |                            |

## 13.6 Register Definitions: PORTB

#### **REGISTER 13-11: PORTB: PORTB REGISTER**

| R/W-x/u                                 | R/W-x/u                           | R/W-x/u                                               | R/W-x/u | R/W-x/u                            | R/W-x/u | R/W-x/u | R/W-x/u |  |

|-----------------------------------------|-----------------------------------|-------------------------------------------------------|---------|------------------------------------|---------|---------|---------|--|

| RB7                                     | RB6                               | RB5                                                   | RB4     | RB3                                | RB2     | RB1     | RB0     |  |

| bit 7                                   |                                   |                                                       |         |                                    |         |         | bit 0   |  |

|                                         |                                   |                                                       |         |                                    |         |         |         |  |

| Legend:                                 |                                   |                                                       |         |                                    |         |         |         |  |

| R = Readable I                          | R = Readable bit W = Writable bit |                                                       | bit     | U = Unimplemented bit, read as '0' |         |         |         |  |

| u = Bit is unchanged x = Bit is unknown |                                   | -n/n = Value at POR and BOR/Value at all other Resets |         |                                    |         |         |         |  |

| '1' = Bit is set '0' = Bit is cleared   |                                   |                                                       | ared    |                                    |         |         |         |  |

bit 7-0 **RB<7:0>**: PORTB General Purpose I/O Pin bits<sup>(1)</sup> 1 = Port pin is ≥ VIH 0 = Port pin is ≤ VIL

## REGISTER 13-12: TRISB: PORTB TRI-STATE REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| TRISB7  | TRISB6  | TRISB5  | TRISB4  | TRISB3  | TRISB2  | TRISB1  | TRISB0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

TRISB<7:0>: PORTB Tri-State Control bits

1 = PORTB pin configured as an input (tri-stated)

0 = PORTB pin configured as an output

### REGISTER 13-13: LATB: PORTB DATA LATCH REGISTER

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

| LATB7   | LATB6   | LATB5   | LATB4   | LATB3   | LATB2   | LATB1   | LATB0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 LATB<7:0>: PORTB Output Latch Value bits<sup>(1)</sup>

**Note 1:** Writes to PORTB are actually written to corresponding LATB register. Reads from PORTB register is return of actual I/O pin values.

**Note 1:** Writes to PORTB are actually written to corresponding LATB register. Reads from PORTB register is return of actual I/O pin values.

## 17.1 ADC Configuration

When configuring and using the ADC the following functions must be considered:

- · Port configuration

- · Channel selection

- Single-ended

- Differential

- ADC voltage reference selection

- ADC conversion clock source

- · Interrupt control

- · Result formatting

## 17.1.1 PORT CONFIGURATION

The ADC can be used to convert both analog and digital signals. When converting analog signals, the I/O pin should be configured for analog by setting the associated TRIS and ANSEL bits. Refer to **Section 13.0 "I/O Ports"** for more information.

Note: Analog voltages on any pin that is defined as a digital input may cause the input buffer to conduct excess current.

### 17.1.2 CHANNEL SELECTION

There are up to 18 channel selections available:

- AN<13:8, 4:0> pins (PIC16(L)F1786 only)

- AN<21, 13:0> pins (PIC16(L)F1784/7 only)

- Temperature Indicator

- DAC\_output

- FVR (Fixed Voltage Reference) Output

Refer to Section 15.0 "Fixed Voltage Reference (FVR)" and Section 16.0 "Temperature Indicator Module" for more information on these channel selections.

When converting differential signals, the negative input for the channel is selected with the CHSN<3:0> bits of the ADCON2 register. Any positive input can be paired with any negative input to determine the differential channel.

The CHS<4:0> bits of the ADCON0 register determine which positive channel is selected.

When CHSN<3:0> = 1111 then the ADC is effectively a single ended ADC converter.

When changing channels, a delay is required before starting the next conversion.

## 17.1.3 ADC VOLTAGE REFERENCE

The ADPREF bits of the ADCON1 register provide control of the positive voltage reference. The positive voltage reference can be:

- VREF+

- VDD

- FVR Buffer1

The ADNREF bits of the ADCON1 register provide control of the negative voltage reference. The negative voltage reference can be:

- VREF- pin

- Vss

See **Section 15.0** "Fixed Voltage Reference (FVR)" for more details on the Fixed Voltage Reference.

## 17.1.4 CONVERSION CLOCK

The source of the conversion clock is software selectable via the ADCS bits of the ADCON1 register. There are seven possible clock options:

- Fosc/2

- Fosc/4

- Fosc/8

- Fosc/16

- Fosc/32

- Fosc/64

- FRC (dedicated internal FRC oscillator)

The time to complete one bit conversion is defined as TAD. One full 12-bit conversion requires 15 TAD periods as shown in Figure 17-2.

For correct conversion, the appropriate TAD specification must be met. Refer to the ADC conversion requirements in **Section 30.0 "Electrical Specifications"** for more information. Table 17-1 gives examples of appropriate ADC clock selections.

**Note:** Unless using the FRC, any changes in the system clock frequency will change the ADC clock frequency, which may adversely affect the ADC result.

## 18.1 Effects of Reset

A device Reset forces all registers to their Reset state. This disables the OPA module.

## 18.2 OPA Module Performance

Common AC and DC performance specifications for the OPA module:

- Common Mode Voltage Range

- Leakage Current

- Input Offset Voltage

- · Open Loop Gain

- · Gain Bandwidth Product

**Common mode voltage range** is the specified voltage range for the OPA+ and OPA- inputs, for which the OPA module will perform to within its specifications. The OPA module is designed to operate with input voltages between Vss and VDD. Behavior for Common mode voltages greater than VDD, or below Vss, are not guaranteed.

**Leakage current** is a measure of the small source or sink currents on the OPA+ and OPA- inputs. To minimize the effect of leakage currents, the effective impedances connected to the OPA+ and OPA- inputs should be kept as small as possible and equal.

**Input offset voltage** is a measure of the voltage difference between the OPA+ and OPA- inputs in a closed loop circuit with the OPA in its linear region. The offset voltage will appear as a DC offset in the output equal to the input offset voltage, multiplied by the gain of the circuit. The input offset voltage is also affected by the Common mode voltage. The OPA is factory calibrated to minimize the input offset voltage of the module.

**Open loop gain** is the ratio of the output voltage to the differential input voltage, (OPA+) - (OPA-). The gain is greatest at DC and falls off with frequency.

**Gain Bandwidth Product** or GBWP is the frequency at which the open loop gain falls off to 0 dB.

## 18.3 OPAxCON Control Register

The OPAxCON register, shown in Register 18-1, controls the OPA module.

The OPA module is enabled by setting the OPAxEN bit of the OPAxCON register. When enabled, the OPA forces the output driver of OPAxOUT pin into tri-state to prevent contention between the driver and the OPA output.

Note: When the OPA module is enabled, the OPAxOUT pin is driven by the op amp output, not by the PORT digital driver. Refer to the Electrical specifications for the op amp output drive capability.

## 19.0 DIGITAL-TO-ANALOG CONVERTER (DAC) MODULE

The Digital-to-Analog Converter supplies a variable voltage reference, ratiometric with the input source, with 256 selectable output levels.

The input of the DAC can be connected to:

- External VREF pins

- VDD supply voltage

- FVR (Fixed Voltage Reference)

The output of the DAC can be configured to supply a reference voltage to the following:

- Comparator positive input

- OpAmp positive input

- ADC input channel

- DAC1OUT1 pin

- DAC1OUT2 pin

The Digital-to-Analog Converter (DAC) is enabled by setting the DAC1EN bit of the DAC1CON0 register.

## 19.1 Output Voltage Selection

The DAC has 256 voltage level ranges. The 256 levels are set with the DAC1R<7:0> bits of the DAC1CON1 register.

The DAC output voltage is determined by Equation 19-1:

## EQUATION 19-1: DAC OUTPUT VOLTAGE

$$\frac{IF \ DACxEN = 1}{VOUT} = \left( (VSOURCE+ - VSOURCE-) \times \frac{DACxR[7:0]}{2^8} \right) + VSOURCE-$$

$$VSOURCE+ = VDD, \ VREF, \ or \ FVR \ BUFFER \ 2$$

$$VSOURCE- = VSS$$

## 19.2 Ratiometric Output Level

The DAC output value is derived using a resistor ladder with each end of the ladder tied to a positive and negative voltage reference input source. If the voltage of either input source fluctuates, a similar fluctuation will result in the DAC output value.

The value of the individual resistors within the ladder can be found in **Section 30.0** "**Electrical Specifications**".

## 19.3 DAC Voltage Reference Output

The DAC voltage can be output to the DAC1OUT1 and DAC1OUT2 pins by setting the respective DAC1OE1 and DAC1OE2 pins of the DAC1CON0 register. Selecting the DAC reference voltage for output on either DAC1OUTx pin automatically overrides the digital output buffer and digital input threshold detector functions of that pin. Reading the DAC1OUTx pin when it has been configured for DAC reference voltage output will always return a '0'.

Due to the limited current drive capability, a buffer must be used on the DAC voltage reference output for external connections to either DAC1OUTx pin. Figure 19-2 shows an example buffering technique.

| R/W-0/u          | R/W-0/u                                                                                                                                                                                                                                                                            | R/W-0/u                          | R/W-0/u        | R/W/HC-0/u                         | R-x/x           | R/W-0/u          | R/W-0/u      |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|----------------|------------------------------------|-----------------|------------------|--------------|--|--|

| TMR1GE           | T1GPOL                                                                                                                                                                                                                                                                             | T1GTM                            | T1GSPM         | T1GGO/<br>DONE                     | T1GVAL          | T1GS             | S<1:0>       |  |  |

| bit 7            |                                                                                                                                                                                                                                                                                    |                                  |                |                                    |                 |                  | bit 0        |  |  |

| Lovende          |                                                                                                                                                                                                                                                                                    |                                  |                |                                    |                 |                  |              |  |  |

| Legend:          | L:4                                                                                                                                                                                                                                                                                |                                  | L:4            |                                    | anted bit was   |                  |              |  |  |

| R = Readable     |                                                                                                                                                                                                                                                                                    | W = Writable                     |                | U = Unimplem                       |                 |                  | athar Decata |  |  |

| u = Bit is unch  | 0                                                                                                                                                                                                                                                                                  | x = Bit is unkl                  |                |                                    |                 | R/Value at all o | other Resets |  |  |

| '1' = Bit is set |                                                                                                                                                                                                                                                                                    | '0' = Bit is cle                 | ared           | HC = Bit is cle                    | ared by nardw   | /are             |              |  |  |

| bit 7            | <ul> <li>TMR1GE: Timer1 Gate Enable bit</li> <li><u>If TMR1ON = 0</u>:</li> <li>This bit is ignored</li> <li><u>If TMR1ON = 1</u>:</li> <li>1 = Timer1 counting is controlled by the Timer1 gate function</li> <li>0 = Timer1 counts regardless of Timer1 gate function</li> </ul> |                                  |                |                                    |                 |                  |              |  |  |

| bit 6            |                                                                                                                                                                                                                                                                                    | IGPOL: Timer1 Gate Polarity bit  |                |                                    |                 |                  |              |  |  |

|                  | 1 = Timer1 g                                                                                                                                                                                                                                                                       | gate is active-hi                | gh (Timer1 co  | unts when gate<br>nts when gate is |                 |                  |              |  |  |

| bit 5            | <b>T1GTM:</b> Timer1 Gate Toggle Mode bit<br>1 = Timer1 Gate Toggle mode is enabled<br>0 = Timer1 Gate Toggle mode is disabled and toggle flip-flop is cleared<br>Timer1 gate flip-flop toggles on every rising edge.                                                              |                                  |                |                                    |                 |                  |              |  |  |

| bit 4            | T1GSPM: Tir                                                                                                                                                                                                                                                                        | mer1 Gate Sing                   | gle-Pulse Mode | e bit                              |                 |                  |              |  |  |

|                  |                                                                                                                                                                                                                                                                                    | Gate Single-Pu<br>Gate Single-Pu |                | abled and is cor<br>abled          | ntrolling Timer | 1 gate           |              |  |  |

| bit 3            | T1GGO/DOM                                                                                                                                                                                                                                                                          | NE: Timer1 Gat                   | e Single-Pulse | Acquisition Sta                    | tus bit         |                  |              |  |  |

|                  | <ul> <li>1 = Timer1 gate single-pulse acquisition is ready, waiting for an edge</li> <li>0 = Timer1 gate single-pulse acquisition has completed or has not been started</li> </ul>                                                                                                 |                                  |                |                                    |                 |                  |              |  |  |

| bit 2            | <b>T1GVAL:</b> Timer1 Gate Current State bit<br>Indicates the current state of the Timer1 gate that could be provided to TMR1H:TMR1L.<br>Unaffected by Timer1 Gate Enable (TMR1GE).                                                                                                |                                  |                |                                    |                 |                  |              |  |  |

| bit 1-0          | T1GSS<1:0>                                                                                                                                                                                                                                                                         | : Timer1 Gate                    | Source Select  | bits                               |                 |                  |              |  |  |

|                  | <b>T1GSS&lt;1:0&gt;:</b> Timer1 Gate Source Select bits<br>11 = Comparator 2 optionally synchronized output (sync_C2OUT)<br>10 = Comparator 1 optionally synchronized output (sync_C1OUT)<br>01 = Timer0 overflow output<br>00 = Timer1 gate pin                                   |                                  |                |                                    |                 |                  |              |  |  |

## REGISTER 22-2: T1GCON: TIMER1 GATE CONTROL REGISTER

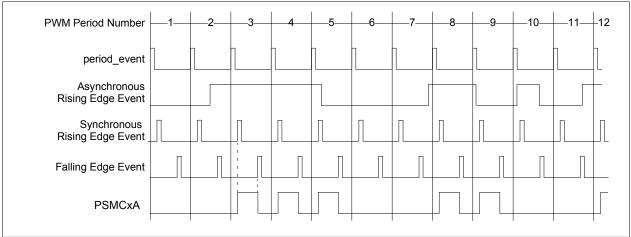

## 24.3.7 PULSE-SKIPPING PWM

The pulse-skipping PWM is used to generate a series of fixed-length pulses that can be triggered at each period event. A rising edge event will be generated when any enabled asynchronous rising edge input is active when the period event occurs, otherwise no event will be generated.

The rising edge event occurs based upon the value in the PSMCxPH register pair.

The falling edge event always occurs according to the enabled event inputs without qualification between any two inputs.

#### 24.3.7.1 Mode Features

- · No dead-band control available

- No steering control available

- PWM is output to only one pin:

- PSMCxA

## 24.3.7.2 Waveform Generation

#### Rising Edge Event

If any enabled asynchronous rising edge event = 1 when there is a period event, then upon the next synchronous rising edge event:

PSMCxA is set active

Falling Edge Event

PSMCxA is set inactive

**Note:** To use this mode, an external source must be used for the determination of whether or not to generate the set pulse. If the phase time base is used, it will either always generate a pulse or never generate a pulse based on the PSMCxPH value.

#### FIGURE 24-10: PULSE-SKIPPING PWM WAVEFORM

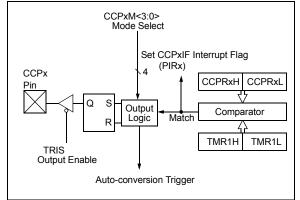

## 25.2 Compare Mode

The Compare mode function described in this section is available and identical for all CCP modules.

Compare mode makes use of the 16-bit Timer1 resource. The 16-bit value of the CCPRxH:CCPRxL register pair is constantly compared against the 16-bit value of the TMR1H:TMR1L register pair. When a match occurs, one of the following events can occur:

- Toggle the CCPx output

- · Set the CCPx output

- · Clear the CCPx output

- · Generate an Auto-conversion Trigger

- · Generate a Software Interrupt

The action on the pin is based on the value of the CCPxM<3:0> control bits of the CCPxCON register. At the same time, the interrupt flag CCPxIF bit is set.

All Compare modes can generate an interrupt.

Figure 25-2 shows a simplified diagram of the compare operation.

## FIGURE 25-2: COMPARE MODE OPERATION BLOCK DIAGRAM

## 25.2.1 CCPX PIN CONFIGURATION

The user must configure the CCPx pin as an output by clearing the associated TRIS bit.

The CCP2 pin function can be moved to alternate pins using the APFCON register (Register 13-1). Refer to **Section 13.1 "Alternate Pin Function"** for more details.

| Note: | Clearing the CCPxCON register will force    |

|-------|---------------------------------------------|

|       | the CCPx compare output latch to the        |

|       | default low level. This is not the PORT I/O |

|       | data latch.                                 |

## 25.2.2 TIMER1 MODE RESOURCE

In Compare mode, Timer1 must be running in either Timer mode or Synchronized Counter mode. The compare operation may not work in Asynchronous Counter mode. See **Section 22.0 "Timer1 Module with Gate Control"** for more information on configuring Timer1.

Note: Clocking Timer1 from the system clock (Fosc) should not be used in Compare mode. In order for Compare mode to recognize the trigger event on the CCPx pin, TImer1 must be clocked from the instruction clock (Fosc/4) or from an external clock source.

### 25.2.3 SOFTWARE INTERRUPT MODE

When Generate Software Interrupt mode is chosen (CCPxM<3:0> = 1010), the CCPx module does not assert control of the CCPx pin (see the CCPxCON register).

## 25.2.4 AUTO-CONVERSION TRIGGER

When Auto-conversion Trigger mode is chosen (CCPxM<3:0> = 1011), the CCPx module does the following:

- Resets Timer1

- · Starts an ADC conversion if ADC is enabled

The CCPx module does not assert control of the CCPx pin in this mode.

The Auto-conversion Trigger output of the CCP occurs immediately upon a match between the TMR1H, TMR1L register pair and the CCPRxH, CCPRxL register pair. The TMR1H, TMR1L register pair is not reset until the next rising edge of the Timer1 clock. The Auto-conversion Trigger output starts an ADC conversion (if the ADC module is enabled). This allows the CCPRxH, CCPRxL register pair to effectively provide a 16-bit programmable period register for Timer1.

Refer to **Section 17.2.5 "Auto-Conversion Trigger"** for more information.

- **Note 1:** The Auto-conversion Trigger from the CCP module does not set interrupt flag bit TMR1IF of the PIR1 register.

- 2: Removing the match condition by changing the contents of the CCPRxH and CCPRxL register pair, between the clock edge that generates the Auto-conversion Trigger and the clock edge that generates the Timer1 Reset, will preclude the Reset from occurring.

## 25.2.5 COMPARE DURING SLEEP

The Compare mode is dependent upon the system clock (Fosc) for proper operation. Since Fosc is shut down during Sleep mode, the Compare mode will not function properly during Sleep.

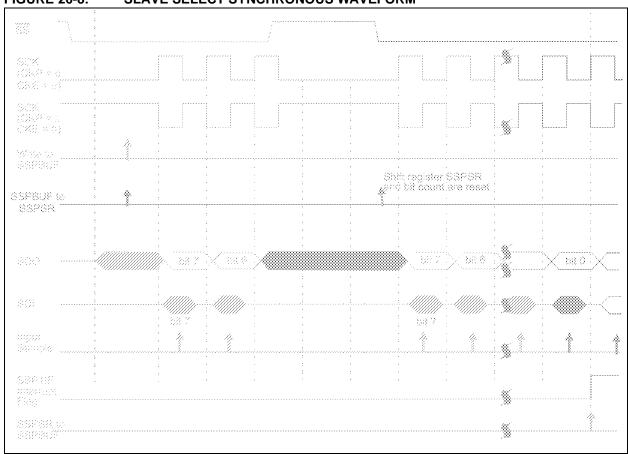

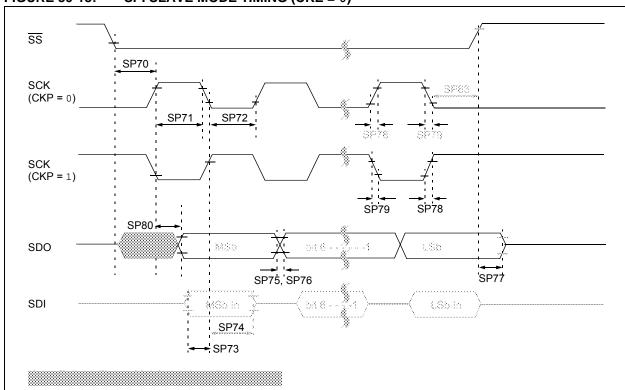

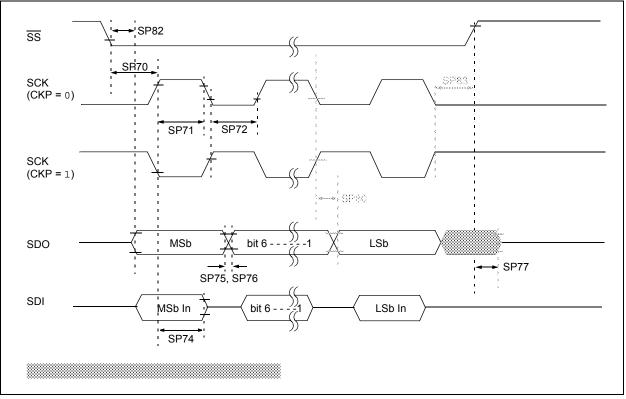

## FIGURE 26-8: SLAVE SELECT SYNCHRONOUS WAVEFORM

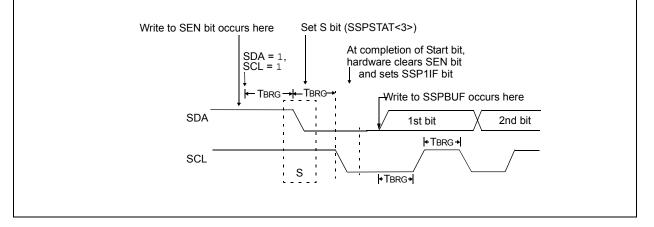

### 26.6.4 I<sup>2</sup>C MASTER MODE START CONDITION TIMING

To initiate a Start condition, the user sets the Start Enable bit, SEN bit of the SSPCON2 register. If the SDA and SCL pins are sampled high, the Baud Rate Generator is reloaded with the contents of SSPADD<7:0> and starts its count. If SCL and SDA are both sampled high when the Baud Rate Generator times out (TBRG), the SDA pin is driven low. The action of the SDA being driven low while SCL is high is the Start condition and causes the S bit of the SSPSTAT1 register to be set. Following this, the Baud Rate Generator is reloaded with the contents of SSPADD<7:0> and resumes its count. When the Baud Rate Generator times out (TBRG), the SEN bit of the SSPCON2 register will be automatically cleared by hardware; the Baud Rate Generator is suspended, leaving the SDA line held low and the Start condition is complete.

the SDA and SCL pins are already sampled low, or if during the Start condition, the SCL line is sampled low before the SDA line is driven low, a bus collision occurs, the Bus Collision Interrupt Flag, BCL1IF, is set, the Start condition is aborted and the I<sup>2</sup>C module is reset into its Idle state.

Note 1: If at the beginning of the Start condition,

2: The Philips I<sup>2</sup>C specification states that a bus collision cannot occur on a Start.

## FIGURE 26-26: FIRST START BIT TIMING

| Configuration Bits |       |      |                     | Dourd Data Formula |  |  |

|--------------------|-------|------|---------------------|--------------------|--|--|

| SYNC               | BRG16 | BRGH | BRG/EUSART Mode     | Baud Rate Formula  |  |  |

| 0                  | 0     | 0    | 8-bit/Asynchronous  | Fosc/[64 (n+1)]    |  |  |

| 0                  | 0     | 1    | 8-bit/Asynchronous  |                    |  |  |

| 0                  | 1     | 0    | 16-bit/Asynchronous | Fosc/[16 (n+1)]    |  |  |

| 0                  | 1     | 1    | 16-bit/Asynchronous |                    |  |  |

| 1                  | 0     | x    | 8-bit/Synchronous   | Fosc/[4 (n+1)]     |  |  |

| 1                  | 1     | х    | 16-bit/Synchronous  |                    |  |  |

## TABLE 27-3: BAUD RATE FORMULAS

Legend: x = Don't care, n = value of SPBRGH, SPBRGL register pair

#### TABLE 27-4: SUMMARY OF REGISTERS ASSOCIATED WITH THE BAUD RATE GENERATOR

| Name    | Bit 7     | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Register<br>on Page |

|---------|-----------|-------|-------|-------|-------|-------|-------|-------|---------------------|

| BAUDCON | ABDOVF    | RCIDL | —     | SCKP  | BRG16 | —     | WUE   | ABDEN | 347                 |

| RCSTA   | SPEN      | RX9   | SREN  | CREN  | ADDEN | FERR  | OERR  | RX9D  | 346                 |

| SPBRGL  | BRG<7:0>  |       |       |       |       |       | 348   |       |                     |

| SPBRGH  | BRG<15:8> |       |       |       |       |       | 348   |       |                     |

| TXSTA   | CSRC      | TX9   | TXEN  | SYNC  | SENDB | BRGH  | TRMT  | TX9D  | 345                 |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used for the Baud Rate Generator.

\* Page provides register information.

## FIGURE 30-18: SPI SLAVE MODE TIMING (CKE = 0)

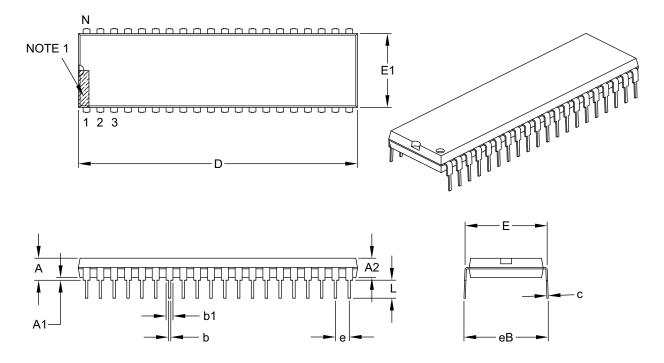

## 40-Lead Plastic Dual In-Line (P) – 600 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units                   |          | INCHES |       |

|----------------------------|-------------------------|----------|--------|-------|

|                            | <b>Dimension Limits</b> | MIN      | NOM    | MAX   |

| Number of Pins             | N                       |          | 40     |       |

| Pitch                      | e                       | .100 BSC |        |       |

| Top to Seating Plane       | A                       | -        | -      | .250  |

| Molded Package Thickness   | A2                      | .125     | -      | .195  |

| Base to Seating Plane      | A1                      | .015     | -      | _     |

| Shoulder to Shoulder Width | E                       | .590     | -      | .625  |

| Molded Package Width       | E1                      | .485     | -      | .580  |

| Overall Length             | D                       | 1.980    | -      | 2.095 |

| Tip to Seating Plane       | L                       | .115     | -      | .200  |

| Lead Thickness             | С                       | .008     | -      | .015  |

| Upper Lead Width           | b1                      | .030     | -      | .070  |

| Lower Lead Width           | b                       | .014     | -      | .023  |

| Overall Row Spacing §      | eB                      | -        | -      | .700  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-016B