Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PSMC, PWM, WDT                                |

| Number of I/O              | 35                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 14x12b; D/A 1x8b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 44-QFN (8x8)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1784-i-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **TABLE 1-2:** PIC16(L)F1784/6/7 PINOUT DESCRIPTION (CONTINUED)

| Name                           | Function | Input<br>Type | Output<br>Type | Description                         |  |  |

|--------------------------------|----------|---------------|----------------|-------------------------------------|--|--|

| RE2 <sup>(3)</sup> /AN7/PSMC3A | RE2      | TTL/ST        | CMOS           | General purpose I/O.                |  |  |

|                                | AN7      | AN            |                | ADC Channel 7 input.                |  |  |

|                                | PSMC3A   | —             | CMOS           | PSMC3 output A.                     |  |  |

| RE3/MCLR/VPP                   | RE3      | TTL/ST        |                | General purpose input.              |  |  |

|                                | MCLR     | ST            |                | Master Clear with internal pull-up. |  |  |

|                                | Vpp      | HV            | _              | Programming voltage.                |  |  |

| Vdd                            | Vdd      | Power         |                | Positive supply.                    |  |  |

| Vss                            | Vss      | Power         | _              | Ground reference.                   |  |  |

**Legend:** AN = Analog input or output CMOS = CMOS compatible input or output

OD = Open Drain

TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels I<sup>2</sup>C<sup>™</sup> = Schmitt Trigger input with I<sup>2</sup>C HV = High Voltage XTAL = Crystal levels

Note 1: Pin functions can be assigned to one of two locations via software. See Register 13-1.

2: All pins have interrupt-on-change functionality.

3: PIC16(L)F1784/7 only.

4: PIC16(L)F1786 only.

#### 3.2.1.1 STATUS Register

The STATUS register, shown in Register 3-1, contains:

- the arithmetic status of the ALU

- · the Reset status

The STATUS register can be the destination for any instruction, like any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

#### 3.3 Register Definitions: Status

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS register as '000u uluu' (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect any Status bits. For other instructions not affecting any Status bits (Refer to **Section 29.0** "Instruction Set Summary").

| Note: | The C and DC bits operate as Borrow and |   |  |  |  |  |  |  |  |  |  |

|-------|-----------------------------------------|---|--|--|--|--|--|--|--|--|--|

|       | Digit Borrow out bits, respectively, ir | ۱ |  |  |  |  |  |  |  |  |  |

|       | subtraction.                            |   |  |  |  |  |  |  |  |  |  |

| REGISTER 3-1: STATUS: S | TATUS REGISTER |

|-------------------------|----------------|

|-------------------------|----------------|

| U-0              | U-0                                                                                                                                                    | U-0                                                                                       | R-1/q                                                                                       | R-1/q         | R/W-0/u          | R/W-0/u           | R/W-0/u          |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|---------------|------------------|-------------------|------------------|--|--|--|--|--|

| _                | _                                                                                                                                                      | _                                                                                         | TO                                                                                          | PD            | Z                | DC <sup>(1)</sup> | C <sup>(1)</sup> |  |  |  |  |  |

| bit 7            |                                                                                                                                                        |                                                                                           |                                                                                             |               |                  |                   | bit 0            |  |  |  |  |  |

| Logondu          |                                                                                                                                                        |                                                                                           |                                                                                             |               |                  |                   | ]                |  |  |  |  |  |

| R = Readable     | Legend:<br>R = Readable bit U = Unimplemented bit, read as '0'                                                                                         |                                                                                           |                                                                                             |               |                  |                   |                  |  |  |  |  |  |

| u = Bit is unch  |                                                                                                                                                        | x = Bit is unkn                                                                           |                                                                                             | •             | at POR and BOI   |                   | thor Posots      |  |  |  |  |  |

| '1' = Bit is set | langeu                                                                                                                                                 | 6'' = Bit is clear                                                                        |                                                                                             |               |                  |                   | ITEL RESELS      |  |  |  |  |  |

| I = BILIS SEL    |                                                                                                                                                        |                                                                                           | areu                                                                                        | q = value dep | pends on conditi |                   |                  |  |  |  |  |  |

| bit 7-5          | Unimplemen                                                                                                                                             | ted: Read as '0                                                                           | )'                                                                                          |               |                  |                   |                  |  |  |  |  |  |

| bit 4            | TO: Time-Out                                                                                                                                           |                                                                                           |                                                                                             |               |                  |                   |                  |  |  |  |  |  |

|                  |                                                                                                                                                        | er-up, CLRWDT                                                                             |                                                                                             | SLEEP instruc | tion             |                   |                  |  |  |  |  |  |

| bit 3            | PD: Power-D                                                                                                                                            | own bit                                                                                   |                                                                                             |               |                  |                   |                  |  |  |  |  |  |

|                  |                                                                                                                                                        | er-up or by the<br>tion of the SLEE                                                       |                                                                                             |               |                  |                   |                  |  |  |  |  |  |

| bit 2            | Z: Zero bit                                                                                                                                            |                                                                                           |                                                                                             |               |                  |                   |                  |  |  |  |  |  |

|                  | <ul> <li>1 = The result of an arithmetic or logic operation is zero</li> <li>0 = The result of an arithmetic or logic operation is not zero</li> </ul> |                                                                                           |                                                                                             |               |                  |                   |                  |  |  |  |  |  |

| bit 1            | DC: Digit Car                                                                                                                                          | DC: Digit Carry/Digit Borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions) <sup>(1)</sup> |                                                                                             |               |                  |                   |                  |  |  |  |  |  |

|                  |                                                                                                                                                        | ut from the 4th                                                                           |                                                                                             |               | curred           |                   |                  |  |  |  |  |  |

|                  |                                                                                                                                                        | out from the 4th                                                                          |                                                                                             |               |                  |                   |                  |  |  |  |  |  |

| bit 0            | C: Carry/Borr                                                                                                                                          | ow bit <sup>(1)</sup> (ADDW                                                               | C: Carry/Borrow bit <sup>(1)</sup> (ADDWF, ADDLW, SUBLW, SUBWF instructions) <sup>(1)</sup> |               |                  |                   |                  |  |  |  |  |  |

- 1 = A carry-out from the Most Significant bit of the result occurred

0 = No carry-out from the Most Significant bit of the result occurred

- **Note 1:** For Borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand.

| U-0                        | R/W-0/0                            | R/W-0/0                                                                           | R/W-0/0         | U-0          | R/W-0/0           | R/W-0/0           | R/W-0/0     |  |  |  |  |  |

|----------------------------|------------------------------------|-----------------------------------------------------------------------------------|-----------------|--------------|-------------------|-------------------|-------------|--|--|--|--|--|

| _                          | PSMC3TIF                           | PSMC2TIF                                                                          | PSMC1TIF        | —            | PSMC3SIF          | PSMC2SIF          | PSMC1SIF    |  |  |  |  |  |

| bit 7                      |                                    |                                                                                   |                 |              |                   |                   | bit         |  |  |  |  |  |

| <del></del>                |                                    |                                                                                   |                 |              |                   |                   |             |  |  |  |  |  |

| Legend:<br>R = Read        | labla bit                          | W = Writable                                                                      | hit             | II – Unimple | emented bit, read |                   |             |  |  |  |  |  |

|                            | unchanged                          | x = Bit is unkr                                                                   |                 | •            | at POR and BO     |                   | thar Pacata |  |  |  |  |  |

| u = Bit is<br>(1) = Bit is | •                                  | 6'' = Bit is clear                                                                |                 |              | at FOR and BO     | R/ value at all C |             |  |  |  |  |  |

|                            | 5 361                              |                                                                                   | areu            |              |                   |                   |             |  |  |  |  |  |

| bit 7                      | Unimplemen                         | ted: Read as '                                                                    | 0'              |              |                   |                   |             |  |  |  |  |  |

| bit 6                      | PSMC3TIF: F                        | SMC3 Time B                                                                       | ase Interrupt F | -lag bit     |                   |                   |             |  |  |  |  |  |

|                            | 1 = Interrupt i<br>0 = Interrupt i |                                                                                   |                 |              |                   |                   |             |  |  |  |  |  |

| bit 5                      | PSMC2TIF: F                        | SMC2 Time B                                                                       | ase Interrupt F | -lag bit     |                   |                   |             |  |  |  |  |  |

|                            | 1 = Interrupt i                    |                                                                                   |                 |              |                   |                   |             |  |  |  |  |  |

|                            | 0 = Interrupt i                    |                                                                                   |                 |              |                   |                   |             |  |  |  |  |  |

| bit 4                      |                                    | SMC1 Time B                                                                       | ase Interrupt F | -lag bit     |                   |                   |             |  |  |  |  |  |

|                            |                                    | 1 = Interrupt is pending<br>0 = Interrupt is not pending                          |                 |              |                   |                   |             |  |  |  |  |  |

| bit 3                      | •                                  | ted: Read as '                                                                    | 0'              |              |                   |                   |             |  |  |  |  |  |

| bit 2                      |                                    | SMC3 Auto-sł                                                                      |                 | bit          |                   |                   |             |  |  |  |  |  |

|                            |                                    | 1 = Interrupt is pending                                                          |                 |              |                   |                   |             |  |  |  |  |  |

|                            | 0 = Interrupt i                    | s not pending                                                                     |                 |              |                   |                   |             |  |  |  |  |  |

| bit 1                      |                                    | PSMC2 Auto-sh                                                                     | nutdown Flag    | bit          |                   |                   |             |  |  |  |  |  |

|                            |                                    | 1 = Interrupt is pending<br>0 = Interrupt is not pending                          |                 |              |                   |                   |             |  |  |  |  |  |

| bit 0                      |                                    | SMC1 Auto-sh                                                                      | autdown Elog I  | bit          |                   |                   |             |  |  |  |  |  |

|                            | 1 = Interrupt i                    |                                                                                   | lutuowiiiilagi  | DIL          |                   |                   |             |  |  |  |  |  |

|                            | 0 = Interrupt i                    |                                                                                   |                 |              |                   |                   |             |  |  |  |  |  |

| Note:                      | Interrupt flag bits a              |                                                                                   |                 |              |                   |                   |             |  |  |  |  |  |

|                            |                                    | ndition occurs, regardless of the state of corresponding enable bit or the Global |                 |              |                   |                   |             |  |  |  |  |  |

|                            | Enable bit, GIE, c                 |                                                                                   |                 |              |                   |                   |             |  |  |  |  |  |

|                            | User software                      | should ensu                                                                       | ure the         |              |                   |                   |             |  |  |  |  |  |

|                            | appropriate interru                |                                                                                   | are clear       |              |                   |                   |             |  |  |  |  |  |

|                            | prior to enabling a                | n interrupt.                                                                      |                 |              |                   |                   |             |  |  |  |  |  |

## REGISTER 8-9: PIR4: PERIPHERAL INTERRUPT REQUEST REGISTER 4

|        | •••    |       |       |            |       |       |       |        |                     |

|--------|--------|-------|-------|------------|-------|-------|-------|--------|---------------------|

| Name   | Bit 7  | Bit 6 | Bit 5 | Bit 4      | Bit 3 | Bit 2 | Bit 1 | Bit 0  | Register<br>on Page |

| OSCCON | SPLLEN |       | IRCF  | <3:0>      |       | —     | SCS   | <1:0>  | 82                  |

| STATUS | —      | —     | —     | TO         | PD    | Z     | DC    | С      | 27                  |

| WDTCON | —      | _     |       | WDTPS<4:0> |       |       |       | SWDTEN | 110                 |

## TABLE 11-3: SUMMARY OF REGISTERS ASSOCIATED WITH WATCHDOG TIMER

**Legend:** x = unknown, u = unchanged, – = unimplemented locations read as '0'. Shaded cells are not used by Watchdog Timer.

#### TABLE 11-4: SUMMARY OF CONFIGURATION WORD WITH WATCHDOG TIMER

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4  | Bit 11/3 | Bit 10/2        | Bit 9/1 | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|-----------|----------|-----------------|---------|---------|---------------------|

|         | 13:8 | _       | _       | FCMEN    | IESO      | CLKOUTEN | UTEN BOREN<1:0> |         | CPD     | 54                  |

| CONFIG1 | 7:0  | CP      | MCLRE   | PWRTE    | WDTE<1:0> |          | )> FOSC<2:0>    |         |         | 54                  |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by Watchdog Timer.

### 12.4 Modifying Flash Program Memory

When modifying existing data in a program memory row, and data within that row must be preserved, it must first be read and saved in a RAM image. Program memory is modified using the following steps:

- 1. Load the starting address of the row to be modified.

- 2. Read the existing data from the row into a RAM image.

- 3. Modify the RAM image to contain the new data to be written into program memory.

- 4. Load the starting address of the row to be rewritten.

- 5. Erase the program memory row.

- 6. Load the write latches with data from the RAM image.

- 7. Initiate a programming operation.

- 8. Repeat steps 6 and 7 as many times as required to reprogram the erased row.

### 12.5 User ID, Device ID and Configuration Word Access

Instead of accessing program memory or EEPROM data memory, the User ID's, Device ID/Revision ID and Configuration Words can be accessed when CFGS = 1 in the EECON1 register. This is the region that would be pointed to by PC<15> = 1, but not all addresses are accessible. Different access may exist for reads and writes. Refer to Table 12-2.

When read access is initiated on an address outside the parameters listed in Table 12-2, the EEDATH:EEDATL register pair is cleared.

| Address     | Function                    | Read Access | Write Access |

|-------------|-----------------------------|-------------|--------------|

| 8000h-8003h | User IDs                    | Yes         | Yes          |

| 8006h       | Device ID/Revision ID       | Yes         | No           |

| 8007h-8008h | Configuration Words 1 and 2 | Yes         | No           |

#### TABLE 12-2: USER ID, DEVICE ID AND CONFIGURATION WORD ACCESS (CFGS = 1)

#### EXAMPLE 12-6: CONFIGURATION WORD AND DEVICE ID ACCESS

\* This code block will read 1 word of program memory at the memory address:

```

* PROG_ADDR_LO (must be 00h-08h) data will be returned in the variables;

```

\* PROG\_DATA\_HI, PROG\_DATA\_LO

| BANKSEL | EEADRL       | ; | Select correct Bank        |

|---------|--------------|---|----------------------------|

| MOVLW   | PROG_ADDR_LO | ; |                            |

| MOVWF   | EEADRL       | ; | Store LSB of address       |

| CLRF    | EEADRH       | ; | Clear MSB of address       |

|         |              |   |                            |

| BSF     | EECON1,CFGS  | ; | Select Configuration Space |

| BCF     | INTCON,GIE   | ; | Disable interrupts         |

| BSF     | EECON1,RD    | ; | Initiate read              |

| NOP     |              | ; | Executed (See Figure 12-1) |

| NOP     |              | ; | Ignored (See Figure 12-1)  |

| BSF     | INTCON,GIE   | ; | Restore interrupts         |

|         |              |   |                            |

| MOVF    | EEDATL,W     | ; | Get LSB of word            |

| MOVWF   | PROG_DATA_LO | ; | Store in user location     |

| MOVF    | EEDATH,W     | ; | Get MSB of word            |

| MOVWF   | PROG_DATA_HI | ; | Store in user location     |

|         |              |   |                            |

| R/W-1/1                                 | R/W-1/1 | R/W-1/1      | R/W-1/1        | R/W-1/1                            | R/W-1/1          | R/W-1/1     | R/W-1/1 |  |

|-----------------------------------------|---------|--------------|----------------|------------------------------------|------------------|-------------|---------|--|

| WPUC7                                   | WPUC6   | WPUC5        | WPUC4          | WPUC3                              | WPUC2            | WPUC1       | WPUC0   |  |

| bit 7 bit 0                             |         |              |                |                                    |                  |             |         |  |

|                                         |         |              |                |                                    |                  |             |         |  |

| Legend:                                 |         |              |                |                                    |                  |             |         |  |

| R = Readable I                          | oit     | W = Writable | bit            | U = Unimplemented bit, read as '0' |                  |             |         |  |

| u = Bit is unchanged x = Bit is unknown |         |              | -n/n = Value a | at POR and BO                      | R/Value at all c | ther Resets |         |  |

#### REGISTER 13-22: WPUC: WEAK PULL-UP PORTC REGISTER

'0' = Bit is cleared

bit 7-0 WPUC<7:0>: Weak Pull-up Register bits 1 = Pull-up enabled 0 = Pull-up disabled

Note 1: Global WPUEN bit of the OPTION\_REG register must be cleared for individual pull-ups to be enabled.

**2:** The weak pull-up device is automatically disabled if the pin is in configured as an output.

#### REGISTER 13-23: ODCONC: PORTC OPEN DRAIN CONTROL REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| ODC7    | ODC6    | ODC5    | ODC4    | ODC3    | ODC2    | ODC1    | ODC0    |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

'1' = Bit is set

**ODC<7:0>:** PORTC Open Drain Enable bits For RC<7:0> pins, respectively

1 = Port pin operates as open-drain drive (sink current only)

0 = Port pin operates as standard push-pull drive (source and sink current)

#### REGISTER 13-24: SLRCONC: PORTC SLEW RATE CONTROL REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| SLRC7   | SLRC6   | SLRC5   | SLRC4   | SLRC3   | SLRC2   | SLRC1   | SLRC0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **SLRC<7:0>:** PORTC Slew Rate Enable bits

For RC<7:0> pins, respectively

1 = Port pin slew rate is limited

0 = Port pin slews at maximum rate

#### 17.1.5 INTERRUPTS

The ADC module allows for the ability to generate an interrupt upon completion of an Analog-to-Digital conversion. The ADC Interrupt Flag is the ADIF bit in the PIR1 register. The ADC Interrupt Enable is the ADIE bit in the PIE1 register. The ADIF bit must be cleared in software.

| Note 1: | The ADIF bit is set at the completion of |

|---------|------------------------------------------|

|         | every conversion, regardless of whether  |

|         | or not the ADC interrupt is enabled.     |

**2:** The ADC operates during Sleep only when the FRC oscillator is selected.

This interrupt can be generated while the device is operating or while in Sleep. If the device is in Sleep, the interrupt will wake-up the device. Upon waking from Sleep, the next instruction following the SLEEP instruction is always executed. If the user is attempting to wake-up from Sleep and resume in-line code execution, the GIE and PEIE bits of the INTCON register must be disabled. If the GIE and PEIE bits of the INTCON register are enabled, execution will switch to the Interrupt Service Routine.

#### 17.1.6 RESULT FORMATTING

The 10-bit and 12-bit ADC conversion results can be supplied in two formats: 2's complement or sign-magnitude. The ADFM bit of the ADCON1 register controls the output format. Sign magnitude is left justified with the sign bit in the LSb position. Negative numbers are indicated when the sign bit is '1'.

Two's complement is right justified with the sign extended into the Most Significant bits.

Figure 17-3 shows the two output formats. Table 17-2 shows conversion examples.

#### FIGURE 17-3: ADC CONVERSION RESULT FORMAT

|                       | 1                                                                                                       |                                                 |

|-----------------------|---------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| 12-bit sign and       | magnitude                                                                                               |                                                 |

|                       | Bit 11 Bit 10 Bit 9 Bit 8 Bit 7 Bit 6 Bit 5 Bit 4                                                       | Bit 3 Bit 2 Bit 1 Bit 0 '0' '0' '0' Sign        |

| ADFM = 0<br>ADRMD = 0 | bit 7 bit 0                                                                                             | bit 7 bit 0                                     |

|                       |                                                                                                         |                                                 |

|                       |                                                                                                         | Ŷ                                               |

|                       | 12-bit ADC Result                                                                                       | Loaded with '0'                                 |

| 12-bit 2's comp       | bliment                                                                                                 |                                                 |

|                       | Bit 12 Bit 12 Bit 12 Bit 12 Bit 11 Bit 10 Bit 9 Bit 8                                                   | Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 |

| ADFM = 1<br>ADRMD = 0 | bit 7 bit 0                                                                                             | bit 7 bit 0                                     |

|                       |                                                                                                         |                                                 |

|                       | Y                                                                                                       |                                                 |

|                       | Loaded with Sign bits'                                                                                  | 12-bit ADC Result                               |

|                       |                                                                                                         |                                                 |

| 10-bit sign and       | magnitude                                                                                               |                                                 |

|                       | Bit 9         Bit 8         Bit 7         Bit 6         Bit 5         Bit 4         Bit 3         Bit 2 | Bit 1 Bit 0 '0' '0' '0' '0' '0' Sign            |

| <b>ADFM =</b> 0       | bit 7 bit 0                                                                                             | bit 7 bit 0                                     |

| ADRMD = 1             |                                                                                                         |                                                 |

|                       |                                                                                                         |                                                 |

|                       | 10-bit ADC Result                                                                                       | Loaded with '0'                                 |

| 10-bit 2's com        | bliment                                                                                                 |                                                 |

|                       | Bit 10 Bit 10 Bit 10 Bit 10 Bit 10 Bit 10 Bit 9 Bit 8                                                   | Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 |

| ADFM = 1              | bit 7 bit 0                                                                                             | bit 7 bit 0                                     |

| ADRMD = 1             |                                                                                                         |                                                 |

|                       |                                                                                                         |                                                 |

|                       | Loaded with Sign bits'                                                                                  | 10-bit ADC Result                               |

## 17.2 ADC Operation

#### 17.2.1 STARTING A CONVERSION

To enable the ADC module, the ADON bit of the ADCON0 register must be set to a '1'. Setting the GO/DONE bit of the ADCON0 register to a '1' will clear the ADRESH and ADRESL registers and start the Analog-to-Digital conversion.

| Note: | The GO/DONE bit should not be set in the |

|-------|------------------------------------------|

|       | same instruction that turns on the ADC.  |

|       | Refer to Section 17.2.6 "A/D Conversion  |

|       | Procedure".                              |

### 17.2.2 COMPLETION OF A CONVERSION

When the conversion is complete, the ADC module will:

- Clear the GO/DONE bit

- · Set the ADIF Interrupt Flag bit

#### 17.2.3 TERMINATING A CONVERSION

When a conversion is terminated before completion by clearing the GO/DONE bit then the partial results are discarded and the results in the ADRESH and ADRESL registers from the previous conversion remain unchanged.

**Note:** A device Reset forces all registers to their Reset state. Thus, the ADC module is turned off and any pending conversion is terminated.

#### 17.2.4 ADC OPERATION DURING SLEEP

The ADC module can operate during Sleep. This requires the ADC clock source to be set to the FRC option. When the FRC oscillator source is selected, the ADC waits one additional instruction before starting the conversion. This allows the SLEEP instruction to be executed, which can reduce system noise during the conversion. If the ADC interrupt is enabled, the device will wake-up from Sleep when the conversion completes. If the ADC interrupt is disabled, the ADC module is turned off after the conversion completes, although the ADON bit remains set.

When the ADC clock source is something other than FRC, a SLEEP instruction causes the present conversion to be aborted and the ADC module is turned off, although the ADON bit remains set.

### 17.2.5 AUTO-CONVERSION TRIGGER

The Auto-conversion Trigger allows periodic ADC measurements without software intervention. When a rising edge of the selected source occurs, the GO/DONE bit is set by hardware.

The Auto-conversion Trigger source is selected with the TRIGSEL<3:0> bits of the ADCON2 register.

Using the Auto-conversion Trigger does not assure proper ADC timing. It is the user's responsibility to ensure that the ADC timing requirements are met.

Auto-conversion sources are:

- CCP1

- CCP2

- CCP3

- PSMC1<sup>(1)</sup>

- PSMC2<sup>(1)</sup>

Note: The PSMC clock frequency, after the prescaler, must be less than Fosc/4 to ensure that the ADC detects the auto-conversion trigger. This limitation can be overcome by synchronizing a slave PSMC, running at the required slower clock frequency, to the first PSMC and triggering the conversion from the slave PSMC.

PSMC3

## 17.3 Register Definitions: ADC Control

## REGISTER 17-1: ADCON0: ADC CONTROL REGISTER 0

| R/W-0/0                   | R/W-0/0                                   | R/W-0/0                                                                                                          | R/W-0/0                             | R/W-0/0           | R/W-0/0         | R/W-0/0            | R/W-0/0 |

|---------------------------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------|-------------------------------------|-------------------|-----------------|--------------------|---------|

| ADRMD                     |                                           |                                                                                                                  | CHS<4:0>                            |                   |                 | GO/DONE            | ADON    |

| bit 7                     | 1                                         |                                                                                                                  |                                     |                   |                 |                    | bit (   |

| l agandı                  |                                           |                                                                                                                  |                                     |                   |                 |                    |         |

| Legend:<br>D - Doodabla k |                                           | )// - )//ritabla bit                                                                                             |                                     | LI – Unimploma    | ntad hit raad a | a (O)              |         |

| R = Readable b            |                                           | W = Writable bit                                                                                                 |                                     | U = Unimpleme     |                 |                    | -       |

| u = Bit is uncha          | inged                                     | x = Bit is unkno                                                                                                 |                                     | -n/n = Value at   | POR and BOR/    | Value at all other | Resets  |

| '1' = Bit is set          |                                           | '0' = Bit is cleare                                                                                              | ed                                  |                   |                 |                    |         |

| bit 7                     | 1 = ADRESL                                | Result Mode bit<br>and ADRESH pro<br>and ADRESH pro                                                              |                                     |                   |                 |                    |         |

|                           | See Figure 17                             | -3 for details                                                                                                   |                                     |                   |                 |                    |         |

| bit 6-2                   | 11111 = FVF<br>11110 = DAG<br>11101 = Ten | ositive Differential<br>R (Fixed Voltage R<br>C_output <sup>(2)</sup><br>nperature Indicato<br>served. No channe | eference) Buffe<br>r <sup>(4)</sup> |                   |                 |                    |         |

|                           | •                                         |                                                                                                                  |                                     |                   |                 |                    |         |

|                           | 10101 = AN2                               | served. No channe<br>21 <sup>(1)</sup><br>served. No channe                                                      |                                     |                   |                 |                    |         |

|                           | •                                         |                                                                                                                  |                                     |                   |                 |                    |         |

|                           | •                                         |                                                                                                                  |                                     |                   |                 |                    |         |

|                           | 01110 = Res                               | erved. No channe                                                                                                 | l connected.                        |                   |                 |                    |         |

|                           | 01101 = AN                                |                                                                                                                  |                                     |                   |                 |                    |         |

|                           | 01100 = AN                                |                                                                                                                  |                                     |                   |                 |                    |         |

|                           | $01011 = AN^{2}$                          |                                                                                                                  |                                     |                   |                 |                    |         |

|                           | $01010 = AN^{2}$                          |                                                                                                                  |                                     |                   |                 |                    |         |

|                           | 01001 = ANS<br>01000 = ANS                |                                                                                                                  |                                     |                   |                 |                    |         |

|                           | 00111 = AN7                               |                                                                                                                  |                                     |                   |                 |                    |         |

|                           | 00110 = AN6                               | <sub>3</sub> (1)                                                                                                 |                                     |                   |                 |                    |         |

|                           | 00101 = AN                                |                                                                                                                  |                                     |                   |                 |                    |         |

|                           | 00100 = AN4                               |                                                                                                                  |                                     |                   |                 |                    |         |

|                           | 00011 = AN3                               | 3                                                                                                                |                                     |                   |                 |                    |         |

|                           | 00010 = AN2                               | 2                                                                                                                |                                     |                   |                 |                    |         |

|                           | 00001 = AN <sup>2</sup>                   | 1                                                                                                                |                                     |                   |                 |                    |         |

|                           | 00000 = AN0                               | )                                                                                                                |                                     |                   |                 |                    |         |

| bit 1                     | 1 = ADC conv<br>This bit is               | DC Conversion Sta<br>ersion cycle in pro<br>automatically clea<br>ersion completed/                              | ogress. Setting<br>red by hardwar   | e when the ADC    |                 |                    |         |

| bit 0                     | ADON: ADC                                 | •                                                                                                                | 1 3 2 5 6                           |                   |                 |                    |         |

|                           | 1 = ADC is en                             |                                                                                                                  | nes no operatir                     | ig current        |                 |                    |         |

| 2: See<br>3: See          | e <b>Section 15.0</b> "                   | <sup>nly.</sup><br>'Digital-to-Analog<br>'Fixed Voltage Re<br>'Temperature Ind                                   | eference (FVR)                      | " for more inform | ation.          | n.                 |         |

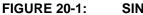

## 20.0 COMPARATOR MODULE

Comparators are used to interface analog circuits to a digital circuit by comparing two analog voltages and providing a digital indication of their relative magnitudes. Comparators are very useful mixed signal building blocks because they provide analog functionality independent of program execution. The analog comparator module includes the following features:

- · Independent comparator control

- Programmable input selection

- · Comparator output is available internally/externally

- Programmable output polarity

- Interrupt-on-change

- · Wake-up from Sleep

- · Programmable Speed/Power optimization

- · PWM shutdown

- Programmable and fixed voltage reference

#### 20.1 Comparator Overview

A single comparator is shown in Figure 20-1 along with the relationship between the analog input levels and the digital output. When the analog voltage at VIN+ is less than the analog voltage at VIN-, the output of the comparator is a digital low level. When the analog voltage at VIN+ is greater than the analog voltage at VIN-, the output of the comparator is a digital high level.

The comparators available for this device are located in Table 20-1.

#### TABLE 20-1: COMPARATOR AVAILABILITY PER DEVICE

| Device            | C1 | C2 | C3 | C4 |

|-------------------|----|----|----|----|

| PIC16(L)F1784/6/7 | ٠  | ٠  | ٠  | •  |

#### SINGLE COMPARATOR

#### 22.6.2 TIMER1 GATE SOURCE SELECTION

Timer1 gate source selections are shown in Table 22-4. Source selection is controlled by the T1GSS bits of the T1GCON register. The polarity for each available source is also selectable. Polarity selection is controlled by the T1GPOL bit of the T1GCON register.

| TABLE 22-4: | TIMER1 GATE SOURCES |

|-------------|---------------------|

|-------------|---------------------|

| T1GSS | Timer1 Gate Source                                                        |

|-------|---------------------------------------------------------------------------|

| 00    | Timer1 Gate Pin                                                           |

| 01    | Overflow of Timer0<br>(TMR0 increments from FFh to 00h)                   |

| 10    | Comparator 1 Output sync_C1OUT<br>(optionally Timer1 synchronized output) |

| 11    | Comparator 2 Output sync_C2OUT<br>(optionally Timer1 synchronized output) |

## 22.6.2.1 T1G Pin Gate Operation

The T1G pin is one source for Timer1 gate control. It can be used to supply an external source to the Timer1 gate circuitry.

#### 22.6.2.2 Timer0 Overflow Gate Operation

When Timer0 increments from FFh to 00h, a low-to-high pulse will automatically be generated and internally supplied to the Timer1 gate circuitry.

### 22.6.2.3 Comparator C1 Gate Operation

The output resulting from a Comparator 1 operation can be selected as a source for Timer1 gate control. The Comparator 1 output (sync\_C1OUT) can be synchronized to the Timer1 clock or left asynchronous. For more information see **Section 20.4.1 "Comparator Output Synchronization"**.

#### 22.6.2.4 Comparator C2 Gate Operation

The output resulting from a Comparator 2 operation can be selected as a source for Timer1 gate control. The Comparator 2 output (sync\_C2OUT) can be synchronized to the Timer1 clock or left asynchronous. For more information see **Section 20.4.1 "Comparator Output Synchronization**".

#### 22.6.3 TIMER1 GATE TOGGLE MODE

When Timer1 Gate Toggle mode is enabled, it is possible to measure the full-cycle length of a Timer1 gate signal, as opposed to the duration of a single level pulse.

The Timer1 gate source is routed through a flip-flop that changes state on every incrementing edge of the signal. See Figure 22-4 for timing details.

Timer1 Gate Toggle mode is enabled by setting the T1GTM bit of the T1GCON register. When the T1GTM bit is cleared, the flip-flop is cleared and held clear. This is necessary in order to control which edge is measured.

| Note: | Enabling Toggle mode at the same time       |

|-------|---------------------------------------------|

|       | as changing the gate polarity may result in |

|       | indeterminate operation.                    |

## 22.6.4 TIMER1 GATE SINGLE-PULSE MODE

When Timer1 Gate Single-Pulse mode is enabled, it is possible to capture a single-pulse gate event. Timer1 Gate Single-Pulse mode is enabled by first setting the T1GSPM bit in the T1GCON register. Next, the T1GGO/DONE bit in the T1GCON register must be set. The Timer1 will be fully enabled on the next incrementing edge. On the next trailing edge of the pulse, the T1GGO/DONE bit will automatically be cleared. No other gate events will be allowed to increment Timer1 until the T1GGO/DONE bit is once again set in software. See Figure 22-5 for timing details.

If the Single-Pulse Gate mode is disabled by clearing the T1GSPM bit in the T1GCON register, the T1GGO/DONE bit should also be cleared.

Enabling the Toggle mode and the Single-Pulse mode simultaneously will permit both sections to work together. This allows the cycle times on the Timer1 gate source to be measured. See Figure 22-6 for timing details.

### 22.6.5 TIMER1 GATE VALUE

When Timer1 Gate Value Status is utilized, it is possible to read the most current level of the gate control value. The value is accessible by reading the T1GVAL bit in the T1GCON register. The T1GVAL bit is valid even when the Timer1 gate is not enabled (TMR1GE bit is cleared).

### 22.6.6 TIMER1 GATE EVENT INTERRUPT

When Timer1 Gate Event Interrupt is enabled, it is possible to generate an interrupt upon the completion of a gate event. When the falling edge of T1GVAL occurs, the TMR1GIF flag bit in the PIR1 register will be set. If the TMR1GIE bit in the PIE1 register is set, then an interrupt will be recognized.

The TMR1GIF flag bit operates even when the Timer1 gate is not enabled (TMR1GE bit is cleared).

## 22.7 Timer1 Interrupt

The Timer1 register pair (TMR1H:TMR1L) increments to FFFFh and rolls over to 0000h. When Timer1 rolls over, the Timer1 interrupt flag bit of the PIR1 register is set. To enable the interrupt on rollover, you must set these bits:

- TMR1ON bit of the T1CON register

- TMR1IE bit of the PIE1 register

- PEIE bit of the INTCON register

- GIE bit of the INTCON register

The interrupt is cleared by clearing the TMR1IF bit in the Interrupt Service Routine.

Note: The TMR1H:TMR1L register pair and the TMR1IF bit should be cleared before enabling interrupts.

## 22.8 Timer1 Operation During Sleep

Timer1 can only operate during Sleep when setup in Asynchronous Counter mode. In this mode, an external crystal or clock source can be used to increment the counter. To set up the timer to wake the device:

- TMR1ON bit of the T1CON register must be set

- TMR1IE bit of the PIE1 register must be set

- · PEIE bit of the INTCON register must be set

- T1SYNC bit of the T1CON register must be set

- TMR1CS bits of the T1CON register must be configured

- T1OSCEN bit of the T1CON register must be configured

The device will wake-up on an overflow and execute the next instructions. If the GIE bit of the INTCON register is set, the device will call the Interrupt Service Routine.

Timer1 oscillator will continue to operate in Sleep regardless of the  $\overline{\text{T1SYNC}}$  bit setting.

### 22.9 CCP Capture/Compare Time Base

The CCP modules use the TMR1H:TMR1L register pair as the time base when operating in Capture or Compare mode.

In Capture mode, the value in the TMR1H:TMR1L register pair is copied into the CCPR1H:CCPR1L register pair on a configured event.

In Compare mode, an event is triggered when the value CCPR1H:CCPR1L register pair matches the value in the TMR1H:TMR1L register pair. This event can be a Auto-conversion Trigger.

For more information, see Section 25.0 "Capture/Compare/PWM Modules".

## 22.10 CCP Auto-Conversion Trigger

When any of the CCP's are configured to trigger a auto-conversion, the trigger will clear the TMR1H:TMR1L register pair. This auto-conversion does not cause a Timer1 interrupt. The CCP module may still be configured to generate a CCP interrupt.

In this mode of operation, the CCPR1H:CCPR1L register pair becomes the period register for Timer1.

Timer1 should be synchronized and Fosc/4 should be selected as the clock source in order to utilize the Auto-conversion Trigger. Asynchronous operation of Timer1 can cause a Auto-conversion Trigger to be missed.

In the event that a write to TMR1H or TMR1L coincides with a Auto-conversion Trigger from the CCP, the write will take precedence.

For more information, see **Section 25.2.4** "Auto-Conversion Trigger".

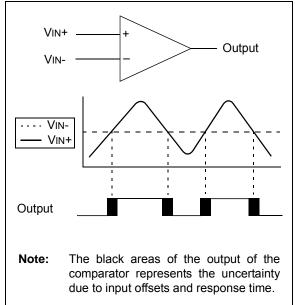

### FIGURE 22-2: TIMER1 INCREMENTING EDGE

| U-0             | U-0                                                                                                                                                  | R/W-0/0                                                                                                                                                                                    | R/W-0/0                               | R/W-0/0                       | R/W-0/0               | R/W-0/0          | R/W-1/1      |  |  |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-------------------------------|-----------------------|------------------|--------------|--|--|

| _               | _                                                                                                                                                    | PxSTRF <sup>(2)</sup>                                                                                                                                                                      | PxSTRE <sup>(2)</sup>                 | PxSTRD <sup>(2)</sup>         | PxSTRC <sup>(2)</sup> | PxSTRB           | PxSTRA       |  |  |

| bit 7           |                                                                                                                                                      | <u> </u>                                                                                                                                                                                   |                                       |                               |                       |                  | bit C        |  |  |

|                 |                                                                                                                                                      |                                                                                                                                                                                            |                                       |                               |                       |                  |              |  |  |

| Legend:         |                                                                                                                                                      |                                                                                                                                                                                            |                                       |                               |                       |                  |              |  |  |

| R = Readabl     | le bit                                                                                                                                               | W = Writable                                                                                                                                                                               | bit                                   | U = Unimpler                  | nented bit, read      | as '0'           |              |  |  |

| u = Bit is und  | changed                                                                                                                                              | x = Bit is unki                                                                                                                                                                            | x = Bit is unknown                    |                               | at POR and BOI        | R/Value at all o | other Resets |  |  |

| '1' = Bit is se | et                                                                                                                                                   | '0' = Bit is cle                                                                                                                                                                           | ared                                  |                               |                       |                  |              |  |  |

|                 |                                                                                                                                                      |                                                                                                                                                                                            |                                       |                               |                       |                  |              |  |  |

| bit 7-6         | Unimpleme                                                                                                                                            | nted: Read as '                                                                                                                                                                            | 0'                                    |                               |                       |                  |              |  |  |

| bit 5           | PxSTRF: PV                                                                                                                                           | VM Steering PS                                                                                                                                                                             | MCxF Output                           | Enable bit <sup>(2)</sup>     |                       |                  |              |  |  |

|                 |                                                                                                                                                      | < <u>3:0&gt; = 0000 (S</u>                                                                                                                                                                 |                                       |                               |                       |                  |              |  |  |

|                 |                                                                                                                                                      | PWM output is                                                                                                                                                                              |                                       |                               |                       |                  |              |  |  |

|                 |                                                                                                                                                      | PWM output is                                                                                                                                                                              |                                       |                               |                       | nactive state    |              |  |  |

|                 |                                                                                                                                                      | $\frac{3:0}{0} = 0.001$ (C                                                                                                                                                                 |                                       |                               |                       |                  |              |  |  |

|                 |                                                                                                                                                      | <ul> <li>1 = Complementary PWM output is active on pin PSMCxF</li> <li>0 = Complementary PWM output is not active on pin PSMCxOUT5. PWM drive is in inactive state</li> </ul>              |                                       |                               |                       |                  |              |  |  |

|                 |                                                                                                                                                      | $\frac{1}{16} = 100 (3-phase Steering):^{(1)}$                                                                                                                                             |                                       |                               |                       |                  |              |  |  |

|                 |                                                                                                                                                      | 1 = PSMCxD and PSMCxE are high. PSMCxA, PMSCxB, PSMCxC and PMSCxF are low.                                                                                                                 |                                       |                               |                       |                  |              |  |  |

|                 |                                                                                                                                                      |                                                                                                                                                                                            |                                       |                               |                       |                  |              |  |  |

| bit 4           | PxSTRE: P\                                                                                                                                           | PxSTRE: PWM Steering PSMCxE Output Enable bit <sup>(2)</sup>                                                                                                                               |                                       |                               |                       |                  |              |  |  |

|                 |                                                                                                                                                      | If PxMODE<3:0> = 000x (single-phase PWM or Complementary PWM):                                                                                                                             |                                       |                               |                       |                  |              |  |  |

|                 |                                                                                                                                                      | 1 = Single PWM output is active on pin PSMCxE                                                                                                                                              |                                       |                               |                       |                  |              |  |  |

|                 | -                                                                                                                                                    | 0 = Single PWM output is not active on pin PSMCxE. PWM drive is in inactive state                                                                                                          |                                       |                               |                       |                  |              |  |  |

|                 | IF PxMODE<3:0> = $1100$ (3-phase Steering): <sup>(1)</sup>                                                                                           |                                                                                                                                                                                            |                                       |                               |                       |                  |              |  |  |

|                 | <ul> <li>1 = PSMCxB and PSMCxE are high. PSMCxA, PMSCxC, PSMCxD and PMSCxF are low.</li> <li>0 = 3-phase output combination is not active</li> </ul> |                                                                                                                                                                                            |                                       |                               |                       |                  |              |  |  |

| bit 3           | <b>PxSTRD</b> : PWM Steering PSMCxD Output Enable bit <sup>(2)</sup>                                                                                 |                                                                                                                                                                                            |                                       |                               |                       |                  |              |  |  |

|                 | If $PxMODE < 3:0> = 0.000$ (Single-phase PWM):                                                                                                       |                                                                                                                                                                                            |                                       |                               |                       |                  |              |  |  |

|                 | 1 = Single PWM output is active on pin PSMCxD                                                                                                        |                                                                                                                                                                                            |                                       |                               |                       |                  |              |  |  |

|                 | 0 = Single PWM output is not active on pin PSMCxD. PWM drive is in inactive state                                                                    |                                                                                                                                                                                            |                                       |                               |                       |                  |              |  |  |

|                 | If PxMODE<3:0> = 0001 (Complementary single-phase PWM):                                                                                              |                                                                                                                                                                                            |                                       |                               |                       |                  |              |  |  |

|                 | 1 = Complementary PWM output is active on pin PSMCxD                                                                                                 |                                                                                                                                                                                            |                                       |                               |                       |                  |              |  |  |

|                 |                                                                                                                                                      | <ul> <li>0 = Complementary PWM output is not active on pin PSMCxD. PWM drive is in inactive state</li> <li><u>IF PxMODE&lt;3:0&gt; = 1100 (3-phase Steering)</u>:<sup>(1)</sup></li> </ul> |                                       |                               |                       |                  |              |  |  |

|                 | $1 = PSMC^{2}$                                                                                                                                       | <pre>&lt;3:0&gt; = 1100 (3 xB and PSMCx()</pre>                                                                                                                                            | <u>-pnase Steeri</u><br>2 are bigh PS | <u>ng):</u> (''<br>MCva PMSC) |                       | d PMSCvE an      | a low        |  |  |