Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PSMC, PWM, WDT                                |

| Number of I/O              | 35                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 14x12b; D/A 1x8b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

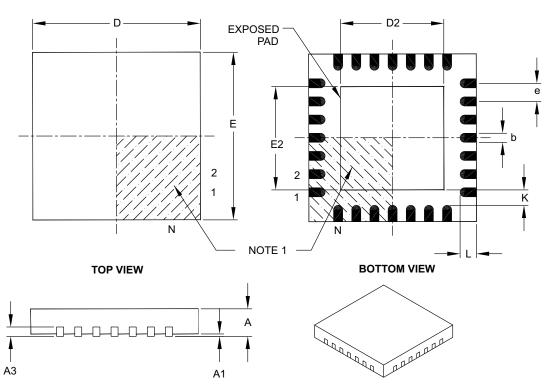

| Package / Case             | 40-UFQFN Exposed Pad                                                       |

| Supplier Device Package    | 40-UQFN (5x5)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1784-i-mv |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABL | E 2:        | 40/44-PIN ALLOCATION TABLE (PIC16(L)F1784/7) |             |            |      |                    |                                      |         |           |                |                                  |                     |                                        |                                          |            |         |                        |

|------|-------------|----------------------------------------------|-------------|------------|------|--------------------|--------------------------------------|---------|-----------|----------------|----------------------------------|---------------------|----------------------------------------|------------------------------------------|------------|---------|------------------------|

| 0]   | 40-Pin PDIP | 40-Pin UQFN                                  | 44-Pin TQFP | 44-Pin QFN | ADC  | Reference          | Comparator                           | Op Amps | 8-bit DAC | Timers         | PSMC                             | ССР                 | EUSART                                 | dssm                                     | Interrupt  | dn-llnd | Basic                  |

| RA0  | 2           | 17                                           | 19          | 19         | AN0  | I                  | C1IN0-<br>C2IN0-<br>C3IN0-<br>C4IN0- | _       | _         |                | I                                | _                   |                                        |                                          | IOC        | Y       | -                      |

| RA1  | 3           | 18                                           | 20          | 20         | AN1  | _                  | C1IN1-<br>C2IN1-<br>C3IN1-<br>C4IN1- | OPA1OUT | _         |                | _                                | _                   | _                                      | _                                        | IOC        | Y       |                        |

| RA2  | 4           | 19                                           | 21          | 21         | AN2  | DAC1VREF-<br>VREF- | C1IN0+<br>C2IN0+<br>C3IN0+<br>C4IN0+ |         | DAC1OUT1  | _              | _                                | -                   | _                                      | _                                        | IOC        | Y       | _                      |

| RA3  | 5           | 20                                           | 22          | 22         | AN3  | DAC1VREF+<br>VREF+ | C1IN1+                               | -       | —         | _              | _                                | —                   | _                                      | _                                        | IOC        | Y       | _                      |

| RA4  | 6           | 21                                           | 23          | 23         | —    | _                  | C10UT                                | OPA1IN+ |           | T0CKI          | _                                | —                   | -                                      | _                                        | IOC        | Y       | _                      |

| RA5  | 7           | 22                                           | 24          | 24         | AN4  |                    | C2OUT                                | OPA1IN- | _         | _              |                                  | —                   | _                                      | SS                                       | IOC        | Y       | _                      |

| RA6  | 14          | 29                                           | 31          | 33         | _    |                    | C2OUT <sup>(1)</sup>                 | _       | _         | _              |                                  | _                   |                                        |                                          | IOC        | Y       | VCAP<br>CLKOUT<br>OSC2 |

| RA7  | 13          | 28                                           | 30          | 32         | _    |                    |                                      | —       | _         |                | PSMC1CLK<br>PSMC2CLK<br>PSMC3CLK | —                   |                                        |                                          | IOC        | Y       | CLKIN<br>OSC1          |

| RB0  | 33          | 8                                            | 8           | 9          | AN12 |                    | C2IN1+                               | —       | —         | _              | PSMC1IN<br>PSMC2IN<br>PSMC3IN    | CCP1 <sup>(1)</sup> |                                        |                                          | INT<br>IOC | Y       | _                      |

| RB1  | 34          | 9                                            | 9           | 10         | AN10 | _                  | C1IN3-<br>C2IN3-<br>C3IN3-<br>C4IN3- | OPA2OUT | _         | _              | _                                | _                   | _                                      | _                                        | IOC        | Y       |                        |

| RB2  | 35          | 10                                           | 10          | 11         | AN8  | —                  | —                                    | OPA2IN- | —         | —              | —                                | —                   | —                                      | —                                        | IOC        | Y       | CLKR                   |

| RB3  | 36          | 11                                           | 11          | 12         | AN9  |                    | C1IN2-<br>C2IN2-<br>C3IN2-           | OPA2IN+ | —         | _              | _                                | CCP2 <sup>(1)</sup> |                                        |                                          | IOC        | Y       | _                      |

| RB4  | 37          | 12                                           | 14          | 14         | AN11 |                    | C3IN1+                               | -       | —         | _              |                                  | —                   |                                        |                                          | IOC        | Y       |                        |

| RB5  | 38          | 13                                           | 15          | 15         | AN13 | _                  | C4IN2-                               | —       | —         | T1G            |                                  | CCP3 <sup>(1)</sup> |                                        | SDO <sup>(1)</sup>                       | IOC        | Y       |                        |

| RB6  | 39          | 14                                           | 16          | 16         | -    | —                  | C4IN1+                               | —       | _         | _              | _                                | —                   | TX <sup>(1)</sup><br>CK <sup>(1)</sup> | SDA <sup>(1)</sup><br>SDI <sup>(1)</sup> | IOC        | Y       | ICSPCLK                |

| RB7  | 40          | 15                                           | 17          | 17         | -    | _                  | _                                    | _       | DAC1OUT2  | _              | _                                | —                   | RX <sup>(1)</sup><br>DT <sup>(1)</sup> | SCL <sup>(1)</sup><br>SCK <sup>(1)</sup> | IOC        | Y       | ICSPDAT                |

| RC0  | 15          | 30                                           | 32          | 34         |      |                    | _                                    | _       | -         | T1CKI<br>T1OSO | PSMC1A                           | —                   | —                                      | —                                        | IOC        | Y       | —                      |

## 40/44-PIN ALLOCATION TABLE (PIC16(L)E1784/7)

Note 1: Alternate pin function selected with the APFCON1 (Register 13-1) and APFCON2 (Register 13-2) registers.

PIC16(L)F1782/3

#### **TABLE 1-2:** PIC16(L)F1784/6/7 PINOUT DESCRIPTION (CONTINUED)

| Name                           | Function | Input<br>Type | Output<br>Type | Description                         |

|--------------------------------|----------|---------------|----------------|-------------------------------------|

| RE2 <sup>(3)</sup> /AN7/PSMC3A | RE2      | TTL/ST        | CMOS           | General purpose I/O.                |

|                                | AN7      | AN            |                | ADC Channel 7 input.                |

|                                | PSMC3A   | —             | CMOS           | PSMC3 output A.                     |

| RE3/MCLR/VPP                   | RE3      | TTL/ST        |                | General purpose input.              |

|                                | MCLR     | ST            |                | Master Clear with internal pull-up. |

|                                | Vpp      | HV            | _              | Programming voltage.                |

| Vdd                            | Vdd      | Power         |                | Positive supply.                    |

| Vss                            | Vss      | Power         | _              | Ground reference.                   |

**Legend:** AN = Analog input or output CMOS = CMOS compatible input or output

OD = Open Drain

TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels I<sup>2</sup>C<sup>™</sup> = Schmitt Trigger input with I<sup>2</sup>C HV = High Voltage XTAL = Crystal levels

Note 1: Pin functions can be assigned to one of two locations via software. See Register 13-1.

2: All pins have interrupt-on-change functionality.

3: PIC16(L)F1784/7 only.

4: PIC16(L)F1786 only.

## 3.2.1.1 STATUS Register

The STATUS register, shown in Register 3-1, contains:

- the arithmetic status of the ALU

- · the Reset status

The STATUS register can be the destination for any instruction, like any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

## 3.3 Register Definitions: Status

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS register as '000u uluu' (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect any Status bits. For other instructions not affecting any Status bits (Refer to **Section 29.0** "Instruction Set Summary").

| Note: | The C and DC bits operate as Borrow a   |   |  |  |  |  |  |  |  |

|-------|-----------------------------------------|---|--|--|--|--|--|--|--|

|       | Digit Borrow out bits, respectively, ir | ۱ |  |  |  |  |  |  |  |

|       | subtraction.                            |   |  |  |  |  |  |  |  |

| REGISTER 3-1: STATUS: S | TATUS REGISTER |

|-------------------------|----------------|

|-------------------------|----------------|

| U-0              | U-0                                                                                                                                                    | U-0                                 | R-1/q         | R-1/q         | R/W-0/u                    | R/W-0/u             | R/W-0/u          |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|---------------|---------------|----------------------------|---------------------|------------------|

| _                | _                                                                                                                                                      | _                                   | TO            | PD            | Z                          | DC <sup>(1)</sup>   | C <sup>(1)</sup> |

| bit 7            |                                                                                                                                                        |                                     |               |               |                            |                     | bit 0            |

| Legend:          |                                                                                                                                                        |                                     |               |               |                            |                     | ]                |

| R = Readable     | bit                                                                                                                                                    | W = Writable I                      | oit           | LI – Unimplor | nented bit, read           | ac '0'              |                  |

| u = Bit is unch  |                                                                                                                                                        | x = Bit is unkn                     |               | •             | at POR and BOI             |                     | thor Posots      |

| '1' = Bit is set | langeu                                                                                                                                                 | 6'' = Bit is clear                  |               |               |                            |                     | ITEL RESELS      |

| I = BILIS SEL    |                                                                                                                                                        |                                     | areu          | q = value dep | pends on conditi           |                     |                  |

| bit 7-5          | Unimplemen                                                                                                                                             | ted: Read as '0                     | )'            |               |                            |                     |                  |

| bit 4            | TO: Time-Out                                                                                                                                           |                                     |               |               |                            |                     |                  |

|                  |                                                                                                                                                        | er-up, CLRWDT                       |               | SLEEP instruc | tion                       |                     |                  |

| bit 3            | PD: Power-D                                                                                                                                            | own bit                             |               |               |                            |                     |                  |

|                  |                                                                                                                                                        | er-up or by the<br>tion of the SLEE |               |               |                            |                     |                  |

| bit 2            | Z: Zero bit                                                                                                                                            |                                     |               |               |                            |                     |                  |

|                  | <ul> <li>1 = The result of an arithmetic or logic operation is zero</li> <li>0 = The result of an arithmetic or logic operation is not zero</li> </ul> |                                     |               |               |                            |                     |                  |

| bit 1            | DC: Digit Car                                                                                                                                          | ry/Digit Borrow                     | bit (ADDWF, A | DDLW, SUBLW,  | SUBWF instruction          | ons) <sup>(1)</sup> |                  |

|                  |                                                                                                                                                        | ut from the 4th                     |               |               | curred                     |                     |                  |

|                  |                                                                                                                                                        | out from the 4th                    |               |               |                            |                     |                  |

| bit 0            | C: Carry/Borr                                                                                                                                          | ow bit <sup>(1)</sup> (ADDW         | F, ADDLW, SUI | BLW, SUBWF in | structions) <sup>(1)</sup> |                     |                  |

- 1 = A carry-out from the Most Significant bit of the result occurred

0 = No carry-out from the Most Significant bit of the result occurred

- **Note 1:** For Borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand.

## 6.6 Register Definitions: Oscillator Control

## REGISTER 6-1: OSCCON: OSCILLATOR CONTROL REGISTER

| R/W-0/0          | R/W-0/0                                                                                                                                                  | R/W-1/1                                                                                                                                                                                           | R/W-1/1                                    | R/W-1/1         | U-0             | R/W-0/0         | R/W-0/0      |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|-----------------|-----------------|-----------------|--------------|

| SPLLEN           |                                                                                                                                                          | IRCF<3:0> SCS<*                                                                                                                                                                                   |                                            |                 |                 | <1:0>           |              |

| bit 7            |                                                                                                                                                          |                                                                                                                                                                                                   |                                            |                 |                 |                 | bit          |

| Legend:          |                                                                                                                                                          |                                                                                                                                                                                                   |                                            |                 |                 |                 |              |

| R = Reada        | ble bit                                                                                                                                                  | W = Writable                                                                                                                                                                                      | bit                                        | U = Unimplem    | ented bit, rea  | id as '0'       |              |

| u = Bit is ur    | nchanged                                                                                                                                                 | x = Bit is unkr                                                                                                                                                                                   | nown                                       | -n/n = Value at | t POR and BO    | OR/Value at all | other Resets |

| '1' = Bit is s   | set                                                                                                                                                      | '0' = Bit is clea                                                                                                                                                                                 | ared                                       |                 |                 |                 |              |

| bit 7            | If PLLEN in<br>SPLLEN bit                                                                                                                                | Configuration W                                                                                                                                                                                   | ′ <u>ords = 1:</u><br>LL is always e       | nabled (subject | to oscillator r | equirements)    |              |

| bit 6-3          | 1111 = 16 $1110 = 8 M$ $1101 = 4 M$ $1100 = 2 M$ $1011 = 1 M$ $1010 = 500$ $1001 = 250$ $1000 = 125$ $0111 = 500$ $0110 = 250$ $0101 = 125$ $0101 = 125$ | /Hz HF<br>/Hz HF<br>) kHz HF <sup>(1)</sup><br>) kHz HF <sup>(1)</sup><br>5 kHz HF <sup>(1)</sup><br>) kHz MF (defau<br>) kHz MF<br>5 kHz MF<br>5 kHz MF<br>25 kHz HF <sup>(1)</sup><br>25 kHz MF | /Hz HF <sup>(2)</sup><br>HF <sup>(2)</sup> |                 |                 |                 |              |

| bit 2<br>bit 1-0 | SCS<1:0>:                                                                                                                                                |                                                                                                                                                                                                   | elect bits                                 |                 |                 |                 |              |

2: 32 MHz when SPLLEN bit is set. Refer to Section 6.2.2.6 "32 MHz Internal Oscillator Frequency Selection".

## 8.6 Register Definitions: Interrupt Control

| R/W-0/0          | R/W-0/0                                                                                                                                                                                                   | R/W-0/0                                                    | R/W-0/0         | R/W-0/0          | R/W-0/0          | R/W-0/0          | R-0/0                |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|-----------------|------------------|------------------|------------------|----------------------|--|

| GIE              | PEIE                                                                                                                                                                                                      | TMR0IE                                                     | INTE            | IOCIE            | TMR0IF           | INTF             | IOCIF <sup>(1)</sup> |  |

| bit 7            |                                                                                                                                                                                                           | ·                                                          |                 |                  |                  |                  | bit 0                |  |

|                  |                                                                                                                                                                                                           |                                                            |                 |                  |                  |                  |                      |  |

| Legend:          |                                                                                                                                                                                                           |                                                            |                 |                  |                  | (0)              |                      |  |

| R = Readable     |                                                                                                                                                                                                           | W = Writable                                               |                 | •                | nented bit, read |                  |                      |  |

| u = Bit is unch  | •                                                                                                                                                                                                         | x = Bit is unkr                                            |                 | -n/n = Value a   | at POR and BO    | R/Value at all o | ther Resets          |  |

| '1' = Bit is set |                                                                                                                                                                                                           | '0' = Bit is clea                                          | ared            |                  |                  |                  |                      |  |

| bit 7            | GIE: Global I                                                                                                                                                                                             | nterrupt Enable                                            | hit             |                  |                  |                  |                      |  |

|                  |                                                                                                                                                                                                           | all active interru                                         |                 |                  |                  |                  |                      |  |

| bit 6            | 1 = Enables                                                                                                                                                                                               | eral Interrupt E<br>all active periph<br>all peripheral ir | eral interrupts | 3                |                  |                  |                      |  |

| bit 5            | 1 = Enables f                                                                                                                                                                                             | er0 Overflow Ir<br>the Timer0 inter<br>the Timer0 inte     | rupt            | e bit            |                  |                  |                      |  |

| bit 4            | 1 = Enables f                                                                                                                                                                                             | tternal Interrupt<br>the INT externa<br>the INT externa    | l interrupt     |                  |                  |                  |                      |  |

| bit 3            | 1 = Enables f                                                                                                                                                                                             | upt-on-Change<br>the interrupt-on<br>the interrupt-or      | -change         |                  |                  |                  |                      |  |

| bit 2            | 1 = TMR0 reg                                                                                                                                                                                              | er0 Overflow Ir<br>gister has overf<br>gister did not ov   | lowed           | it               |                  |                  |                      |  |

| bit 1            | 1 = The INT                                                                                                                                                                                               | ternal Interrupt<br>external interruj<br>external interruj | ot occurred     | ır               |                  |                  |                      |  |

| bit 0            | <b>IOCIF:</b> Interrupt-on-Change Interrupt Flag bit <sup>(1)</sup><br>1 = When at least one of the interrupt-on-change pins changed state<br>0 = None of the interrupt-on-change pins have changed state |                                                            |                 |                  |                  |                  |                      |  |

|                  | e IOCIF Flag bi<br>ve been cleared                                                                                                                                                                        |                                                            | nd cleared wh   | en all the Inter | rupt-on-change   | flags in the IO  | CBF register         |  |

## REGISTER 8-1: INTCON: INTERRUPT CONTROL REGISTER

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Enable bit, GIE, of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

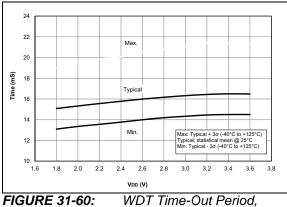

## 11.1 Independent Clock Source

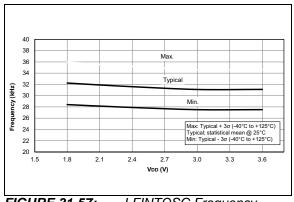

The WDT derives its time base from the 31 kHz LFINTOSC internal oscillator. Time intervals in this chapter are based on a nominal interval of 1 ms. See **Section 30.0 "Electrical Specifications**" for the LFINTOSC tolerances.

## 11.2 WDT Operating Modes

The Watchdog Timer module has four operating modes controlled by the WDTE<1:0> bits in Configuration Words. See Table 11-1.

#### 11.2.1 WDT IS ALWAYS ON

When the WDTE bits of Configuration Words are set to '11', the WDT is always on.

WDT protection is active during Sleep.

#### 11.2.2 WDT IS OFF IN SLEEP

When the WDTE bits of Configuration Words are set to '10', the WDT is on, except in Sleep.

WDT protection is not active during Sleep.

### 11.2.3 WDT CONTROLLED BY SOFTWARE

When the WDTE bits of Configuration Words are set to '01', the WDT is controlled by the SWDTEN bit of the WDTCON register.

WDT protection is unchanged by Sleep. See Table 11-1 for more details.

| WDTE<1:0> | SWDTEN | Device<br>Mode | WDT<br>Mode |  |

|-----------|--------|----------------|-------------|--|

| 11        | х      | Х              | Active      |  |

| 10        |        | Awake          | Active      |  |

| 10        | Х      | Sleep          | Disabled    |  |

| 0.1       | 1 X    |                | Active      |  |

| 01        | 0      | ~              | Disabled    |  |

| 00        | х      | Х              | Disabled    |  |

## TABLE 11-2: WDT CLEARING CONDITIONS

### 11.3 Time-Out Period

The WDTPS bits of the WDTCON register set the time-out period from 1 ms to 256 seconds (nominal). After a Reset, the default time-out period is two seconds.

## 11.4 Clearing the WDT

The WDT is cleared when any of the following conditions occur:

- Any Reset

- CLRWDT instruction is executed

- Device enters Sleep

- · Device wakes up from Sleep

- · Oscillator fail

- · WDT is disabled

- Oscillator Start-up TImer (OST) is running

See Table 11-2 for more information.

## 11.5 Operation During Sleep

When the device enters Sleep, the WDT is cleared. If the WDT is enabled during Sleep, the WDT resumes counting.

When the device exits Sleep, the WDT is cleared again. The WDT remains clear until the OST, if enabled, completes. See **Section 6.0** "Oscillator **Module (with Fail-Safe Clock Monitor)**" for more information on the OST.

When a WDT time-out occurs while the device is in Sleep, no Reset is generated. Instead, the device wakes up and resumes operation. The TO and PD bits in the STATUS register are changed to indicate the event. See **Section 3.0** "**Memory Organization**" and Status Register (Register 3-1) for more information.

| WDT                          |  |  |  |  |  |  |

|------------------------------|--|--|--|--|--|--|

|                              |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |

| Cleared                      |  |  |  |  |  |  |

| Cleared                      |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |

| Cleared until the end of OST |  |  |  |  |  |  |

| Unaffected                   |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |

## 17.2.6 A/D CONVERSION PROCEDURE

This is an example procedure for using the ADC to perform an Analog-to-Digital conversion:

- 1. Configure Port:

- Disable pin output driver (Refer to the TRIS register)

- Configure pin as analog (Refer to the ANSEL register)

- 2. Configure the ADC module:

- Select ADC conversion clock

- Configure voltage reference

- Select ADC input channel

- Turn on ADC module

- 3. Configure ADC interrupt (optional):

- Clear ADC interrupt flag

- Enable ADC interrupt

- Enable peripheral interrupt

- Enable global interrupt<sup>(1)</sup>

- 4. Wait the required acquisition time<sup>(2)</sup>.

- 5. Start conversion by setting the GO/DONE bit.

- 6. Wait for ADC conversion to complete by one of the following:

- Polling the GO/DONE bit

- Waiting for the ADC interrupt (interrupts enabled)

- 7. Read ADC Result.

- 8. Clear the ADC interrupt flag (required if interrupt is enabled).

**Note 1:** The global interrupt can be disabled if the user is attempting to wake-up from Sleep and resume in-line code execution.

2: Refer to Section 17.4 "ADC Acquisition Requirements".

## EXAMPLE 17-1: A/D CONVERSION

;This code block configures the ADC ; for polling, Vdd and Vss references, Frc ;clock and ANO input. ;Conversion start & polling for completion ; are included. BANKSEL ADCON1 ; B'11110000' ;2's complement, Frc MOVLW ;clock MOVWF ADCON1 ;Vdd and Vss Vref B'00001111' ;set negative input MOVLW MOVWF ADCON2 ;to negative ;reference BANKSEL TRISA BSF TRISA,0 ;Set RA0 to input BANKSEL ANSEL ANSEL.0 BSF ;Set RA0 to analog BANKSEL ADCON0 ; B'00000001' ;Select channel AN0 MOVLW MOVWF ADCON0 ;Turn ADC On CALL SampleTime ; Acquisiton delay BSF ADCON0, ADGO ;Start conversion ADCON0, ADGO ; Is conversion done? BTFSC GOTO \$-1 ;No, test again BANKSEL ADRESH ; MOVF ADRESH,W ;Read upper 2 bits MOVWF RESULTHI ;store in GPR space

## **19.6 Register Definitions: DAC Control**

## REGISTER 19-1: DAC1CON0: VOLTAGE REFERENCE CONTROL REGISTER 0

|                  |                                                                                                                                      |                                                            | -              |                |                     | -               |            |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|----------------|----------------|---------------------|-----------------|------------|

| R/W-0/0          | U-0                                                                                                                                  | R/W-0/0                                                    | R/W-0/0        | R/W-0/0        | R/W-0/0             | U-0             | R/W-0/0    |

| DAC1EN           | _                                                                                                                                    | DAC10E1                                                    | DAC10E2        | DAC1F          | PSS<1:0>            | _               | DAC1NSS    |

| bit 7            | ·                                                                                                                                    |                                                            |                |                |                     |                 | bit C      |

|                  |                                                                                                                                      |                                                            |                |                |                     |                 |            |

| Legend:          |                                                                                                                                      |                                                            |                |                |                     |                 |            |

| R = Readable     | bit                                                                                                                                  | W = Writable I                                             | bit            | U = Unimplem   | nented bit, read as | s '0'           |            |

| u = Bit is unch  | anged                                                                                                                                | x = Bit is unkn                                            | own            | -n/n = Value a | t POR and BOR/      | Value at all of | her Resets |

| '1' = Bit is set |                                                                                                                                      | '0' = Bit is clea                                          | ared           |                |                     |                 |            |

| bit 7            | <b>DAC1EN:</b> DA(<br>1 = DAC1 is e<br>0 = DAC1 is e                                                                                 | enabled                                                    |                |                |                     |                 |            |

| bit 6            | Unimplement                                                                                                                          | ed: Read as '0                                             |                |                |                     |                 |            |

| bit 5            | 1 = DAC1 vol                                                                                                                         | AC1 Voltage Ou<br>Itage level is als<br>Itage level is dis | o an output on | the DAC1OUT    | •                   |                 |            |

| bit 4            | 1 = DAC1 vol                                                                                                                         | AC1 Voltage Ou<br>Itage level is als<br>Itage level is dis | o an output on | the DAC1OUT    | •                   |                 |            |

| bit 3-2          | DAC1PSS<1:0>: DAC1 Positive Source Select bits<br>11 = Reserved, do not use<br>10 = FVR Buffer2 output<br>01 = VREF+ pin<br>00 = VDD |                                                            |                |                |                     |                 |            |

| bit 1            | Unimplement                                                                                                                          | ed: Read as '0'                                            |                |                |                     |                 |            |

| bit 0            | <b>DAC1NSS:</b> D/<br>1 = VREF-pin<br>0 = VSS                                                                                        | AC1 Negative S                                             | ource Select b | its            |                     |                 |            |

|                  |                                                                                                                                      |                                                            |                |                |                     |                 |            |

### REGISTER 19-2: DAC1CON1: VOLTAGE REFERENCE CONTROL REGISTER 1

| R/W-0/0          | R/W-0/0 | R/W-0/0          | R/W-0/0 | R/W-0/0      | R/W-0/0           | R/W-0/0 | R/W-0/0 |

|------------------|---------|------------------|---------|--------------|-------------------|---------|---------|

|                  |         |                  | DAC1    | R<7:0>       |                   |         |         |

| bit 7            |         |                  |         |              |                   |         | bit 0   |

|                  |         |                  |         |              |                   |         |         |

| Legend:          |         |                  |         |              |                   |         |         |

| R = Readable bit |         | W = Writable bit |         | U = Unimplem | ented bit, read a | is '0'  |         |

| bit 7-0 | DAC1R<7:0>: DAC1 Voltage Output Select bits |

|---------|---------------------------------------------|

|         | Bron voltage output oclost bits             |

x = Bit is unknown

'0' = Bit is cleared

#### TABLE 19-1: SUMMARY OF REGISTERS ASSOCIATED WITH THE DAC MODULE

| Name     | Bit 7  | Bit 6      | Bit 5   | Bit 4   | Bit 3  | Bit 2   | Bit 1 | Bit 0   | Register<br>on page |

|----------|--------|------------|---------|---------|--------|---------|-------|---------|---------------------|

| FVRCON   | FVREN  | FVRRDY     | TSEN    | TSRNG   | CDAFV  | ′R<1:0> | ADFVF | R<1:0>  | 162                 |

| DAC1CON0 | DAC1EN | _          | DAC10E1 | DAC10E2 | DAC1PS | SS<1:0> | _     | DAC1NSS | 186                 |

| DAC1CON1 |        | DAC1R<7:0> |         |         |        |         |       | 186     |                     |

**Legend:** — = Unimplemented location, read as '0'. Shaded cells are not used with the DAC module.

u = Bit is unchanged

'1' = Bit is set

-n/n = Value at POR and BOR/Value at all other Resets

## 21.1.3 SOFTWARE PROGRAMMABLE PRESCALER

A software programmable prescaler is available for exclusive use with Timer0. The prescaler is enabled by clearing the PSA bit of the OPTION\_REG register.

| Note: | The Watchdog Timer (WDT) uses its own |

|-------|---------------------------------------|

|       | independent prescaler.                |

There are eight prescaler options for the Timer0 module ranging from 1:2 to 1:256. The prescale values are selectable via the PS<2:0> bits of the OPTION\_REG register. In order to have a 1:1 prescaler value for the Timer0 module, the prescaler must be disabled by setting the PSA bit of the OPTION\_REG register.

The prescaler is not readable or writable. All instructions writing to the TMR0 register will clear the prescaler.

## 21.1.4 TIMER0 INTERRUPT

Timer0 will generate an interrupt when the TMR0 register overflows from FFh to 00h. The TMR0IF interrupt flag bit of the INTCON register is set every time the TMR0 register overflows, regardless of whether or not the Timer0 interrupt is enabled. The TMR0IF bit can only be cleared in software. The Timer0 interrupt enable is the TMR0IE bit of the INTCON register.

| Note: | The Timer0 interrupt cannot wake the    |

|-------|-----------------------------------------|

|       | processor from Sleep since the timer is |

|       | frozen during Sleep.                    |

## 21.1.5 8-BIT COUNTER MODE SYNCHRONIZATION

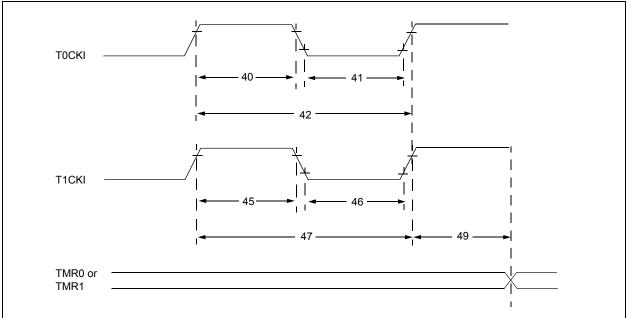

When in 8-Bit Counter mode, the incrementing edge on the T0CKI pin must be synchronized to the instruction clock. Synchronization can be accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the instruction clock. The high and low periods of the external clocking source must meet the timing requirements as shown in **Section 30.0 "Electrical Specifications"**.

## 21.1.6 OPERATION DURING SLEEP

Timer0 cannot operate while the processor is in Sleep mode. The contents of the TMR0 register will remain unchanged while the processor is in Sleep mode.

## 24.2.1.4 16-bit Duty Cycle Register

The PSMCxDC Duty Cycle register is used to determine a synchronous falling edge event referenced to the 16-bit PSMCxTMR digital counter. A match between the PSMCxTMR and PSMCxDC register values will generate a falling edge event.

The match will generate a duty cycle match interrupt, thereby setting the PxTDCIF bit of the PSMC Time Base Interrupt Control (PSMCxINT) register (Register 24-33).

The 16-bit duty cycle value is accessible to software as two 8-bit registers:

- PSMC Duty Cycle Count Low Byte (PSMCxDCL) register (Register 24-22)

- PSMC Duty Cycle Count High Byte (PSMCxDCH) register (Register 24-23)

The 16-bit duty cycle value is double-buffered before it is presented to the 16-bit time base for comparison. The buffered registers are updated on the first period event Reset after the PSMCxLD bit of the PSMCxCON register is set.

When the period, phase, and duty cycle are all determined from the time base, the effective PWM duty cycle can be expressed as shown in Equation 24-2.

## EQUATION 24-2: PWM DUTY CYCLE

| DUTYCYCLE = | PSMCxDC[15:0] - PSMCxPH[15:0] |

|-------------|-------------------------------|

| DUITCICLE - | (PSMCxPR[15:0] + 1)           |

## 24.2.2 0% DUTY CYCLE OPERATION USING TIME BASE

To configure the PWM for 0% duty cycle set PSMCxDC<15:0> = PSMCxPH<15:0>. This will trigger a falling edge event simultaneous with the rising edge event and prevent the PWM from being asserted.

## 24.2.3 100% DUTY CYCLE OPERATION USING TIME BASE

To configure the PWM for 100% duty cycle set PSMCxDC<15:0> > PSMCxPR<15:0>.

This will prevent a falling edge event from occurring as the PSMCxDC<15:0> value and the time base value PSMCxTMR<15:0> will never be equal.

### 24.2.4 TIME BASE INTERRUPT GENERATION

The Time Base section can generate four unique interrupts:

- Time Base Counter Overflow Interrupt

- Time Base Phase Register Match Interrupt

- Time Base Duty Cycle Register Match Interrupt

- Time Base Period Register Match Interrupt

Each interrupt has an interrupt flag bit and an interrupt enable bit. The interrupt flag bit is set anytime a given event occurs, regardless of the status of the enable bit.

Time base interrupt enables and flags are located in the PSMC Time Base Interrupt Control (PSMCxINT) register (Register 24-33).

PSMC time base interrupts also require that the PSMCxTIE bit in the PIE4 register and the PEIE and GIE bits in the INTCON register be set in order to generate an interrupt. The PSMCxTIF interrupt flag in the PIR4 register will only be set by a time base interrupt when one or more of the enable bits in the PSMCxINT register is set.

The interrupt flag bits need to be cleared in software. However, all PMSCx time base interrupt flags, except PSMCxTIF, are cleared when the PSMCxEN bit is cleared.

Interrupt bits that are set by software will generate an interrupt provided that the corresponding interrupt is enabled.

**Note:** Interrupt flags in both the PIE4 and PSMCxINT registers must be cleared to clear the interrupt. The PSMCxINT flags must be cleared first.

## 24.2.5 PSMC TIME BASE CLOCK SOURCES

There are three clock sources available to the module:

- Internal 64 MHz clock

- Fosc system clock

- External clock input pin

The clock source is selected with the PxCSRC<1:0> bits of the PSMCx Clock Control (PSMCxCLK) register (Register 24-6).

When the Internal 64 MHz clock is selected as the source, the HFINTOSC continues to operate and clock the PSMC circuitry in Sleep. However, the system clock to other peripherals and the CPU is suppressed.

Note: When the 64 MHz clock is selected, the clock continues to operate in Sleep, even when the PSMC is disabled (PSMCxEN = 0). Select a clock other than the 64 MHz clock to minimize power consumption when the PSMC is not enabled.

The Internal 64 MHz clock utilizes the system clock 4x PLL. When the system clock source is external and the PSMC is using the Internal 64 MHz clock, the 4x PLL should not be used for the system clock.

## REGISTER 24-31: PSMCxSTR0: PSMC STEERING CONTROL REGISTER 0

| bit 1 | PxSTRB: PWM Steering PSMCxB Output Enable bit                                                                                                              |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | If PxMODE<3:0> = 0000 (Single-phase PWM):                                                                                                                  |

|       | <ol> <li>Single PWM output is active on pin PSMCxOUT1</li> <li>Single PWM output is not active on pin PSMCxOUT1. PWM drive is in inactive state</li> </ol> |

|       |                                                                                                                                                            |

|       | <u>If PxMODE&lt;3:0&gt; = 0001 (Complementary Single-phase PWM):</u><br>1 = Complementary PWM output is active on pin PSMCxB                               |

|       | 0 = Complementary PWM output is not active on pin PSMCxB. PWM drive is in inactive state                                                                   |

|       | IF PxMODE<3:0> = 1100 (3-phase Steering): <sup>(1)</sup>                                                                                                   |

|       | 1 = PSMCxA and PSMCxF are high. PSMCxB, PMSCxC, PSMCxD and PMSCxE are low.                                                                                 |

|       | <ul><li>0 = 3-phase output combination is not active</li></ul>                                                                                             |

| bit 0 | PxSTRA: PWM Steering PSMCxA Output Enable bit                                                                                                              |

|       | <u>If PxMODE&lt;3:0&gt; = 000x (Single-phase PWM or Complementary PWM):</u>                                                                                |

|       | <ol> <li>Single PWM output is active on pin PSMCxA</li> </ol>                                                                                              |

|       | 0 = Single PWM output is not active on pin PSMCxA. PWM drive is in inactive state                                                                          |

|       | IF PxMODE<3:0> = <u>1100</u> (3-phase Steering): <sup>(1)</sup>                                                                                            |

|       | 1 = PSMCxA and PSMCxD are high. PSMCxB, PMSCxC, PSMCxE and PMSCxF are low.                                                                                 |

|       | <ul><li>0 = 3-phase output combination is not active</li></ul>                                                                                             |

- **Note 1:** In 3-phase Steering mode, only one PSTRx bit should be set at a time. If more than one is set, then the lowest bit number steering combination has precedence.

- **2:** These bits are not implemented on PSMC2.

### 26.2.4 SPI SLAVE MODE

In Slave mode, the data is transmitted and received as external clock pulses appear on SCK. When the last bit is latched, the SSP1IF interrupt flag bit is set.

Before enabling the module in SPI Slave mode, the clock line must match the proper Idle state. The clock line can be observed by reading the SCK pin. The Idle state is determined by the CKP bit of the SSPCON1 register.

While in Slave mode, the external clock is supplied by the external clock source on the SCK pin. This external clock must meet the minimum high and low times as specified in the electrical specifications.

While in Sleep mode, the slave can transmit/receive data. The shift register is clocked from the SCK pin input and when a byte is received, the device will generate an interrupt. If enabled, the device will wake-up from Sleep.

### 26.2.4.1 Daisy-Chain Configuration

The SPI bus can sometimes be connected in a daisy-chain configuration. The first slave output is connected to the second slave input, the second slave output is connected to the third slave input, and so on. The final slave output is connected to the master input. Each slave sends out, during a second group of clock pulses, an exact copy of what was received during the first group of clock pulses. The whole chain acts as one large communication shift register. The daisy-chain feature only requires a single Slave Select line from the master device.

Figure 26-7 shows the block diagram of a typical daisy-chain connection when operating in SPI mode.

In a daisy-chain configuration, only the most recent byte on the bus is required by the slave. Setting the BOEN bit of the SSPCON3 register will enable writes to the SSPBUF register, even if the previous byte has not been read. This allows the software to ignore data that may not apply to it.

## 26.2.5 SLAVE SELECT SYNCHRONIZATION

The Slave Select can also be used to synchronize communication. The Slave Select line is held high until the master device is ready to communicate. When the Slave Select line is pulled low, the slave knows that a new transmission is starting.

If the slave fails to receive the communication properly, it will be reset at the end of the transmission, when the Slave Select line returns to a high state. The slave is then ready to receive a new transmission when the Slave Select line is pulled low again. If the Slave Select line is not used, there is a risk that the slave will eventually become out of sync with the master. If the slave misses a bit, it will always be one bit off in future transmissions. Use of the Slave Select line allows the slave and master to align themselves at the beginning of each transmission.

The  $\overline{SS}$  pin allows a Synchronous Slave mode. The SPI must be in Slave mode with  $\overline{SS}$  pin control enabled (SSPCON1<3:0> = 0100).

When the  $\overline{SS}$  pin is low, transmission and reception are enabled and the SDO pin is driven.

When the  $\overline{SS}$  pin goes high, the SDO pin is no longer driven, even if in the middle of a transmitted byte and becomes a floating output. External pull-up/pull-down resistors may be desirable depending on the application.

| Note 1: | When the SPI is in Slave mode with $\overline{SS}$ pin<br>control enabled (SSPCON1<3:0> =<br>0100), the SPI module will reset if the $\overline{SS}$<br>pin is set to VDD. |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2:      | When the SPI is used in Slave mode with CKE set; the user must enable $\overline{SS}$ pin control.                                                                         |

| 3:      | While operated in SPI Slave mode the SMP bit of the SSPSTAT register must remain clear.                                                                                    |

When the SPI module resets, the bit counter is forced to '0'. This can be done by either forcing the  $\overline{SS}$  pin to a high level or clearing the SSPEN bit.

## REGISTER 26-5: SSPMSK: SSP MASK REGISTER

| R/W-1/1                       | R/W-1/1                                                                                                                                                                                                                                                                                                                                                                                                              | R/W-1/1            | R/W-1/1 | R/W-1/1                                               | R/W-1/1 | R/W-1/1 | R/W-1/1 |  |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|---------|-------------------------------------------------------|---------|---------|---------|--|

|                               |                                                                                                                                                                                                                                                                                                                                                                                                                      |                    | MSK     | <7:0>                                                 |         |         |         |  |

| bit 7                         |                                                                                                                                                                                                                                                                                                                                                                                                                      |                    |         |                                                       |         |         | bit 0   |  |

|                               |                                                                                                                                                                                                                                                                                                                                                                                                                      |                    |         |                                                       |         |         |         |  |

| Legend:                       |                                                                                                                                                                                                                                                                                                                                                                                                                      |                    |         |                                                       |         |         |         |  |

| R = Readable bit              |                                                                                                                                                                                                                                                                                                                                                                                                                      | W = Writable       | bit     | U = Unimplemented bit, read as '0'                    |         |         |         |  |

| u = Bit is unchanged          |                                                                                                                                                                                                                                                                                                                                                                                                                      | x = Bit is unknown |         | -n/n = Value at POR and BOR/Value at all other Resets |         |         |         |  |

| '1' = Bit is set '0' = Bit is |                                                                                                                                                                                                                                                                                                                                                                                                                      | '0' = Bit is cle   | ared    |                                                       |         |         |         |  |

| bit 7-1                       | MSK<7:1>:                                                                                                                                                                                                                                                                                                                                                                                                            | Mask bits          |         |                                                       |         |         |         |  |

|                               | 1 = The received address bit n is compared to SSPADD <n> to detect <math>I^2C</math> address match<br/>0 = The received address bit n is not used to detect <math>I^2C</math> address match</n>                                                                                                                                                                                                                      |                    |         |                                                       |         |         | tch     |  |

| bit 0                         | <b>MSK&lt;0&gt;:</b> Mask bit for I <sup>2</sup> C Slave mode, 10-bit Address<br>I <sup>2</sup> C Slave mode, 10-bit address (SSPM<3:0> = 0111 or 1111):<br>1 = The received address bit 0 is compared to SSPADD<0> to detect I <sup>2</sup> C address match<br>0 = The received address bit 0 is not used to detect I <sup>2</sup> C address match<br>I <sup>2</sup> C Slave mode. Z bit address the bit is ignored |                    |         |                                                       |         |         |         |  |

I<sup>2</sup>C Slave mode, 7-bit address, the bit is ignored

'0' = Bit is cleared

## REGISTER 26-6: SSPADD: MSSP ADDRESS AND BAUD RATE REGISTER (I<sup>2</sup>C MODE)

| R/W-0/0                                 | R/W-0/0   | R/W-0/0        | R/W-0/0   | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0      |

|-----------------------------------------|-----------|----------------|-----------|----------------|------------------|------------------|--------------|

| 10,00-070                               | 10/00-0/0 | 10,00-0/0      | 10/07-0/0 | 10,00-0/0      | 10,00-070        | 10,00-0/0        | 10/0/0/0     |

|                                         |           |                | ADD       | <7:0>          |                  |                  |              |

| bit 7                                   |           |                |           |                |                  |                  | bit 0        |

|                                         |           |                |           |                |                  |                  |              |

| Legend:                                 |           |                |           |                |                  |                  |              |

| R = Readable                            | bit       | W = Writable I | bit       | U = Unimpler   | nented bit, read | d as '0'         |              |

| u = Bit is unchanged x = Bit is unknown |           |                | iown      | -n/n = Value a | at POR and BO    | R/Value at all o | other Resets |

| Master | mode: |  |

|--------|-------|--|

1' = Bit is set

| bit 7-0 | ADD<7:0>: Baud Rate Clock Divider bits          |

|---------|-------------------------------------------------|

|         | SCL pin clock period = ((ADD<7:0> + 1) *4)/Fosc |

## <u>10-Bit Slave mode — Most Significant Address Byte:</u>

- bit 7-3 **Not used:** Unused for Most Significant Address byte. Bit state of this register is a "don't care". Bit pattern sent by master is fixed by I<sup>2</sup>C specification and must be equal to '11110'. However, those bits are compared by hardware and are not affected by the value in this register.

- bit 2-1 ADD<2:1>: Two Most Significant bits of 10-bit address

- bit 0 Not used: Unused in this mode. Bit state is a "don't care".

### <u>10-Bit Slave mode — Least Significant Address Byte:</u>

bit 7-0 ADD<7:0>: Eight Least Significant bits of 10-bit address

### 7-Bit Slave mode:

bit 0 Not used: Unused in this mode. Bit state is a "don't care".

| R/W-0/0         | R/W-0/0                                                                                                                                                      | R/W-0/0                                                                                                              | R/W-0/0         | R/W-0/0     | R-0/0            | R-0/0           | R-0/0 |  |  |  |  |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-----------------|-------------|------------------|-----------------|-------|--|--|--|--|

| SPEN            | RX9                                                                                                                                                          | SREN                                                                                                                 | CREN            | ADDEN       | FERR             | OERR            | RX9D  |  |  |  |  |

| bit 7           | •                                                                                                                                                            | -                                                                                                                    |                 |             |                  | -               | bit 0 |  |  |  |  |

|                 |                                                                                                                                                              |                                                                                                                      |                 |             |                  |                 |       |  |  |  |  |

| Legend:         |                                                                                                                                                              |                                                                                                                      |                 |             |                  |                 |       |  |  |  |  |

| R = Readabl     | e bit                                                                                                                                                        | W = Writable                                                                                                         | bit             | U = Unimple | mented bit, read | l as '0'        |       |  |  |  |  |

| u = Bit is und  | Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Re                                                                        |                                                                                                                      |                 |             |                  |                 |       |  |  |  |  |

| '1' = Bit is se | t                                                                                                                                                            | '0' = Bit is cle                                                                                                     | ared            |             |                  |                 |       |  |  |  |  |

| hit 7           | CDEN: Corio                                                                                                                                                  | l Dort Enchla h                                                                                                      |                 |             |                  |                 |       |  |  |  |  |

| bit 7           |                                                                                                                                                              | <b>SPEN:</b> Serial Port Enable bit<br>1 = Serial port enabled (configures RX/DT and TX/CK pins as serial port pins) |                 |             |                  |                 |       |  |  |  |  |

|                 |                                                                                                                                                              | ort disabled (he                                                                                                     |                 |             |                  |                 |       |  |  |  |  |

| bit 6           |                                                                                                                                                              | eceive Enable l                                                                                                      | -               |             |                  |                 |       |  |  |  |  |

|                 |                                                                                                                                                              | 9-bit reception<br>8-bit reception                                                                                   |                 |             |                  |                 |       |  |  |  |  |

| bit 5           |                                                                                                                                                              | •                                                                                                                    | ole bit         |             |                  |                 |       |  |  |  |  |

|                 | -                                                                                                                                                            | SREN: Single Receive Enable bit<br>Asynchronous mode:                                                                |                 |             |                  |                 |       |  |  |  |  |

|                 | Don't care                                                                                                                                                   | -                                                                                                                    |                 |             |                  |                 |       |  |  |  |  |

|                 | Synchronous mode – Master:                                                                                                                                   |                                                                                                                      |                 |             |                  |                 |       |  |  |  |  |

|                 | 1 = Enables single receive                                                                                                                                   |                                                                                                                      |                 |             |                  |                 |       |  |  |  |  |

|                 | <ul> <li>Disables single receive</li> <li>This bit is cleared after reception is complete.</li> </ul>                                                        |                                                                                                                      |                 |             |                  |                 |       |  |  |  |  |

|                 | Synchronous mode – Slave                                                                                                                                     |                                                                                                                      |                 |             |                  |                 |       |  |  |  |  |