Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PSMC, PWM, WDT                                 |

| Number of I/O              | 35                                                                          |

| Program Memory Size        | 7KB (4K x 14)                                                               |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 512 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 14x12b; D/A 1x8b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-VQFN Exposed Pad                                                         |

| Supplier Device Package    | 44-QFN (8x8)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1784t-i-ml |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC16(L)F1784/6/7

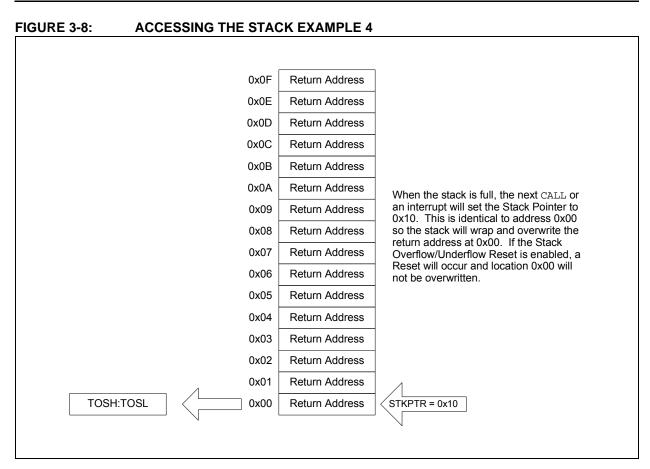

# 3.5.2 OVERFLOW/UNDERFLOW RESET

If the STVREN bit in Configuration Words is programmed to '1', the device will be reset if the stack is PUSHed beyond the sixteenth level or POPed beyond the first level, setting the appropriate bits (STKOVF or STKUNF, respectively) in the PCON register.

# 3.6 Indirect Addressing

The INDFn registers are not physical registers. Any instruction that accesses an INDFn register actually accesses the register at the address specified by the File Select Registers (FSR). If the FSRn address specifies one of the two INDFn registers, the read will return '0' and the write will not occur (though Status bits may be affected). The FSRn register value is created by the pair FSRnH and FSRnL.

The FSR registers form a 16-bit address that allows an addressing space with 65536 locations. These locations are divided into three memory regions:

- · Traditional Data Memory

- Linear Data Memory

- Program Flash Memory

### 6.2.2.5 Internal Oscillator Frequency Selection

The system clock speed can be selected via software using the Internal Oscillator Frequency Select bits IRCF<3:0> of the OSCCON register.

The output of the 16 MHz HFINTOSC, 500 kHz MFINTOSC, and 31 kHz LFINTOSC connects to a postscaler and multiplexer (see Figure 6-1). The Internal Oscillator Frequency Select bits IRCF<3:0> of the OSCCON register select the frequency output of the internal oscillators. One of the following frequencies can be selected via software:

- 32 MHz (requires 4x PLL)

- 16 MHz

- 8 MHz

- 4 MHz

- 2 MHz

- 1 MHz

- 500 kHz (default after Reset)

- 250 kHz

- 125 kHz

- 62.5 kHz

- 31.25 kHz

- 31 kHz (LFINTOSC)

- Note: Following any Reset, the IRCF<3:0> bits of the OSCCON register are set to '0111' and the frequency selection is set to 500 kHz. The user can modify the IRCF bits to select a different frequency.

The IRCF<3:0> bits of the OSCCON register allow duplicate selections for some frequencies. These duplicate choices can offer system design trade-offs. Lower power consumption can be obtained when changing oscillator sources for a given frequency. Faster transition times can be obtained between frequency changes that use the same oscillator source.

# 6.2.2.6 32 MHz Internal Oscillator Frequency Selection

The Internal Oscillator Block can be used with the 4x PLL associated with the External Oscillator Block to produce a 32 MHz internal system clock source. The following settings are required to use the 32 MHz internal clock source:

- The FOSC bits in Configuration Words must be set to use the INTOSC source as the device system clock (FOSC<2:0> = 100).

- The SCS bits in the OSCCON register must be cleared to use the clock determined by FOSC<2:0> in Configuration Words (SCS<1:0> = 00).

- The IRCF bits in the OSCCON register must be set to the 8 MHz or 16 MHz HFINTOSC set to use (IRCF<3:0> = 111x).

- The SPLLEN bit in the OSCCON register must be set to enable the 4x PLL, or the PLLEN bit of the Configuration Words must be programmed to a '1'.

- **Note:** When using the PLLEN bit of the Configuration Words, the 4x PLL cannot be disabled by software and the SPLLEN option will not be available.

The 4x PLL is not available for use with the internal oscillator when the SCS bits of the OSCCON register are set to '1x'. The SCS bits must be set to '00' to use the 4x PLL with the internal oscillator.

### 6.2.2.7 Internal Oscillator Clock Switch Timing

When switching between the HFINTOSC, MFINTOSC and the LFINTOSC, the new oscillator may already be shut down to save power (see Figure 6-7). If this is the case, there is a delay after the IRCF<3:0> bits of the OSCCON register are modified before the frequency selection takes place. The OSCSTAT register will reflect the current active status of the HFINTOSC, MFINTOSC and LFINTOSC oscillators. The sequence of a frequency selection is as follows:

- 1. IRCF<3:0> bits of the OSCCON register are modified.

- 2. If the new clock is shut down, a clock start-up delay is started.

- 3. Clock switch circuitry waits for a falling edge of the current clock.

- 4. The current clock is held low and the clock switch circuitry waits for a rising edge in the new clock.

- 5. The new clock is now active.

- 6. The OSCSTAT register is updated as required.

- 7. Clock switch is complete.

See Figure 6-7 for more details.

If the internal oscillator speed is switched between two clocks of the same source, there is no start-up delay before the new frequency is selected. Clock switching time delays are shown in Table 6-1.

Start-up delay specifications are located in the oscillator tables of **Section 30.0** "**Electrical Specifications**".

# 8.1 Operation

Interrupts are disabled upon any device Reset. They are enabled by setting the following bits:

- · GIE bit of the INTCON register

- Interrupt Enable bit(s) for the specific interrupt event(s)

- PEIE bit of the INTCON register (if the Interrupt Enable bit of the interrupt event is contained in the PIE1 or PIE2 registers)

The INTCON, PIR1 and PIR2 registers record individual interrupts via interrupt flag bits. Interrupt flag bits will be set, regardless of the status of the GIE, PEIE and individual interrupt enable bits.

The following events happen when an interrupt event occurs while the GIE bit is set:

- Current prefetched instruction is flushed

- · GIE bit is cleared

- Current Program Counter (PC) is pushed onto the stack

- Critical registers are automatically saved to the shadow registers (See "Section 8.5 "Automatic Context Saving".")

- PC is loaded with the interrupt vector 0004h

The firmware within the Interrupt Service Routine (ISR) should determine the source of the interrupt by polling the interrupt flag bits. The interrupt flag bits must be cleared before exiting the ISR to avoid repeated interrupts. Because the GIE bit is cleared, any interrupt that occurs while executing the ISR will be recorded through its interrupt flag, but will not cause the processor to redirect to the interrupt vector.

The RETFIE instruction exits the ISR by popping the previous address from the stack, restoring the saved context from the shadow registers and setting the GIE bit.

For additional information on a specific interrupt's operation, refer to its peripheral chapter.

| Note 1: | Individual  | interrupt |     | flag  | bits | s are | set,  |

|---------|-------------|-----------|-----|-------|------|-------|-------|

|         | regardless  | of        | the | state | of   | any   | other |

|         | enable bits |           |     |       |      |       |       |

2: All interrupts will be ignored while the GIE bit is cleared. Any interrupt occurring while the GIE bit is clear will be serviced when the GIE bit is set again.

# 8.2 Interrupt Latency

Interrupt latency is defined as the time from when the interrupt event occurs to the time code execution at the interrupt vector begins. The latency for synchronous interrupts is three or four instruction cycles. For asynchronous interrupts, the latency is three to five instruction cycles, depending on when the interrupt occurs. See Figure 8-2 and Figure 8.3 for more details.

| U-0                                                                                         | U-0        | U-0               | R/W-0/0 | U-0                                                   | U-0 | U-0 | U-0   |  |  |  |

|---------------------------------------------------------------------------------------------|------------|-------------------|---------|-------------------------------------------------------|-----|-----|-------|--|--|--|

| —                                                                                           | —          | - CCP3IE          |         | —                                                     | —   | —   | —     |  |  |  |

| bit 7                                                                                       | bit 7      |                   |         |                                                       |     |     | bit 0 |  |  |  |

|                                                                                             |            |                   |         |                                                       |     |     |       |  |  |  |

| Legend:                                                                                     |            |                   |         |                                                       |     |     |       |  |  |  |

| R = Readable                                                                                | bit        | W = Writable      | bit     | U = Unimplemented bit, read as '0'                    |     |     |       |  |  |  |

| u = Bit is unch                                                                             | nanged     | x = Bit is unkn   | iown    | -n/n = Value at POR and BOR/Value at all other Resets |     |     |       |  |  |  |

| '1' = Bit is set                                                                            |            | '0' = Bit is clea | ared    |                                                       |     |     |       |  |  |  |

| bit 7-5                                                                                     | Unimplemen | ted: Read as '    | )'      |                                                       |     |     |       |  |  |  |

| bit 4                                                                                       | •          | P3 Interrupt Ena  |         |                                                       |     |     |       |  |  |  |

| <ul> <li>1 = Enables the CCP3 interrupt</li> <li>0 = Disables the CCP3 interrupt</li> </ul> |            |                   |         |                                                       |     |     |       |  |  |  |

| bit 3-0                                                                                     | Unimplemen | ted: Read as '    | )'      |                                                       |     |     |       |  |  |  |

# REGISTER 8-4: PIE3: PERIPHERAL INTERRUPT ENABLE REGISTER 3

### REGISTER 13-38: WPUE: WEAK PULL-UP PORTE REGISTER

| U-0   | U-0 | U-0 | U-0 | R/W-1/1 | R/W-1/1              | R/W-1/1              | R/W-1/1              |

|-------|-----|-----|-----|---------|----------------------|----------------------|----------------------|

| —     | _   | _   | _   | WPUE3   | WPUE2 <sup>(3)</sup> | WPUE1 <sup>(3)</sup> | WPUE0 <sup>(3)</sup> |

| bit 7 |     |     |     |         |                      |                      | bit 0                |

|       |     |     |     |         |                      |                      |                      |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

|                      |                      |                                                       |

bit 7-4 Unimplemented: Read as '0'

bit 3-0 WPUE<3:0>: Weak Pull-up Register bit<sup>(3)</sup> 1 = Pull-up enabled 0 = Pull-up disabled

**Note 1:** Global WPUEN bit of the OPTION\_REG register must be cleared for individual pull-ups to be enabled.

- 2: The weak pull-up device is automatically disabled if the pin is in configured as an output.

- 3: WPUSE<2:0> are available on PIC16(L)F1784/7 only.

# **REGISTER 13-39: ODCONE: PORTE OPEN DRAIN CONTROL REGISTER<sup>(1)</sup>**

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|-----|-----|---------|---------|---------|

| —     | _   | -   | —   | _   | ODE2    | ODE1    | ODE0    |

| bit 7 |     |     |     |     |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-3 Unimplemented: Read as '0'

bit 2-0 **ODE<2:0>:** PORTE Open Drain Enable bits For RE<2:0> pins, respectively

1 = Port pin operates as open-drain drive (sink current only)

0 = Port pin operates as standard push-pull drive (source and sink current)

Note 1: ODCONE<2:0> are available on PIC16(L)F1784/7 only.

|  | REGISTER 20-3: | CMOUT: COMPARATOR OUTPUT REGISTER |

|--|----------------|-----------------------------------|

|--|----------------|-----------------------------------|

| U-0   | U-0 | U-0 | U-0 | R-0/0                 | R-0/0  | R-0/0  | R-0/0  |

|-------|-----|-----|-----|-----------------------|--------|--------|--------|

| —     | _   | _   | —   | MC4OUT <sup>(1)</sup> | MC3OUT | MC2OUT | MC10UT |

| bit 7 |     |     |     |                       |        |        | bit 0  |

# Legend:

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

|----------------------|----------------------|-------------------------------------------------------|

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

- bit 7-4 Unimplemented: Read as '0'

- bit 3 MC4OUT: Mirror Copy of C4OUT bit<sup>(1)</sup>

- bit 2 MC3OUT: Mirror Copy of C3OUT bit

- bit 1 MC2OUT: Mirror Copy of C2OUT bit

- bit 0 MC1OUT: Mirror Copy of C1OUT bit

Note 1: PIC16(L)F1784/7 only.

### TABLE 20-3: SUMMARY OF REGISTERS ASSOCIATED WITH COMPARATOR MODULE

| Name     | Bit 7  | Bit 6  | Bit 5   | Bit 4     | Bit 3                 | Bit 2      | Bit 1      | Bit 0   | Register<br>on Page |

|----------|--------|--------|---------|-----------|-----------------------|------------|------------|---------|---------------------|

| ANSELA   | ANSA7  | _      | ANSA5   | ANSA4     | ANSA3                 | ANSA2      | ANSA1      | ANSA0   | 132                 |

| ANSELB   | _      | ANSB6  | ANSB5   | ANSB4     | ANSB3                 | ANSB2      | ANSB1      | ANSB0   | 138                 |

| CM1CON0  | C10N   | C1OUT  | C10E    | C1POL     | C1ZLF                 | C1SP       | C1HYS      | C1SYNC  | 193                 |

| CM2CON0  | C2ON   | C2OUT  | C2OE    | C2POL     | C2ZLF                 | C2SP       | C2HYS      | C2SYNC  | 193                 |

| CM1CON1  | C1NTP  | C1INTN |         | C1PCH<2:0 | >                     |            | C1NCH<2:0> | •       | 194                 |

| CM2CON1  | C2NTP  | C2INTN |         | C2PCH<2:0 | >                     |            | C2NCH<2:0> | •       | 194                 |

| CM3CON0  | C3ON   | C3OUT  | C3OE    | C3POL     | C3ZLF                 | C3SP       | C3HYS      | C3SYNC  | 193                 |

| CM3CON1  | C3INTP | C3INTN |         | C3PCH<2:0 | >                     | C3NCH<2:0> |            |         | 194                 |

| CMOUT    | _      | _      | _       | _         | MC4OUT <sup>(1)</sup> | MC3OUT     | MC2OUT     | MC10UT  | 195                 |

| FVRCON   | FVREN  | FVRRDY | TSEN    | TSRNG     | CDAFV                 | R<1:0>     | ADFV       | R<1:0>  | 162                 |

| DAC1CON0 | DAC1EN |        | DAC10E1 | DAC10E2   | DAC1PS                | SS<1:0>    | —          | DAC1NSS | 186                 |

| DAC1CON1 |        |        |         | DAC1F     | R<7:0>                |            |            |         | 186                 |

| INTCON   | GIE    | PEIE   | TMR0IE  | INTE      | IOCIE                 | TMR0IF     | INTF       | IOCIF   | 93                  |

| PIE2     | OSFIE  | C2IE   | C1IE    | EEIE      | BCL1IE                | C4IE       | C3IE       | CCP2IE  | 95                  |

| PIR2     | OSFIF  | C2IF   | C1IF    | EEIF      | BCL1IF                | C4IF       | C3IF       | CCP2IF  | 99                  |

| TRISA    | TRISA7 | TRISA6 | TRISA5  | TRISA4    | TRISA3                | TRISA2     | TRISA1     | TRISA0  | 132                 |

| TRISB    | TRISB7 | TRISB6 | TRISB5  | TRISB4    | TRISB3                | TRISB2     | TRISB1     | TRISB0  | 138                 |

| TRISC    | TRISC7 | TRISC6 | TRISC5  | TRISC4    | TRISC3                | TRISC2     | TRISC1     | TRISC0  | 142                 |

Legend: — = unimplemented location, read as '0'. Shaded cells are unused by the comparator module.

**Note 1:** PIC16(L)F1784/7 only.

| Name    | Bit 7        | Bit 6           | Bit 5          | Bit 4          | Bit 3          | Bit 2    | Bit 1  | Bit 0  | Register<br>on Page |

|---------|--------------|-----------------|----------------|----------------|----------------|----------|--------|--------|---------------------|

| ANSELB  | —            | ANSB6           | ANSB5          | ANSB4          | ANSB3          | ANSB2    | ANSB1  | ANSB0  | 138                 |

| CCP1CON | —            | _               | DC1B           | <1:0>          |                | CCP1N    | 1<3:0> |        | 280                 |

| CCP2CON | —            | _               | DC2B           | <1:0>          |                | CCP2N    | 1<3:0> |        | 280                 |

| INTCON  | GIE          | PEIE            | TMR0IE         | INTE           | IOCIE          | TMR0IF   | INTF   | IOCIF  | 93                  |

| PIE1    | TMR1GIE      | ADIE            | RCIE           | TXIE           | SSP1IE         | CCP1IE   | TMR2IE | TMR1IE | 94                  |

| PIR1    | TMR1GIF      | ADIF            | RCIF           | TXIF           | SSP1IF         | CCP1IF   | TMR2IF | TMR1IF | 98                  |

| TMR1H   | Holding Regi | ster for the M  | ost Significan | t Byte of the  | 16-bit TMR1 F  | Register |        |        | 199*                |

| TMR1L   | Holding Regi | ster for the Le | east Significa | nt Byte of the | 16-bit TMR1    | Register |        |        | 199*                |

| TRISB   | TRISB7       | TRISB6          | TRISB5         | TRISB4         | TRISB3         | TRISB2   | TRISB1 | TRISB0 | 137                 |

| TRISC   | TRISC7       | TRISC6          | TRISC5         | TRISC4         | TRISC3         | TRISC2   | TRISC1 | TRISC0 | 142                 |

| T1CON   | TMR1C        | S<1:0>          | T1CKP          | T1CKPS<1:0>    |                | T1SYNC   | —      | TMR10N | 207                 |

| T1GCON  | TMR1GE       | T1GPOL          | T1GTM          | T1GSPM         | T1GGO/<br>DONE | T1GVAL   | T1GS   | S<1:0> | 208                 |

| TABLE 22-5: | SUMMARY OF REGISTERS ASSOCIATED WITH TIMER1 |

|-------------|---------------------------------------------|

|-------------|---------------------------------------------|

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by the Timer1 module.

\* Page provides register information.

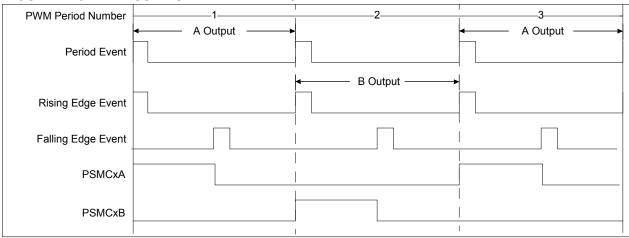

#### 24.3.3 PUSH-PULL PWM

The push-pull PWM is used to drive transistor bridge circuits. It uses at least two outputs and generates PWM signals that alternate between the two outputs in even and odd cycles.

Variations of the push-pull waveform include four outputs with two outputs being complementary or two sets of two identical outputs. Refer to Sections 24.3.4 through 24.3.6 for the other Push-Pull modes.

#### 24.3.3.1 Mode Features

- · No dead-band control available

- · No steering control available

- · Output is on the following two pins only:

- PSMCxA

- PSMCxB

Note: This is a subset of the 6-pin output of the push-pull PWM output, which is why pin functions are fixed in these positions, so they are compatible with that mode. See Section 24.3.6 "Push-Pull PWM with Four Full-Bridge and Complementary Outputs"

#### 24.3.3.2 Waveform Generation

Odd numbered period rising edge event:

PSMCxA is set active

Odd numbered period falling edge event:

· PSMCxA is set inactive

Even numbered period rising edge event:

PSMCxB is set active

Even numbered period falling edge event:

PSMCxB is set inactive

#### **FIGURE 24-6:** PUSH-PULL PWM WAVEFORM

Code for setting up the PSMC generate the complementary single-phase waveform shown in Figure 24-6, and given in Example 24-3.

#### EXAMPLE 24-3: **PUSH-PULL SETUP**

- ; Push-Pull PWM PSMC setup

- ; Fully synchronous operation

- ; Period = 10 us

BCF

TRISC, 1

; Duty cycle = 50% (25% each phase) BANKSEL PSMC1CON MOVLW  $0 \times 02$ ; set period MOVWF PSMC1PRH MOVLW  $0 \times 7 F$ MOVWF PSMC1PRL MOVLW 0x01 ; set duty cycle MOVWF PSMC1DCH MOVLW 0x3F MOVWF PSMC1DCL CLRF PSMC1PHH ; no phase offset PSMC1PHL CLRF MOVLW 0x01 ; PSMC clock=64 MHz MOVWF PSMC1CLK ; output on A and B, normal polarity MOVLW B'0000011' MOVWF PSMC10EN CLRF PSMC1POL ; set time base as source for all events BSF PSMC1PRS, P1PRST BSF PSMC1PHS, P1PHST BSF PSMC1DCS, P1DCST ; enable PSMC in Push-Pull Mode ; this also loads steering and time buffers MOVLW B'11000010' MOVWF PSMC1CON BANKSEL TRISC BCF TRISC, 0 ; enable pin drivers

### 24.5.3 COMPLEMENTARY PWM STEERING

In Complementary PWM Steering mode, the primary PWM signal (non-complementary) and complementary signal can be steered according to their respective type.

Primary PWM signal can be steered to any of the following outputs:

- PSMCxA

- PSMCxC

- PSMCxE

The complementary PWM signal can be steered to any of the following outputs:

- PSMCxB

- PSMCxD

- PSMCxE

Examples of unsynchronized complementary steering are shown in Figure 24-17.

# FIGURE 24-17: COMPLEMENTARY PWM STEERING WAVEFORM (NO SYNCHRONIZATION, ZERO DEAD-BAND TIME)

| Base_PWM_signal |                                                                                                                    |

|-----------------|--------------------------------------------------------------------------------------------------------------------|

| PxSTRA          |                                                                                                                    |

| PSMCxA          |                                                                                                                    |

| PSMCxB          |                                                                                                                    |

| PxSTRB          | Arrows indicate where a change in the steering bit automatically forces a change in the corresponding PSMC output. |

| PxSTRC          |                                                                                                                    |

| PSMCxC          |                                                                                                                    |

| PSMCxD          |                                                                                                                    |

| PxSTRD          |                                                                                                                    |

| PxSTRE          |                                                                                                                    |

| PSMCxE          |                                                                                                                    |

| PSMCxF          |                                                                                                                    |

| PxSTRF          |                                                                                                                    |

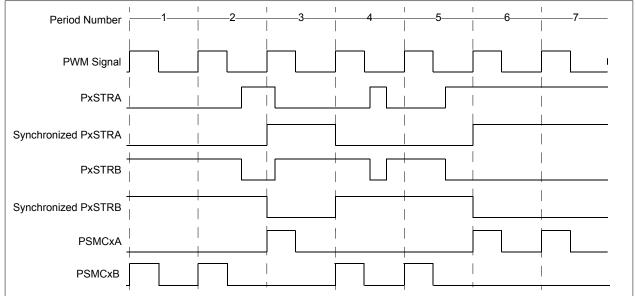

### 24.5.4 SYNCHRONIZED PWM STEERING

In Single, Complementary and 3-phase PWM modes, it is possible to synchronize changes to steering selections with the period event. This is so that PWM outputs do not change in the middle of a cycle and therefore, disrupt operation of the application.

Steering synchronization is enabled by setting the PxSSYNC bit of the PSMC Steering Control 1 (PSMCxSTR1) register (Register 24-32).

When synchronized steering is enabled while the PSMC module is enabled, steering changes do not take effect until the first period event after the PSMCxLD bit is set.

Examples of synchronized steering are shown in Figure 24-18.

### 24.5.5 INITIALIZING SYNCHRONIZED STEERING

If synchronized steering is to be used, special care should be taken to initialize the PSMC Steering Control 0 (PSMCxSTR0) register (Register 24-31) in a safe configuration before setting either the PSMCxEN or PSMCxLD bits. When either of those bits are set, the PSMCxSTR0 value at that time is loaded into the synchronized steering output buffer. The buffer load occurs even if the PxSSYNC bit is low. When the PxSSYNC bit is set, the outputs will immediately go to the drive states in the preloaded buffer.

FIGURE 24-18: PWM STEERING WITH SYNCHRONIZATION WAVEFORM

# PIC16(L)F1784/6/7

# 27.5.1.5 Synchronous Master Reception

Data is received at the RX/DT pin. The RX/DT pin output driver is automatically disabled when the EUSART is configured for synchronous master receive operation.

In Synchronous mode, reception is enabled by setting either the Single Receive Enable bit (SREN of the RCSTA register) or the Continuous Receive Enable bit (CREN of the RCSTA register).

When SREN is set and CREN is clear, only as many clock cycles are generated as there are data bits in a single character. The SREN bit is automatically cleared at the completion of one character. When CREN is set, clocks are continuously generated until CREN is cleared. If CREN is cleared in the middle of a character the CK clock stops immediately and the partial character is discarded. If SREN and CREN are both set, then SREN is cleared at the completion of the first character and CREN takes precedence.

To initiate reception, set either SREN or CREN. Data is sampled at the RX/DT pin on the trailing edge of the TX/CK clock pin and is shifted into the Receive Shift Register (RSR). When a complete character is received into the RSR, the RCIF bit is set and the character is automatically transferred to the two character receive FIFO. The Least Significant eight bits of the top character in the receive FIFO are available in RCREG. The RCIF bit remains set as long as there are unread characters in the receive FIFO.

| Note: | If the RX/DT function is on an analog pin, |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|

|       | the corresponding ANSEL bit must be        |  |  |  |  |  |

|       | cleared for the receiver to function.      |  |  |  |  |  |

# 27.5.1.6 Slave Clock

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a slave receives the clock on the TX/CK line. The TX/CK pin output driver is automatically disabled when the device is configured for synchronous slave transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One data bit is transferred for each clock cycle. Only as many clock cycles should be received as there are data bits.

**Note:** If the device is configured as a slave and the TX/CK function is on an analog pin, the corresponding ANSEL bit must be cleared.

# 27.5.1.7 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated if a third character, in its entirety, is received before RCREG is read to access the FIFO. When this happens the OERR bit of the RCSTA register is set. Previous data in the FIFO will not be overwritten. The two characters in the FIFO buffer can be read, however, no additional characters

will be received until the error is cleared. The OERR bit can only be cleared by clearing the overrun condition. If the overrun error occurred when the SREN bit is set and CREN is clear then the error is cleared by reading RCREG. If the overrun occurred when the CREN bit is set then the error condition is cleared by either clearing the CREN bit of the RCSTA register or by clearing the SPEN bit which resets the EUSART.

# 27.5.1.8 Receiving 9-bit Characters

The EUSART supports 9-bit character reception. When the RX9 bit of the RCSTA register is set the EUSART will shift 9-bits into the RSR for each character received. The RX9D bit of the RCSTA register is the ninth, and Most Significant, data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the eight Least Significant bits from the RCREG.

# 27.5.1.9 Synchronous Master Reception Set-up:

- 1. Initialize the SPBRGH, SPBRGL register pair for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Clear the ANSEL bit for the RX pin (if applicable).

- 3. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 4. Ensure bits CREN and SREN are clear.

- 5. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 6. If 9-bit reception is desired, set bit RX9.

- 7. Start reception by setting the SREN bit or for continuous reception, set the CREN bit.

- 8. Interrupt flag bit RCIF will be set when reception of a character is complete. An interrupt will be generated if the enable bit RCIE was set.

- 9. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 10. Read the 8-bit received data by reading the RCREG register.

- 11. If an overrun error occurs, clear the error by either clearing the CREN bit of the RCSTA register or by clearing the SPEN bit which resets the EUSART.

# PIC16(L)F1784/6/7

# TABLE 30-4: I/O PORTS (CONTINUED)

Standard Operating Conditions (unless otherwise stated)

| Param<br>No. | Sym.  | Characteristic                                   | Min. | Тур† | Max. | Units | Conditions                                                             |  |

|--------------|-------|--------------------------------------------------|------|------|------|-------|------------------------------------------------------------------------|--|

|              |       | Capacitive Loading Specs on Output Pins          |      |      |      |       |                                                                        |  |

| D101*        | COSC2 | OSC2 pin                                         | —    | —    | 15   | pF    | In XT, HS and LP modes when<br>external clock is used to drive<br>OSC1 |  |

| D101A*       | Сю    | All I/O pins                                     | —    | _    | 50   | pF    |                                                                        |  |

|              |       | VCAP Capacitor Charging                          |      |      |      |       |                                                                        |  |

| D102         |       | Charging current                                 |      | 200  |      | μΑ    |                                                                        |  |

| D102A        |       | Source/sink capability when<br>charging complete | —    | 0.0  | —    | mA    |                                                                        |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended to use an external clock in RC mode.

**2:** Negative current is defined as current sourced by the pin.

3: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

**4:** Including OSC2 in CLKOUT mode.

| Param<br>No. | Sym.   | Characteristic                                                      | Min.   | Тур† | Max.   | Units | Conditions                                    |

|--------------|--------|---------------------------------------------------------------------|--------|------|--------|-------|-----------------------------------------------|

|              |        | Program Memory<br>Programming Specifications                        |        |      |        |       |                                               |

| D110         | VIHH   | Voltage on MCLR/VPP/RE3 pin                                         | 8.0    | _    | 9.0    | V     | (Note 3)                                      |

| D111         | IDDP   | Supply Current during<br>Programming                                | —      | —    | 10     | mA    |                                               |

| D112         |        | VDD for Bulk Erase                                                  | 2.7    | —    | VDDMAX | V     |                                               |

| D113         | VPEW   | VDD for Write or Row Erase                                          | VDDMIN | —    | VDDMAX | V     |                                               |

| D114         | IPPPGM | Current on MCLR/VPP during<br>Erase/Write                           | —      | —    | 1.0    | mA    |                                               |

| D115         | IDDPGM | Current on VDD during Erase/Write                                   | —      |      | 5.0    | mA    |                                               |

|              |        | Data EEPROM Memory                                                  |        |      |        |       |                                               |

| D116         | ED     | Byte Endurance                                                      | 100K   | —    | _      | E/W   | -40°C to +85°C                                |

| D117         | VDRW   | VDD for Read/Write                                                  | VDDMIN | —    | VDDMAX | V     |                                               |

| D118         | TDEW   | Erase/Write Cycle Time                                              | —      | 4.0  | 5.0    | ms    |                                               |

| D119         | TRETD  | Characteristic Retention                                            | —      | 40   | _      | Year  | Provided no other specifications are violated |

| D120         | TREF   | Number of Total Erase/Write<br>Cycles before Refresh <sup>(2)</sup> | 100k   | —    | _      | E/W   | -40°C to +85°C                                |

|              |        | Program Flash Memory                                                |        |      |        |       |                                               |

| D121         | Eр     | Cell Endurance                                                      | 10K    | —    | _      | E/W   | -40°C to +85°C ( <b>Note 1</b> )              |

| D122         | Vpr    | VDD for Read                                                        | VDDMIN | —    | VDDMAX | V     |                                               |

| D123         | Tiw    | Self-timed Write Cycle Time                                         | —      | 2    | 2.5    | ms    |                                               |

| D124         | TRETD  | Characteristic Retention                                            | —      | 40   | _      | Year  | Provided no other specifications are violated |

# Standard Operating Conditions (unless otherwise stated)

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Self-write and Block Erase.

2: Refer to Section 12.2 "Using the Data EEPROM" for a more detailed discussion on data EEPROM endurance.

3: Required only if single-supply programming is disabled.

# 30.5 AC Characteristics

Timing Parameter Symbology has been created with one of the following formats:

1. TppS2ppS

2. TppS

| 2. TPp0 |                                       |     |                |

|---------|---------------------------------------|-----|----------------|

| т       |                                       |     |                |

| F       | Frequency                             | Т   | Time           |

| Lowerc  | case letters (pp) and their meanings: |     |                |

| рр      |                                       |     |                |

| сс      | CCP1                                  | OSC | OSC1           |

| ck      | CLKOUT                                | rd  | RD             |

| CS      | CS                                    | rw  | RD or WR       |

| di      | SDI                                   | SC  | SCK            |

| do      | SDO                                   | SS  | SS             |

| dt      | Data in                               | tO  | TOCKI          |

| io      | I/O PORT                              | t1  | T1CKI          |

| mc      | MCLR                                  | wr  | WR             |

| Upperc  | case letters and their meanings:      |     |                |

| S       |                                       |     |                |

| F       | Fall                                  | Р   | Period         |

| н       | High                                  | R   | Rise           |

| I       | Invalid (High-impedance)              | V   | Valid          |

| L       | Low                                   | Z   | High-impedance |

# FIGURE 30-4: LOAD CONDITIONS

# PIC16(L)F1784/6/7

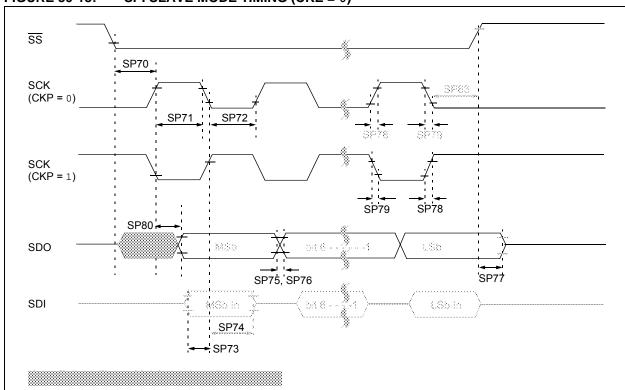

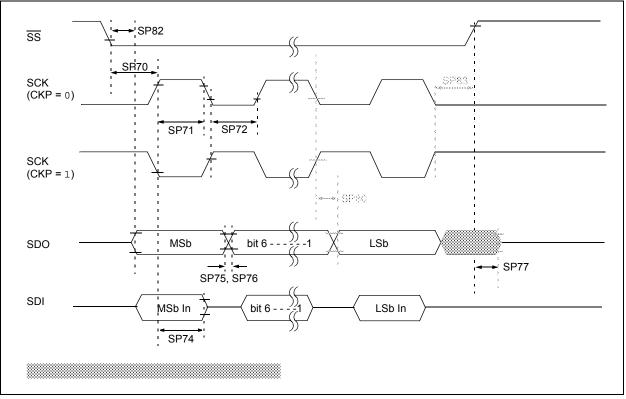

### FIGURE 30-18: SPI SLAVE MODE TIMING (CKE = 0)

# 32.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16, and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- · Flexible macro language

- MPLAB X IDE compatibility

# 32.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB X IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

# 32.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

# 32.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- Support for fixed-point and floating-point data

- Command-line interface

- Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

# 33.2 Package Details

The following sections give the technical details of the packages.

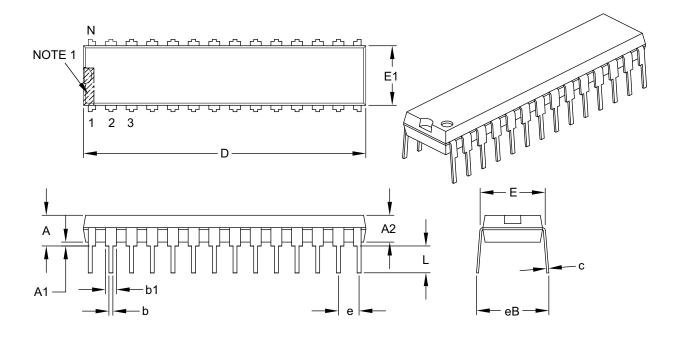

### 28-Lead Skinny Plastic Dual In-Line (SP) – 300 mil Body [SPDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units            |       |          | INCHES |  |  |  |

|----------------------------|------------------|-------|----------|--------|--|--|--|

| Dime                       | Dimension Limits |       | NOM      | MAX    |  |  |  |

| Number of Pins N           |                  | 28    |          |        |  |  |  |

| Pitch                      | е                |       | .100 BSC |        |  |  |  |

| Top to Seating Plane       | А                | -     | -        | .200   |  |  |  |

| Molded Package Thickness   | A2               | .120  | .135     | .150   |  |  |  |

| Base to Seating Plane      | A1               | .015  | -        | _      |  |  |  |

| Shoulder to Shoulder Width | E                | .290  | .310     | .335   |  |  |  |

| Molded Package Width       | E1               | .240  | .285     | .295   |  |  |  |

| Overall Length             | D                | 1.345 | 1.365    | 1.400  |  |  |  |

| Tip to Seating Plane       | L                | .110  | .130     | .150   |  |  |  |

| Lead Thickness             | С                | .008  | .010     | .015   |  |  |  |

| Upper Lead Width           | b1               | .040  | .050     | .070   |  |  |  |

| Lower Lead Width           | b                | .014  | .018     | .022   |  |  |  |

| Overall Row Spacing §      | eB               | -     | -        | .430   |  |  |  |

### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-070B

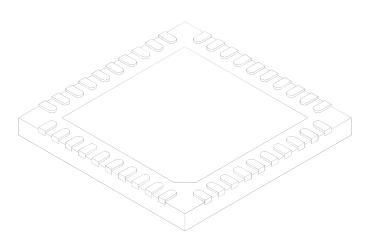

# 40-Lead Ultra Thin Plastic Quad Flat, No Lead Package (MV) – 5x5x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | MILLIMETERS |                |          |      |  |

|------------------------|-------------|----------------|----------|------|--|

| Dimensio               | MIN         | NOM            | MAX      |      |  |

| Number of Pins         | N           |                | 40       |      |  |

| Pitch                  | е           |                | 0.40 BSC |      |  |

| Overall Height         | Α           | 0.45           | 0.50     | 0.55 |  |

| Standoff               | A1          | 0.00           | 0.02     | 0.05 |  |

| Contact Thickness      | A3          | 0.127 REF      |          | -    |  |

| Overall Width          | E           | 5.00 BSC       |          |      |  |

| Exposed Pad Width      | E2          | 3.60 3.70 3.80 |          |      |  |

| Overall Length         | D           | 5.00 BSC       |          |      |  |

| Exposed Pad Length     | D2          | 3.60           | 3.70     | 3.80 |  |

| Contact Width          | b           | 0.15           | 0.20     | 0.25 |  |

| Contact Length         | L           | 0.30           | 0.40     | 0.50 |  |

| Contact-to-Exposed Pad |             | 0.20           | -        | -    |  |

### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-156A Sheet 2 of 2