Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PSMC, PWM, WDT                                 |

| Number of I/O              | 35                                                                          |

| Program Memory Size        | 7KB (4K x 14)                                                               |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 512 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 14x12b; D/A 1x8b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 40-UFQFN Exposed Pad                                                        |

| Supplier Device Package    | 40-UQFN (5x5)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1784t-i-mv |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Table of Contents**

| 1.0   | Device Overview                                |     |

|-------|------------------------------------------------|-----|

| 2.0   | Enhanced Mid-Range CPU                         |     |

| 3.0   | Memory Organization                            | 23  |

| 4.0   | Device Configuration                           | 53  |

| 5.0   | Resets                                         | 59  |

| 6.0   | Oscillator Module                              | 67  |

| 7.0   | Reference Clock Module                         | 85  |

| 8.0   | Interrupts                                     |     |

| 9.0   | Power-Down Mode (Sleep)                        | 103 |

|       | Low Dropout (LDO) Voltage Regulator            |     |

| 11.0  | Watchdog Timer (WDT)                           |     |

| 12.0  | Date EEPROM and Flash Program Memory Control   |     |

| 13.0  | I/O Ports                                      | 125 |

| 14.0  | Interrupt-on-Change                            |     |

| 15.0  | Fixed Voltage Reference (FVR)                  |     |

|       | Temperature Indicator                          |     |

| 17.0  | Analog-to-Digital Converter (ADC) Module       |     |

| 18.0  | Operational Amplifier (OPA) Module             |     |

|       | Digital-to-Analog Converter (DAC) Module       |     |

|       | Comparator Module                              |     |

| 21.0  | Timer0 Module                                  | 196 |

|       | Timer1 Module                                  |     |

|       | Timer2 Module                                  |     |

|       | Programmable Switch Mode Control (PSMC) Module |     |

|       | Capture/Compare/PWM Module                     |     |

|       | Master Synchronous Serial Port (MSSP) Module   |     |

|       | · · · · · · · · · · · · · · · · · · ·          |     |

|       | In-Circuit Serial Programming™ (ICSP™)         |     |

|       | Instruction Set Summary                        |     |

|       | Electrical Specifications                      |     |

| 31.0  | DC and AC Characteristics Graphs and Tables    |     |

| 32.0  | Development Support                            |     |

|       | Packaging Information                          |     |

|       | ndix A: Revision History                       |     |

|       | Aicrochip Web Site                             |     |

|       | omer Change Notification Service               |     |

|       | omer Support                                   |     |

| Produ | uct Identification System                      | 462 |

# PIC16(L)F1784/6/7

#### TABLE 3-12: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

| Addr       | Name    | Bit 7         Bit 6         Bit 5         Bit 4         Bit 3         Bit 2         Bit 1         Bit 0 |   |  |  |  |  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |   |   |

|------------|---------|---------------------------------------------------------------------------------------------------------|---|--|--|--|--|----------------------|---------------------------------|---|---|

| Bank       | c 11-15 |                                                                                                         |   |  |  |  |  |                      |                                 |   |   |

| x0Ch       |         |                                                                                                         |   |  |  |  |  |                      |                                 |   |   |

| or<br>x8Ch |         |                                                                                                         |   |  |  |  |  |                      |                                 |   |   |

| to         | _       | Unimplemente                                                                                            | d |  |  |  |  |                      |                                 | _ | _ |

| x6Fh       |         |                                                                                                         |   |  |  |  |  |                      |                                 |   |   |

| or<br>xEFh |         |                                                                                                         |   |  |  |  |  |                      |                                 |   |   |

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

**1:** These registers can be addressed from any bank.

**2:** Unimplemented, read as '1'.

3: PIC16(L)F1784/7 only.

Note

4: PIC16F1784/6/7 only.

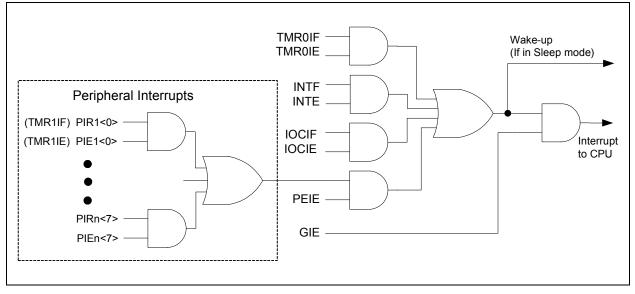

# 8.0 INTERRUPTS

The interrupt feature allows certain events to preempt normal program flow. Firmware is used to determine the source of the interrupt and act accordingly. Some interrupts can be configured to wake the MCU from Sleep mode.

This chapter contains the following information for Interrupts:

- · Operation

- Interrupt Latency

- Interrupts During Sleep

- INT Pin

- · Automatic Context Saving

Many peripherals produce interrupts. Refer to the corresponding chapters for details.

A block diagram of the interrupt logic is shown in Figure 8-1.

#### FIGURE 8-1: INTERRUPT LOGIC

### 8.1 Operation

Interrupts are disabled upon any device Reset. They are enabled by setting the following bits:

- · GIE bit of the INTCON register

- Interrupt Enable bit(s) for the specific interrupt event(s)

- PEIE bit of the INTCON register (if the Interrupt Enable bit of the interrupt event is contained in the PIE1 or PIE2 registers)

The INTCON, PIR1 and PIR2 registers record individual interrupts via interrupt flag bits. Interrupt flag bits will be set, regardless of the status of the GIE, PEIE and individual interrupt enable bits.

The following events happen when an interrupt event occurs while the GIE bit is set:

- Current prefetched instruction is flushed

- · GIE bit is cleared

- Current Program Counter (PC) is pushed onto the stack

- Critical registers are automatically saved to the shadow registers (See "Section 8.5 "Automatic Context Saving".")

- PC is loaded with the interrupt vector 0004h

The firmware within the Interrupt Service Routine (ISR) should determine the source of the interrupt by polling the interrupt flag bits. The interrupt flag bits must be cleared before exiting the ISR to avoid repeated interrupts. Because the GIE bit is cleared, any interrupt that occurs while executing the ISR will be recorded through its interrupt flag, but will not cause the processor to redirect to the interrupt vector.

The RETFIE instruction exits the ISR by popping the previous address from the stack, restoring the saved context from the shadow registers and setting the GIE bit.

For additional information on a specific interrupt's operation, refer to its peripheral chapter.

| Note 1: | Individual  | inte | rrupt | flag  | bits | s are | set,  |

|---------|-------------|------|-------|-------|------|-------|-------|

|         | regardless  | of   | the   | state | of   | any   | other |

|         | enable bits |      |       |       |      |       |       |

2: All interrupts will be ignored while the GIE bit is cleared. Any interrupt occurring while the GIE bit is clear will be serviced when the GIE bit is set again.

### 8.2 Interrupt Latency

Interrupt latency is defined as the time from when the interrupt event occurs to the time code execution at the interrupt vector begins. The latency for synchronous interrupts is three or four instruction cycles. For asynchronous interrupts, the latency is three to five instruction cycles, depending on when the interrupt occurs. See Figure 8-2 and Figure 8.3 for more details.

# 8.6 Register Definitions: Interrupt Control

| R/W-0/0          | R/W-0/0                                                                                                                          | R/W-0/0                                                    | R/W-0/0         | R/W-0/0          | R/W-0/0          | R/W-0/0          | R-0/0                |

|------------------|----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|-----------------|------------------|------------------|------------------|----------------------|

| GIE              | PEIE                                                                                                                             | TMR0IE                                                     | INTE            | IOCIE            | TMR0IF           | INTF             | IOCIF <sup>(1)</sup> |

| bit 7            |                                                                                                                                  | ·                                                          |                 |                  |                  |                  | bit 0                |

|                  |                                                                                                                                  |                                                            |                 |                  |                  |                  |                      |

| Legend:          |                                                                                                                                  |                                                            |                 |                  |                  | (0)              |                      |

| R = Readable     |                                                                                                                                  | W = Writable                                               |                 | •                | nented bit, read |                  |                      |

| u = Bit is unch  | •                                                                                                                                | x = Bit is unkr                                            |                 | -n/n = Value a   | at POR and BO    | R/Value at all o | ther Resets          |

| '1' = Bit is set |                                                                                                                                  | '0' = Bit is clea                                          | ared            |                  |                  |                  |                      |

| bit 7            | GIE: Global I                                                                                                                    | nterrupt Enable                                            | hit             |                  |                  |                  |                      |

|                  |                                                                                                                                  | all active interru                                         |                 |                  |                  |                  |                      |

| bit 6            | 1 = Enables                                                                                                                      | eral Interrupt E<br>all active periph<br>all peripheral ir | eral interrupts | 3                |                  |                  |                      |

| bit 5            | 1 = Enables f                                                                                                                    | er0 Overflow Ir<br>the Timer0 inter<br>the Timer0 inte     | rupt            | e bit            |                  |                  |                      |

| bit 4            | 1 = Enables f                                                                                                                    | tternal Interrupt<br>the INT externa<br>the INT externa    | l interrupt     |                  |                  |                  |                      |

| bit 3            | 1 = Enables f                                                                                                                    | upt-on-Change<br>the interrupt-on<br>the interrupt-or      | -change         |                  |                  |                  |                      |

| bit 2            | 1 = TMR0 reg                                                                                                                     | er0 Overflow Ir<br>gister has overf<br>gister did not ov   | lowed           | it               |                  |                  |                      |

| bit 1            | INTF: INT External Interrupt Flag bit<br>1 = The INT external interrupt occurred<br>0 = The INT external interrupt did not occur |                                                            |                 |                  |                  |                  |                      |

| bit 0            | (4)                                                                                                                              |                                                            |                 |                  |                  |                  |                      |

|                  | e IOCIF Flag bi<br>ve been cleared                                                                                               |                                                            | nd cleared wh   | en all the Inter | rupt-on-change   | flags in the IO  | CBF register         |

#### REGISTER 8-1: INTCON: INTERRUPT CONTROL REGISTER

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Enable bit, GIE, of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

# 10.0 LOW DROPOUT (LDO) **VOLTAGE REGULATOR**

The "F" devices have an internal Low Dropout Regulator (LDO) which provide operation above 3.6V. The LDO regulates a voltage for the internal device logic while permitting the VDD and I/O pins to operate at a higher voltage. There is no user enable/disable control available for the LDO, it is always active. The "LF" devices operate at a maximum VDD of 3.6V and does not incorporate an LDO.

A device I/O pin may be configured as the LDO voltage output, identified as the VCAP pin. Although not required, an external low-ESR capacitor may be connected to the VCAP pin for additional regulator stability.

The VCAPEN bit of Configuration Words determines if which pin is assigned as the VCAP pin. Refer to Table 10-1.

**VCAPEN SELECT BIT** TABLE 10-1: VCAPEN Pin No VCAP 1 RA6 0

On power-up, the external capacitor will load the LDO voltage regulator. To prevent erroneous operation, the device is held in Reset while a constant current source charges the external capacitor. After the cap is fully charged, the device is released from Reset. For more information on the constant current rate, refer to the LDO Regulator Characteristics Table in Section 30.0 "Electrical Specifications".

#### **TABLE 10-2:** SUMMARY OF CONFIGURATION WORD WITH LDO

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5              | Bit 12/4 | Bit 11/3 | Bit 10/2 | Bit 9/1 | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|-----------------------|----------|----------|----------|---------|---------|---------------------|

|         | 13:8 | _       |         | LVP                   | DEBUG    | LPBOR    | BORV     | STVREN  | PLLEN   | 50                  |

| CONFIG2 | 7:0  | _       |         | VCAPEN <sup>(1)</sup> | _        | _        |          | WRT     | <1:0>   | 56                  |

- = unimplemented locations read as '0'. Shaded cells are not used by LDO. Legend:

Note 1: "F" devices only.

#### 11.1 Independent Clock Source

The WDT derives its time base from the 31 kHz LFINTOSC internal oscillator. Time intervals in this chapter are based on a nominal interval of 1 ms. See **Section 30.0 "Electrical Specifications**" for the LFINTOSC tolerances.

#### 11.2 WDT Operating Modes

The Watchdog Timer module has four operating modes controlled by the WDTE<1:0> bits in Configuration Words. See Table 11-1.

#### 11.2.1 WDT IS ALWAYS ON

When the WDTE bits of Configuration Words are set to '11', the WDT is always on.

WDT protection is active during Sleep.

#### 11.2.2 WDT IS OFF IN SLEEP

When the WDTE bits of Configuration Words are set to '10', the WDT is on, except in Sleep.

WDT protection is not active during Sleep.

#### 11.2.3 WDT CONTROLLED BY SOFTWARE

When the WDTE bits of Configuration Words are set to '01', the WDT is controlled by the SWDTEN bit of the WDTCON register.

WDT protection is unchanged by Sleep. See Table 11-1 for more details.

| WDTE<1:0> | SWDTEN | Device<br>Mode | WDT<br>Mode |

|-----------|--------|----------------|-------------|

| 11        | х      | Х              | Active      |

| 10        |        | Awake          | Active      |

| 10        | Х      | Sleep          | Disabled    |

| 0.1       | 1      | х              | Active      |

| 01        | 0      | ~              | Disabled    |

| 00        | х      | Х              | Disabled    |

#### TABLE 11-2: WDT CLEARING CONDITIONS

#### 11.3 Time-Out Period

The WDTPS bits of the WDTCON register set the time-out period from 1 ms to 256 seconds (nominal). After a Reset, the default time-out period is two seconds.

#### 11.4 Clearing the WDT

The WDT is cleared when any of the following conditions occur:

- Any Reset

- CLRWDT instruction is executed

- Device enters Sleep

- · Device wakes up from Sleep

- · Oscillator fail

- · WDT is disabled

- Oscillator Start-up TImer (OST) is running

See Table 11-2 for more information.

#### 11.5 Operation During Sleep

When the device enters Sleep, the WDT is cleared. If the WDT is enabled during Sleep, the WDT resumes counting.

When the device exits Sleep, the WDT is cleared again. The WDT remains clear until the OST, if enabled, completes. See **Section 6.0** "Oscillator **Module (with Fail-Safe Clock Monitor)**" for more information on the OST.

When a WDT time-out occurs while the device is in Sleep, no Reset is generated. Instead, the device wakes up and resumes operation. The TO and PD bits in the STATUS register are changed to indicate the event. See **Section 3.0** "**Memory Organization**" and Status Register (Register 3-1) for more information.

| WDT                          |  |  |  |  |  |  |

|------------------------------|--|--|--|--|--|--|

|                              |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |

| Cleared                      |  |  |  |  |  |  |

| Cleared                      |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |

| Cleared until the end of OST |  |  |  |  |  |  |

| Unaffected                   |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |

| R/W-1/1                                             | R/W-1/1 | R/W-1/1        | R/W-1/1                                              | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|-----------------------------------------------------|---------|----------------|------------------------------------------------------|---------|---------|---------|---------|

| WPUC7                                               | WPUC6   | WPUC5          | WPUC4                                                | WPUC3   | WPUC2   | WPUC1   | WPUC0   |

| bit 7                                               | 1       |                | I.                                                   |         |         | •       | bit 0   |

|                                                     |         |                |                                                      |         |         |         |         |

| Legend:                                             |         |                |                                                      |         |         |         |         |

| R = Readable bit W = Writable bit                   |         | bit            | U = Unimplemented bit, read as '0'                   |         |         |         |         |

| u = Bit is unchanged x = Bit is unknown -n/n = Valu |         | -n/n = Value a | n/n = Value at POR and BOR/Value at all other Resets |         |         |         |         |

#### REGISTER 13-22: WPUC: WEAK PULL-UP PORTC REGISTER

'0' = Bit is cleared

bit 7-0 WPUC<7:0>: Weak Pull-up Register bits 1 = Pull-up enabled 0 = Pull-up disabled

Note 1: Global WPUEN bit of the OPTION\_REG register must be cleared for individual pull-ups to be enabled.

**2:** The weak pull-up device is automatically disabled if the pin is in configured as an output.

#### REGISTER 13-23: ODCONC: PORTC OPEN DRAIN CONTROL REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| ODC7    | ODC6    | ODC5    | ODC4    | ODC3    | ODC2    | ODC1    | ODC0    |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

'1' = Bit is set

**ODC<7:0>:** PORTC Open Drain Enable bits For RC<7:0> pins, respectively

1 = Port pin operates as open-drain drive (sink current only)

0 = Port pin operates as standard push-pull drive (source and sink current)

#### REGISTER 13-24: SLRCONC: PORTC SLEW RATE CONTROL REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| SLRC7   | SLRC6   | SLRC5   | SLRC4   | SLRC3   | SLRC2   | SLRC1   | SLRC0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **SLRC<7:0>:** PORTC Slew Rate Enable bits

For RC<7:0> pins, respectively

1 = Port pin slew rate is limited

0 = Port pin slews at maximum rate

| R/W/HS-0/0                              | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0                                            | R/W/HS-0/0                         | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 |  |

|-----------------------------------------|------------|------------|-------------------------------------------------------|------------------------------------|------------|------------|------------|--|

| IOCxF7                                  | IOCxF6     | IOCxF5     | IOCxF4                                                | IOCxF3                             | IOCxF2     | IOCxF1     | IOCxF0     |  |

| bit 7 bit                               |            |            |                                                       |                                    |            |            |            |  |

|                                         |            |            |                                                       |                                    |            |            |            |  |

| Legend:                                 |            |            |                                                       |                                    |            |            |            |  |

| R = Readable bit W = Writable bit       |            |            | bit                                                   | U = Unimplemented bit, read as '0' |            |            |            |  |

| u = Bit is unchanged x = Bit is unknown |            |            | -n/n = Value at POR and BOR/Value at all other Resets |                                    |            |            |            |  |

| '1' = Bit is set '0' = Bit is cleared   |            |            | HS - Bit is set in hardware                           |                                    |            |            |            |  |

# REGISTER 14-3: IOCxF: INTERRUPT-ON-CHANGE FLAG REGISTER

bit 7-0 IOCxF<7:0>: Interrupt-on-Change Flag bits<sup>(1)</sup>

- 1 = An enabled change was detected on the associated pin.

Set when IOCxPx = 1 and a rising edge was detected RBx, or when IOCxNx = 1 and a falling edge was detected on RBx.

- 0 = No change was detected, or the user cleared the detected change.

Note 1: For IOCEF register, bit 3 (IOCEF3) is the only implemented bit in the register.

| Name   | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------------|

| ANSELB | —      | ANSB6  | ANSB5  | ANSB4  | ANSB3  | ANSB2  | ANSB1  | ANSB0  | 138                 |

| INTCON | GIE    | PEIE   | TMR0IE | INTE   | IOCIE  | TMR0IF | INTF   | IOCIF  | 93                  |

| IOCAF  | IOCAF7 | IOCAF6 | IOCAF5 | IOCAF4 | IOCAF3 | IOCAF2 | IOCAF1 | IOCAF0 | 159                 |

| IOCAN  | IOCAN7 | IOCAN6 | IOCAN5 | IOCAN4 | IOCAN3 | IOCAN2 | IOCAN1 | IOCAN0 | 158                 |

| IOCAP  | IOCAP7 | IOCAP6 | IOCAP5 | IOCAP4 | IOCAP3 | IOCAP2 | IOCAP1 | IOCAP0 | 158                 |

| IOCBF  | IOCBF7 | IOCBF6 | IOCBF5 | IOCBF4 | IOCBF3 | IOCBF2 | IOCBF1 | IOCBF0 | 159                 |

| IOCBN  | IOCBN7 | IOCBN6 | IOCBN5 | IOCBN4 | IOCBN3 | IOCBN2 | IOCBN1 | IOCBN0 | 158                 |

| IOCBP  | IOCBP7 | IOCBP6 | IOCBP5 | IOCBP4 | IOCBP3 | IOCBP2 | IOCBP1 | IOCBP0 | 158                 |

| IOCCF  | IOCCF7 | IOCCF6 | IOCCF5 | IOCCF4 | IOCCF3 | IOCCF2 | IOCCF1 | IOCCF0 | 159                 |

| IOCCN  | IOCCN7 | IOCCN6 | IOCCN5 | IOCCN4 | IOCCN3 | IOCCN2 | IOCCN1 | IOCCN0 | 158                 |

| IOCCP  | IOCCP7 | IOCCP6 | IOCCP5 | IOCCP4 | IOCCP3 | IOCCP2 | IOCCP1 | IOCCP0 | 158                 |

| IOCEF  | _      | _      | _      | _      | IOCEF3 | —      | _      | _      | 159                 |

| IOCEN  |        |        |        |        | IOCEN3 |        |        |        | 158                 |

| IOCEP  | _      | _      | _      | _      | IOCEP3 | _      |        | _      | 158                 |

| TRISB  | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | 137                 |

TABLE 14-1:

SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPT-ON-CHANGE

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by interrupt-on-change.

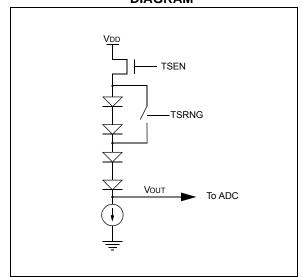

# 16.0 TEMPERATURE INDICATOR MODULE

This family of devices is equipped with a temperature circuit designed to measure the operating temperature of the silicon die. The circuit's range of operating temperature falls between -40°C and +85°C. The output is a voltage that is proportional to the device temperature. The output of the temperature indicator is internally connected to the device ADC.

The circuit may be used as a temperature threshold detector or a more accurate temperature indicator, depending on the level of calibration performed. A one-point calibration allows the circuit to indicate a temperature closely surrounding that point. A two-point calibration allows the circuit to sense the entire range of temperature more accurately. Reference Application Note AN1333, *"Use and Calibration of the Internal Temperature Indicator"* (DS01333) for more details regarding the calibration process.

# 16.1 Circuit Operation

Figure 16-1 shows a simplified block diagram of the temperature circuit. The proportional voltage output is achieved by measuring the forward voltage drop across multiple silicon junctions.

Equation 16-1 describes the output characteristics of the temperature indicator.

# EQUATION 16-1: VOUT RANGES

High Range: VOUT = VDD - 4VT

Low Range: VOUT = VDD - 2VT

The temperature sense circuit is integrated with the Fixed Voltage Reference (FVR) module. See **Section 15.0 "Fixed Voltage Reference (FVR)"** for more information.

The circuit is enabled by setting the TSEN bit of the FVRCON register. When disabled, the circuit draws no current.

The circuit operates in either high or low range. The high range, selected by setting the TSRNG bit of the FVRCON register, provides a wider output voltage. This provides more resolution over the temperature range, but may be less consistent from part to part. This range requires a higher bias voltage to operate and thus, a higher VDD is needed.

The low range is selected by clearing the TSRNG bit of the FVRCON register. The low range generates a lower voltage drop and thus, a lower bias voltage is needed to operate the circuit. The low range is provided for lowvoltage operation.

# FIGURE 16-1: TEMPERATURE CIRCUIT DIAGRAM

# 16.2 Minimum Operating VDD

When the temperature circuit is operated in low range, the device may be operated at any operating voltage that is within specifications.

When the temperature circuit is operated in high range, the device operating voltage, VDD, must be high enough to ensure that the temperature circuit is correctly biased.

Table 16-1 shows the recommended minimum  $\mathsf{V}\mathsf{D}\mathsf{D}$  vs. range setting.

#### TABLE 16-1: RECOMMENDED VDD VS. RANGE

| Min. VDD, TSRNG = 1 | Min. VDD, TSRNG = 0 |  |  |  |  |

|---------------------|---------------------|--|--|--|--|

| 3.6V                | 1.8V                |  |  |  |  |

# 16.3 Temperature Output

The output of the circuit is measured using the internal Analog-to-Digital Converter. A channel is reserved for the temperature circuit output. Refer to **Section 17.0 "Analog-to-Digital Converter (ADC) Module"** for detailed information.

# 16.4 ADC Acquisition Time

To ensure accurate temperature measurements, the user must wait at least 200  $\mu$ s after the ADC input multiplexer is connected to the temperature indicator output before the conversion is performed. In addition, the user must wait 200  $\mu$ s between sequential conversions of the temperature indicator output.

### REGISTER 17-6: ADRESH: ADC RESULT REGISTER HIGH (ADRESH) ADFM = 1

| R/W-x/u                                 | R/W-x/u           | R/W-x/u                                             | R/W-x/u                                               | R/W-x/u                                                                                                      | R/W-x/u                                                                                                                                        | R/W-x/u                                                                                                                                                                      |  |  |

|-----------------------------------------|-------------------|-----------------------------------------------------|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| AD                                      | SIGN              |                                                     |                                                       | AD<                                                                                                          | 11:8>                                                                                                                                          |                                                                                                                                                                              |  |  |

|                                         |                   |                                                     | ·                                                     |                                                                                                              |                                                                                                                                                | bit 0                                                                                                                                                                        |  |  |

|                                         |                   |                                                     |                                                       |                                                                                                              |                                                                                                                                                |                                                                                                                                                                              |  |  |

|                                         |                   |                                                     |                                                       |                                                                                                              |                                                                                                                                                |                                                                                                                                                                              |  |  |

| bit                                     | W = Writable      | bit                                                 | U = Unimplemented bit, read as '0'                    |                                                                                                              |                                                                                                                                                |                                                                                                                                                                              |  |  |

| u = Bit is unchanged x = Bit is unknown |                   |                                                     | -n/n = Value at POR and BOR/Value at all other Resets |                                                                                                              |                                                                                                                                                |                                                                                                                                                                              |  |  |

|                                         | '0' = Bit is clea | ared                                                |                                                       |                                                                                                              |                                                                                                                                                |                                                                                                                                                                              |  |  |

|                                         | AD                | ADSIGN<br>bit W = Writable<br>anged x = Bit is unkr | ADSIGN<br>bit W = Writable bit                        | ADSIGN       bit     W = Writable bit     U = Unimpler       anged     x = Bit is unknown     -n/n = Value a | ADSIGN     AD       bit     W = Writable bit     U = Unimplemented bit, read       anged     x = Bit is unknown     -n/n = Value at POR and BC | ADSIGN     AD<11:8>       bit     W = Writable bit     U = Unimplemented bit, read as '0'       anged     x = Bit is unknown     -n/n = Value at POR and BOR/Value at all of |  |  |

bit 3-0 AD<11:8>: ADC Result Register bits Most Significant 4 bits of 12-bit conversion result

#### **REGISTER 17-7:** ADRESL: ADC RESULT REGISTER LOW (ADRESL) ADFM = 1

| R/W-x/u |  |

|---------|---------|---------|---------|---------|---------|---------|---------|--|

| AD<7:0> |         |         |         |         |         |         |         |  |

| bit 7   |         |         |         |         |         |         | bit 0   |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 AD<7:0>: ADC Result Register bits Least Significant 8 bits of 12-bit conversion result

# 20.11 Register Definitions: Comparator Control

#### **REGISTER 20-1: CMxCON0: COMPARATOR Cx CONTROL REGISTER 0**

| R/W-0/0         | R-0/0                                                                                                                                                        | R/W-0/0                                                                                                                    | R/W-0/0         | R/W-0/0          | R/W-1/1         | R/W-0/0        | R/W-0/0       |  |  |  |  |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-----------------|------------------|-----------------|----------------|---------------|--|--|--|--|

| CxON            | CxOUT                                                                                                                                                        | CxOE                                                                                                                       | CxPOL           | CxZLF            | CxSP            | CxHYS          | CxSYNC        |  |  |  |  |

| bit 7           |                                                                                                                                                              |                                                                                                                            |                 |                  |                 |                | bit 0         |  |  |  |  |

|                 |                                                                                                                                                              |                                                                                                                            |                 |                  |                 |                |               |  |  |  |  |

| Legend:         |                                                                                                                                                              |                                                                                                                            |                 |                  |                 |                |               |  |  |  |  |

| R = Readable    |                                                                                                                                                              | W = Writable                                                                                                               |                 |                  | mented bit, rea |                |               |  |  |  |  |

| u = Bit is und  | -                                                                                                                                                            | x = Bit is unki                                                                                                            |                 | -n/n = Value a   | at POR and BC   | R/Value at all | other Resets  |  |  |  |  |

| '1' = Bit is se | t                                                                                                                                                            | '0' = Bit is cle                                                                                                           | ared            |                  |                 |                |               |  |  |  |  |

| bit 7           | CxON: Com                                                                                                                                                    | parator Enable                                                                                                             | bit             |                  |                 |                |               |  |  |  |  |

|                 | -                                                                                                                                                            | ator is enabled                                                                                                            |                 |                  |                 |                |               |  |  |  |  |

|                 | 0 = Compara                                                                                                                                                  | 0 = Comparator is disabled and consumes no active power                                                                    |                 |                  |                 |                |               |  |  |  |  |

| bit 6           | CxOUT: Con                                                                                                                                                   | nparator Output                                                                                                            | t bit           |                  |                 |                |               |  |  |  |  |

|                 |                                                                                                                                                              | If CxPOL = 1 (inverted polarity):                                                                                          |                 |                  |                 |                |               |  |  |  |  |

|                 | 1 = CxVP < CxVN $0 = CxVP > CxVN$                                                                                                                            |                                                                                                                            |                 |                  |                 |                |               |  |  |  |  |

|                 | If CxPOL = 0 (non-inverted polarity):                                                                                                                        |                                                                                                                            |                 |                  |                 |                |               |  |  |  |  |

|                 | 1 = CxVP > CxVN                                                                                                                                              |                                                                                                                            |                 |                  |                 |                |               |  |  |  |  |

|                 | 0 = CxVP <                                                                                                                                                   | CxVN                                                                                                                       |                 |                  |                 |                |               |  |  |  |  |

| bit 5           | CxOE: Comparator Output Enable bit                                                                                                                           |                                                                                                                            |                 |                  |                 |                |               |  |  |  |  |

|                 | <ol> <li>CXOUT is present on the CXOUT pin. Requires that the associated TRIS bit be cleared to actually<br/>drive the pin. Not affected by CXON.</li> </ol> |                                                                                                                            |                 |                  |                 |                |               |  |  |  |  |

|                 |                                                                                                                                                              | is internal only                                                                                                           |                 |                  |                 |                |               |  |  |  |  |

| bit 4           |                                                                                                                                                              | <b>CxPOL:</b> Comparator Output Polarity Select bit                                                                        |                 |                  |                 |                |               |  |  |  |  |

|                 | 1 = Comparator output is inverted                                                                                                                            |                                                                                                                            |                 |                  |                 |                |               |  |  |  |  |

|                 | 0 = Comparator output is not inverted                                                                                                                        |                                                                                                                            |                 |                  |                 |                |               |  |  |  |  |

| bit 3           | CxZLF: Com                                                                                                                                                   | parator Zero La                                                                                                            | atency Filter E | nable bit        |                 |                |               |  |  |  |  |

|                 | 1 = Comparator output is filtered                                                                                                                            |                                                                                                                            |                 |                  |                 |                |               |  |  |  |  |

|                 | 0 = Comparator output is unfiltered                                                                                                                          |                                                                                                                            |                 |                  |                 |                |               |  |  |  |  |

| bit 2           | CxSP: Comparator Speed/Power Select bit                                                                                                                      |                                                                                                                            |                 |                  |                 |                |               |  |  |  |  |

|                 | <ol> <li>Comparator operates in normal power, higher speed mode</li> <li>Comparator operates in low-power, low-speed mode</li> </ol>                         |                                                                                                                            |                 |                  |                 |                |               |  |  |  |  |

| bit 1           | -                                                                                                                                                            | <b>CxHYS:</b> Comparator Hysteresis Enable bit                                                                             |                 |                  |                 |                |               |  |  |  |  |

|                 |                                                                                                                                                              | 1 = Comparator hysteresis enabled                                                                                          |                 |                  |                 |                |               |  |  |  |  |

|                 | 0 = Compara                                                                                                                                                  | ator hysteresis                                                                                                            | disabled        |                  |                 |                |               |  |  |  |  |

| bit 0           | CxSYNC: Co                                                                                                                                                   | omparator Outp                                                                                                             | ut Synchronou   | is Mode bit      |                 |                |               |  |  |  |  |

|                 |                                                                                                                                                              | ator output to T                                                                                                           |                 |                  |                 | ges on Timer1  | clock source. |  |  |  |  |

|                 |                                                                                                                                                              | Output updated on the falling edge of Timer1 clock source.<br>0 = Comparator output to Timer1 and I/O pin is asynchronous. |                 |                  |                 |                |               |  |  |  |  |

|                 |                                                                                                                                                              |                                                                                                                            |                 | pin is asyncillu | nous.           |                |               |  |  |  |  |

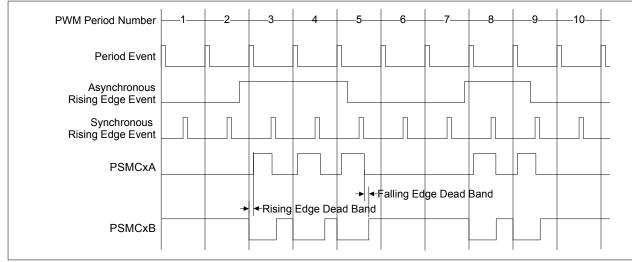

#### 24.3.6 PUSH-PULL PWM WITH FOUR FULL-BRIDGE AND COMPLEMENTARY OUTPUTS

The push-pull PWM is used to drive transistor bridge circuits as well as synchronous switches on the secondary side of the bridge. It uses six outputs and generates PWM signals with dead band that alternate between the six outputs in even and odd cycles.

24.3.6.1 Mode Features and Controls

- Dead-band control is available

- · No steering control available

- Primary PWM is output on the following four pins:

- PSMCxA

- PSMCxB

- PSMCxC

- PSMCxD

- Complementary PWM is output on the following two pins:

- PSMCxE

- PSMCxF

Note: PSMCxA and PSMCxC are identical waveforms, and PSMCxB and PSMCxD are identical waveforms.

# 24.3.6.2 Waveform Generation

Push-pull waveforms generate alternating outputs on two sets of pin. Therefore, there are two sets of rising edge events and two sets of falling edge events

Odd numbered period rising edge event:

- · PSMCxE is set inactive

- Dead-band rising is activated (if enabled)

- PSMCxA and PSMCxC are set active

Odd numbered period falling edge event:

- PSMCxA and PSMCxC are set inactive

- Dead-band falling is activated (if enabled)

- PSMCxE is set active

Even numbered period rising edge event:

- PSMCxF is set inactive

- · Dead-band rising is activated (if enabled)

- PSMCxB and PSMCxD are set active

Even numbered period falling edge event:

- PSMCxB and PSMCxOUT3 are set inactive

- Dead-band falling is activated (if enabled)

- · PSMCxF is set active

#### FIGURE 24-9: PUSH-PULL 4 FULL-BRIDGE AND COMPLEMENTARY PWM

| PWM Period Number  | 1                                                       |

|--------------------|---------------------------------------------------------|

| Period Event       |                                                         |

| Rising Edge Event  |                                                         |

| Falling Edge Event |                                                         |

| →<br>PSMCxA        |                                                         |

| PSMCxC             |                                                         |

| PSMCxE             | ← Falling Edge Dead Band Falling Edge Dead Band      ←  |

| PSMCxB             |                                                         |

| PSMCxD             |                                                         |

| PSMCxF             | → ← Falling Edge Dead Band<br>→ ← Rising Edge Dead Band |

#### 24.3.8 PULSE-SKIPPING PWM WITH COMPLEMENTARY OUTPUTS

The pulse-skipping PWM is used to generate a series of fixed-length pulses that may or not be triggered at each period event. If any of the sources enabled to generate a rising edge event are high when a period event occurs, a pulse will be generated. If the rising edge sources are low at the period event, no pulse will be generated.

The rising edge occurs based upon the value in the PSMCxPH register pair.

The falling edge event always occurs according to the enabled event inputs without qualification between any two inputs.

#### 24.3.8.1 Mode Features

- · Dead-band control is available

- · No steering control available

- · Primary PWM is output on only PSMCxA.

- · Complementary PWM is output on only PSMCxB.

### 24.3.8.2 Waveform Generation

#### Rising Edge Event

If any enabled asynchronous rising edge event = 1 when there is a period event, then upon the next synchronous rising edge event:

- · Complementary output is set inactive

- Dead-band rising is activated (if enabled)

- · Primary output is set active

#### Falling Edge Event

- · Primary output is set inactive

- Dead-band falling is activated (if enabled)

- · Complementary output is set active

Note: To use this mode, an external source must be used for the determination of whether or not to generate the set pulse. If the phase time base is used, it will either always generate a pulse or never generate a pulse based on the PSMCxPH value.

#### FIGURE 24-11: PULSE-SKIPPING WITH COMPLEMENTARY OUTPUT PWM WAVEFORM

# 24.7 Auto-Shutdown

Auto-shutdown is a method to immediately override the PSMC output levels with specific overrides that allow for safe shutdown of the application.

Auto-shutdown includes a mechanism to allow the application to restart under different conditions.

Auto-shutdown is enabled with the PxASDEN bit of the PSMC Auto-shutdown Control (PSMCxASDC) register (Register 24-15). All auto-shutdown features are enabled when PxASDEN is set and disabled when cleared.

#### 24.7.1 SHUTDOWN

There are two ways to generate a shutdown event:

- Manual

- External Input

#### 24.7.1.1 Manual Override

The auto-shutdown control register can be used to manually override the pin functions. Setting the PxASE bit of the PSMC Auto-shutdown Control (PSMCxASDC) register (Register 24-15) generates a software shut-down event.

The auto-shutdown override will persist as long as PxASE remains set.

#### 24.7.1.2 External Input Source

Any of the given sources that are available for event generation are also available for system shut-down. This is so that external circuitry can monitor and force a shutdown without any software overhead. Auto-shutdown sources are selected with the PSMC Auto-shutdown Source (PSMCxASDS) register (Register 24-17).

When any of the selected external auto-shutdown sources go high, the PxASE bit is set and an auto-shutdown interrupt is generated.

Note: The external shutdown sources are level sensitive, not edge sensitive. The shutdown condition will persist as long as the circuit is driving the appropriate logic level.

#### 24.7.2 PIN OVERRIDE LEVELS

The logic levels driven to the output pins during an auto-shutdown event are determined by the PSMC Auto-shutdown Output Level (PSMCxASDL) register (Register 24-16).

#### 24.7.2.1 PIN Override Enable

Setting the PxASDOV bit of the PSMC Auto-shutdown Control (PSMCxASDC) register (Register 24-15) will also force the override levels onto the pins, exactly like what happens when the auto-shutdown is used. However, whereas setting PxASE causes an auto-shutdown interrupt, setting PxASDOV does not generate an interrupt.

#### 24.7.3 RESTART FROM AUTO-SHUTDOWN

After an auto-shutdown event has occurred, there are two ways for the module to resume operation:

- Manual restart

- Automatic restart

The restart method is selected with the PxARSEN bit of the PSMC Auto-shutdown Control (PSMCxASDC) register (Register 24-15).

#### 24.7.3.1 Manual Restart

When PxARSEN is cleared, and once the PxASDE bit is set, it will remain set until cleared by software.

The PSMC will restart on the period event after PxASDE bit is cleared in software.

#### 24.7.3.2 Auto-Restart

When PxARSEN is set, the PxASDE bit will clear automatically when the source causing the Reset and no longer asserts the shut-down condition.

The PSMC will restart on the next period event after the auto-shutdown condition is removed.

Examples of manual and automatic restart are shown in Figure 24-20.

Note: Whether manual or auto-restart is selected, the PxASDE bit cannot be cleared in software when the auto-shutdown condition is still present.

#### REGISTER 24-3: PSMC1SYNC: PSMC1 SYNCHRONIZATION CONTROL REGISTER

| R/W-0/0           | R/W-0/0                                                                                                                                                                                  | R/W-0/0                                              | U-0               | U-0                | U-0                   | R/W-0/0            | R/W-0/0 |  |  |  |  |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|-------------------|--------------------|-----------------------|--------------------|---------|--|--|--|--|

| P1POFST           | P1PRPOL                                                                                                                                                                                  | P1DCPOL                                              | 0-0               | 0-0                | 0-0                   |                    | IC<1:0> |  |  |  |  |

|                   | PIPRPUL                                                                                                                                                                                  | PIDCPOL                                              | —                 | _                  | —                     | PISTN              |         |  |  |  |  |

| bit 7             |                                                                                                                                                                                          |                                                      |                   |                    |                       |                    | bit 0   |  |  |  |  |

| I a man di        |                                                                                                                                                                                          |                                                      |                   |                    |                       |                    |         |  |  |  |  |

| Legend:           |                                                                                                                                                                                          |                                                      |                   |                    |                       |                    |         |  |  |  |  |

| R = Readable bi   | t                                                                                                                                                                                        | W = Writable bit                                     |                   | U = Unimpleme      | ented bit, read as '0 | )'                 |         |  |  |  |  |

| u = Bit is unchar | iged                                                                                                                                                                                     | x = Bit is unknow                                    | wn                | -n/n = Value at    | POR and BOR/Val       | ue at all other Re | esets   |  |  |  |  |

| '1' = Bit is set  |                                                                                                                                                                                          | '0' = Bit is cleare                                  | ed                |                    |                       |                    |         |  |  |  |  |

|                   |                                                                                                                                                                                          |                                                      |                   |                    |                       |                    |         |  |  |  |  |

| bit 7             |                                                                                                                                                                                          | IC1 Phase Offset                                     |                   | set source is svn  | chronous period ev    | /ent               |         |  |  |  |  |

|                   | <ul> <li>1 = sync_out source is phase event and latch set source is synchronous period event</li> <li>0 = sync_out source is period event and latch set source is phase event</li> </ul> |                                                      |                   |                    |                       |                    |         |  |  |  |  |

| bit 6             | P1PRPOL: PSI                                                                                                                                                                             | MC1 Period Polar                                     | itv Event Contro  | ol bit             |                       |                    |         |  |  |  |  |

|                   | 1 = Selected asynchronous period event inputs are inverted                                                                                                                               |                                                      |                   |                    |                       |                    |         |  |  |  |  |

|                   | 0 = Selected                                                                                                                                                                             | asynchronous pe                                      | riod event input  | s are not inverted | t                     |                    |         |  |  |  |  |

| bit 5             | P1DCPOL: PS                                                                                                                                                                              | P1DCPOL: PSMC1 Duty-cycle Event Polarity Control bit |                   |                    |                       |                    |         |  |  |  |  |

|                   | 1 = Selected asynchronous duty-cycle event inputs are inverted                                                                                                                           |                                                      |                   |                    |                       |                    |         |  |  |  |  |

|                   | 0 = Selected                                                                                                                                                                             | asynchronous du                                      | ty-cycle event ir | nputs are not inve | erted                 |                    |         |  |  |  |  |

| bit 4-2           | Unimplemente                                                                                                                                                                             | d: Read as '0'                                       |                   |                    |                       |                    |         |  |  |  |  |

| bit 1-0           |                                                                                                                                                                                          | P1SYNC<1:0>: PSMC1 Period Synchronization Mode bits  |                   |                    |                       |                    |         |  |  |  |  |

|                   |                                                                                                                                                                                          | ,                                                    |                   | () _               | n comes from PSM      | · _ /              |         |  |  |  |  |

|                   |                                                                                                                                                                                          | ed - Do not use                                      | with the PSMC2    | module (sync_ir    | n comes from PSM      | C2 sync_out)       |         |  |  |  |  |

|                   |                                                                                                                                                                                          | is synchronized                                      | with period ever  | at                 |                       |                    |         |  |  |  |  |

|                   |                                                                                                                                                                                          | is synchronized                                      |                   |                    |                       |                    |         |  |  |  |  |

|                   |                                                                                                                                                                                          |                                                      |                   |                    |                       |                    |         |  |  |  |  |

### REGISTER 24-4: PSMC2SYNC: PSMC2 SYNCHRONIZATION CONTROL REGISTER

| R/W-0/0 | R/W-0/0 | R/W-0/0 | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 |

|---------|---------|---------|-----|-----|-----|---------|---------|

| P2POFST | P2PRPOL | P2DCPOL | —   | —   | —   | P2SYN   | C<1:0>  |

| bit 7   |         |         |     |     |     |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7   | <ul> <li>P2POFST: PSMC2 Phase Offset Control bit</li> <li>1 = sync_out source is phase event and latch set source is synchronous period event</li> <li>0 = sync_out source is period event and latch set source is phase event</li> </ul>                                                                                                                           |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | <ul> <li>P2PRPOL: PSMC2 Period Polarity Event Control bit</li> <li>1 = Selected asynchronous period event inputs are inverted</li> <li>0 = Selected asynchronous period event inputs are not inverted</li> </ul>                                                                                                                                                    |

| bit 5   | <ul> <li>P2DCPOL: PSMC2 Duty-cycle Event Polarity Control bit</li> <li>1 = Selected asynchronous duty-cycle event inputs are inverted</li> <li>0 = Selected asynchronous duty-cycle event inputs are not inverted</li> </ul>                                                                                                                                        |

| bit 4-2 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                          |

| bit 1-0 | <ul> <li>P2SYNC&lt;1:0&gt;: PSMC2 Period Synchronization Mode bits</li> <li>11 = PSMC2 is synchronized with the PSMC3 module (sync_in comes from PSMC3 sync_out)</li> <li>10 = Reserved - Do not use</li> <li>01 = PSMC2 is synchronized with the PSMC1 module (sync_in comes from PSMC1 sync_out)</li> <li>00 = PSMC2 is synchronized with period event</li> </ul> |

# 27.6 EUSART Operation During Sleep

The EUSART will remain active during Sleep only in the Synchronous Slave mode. All other modes require the system clock and therefore cannot generate the necessary signals to run the Transmit or Receive Shift registers during Sleep.

Synchronous Slave mode uses an externally generated clock to run the Transmit and Receive Shift registers.

# 27.6.1 SYNCHRONOUS RECEIVE DURING SLEEP

To receive during Sleep, all the following conditions must be met before entering Sleep mode:

- RCSTA and TXSTA Control registers must be configured for Synchronous Slave Reception (see Section 27.5.2.4 "Synchronous Slave Reception Set-up:").

- If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- The RCIF interrupt flag must be cleared by reading RCREG to unload any pending characters in the receive buffer.

Upon entering Sleep mode, the device will be ready to accept data and clocks on the RX/DT and TX/CK pins, respectively. When the data word has been completely clocked in by the external device, the RCIF interrupt flag bit of the PIR1 register will be set. Thereby, waking the processor from Sleep.

Upon waking from Sleep, the instruction following the SLEEP instruction will be executed. If the Global Interrupt Enable (GIE) bit of the INTCON register is also set, then the Interrupt Service Routine at address 004h will be called.