Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PSMC, PWM, WDT                                 |

| Number of I/O              | 35                                                                          |

| Program Memory Size        | 7KB (4K x 14)                                                               |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 512 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 14x12b; D/A 1x8b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-TQFP                                                                     |

| Supplier Device Package    | 44-TQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1784t-i-pt |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 6.0 OSCILLATOR MODULE (WITH FAIL-SAFE CLOCK MONITOR)

#### 6.1 Overview

The oscillator module has a wide variety of clock sources and selection features that allow it to be used in a wide range of applications while maximizing performance and minimizing power consumption. Figure 6-1 illustrates a block diagram of the oscillator module.

Clock sources can be supplied from external oscillators, quartz crystal resonators, ceramic resonators and Resistor-Capacitor (RC) circuits. In addition, the system clock source can be supplied from one of two internal oscillators and PLL circuits, with a choice of speeds selectable via software. Additional clock features include:

- Selectable system clock source between external or internal sources via software.

- Two-Speed Start-up mode, which minimizes latency between external oscillator start-up and code execution.

- Fail-Safe Clock Monitor (FSCM) designed to detect a failure of the external clock source (LP, XT, HS, EC or RC modes) and switch automatically to the internal oscillator.

- Oscillator Start-up Timer (OST) ensures stability of crystal oscillator sources

The oscillator module can be configured in one of eight clock modes.

- 1. ECL External Clock Low-Power mode (0 MHz to 0.5 MHz)

- 2. ECM External Clock Medium-Power mode (0.5 MHz to 4 MHz)

- 3. ECH External Clock High-Power mode (4 MHz to 32 MHz)

- 4. LP 32 kHz Low-Power Crystal mode.

- 5. XT Medium Gain Crystal or Ceramic Resonator Oscillator mode (up to 4 MHz)

- 6. HS High Gain Crystal or Ceramic Resonator mode (4 MHz to 20 MHz)

- 7. RC External Resistor-Capacitor (RC).

- 8. INTOSC Internal oscillator (31 kHz to 32 MHz).

Clock Source modes are selected by the FOSC<2:0> bits in the Configuration Words. The FOSC bits determine the type of oscillator that will be used when the device is first powered.

The EC clock mode relies on an external logic level signal as the device clock source. The LP, XT, and HS clock modes require an external crystal or resonator to be connected to the device. Each mode is optimized for a different frequency range. The RC clock mode requires an external resistor and capacitor to set the oscillator frequency.

The INTOSC internal oscillator block produces low, medium, and high-frequency clock sources, designated LFINTOSC, MFINTOSC and HFINTOSC. (see Internal Oscillator Block, Figure 6-1). A wide selection of device clock frequencies may be derived from these three clock sources.

#### 6.2.2.7 Internal Oscillator Clock Switch Timing

When switching between the HFINTOSC, MFINTOSC and the LFINTOSC, the new oscillator may already be shut down to save power (see Figure 6-7). If this is the case, there is a delay after the IRCF<3:0> bits of the OSCCON register are modified before the frequency selection takes place. The OSCSTAT register will reflect the current active status of the HFINTOSC, MFINTOSC and LFINTOSC oscillators. The sequence of a frequency selection is as follows:

- 1. IRCF<3:0> bits of the OSCCON register are modified.

- 2. If the new clock is shut down, a clock start-up delay is started.

- 3. Clock switch circuitry waits for a falling edge of the current clock.

- 4. The current clock is held low and the clock switch circuitry waits for a rising edge in the new clock.

- 5. The new clock is now active.

- 6. The OSCSTAT register is updated as required.

- 7. Clock switch is complete.

See Figure 6-7 for more details.

If the internal oscillator speed is switched between two clocks of the same source, there is no start-up delay before the new frequency is selected. Clock switching time delays are shown in Table 6-1.

Start-up delay specifications are located in the oscillator tables of **Section 30.0** "**Electrical Specifications**".

| R-1/q            | R-0/q      | R-q/q                                                                               | R-0/q           | R-0/q            | R-q/q            | R-0/0          | R-0/q        |  |  |  |  |  |

|------------------|------------|-------------------------------------------------------------------------------------|-----------------|------------------|------------------|----------------|--------------|--|--|--|--|--|

| T10SCR           | PLLR       | OSTS                                                                                | HFIOFR          | HFIOFL           | MFIOFR           | LFIOFR         | HFIOFS       |  |  |  |  |  |

| bit 7            | ·          |                                                                                     |                 |                  |                  |                | bit 0        |  |  |  |  |  |

|                  |            |                                                                                     |                 |                  |                  |                |              |  |  |  |  |  |

| Legend:          |            |                                                                                     |                 |                  |                  |                |              |  |  |  |  |  |

| R = Readable     | e bit      | W = Writable                                                                        | bit             | U = Unimpler     | mented bit, read | d as '0'       |              |  |  |  |  |  |

| u = Bit is unc   | hanged     | x = Bit is unk                                                                      | nown            | -n/n = Value a   | at POR and BC    | R/Value at all | other Resets |  |  |  |  |  |

| '1' = Bit is set | t          | '0' = Bit is cle                                                                    | ared            | q = Condition    | nal              |                |              |  |  |  |  |  |

|                  |            |                                                                                     |                 |                  |                  |                |              |  |  |  |  |  |

| bit 7            |            | imer1 Oscillator                                                                    | Ready bit       |                  |                  |                |              |  |  |  |  |  |

|                  | If TIOSCEN |                                                                                     |                 |                  |                  |                |              |  |  |  |  |  |

|                  |            | oscillator is rea<br>oscillator is not                                              |                 |                  |                  |                |              |  |  |  |  |  |

|                  | If T10SCEN |                                                                                     | Teauy           |                  |                  |                |              |  |  |  |  |  |

|                  |            | 1 = Timer1 clock source is always ready                                             |                 |                  |                  |                |              |  |  |  |  |  |

| bit 6            | PLLR 4x PL |                                                                                     | , ,             |                  |                  |                |              |  |  |  |  |  |

|                  |            | 1 = 4x PLL is ready                                                                 |                 |                  |                  |                |              |  |  |  |  |  |

|                  | 0 = 4x PLL | is not ready                                                                        |                 |                  |                  |                |              |  |  |  |  |  |

| bit 5            | OSTS: Osci | llator Start-up T                                                                   | imer Status bit |                  |                  |                |              |  |  |  |  |  |

|                  |            | 1 = Running from the clock defined by the FOSC<2:0> bits of the Configuration Words |                 |                  |                  |                |              |  |  |  |  |  |

|                  |            | ig from an interr                                                                   |                 |                  | 00)              |                |              |  |  |  |  |  |

| bit 4            |            | HFIOFR: High-Frequency Internal Oscillator Ready bit                                |                 |                  |                  |                |              |  |  |  |  |  |

|                  |            | 1 = HFINTOSC is ready                                                               |                 |                  |                  |                |              |  |  |  |  |  |

|                  |            | DSC is not ready                                                                    |                 |                  |                  |                |              |  |  |  |  |  |

| bit 3            |            | gh-Frequency Ir                                                                     |                 | or Locked bit    |                  |                |              |  |  |  |  |  |

|                  |            | 1 = HFINTOSC is at least 2% accurate<br>0 = HFINTOSC is not 2% accurate             |                 |                  |                  |                |              |  |  |  |  |  |

| hit 0            |            |                                                                                     |                 | villator Doody b | :+               |                |              |  |  |  |  |  |

| bit 2            |            | edium-Frequen                                                                       | cy internal Osc | mator Ready D    | iit.             |                |              |  |  |  |  |  |

|                  |            | 1 = MFINTOSC is ready<br>0 = MFINTOSC is not ready                                  |                 |                  |                  |                |              |  |  |  |  |  |

| bit 1            |            | w-Frequency In                                                                      | •               | or Ready bit     |                  |                |              |  |  |  |  |  |

|                  |            | SC is ready                                                                         |                 | in ready bit     |                  |                |              |  |  |  |  |  |

|                  |            | SC is not ready                                                                     | /               |                  |                  |                |              |  |  |  |  |  |

| bit 0            |            | gh-Frequency Ir                                                                     |                 | or Stable bit    |                  |                |              |  |  |  |  |  |

|                  |            | DSC is at least 0                                                                   |                 |                  |                  |                |              |  |  |  |  |  |

|                  |            |                                                                                     |                 |                  |                  |                |              |  |  |  |  |  |

#### REGISTER 6-2: OSCSTAT: OSCILLATOR STATUS REGISTER

| U-0            | U-0           | R/W-0/0                                                                    | R/W-0/0 | R/W-0/0        | R/W-0/0          | R/W-0/0        | R/W-0/0      |  |  |  |  |

|----------------|---------------|----------------------------------------------------------------------------|---------|----------------|------------------|----------------|--------------|--|--|--|--|

|                | _             |                                                                            |         | TUN            | <5:0>            |                |              |  |  |  |  |

| bit 7          |               |                                                                            |         |                |                  |                | bit 0        |  |  |  |  |

|                |               |                                                                            |         |                |                  |                |              |  |  |  |  |

| Legend:        |               |                                                                            |         |                |                  |                |              |  |  |  |  |

| R = Reada      | ble bit       | W = Writable                                                               | bit     | U = Unimpler   | nented bit, read | d as '0'       |              |  |  |  |  |

| u = Bit is ur  | nchanged      | x = Bit is unkr                                                            | nown    | -n/n = Value a | at POR and BC    | R/Value at all | other Resets |  |  |  |  |

| '1' = Bit is s | set           | '0' = Bit is cle                                                           | ared    |                |                  |                |              |  |  |  |  |

|                |               |                                                                            |         |                |                  |                |              |  |  |  |  |

| bit 7-6        | Unimpleme     | ented: Read as '                                                           | 0'      |                |                  |                |              |  |  |  |  |

| bit 5-0        | TUN<5:0>:     | Frequency Tunii                                                            | ng bits |                |                  |                |              |  |  |  |  |

|                | 100000 =      | Minimum freque                                                             | ncy     |                |                  |                |              |  |  |  |  |

|                | •             |                                                                            |         |                |                  |                |              |  |  |  |  |

|                | •             |                                                                            |         |                |                  |                |              |  |  |  |  |

|                | •<br>111111 = |                                                                            |         |                |                  |                |              |  |  |  |  |

|                |               | 000000 = Oscillator module is running at the factory-calibrated frequency. |         |                |                  |                |              |  |  |  |  |

|                | 000001 =      |                                                                            | 5       | , <b>,</b>     |                  | - 5            |              |  |  |  |  |

|                | •             |                                                                            |         |                |                  |                |              |  |  |  |  |

|                | •             |                                                                            |         |                |                  |                |              |  |  |  |  |

|                | •             |                                                                            |         |                |                  |                |              |  |  |  |  |

|                | 011110 =      | Maximum freque                                                             | ncv     |                |                  |                |              |  |  |  |  |

|                | 011111 -      | maximum neque                                                              | incy    |                |                  |                |              |  |  |  |  |

#### REGISTER 6-3: OSCTUNE: OSCILLATOR TUNING REGISTER

| Name    | Bit 7  | Bit 6  | Bit 5 | Bit 4     | Bit 3   | Bit 2         | Bit 1  | Bit 0  | Register<br>on Page |

|---------|--------|--------|-------|-----------|---------|---------------|--------|--------|---------------------|

| OSCCON  | SPLLEN |        | IRCF  | IRCF<3:0> |         |               | SCS    | 82     |                     |

| OSCSTAT | T1OSCR | PLLR   | OSTS  | HFIOFR    | HFIOFL  | MFIOFR        | LFIOFR | HFIOFS | 83                  |

| OSCTUNE | _      | _      |       |           | TUN     | <5:0>         |        |        | 84                  |

| PIE2    | OSFIE  | C2IE   | C1IE  | EEIE      | BCL1IE  | C4IE          | C3IE   | CCP2IE | 95                  |

| PIR2    | OSFIF  | C2IF   | C1IF  | EEIF      | BCL1IF  | C4IF          | C3IF   | CCP2IF | 99                  |

| T1CON   | TMR1C  | S<1:0> | T1CKP | S<1:0>    | T10SCEN | <b>T1SYNC</b> |        | TMR10N | 207                 |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by clock sources.

#### TABLE 6-3: SUMMARY OF CONFIGURATION WORD WITH CLOCK SOURCES

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2   | Bit 9/1   | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|----------|----------|------------|-----------|---------|---------------------|

| CONFIG1 | 13:8 | _       | —       | FCMEN    | IESO     | CLKOUTEN | BOREN<1:0> |           | CPD     | 54                  |

| CONFIGT | 7:0  | CP      | MCLRE   | PWRTE    | WDTE     | E<1:0>   |            | FOSC<2:0> |         | 54                  |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by clock sources.

Note 1: PIC16F1784/6/7 only.

### 11.6 Register Definitions: Watchdog Control

#### REGISTER 11-1: WDTCON: WATCHDOG TIMER CONTROL REGISTER

| U-0              | U-0                  | R/W-0/0                                                                                                                   | R/W-1/1        | R/W-0/0         | R/W-1/1          | R/W-1/1         | R/W-0/0      |  |  |  |  |  |  |

|------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------|----------------|-----------------|------------------|-----------------|--------------|--|--|--|--|--|--|

| _                | —                    |                                                                                                                           |                | WDTPS<4:02      | >                |                 | SWDTEN       |  |  |  |  |  |  |

| bit 7            |                      |                                                                                                                           |                |                 |                  |                 | bit C        |  |  |  |  |  |  |

|                  |                      |                                                                                                                           |                |                 |                  |                 |              |  |  |  |  |  |  |

| Legend:          |                      |                                                                                                                           |                |                 |                  |                 |              |  |  |  |  |  |  |

| R = Readable     |                      | W = Writable                                                                                                              | bit            | •               | mented bit, read |                 |              |  |  |  |  |  |  |

| u = Bit is unc   | hanged               | x = Bit is unkı                                                                                                           | nown           | -m/n = Value    | at POR and BC    | OR/Value at all | other Resets |  |  |  |  |  |  |

| '1' = Bit is set | t                    | '0' = Bit is cle                                                                                                          | ared           |                 |                  |                 |              |  |  |  |  |  |  |

| bit 7-6          | Unimpleme            | nted: Read as '                                                                                                           | 0'             |                 |                  |                 |              |  |  |  |  |  |  |

| bit 5-1          | -                    |                                                                                                                           |                | elect bits(1)   |                  |                 |              |  |  |  |  |  |  |

|                  |                      | WDTPS<4:0>: Watchdog Timer Period Select bits <sup>(1)</sup><br>Bit Value = Prescale Rate                                 |                |                 |                  |                 |              |  |  |  |  |  |  |

|                  |                      | eserved. Result                                                                                                           | s in minimum   | interval (1:32) |                  |                 |              |  |  |  |  |  |  |

|                  | •                    |                                                                                                                           |                | (1.02)          |                  |                 |              |  |  |  |  |  |  |

|                  | •                    |                                                                                                                           |                |                 |                  |                 |              |  |  |  |  |  |  |

|                  | • _                  | •                                                                                                                         |                |                 |                  |                 |              |  |  |  |  |  |  |

|                  | 10011 = R            | 10011 = Reserved. Results in minimum interval (1:32)                                                                      |                |                 |                  |                 |              |  |  |  |  |  |  |

|                  | 10010 = <b>1</b> :   | .8388608 (2 <sup>23</sup> ) (                                                                                             | Interval 256s  | nominal)        |                  |                 |              |  |  |  |  |  |  |

|                  |                      | $10001 = 1.4194304 (2^{22})$ (Interval 128s nominal)                                                                      |                |                 |                  |                 |              |  |  |  |  |  |  |

|                  | 10000 = 1:           | $10000 = 1:2097152 (2^{21}) (Interval 64s nominal)$                                                                       |                |                 |                  |                 |              |  |  |  |  |  |  |

|                  | 01111 = 1:           | 01111 = 1:1048576 (2 <sup>20</sup> ) (Interval 32s nominal)<br>01110 = 1:524288 (2 <sup>19</sup> ) (Interval 16s nominal) |                |                 |                  |                 |              |  |  |  |  |  |  |

|                  | 01110 = 1:           | 1110 = 1:524288 (2 <sup>19</sup> ) (Interval 16s nominal)<br>1101 = 1:262144 (2 <sup>18</sup> ) (Interval 8s nominal)     |                |                 |                  |                 |              |  |  |  |  |  |  |

|                  |                      |                                                                                                                           |                |                 |                  |                 |              |  |  |  |  |  |  |

|                  |                      | = 1:131072 (2 <sup>17</sup> ) (Interval 4s nominal)<br>= 1:65536 (Interval 2s nominal) (Reset value)                      |                |                 |                  |                 |              |  |  |  |  |  |  |

|                  |                      | 32768 (Interval                                                                                                           |                |                 |                  |                 |              |  |  |  |  |  |  |

|                  |                      | 16384 (Interval                                                                                                           |                | nal)            |                  |                 |              |  |  |  |  |  |  |

|                  |                      | 01000 = 1.8192 (Interval 256 ms nominal)                                                                                  |                |                 |                  |                 |              |  |  |  |  |  |  |

|                  |                      | 00111 = 1:4096 (Interval 128 ms nominal)                                                                                  |                |                 |                  |                 |              |  |  |  |  |  |  |

|                  |                      | 00110 = 1:2048 (Interval 64 ms nominal)<br>00101 = 1:1024 (Interval 32 ms nominal)                                        |                |                 |                  |                 |              |  |  |  |  |  |  |

|                  |                      | 512 (Interval 16                                                                                                          |                | )               |                  |                 |              |  |  |  |  |  |  |

|                  |                      | :256 (Interval 8 r                                                                                                        | ,              |                 |                  |                 |              |  |  |  |  |  |  |

|                  |                      | 128 (Interval 4 r                                                                                                         | ,              |                 |                  |                 |              |  |  |  |  |  |  |

|                  | 00001 = <b>1</b> :   | 64 (Interval 2 m                                                                                                          | s nominal)     |                 |                  |                 |              |  |  |  |  |  |  |

|                  | 00000 = 1:           | 00000 = 1:32 (Interval 1 ms nominal)                                                                                      |                |                 |                  |                 |              |  |  |  |  |  |  |

| bit 0            | SWDTEN: S            | Software Enable                                                                                                           | /Disable for W | /atchdog Timer  | bit              |                 |              |  |  |  |  |  |  |

|                  | <u>If WDTE&lt;1:</u> | 0> = 1x:                                                                                                                  |                |                 |                  |                 |              |  |  |  |  |  |  |

|                  | This bit is ig       |                                                                                                                           |                |                 |                  |                 |              |  |  |  |  |  |  |

|                  | If WDTE<1:           |                                                                                                                           |                |                 |                  |                 |              |  |  |  |  |  |  |

|                  | 1 = WDT is           |                                                                                                                           |                |                 |                  |                 |              |  |  |  |  |  |  |

|                  | 0 = WDT is           |                                                                                                                           |                |                 |                  |                 |              |  |  |  |  |  |  |

|                  | If WDTE<1:0          | 0 > = 0 0                                                                                                                 |                |                 |                  |                 |              |  |  |  |  |  |  |

Note 1: Times are approximate. WDT time is based on 31 kHz LFINTOSC.

| Name       | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|------------|---------|---------|---------|---------|---------|---------|---------|---------|---------------------|

| ANSELA     | ANSA7   | _       | ANSA5   | ANSA4   | ANSA3   | ANSA2   | ANSA1   | ANSA0   | 132                 |

| INLVLA     | INLVLA7 | INLVLA6 | INLVLA5 | INLVLA4 | INLVLA3 | INLVLA2 | INLVLA1 | INLVLA0 | 133                 |

| LATA       | LATA7   | LATA6   | LATA5   | LATA4   | LATA3   | LATA2   | LATA1   | LATA0   | 131                 |

| ODCONA     | ODA7    | ODA6    | ODA5    | ODA4    | ODA3    | ODA2    | ODA1    | ODA0    | 133                 |

| OPTION_REG | WPUEN   | INTEDG  | TMR0CS  | TMR0SE  | PSA     |         | PS<2:0> |         | 198                 |

| PORTA      | RA7     | RA6     | RA5     | RA4     | RA3     | RA2     | RA1     | RA0     | 131                 |

| SLRCONA    | SLRA7   | SLRA6   | SLRA5   | SLRA4   | SLRA3   | SLRA2   | SLRA1   | SLRA0   | 133                 |

| TRISA      | TRISA7  | TRISA6  | TRISA5  | TRISA4  | TRISA3  | TRISA2  | TRISA1  | TRISA0  | 131                 |

| WPUA       | WPUA7   | WPUA6   | WPUA5   | WPUA4   | WPUA3   | WPUA2   | WPUA1   | WPUA0   | 132                 |

#### TABLE 13-3: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

#### TABLE 13-4: SUMMARY OF CONFIGURATION WORD WITH PORTA

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2   | Bit 9/1   | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|----------|----------|------------|-----------|---------|---------------------|

|         | 13:8 |         | —       | FCMEN    | IESO     | CLKOUTEN | BOREN<1:0> |           | CPD     | 54                  |

| CONFIG1 | 7:0  | CP      | MCLRE   | PWRTE    | WDTE     | E<1:0>   |            | FOSC<2:0> |         | 54                  |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by PORTA.

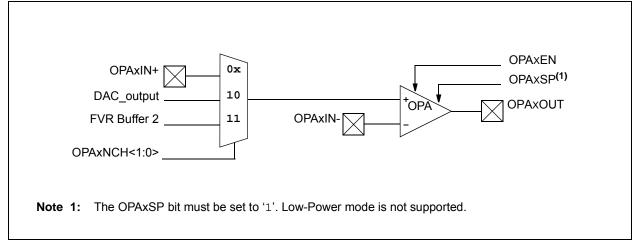

#### 18.0 OPERATIONAL AMPLIFIER (OPA) MODULES

The Operational Amplifier (OPA) is a standard three-terminal device requiring external feedback to operate. The OPA module has the following features:

- External connections to I/O ports

- · Low leakage inputs

- Factory Calibrated Input Offset Voltage

#### FIGURE 18-1: OPAx MODULE BLOCK DIAGRAM

#### 22.3 Timer1 Prescaler

Timer1 has four prescaler options allowing 1, 2, 4 or 8 divisions of the clock input. The T1CKPS bits of the T1CON register control the prescale counter. The prescale counter is not directly readable or writable; however, the prescaler counter is cleared upon a write to TMR1H or TMR1L.

#### 22.4 Timer1 Oscillator

A dedicated low-power 32.768 kHz oscillator circuit is built-in between pins T1OSI (input) and T1OSO (amplifier output). This internal circuit is to be used in conjunction with an external 32.768 kHz crystal.

The oscillator circuit is enabled by setting the T1OS-CEN bit of the T1CON register. The oscillator will continue to run during Sleep.

Note: The oscillator requires a start-up and stabilization time before use. Thus, T1OSCEN should be set and a suitable delay observed prior to using Timer1. A suitable delay similar to the OST delay can be implemented in software by clearing the TMR1IF bit then presetting the TMR1H:TMR1L register pair to FC00h. The TMR1IF flag will be set when 1024 clock cycles have elapsed, thereby indicating that the oscillator is running and reasonably stable.

#### 22.5 Timer1 Operation in Asynchronous Counter Mode

If the control bit T1SYNC of the T1CON register is set, the external clock input is not synchronized. The timer increments asynchronously to the internal phase clocks. If the external clock source is selected then the timer will continue to run during Sleep and can generate an interrupt on overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (see Section 22.5.1 "Reading and Writing Timer1 in Asynchronous Counter Mode").

| Note: | When switching from synchronous to        |

|-------|-------------------------------------------|

|       | asynchronous operation, it is possible to |

|       | skip an increment. When switching from    |

|       | asynchronous to synchronous operation,    |

|       | it is possible to produce an additional   |

|       | increment.                                |

#### 22.5.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running from an external asynchronous clock will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the TMR1H:TMR1L register pair.

### 22.6 Timer1 Gate

Timer1 can be configured to count freely or the count can be enabled and disabled using Timer1 gate circuitry. This is also referred to as Timer1 Gate Enable.

Timer1 gate can also be driven by multiple selectable sources.

#### 22.6.1 TIMER1 GATE ENABLE

The Timer1 Gate Enable mode is enabled by setting the TMR1GE bit of the T1GCON register. The polarity of the Timer1 Gate Enable mode is configured using the T1GPOL bit of the T1GCON register.

When Timer1 Gate Enable mode is enabled, Timer1 will increment on the rising edge of the Timer1 clock source. When Timer1 Gate Enable mode is disabled, no incrementing will occur and Timer1 will hold the current count. See Figure 22-3 for timing details.

TABLE 22-3: TIMER1 GATE ENABLE SELECTIONS

| T1CLK      | T1GPOL | T1G | Timer1 Operation |  |  |

|------------|--------|-----|------------------|--|--|

| $\uparrow$ | 0      | 0   | Counts           |  |  |

| $\uparrow$ | 0      | 1   | Holds Count      |  |  |

| 1          | 1      | 0   | Holds Count      |  |  |

| 1          | 1      | 1   | Counts           |  |  |

### 22.11 Register Definitions: Timer1 Control

Т

bit 1

bit 0

#### REGISTER 22-1: T1CON: TIMER1 CONTROL REGISTER

Unimplemented: Read as '0'

0 = Stops Timer1 and clears Timer1 gate flip-flop

**TMR1ON:** Timer1 On bit 1 = Enables Timer1

| R/W-0/u          | R/W-0/u                                                                                                                                          | R/W-0/u                                                                                                                                                                                                                      | R/W-0/u                                        | R/W-0/u                         | R/W-0/u          | U-0            | R/W-0/u        |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|---------------------------------|------------------|----------------|----------------|--|

| TMR1             | CS<1:0>                                                                                                                                          | T1CKP                                                                                                                                                                                                                        | S<1:0>                                         | T1OSCEN                         | T1SYNC           | _              | TMR10N         |  |

| bit 7            |                                                                                                                                                  |                                                                                                                                                                                                                              |                                                |                                 |                  |                | bit 0          |  |

| Legend:          |                                                                                                                                                  |                                                                                                                                                                                                                              |                                                |                                 |                  |                |                |  |

| R = Readable bit |                                                                                                                                                  | W = Writable                                                                                                                                                                                                                 | oit                                            | U = Unimplen                    | nented bit, read | l as '0'       |                |  |

| u = Bit is unc   | hanged                                                                                                                                           | x = Bit is unkn                                                                                                                                                                                                              | own                                            | -n/n = Value a                  | at POR and BO    | R/Value at all | l other Resets |  |

| '1' = Bit is se  | t                                                                                                                                                | '0' = Bit is clea                                                                                                                                                                                                            | ared                                           |                                 |                  |                |                |  |

| bit 7-6          |                                                                                                                                                  | <b>0&gt;:</b> Timer1 Cloc<br>ed, do not use.                                                                                                                                                                                 | k Source Sele                                  | ect bits                        |                  |                |                |  |

|                  | <u>If T10S0</u><br>External<br><u>If T10S0</u><br>Crystal c<br>01 = Timer1                                                                       | clock source is<br><u>CEN = 0</u> :<br>clock from T10<br><u>CEN = 1</u> :<br>poscillator on T10<br>clock source is<br>clock source is                                                                                        | CKI pin (on the<br>OSI/T1OSO p<br>system clock | e rising edge)<br>ins<br>(Fosc) |                  |                |                |  |

| bit 5-4          | 11 = 1:8 Pres<br>10 = 1:4 Pres<br>01 = 1:2 Pres                                                                                                  | <pre>00 = Timer1 clock source is instruction clock (Fosc/4) T1CKPS&lt;1:0&gt;: Timer1 Input Clock Prescale Select bits 11 = 1:8 Prescale value 10 = 1:4 Prescale value 01 = 1:2 Prescale value 00 = 1:1 Prescale value</pre> |                                                |                                 |                  |                |                |  |

| bit 3            | T1OSCEN: LP Oscillator Enable Control bit<br>1 = Dedicated Timer1 oscillator circuit enabled<br>0 = Dedicated Timer1 oscillator circuit disabled |                                                                                                                                                                                                                              |                                                |                                 |                  |                |                |  |

| bit 2            | 1 = Do not s                                                                                                                                     | ner1 Synchroniz<br>ynchronize asyn<br>nize asynchron                                                                                                                                                                         | nchronous clo                                  | ck input                        | lock (Fosc)      |                |                |  |

#### 24.3.6 PUSH-PULL PWM WITH FOUR FULL-BRIDGE AND COMPLEMENTARY OUTPUTS

The push-pull PWM is used to drive transistor bridge circuits as well as synchronous switches on the secondary side of the bridge. It uses six outputs and generates PWM signals with dead band that alternate between the six outputs in even and odd cycles.

24.3.6.1 Mode Features and Controls

- Dead-band control is available

- · No steering control available

- Primary PWM is output on the following four pins:

- PSMCxA

- PSMCxB

- PSMCxC

- PSMCxD

- Complementary PWM is output on the following two pins:

- PSMCxE

- PSMCxF

Note: PSMCxA and PSMCxC are identical waveforms, and PSMCxB and PSMCxD are identical waveforms.

#### 24.3.6.2 Waveform Generation

Push-pull waveforms generate alternating outputs on two sets of pin. Therefore, there are two sets of rising edge events and two sets of falling edge events

Odd numbered period rising edge event:

- · PSMCxE is set inactive

- Dead-band rising is activated (if enabled)

- PSMCxA and PSMCxC are set active

Odd numbered period falling edge event:

- PSMCxA and PSMCxC are set inactive

- Dead-band falling is activated (if enabled)

- PSMCxE is set active

Even numbered period rising edge event:

- PSMCxF is set inactive

- · Dead-band rising is activated (if enabled)

- PSMCxB and PSMCxD are set active

Even numbered period falling edge event:

- PSMCxB and PSMCxOUT3 are set inactive

- Dead-band falling is activated (if enabled)

- · PSMCxF is set active

#### FIGURE 24-9: PUSH-PULL 4 FULL-BRIDGE AND COMPLEMENTARY PWM

| PWM Period Number  | 1                            | 2                                           | 3               |

|--------------------|------------------------------|---------------------------------------------|-----------------|

| Period Event       |                              |                                             |                 |

| Rising Edge Event  |                              |                                             |                 |

| Falling Edge Event |                              |                                             |                 |

| →<br>PSMCxA        |                              |                                             |                 |

| PSMCxC             |                              |                                             |                 |

| PSMCxE             | → <del>&lt;</del> Falling Ed | ge Dead Band Falling Ed                     | ge Dead Band∔ ← |

| PSMCxB             |                              |                                             |                 |

| PSMCxD             |                              |                                             |                 |

| PSMCxF             | -                            | -► - Falling Edg<br>- Rising Edge Dead Band | e Dead Band     |

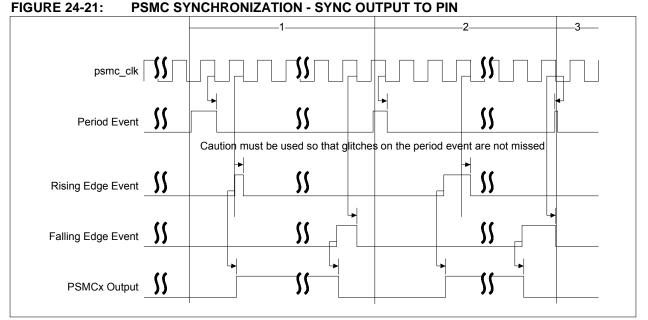

#### 24.8 **PSMC** Synchronization

It is possible to synchronize the periods of two or more PSMC modules together, provided that all modules are on the same device.

Synchronization is achieved by sending a sync signal from the master PSMC module to the desired slave modules. This sync signal generates a period event in each slave module, thereby aligning all slaves with the master. This is useful when an application requires different PWM signal generation from each module but the waveforms must be consistent within a PWM period.

#### 24.8.1 SYNCHRONIZATION SOURCES

The synchronization source can be any PSMC module on the same device. For example, in a device with two PSMC modules, the possible sources for each device is as shown below:

- Sources for PSMC1

- PSMC2

- Sources for PSMC2

PSMC1

## 24.8.1.1 PSMC Internal Connections

The sync signal from the master PSMC module is essentially that modules period event trigger. The slave PSMC modules reset their PSMCxTMR with the sync signal instead of their own period event.

Enabling a module as a slave recipient is done with the PxSYNC bits of the PSMC Synchronization Control (PSMCxSYNC) registers; registers 24-3 and 24-4.

#### 24.8.1.2 Phase Offset Synchronization

The synchronization output signal from the PSMC module is selectable. The sync\_out source may be either:

- Period Event

- Rising Event

Source selection is made with the PxPOFST bit of the PSMCxSYNC registers, registers 24-3, 24-4 and 24-6.

When the PxPOFST bit is set, the sync\_out signal comes from the rising event and the period event replaces the rising event as the start of the active drive period. When PxPOFST is set, duty cycles of up to 100% are achievable in both the slave and master.

When PXPOFST is clear, the sync\_out signal comes from the period event. When PxPOFST is clear, rising events that start after the period event remove the equivalent start delay percentage from the maximum 100% duty cycle.

#### 24.8.1.3 Synchronization Skid

When the sync\_out source is the Period Event, the slave synchronous rising and falling events will lag by one psmc\_clk period. When the sync\_out source is the Rising Event, the synchronous events will lag by two clock periods. To compensate for this, the values in PHH:PHL and DCH:DCL registers can be reduced by the number of lag cycles.

#### REGISTER 24-18: PSMCxTMRL: PSMC TIME BASE COUNTER LOW REGISTER

| R/W-0/0          | R/W-0/0 | R/W-0/0           | R/W-0/0 | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0     |

|------------------|---------|-------------------|---------|----------------|------------------|------------------|-------------|

|                  |         |                   | PSMCxT  | MRL<7:0>       |                  |                  |             |

| bit 7            |         |                   |         |                |                  |                  | bit 0       |

|                  |         |                   |         |                |                  |                  |             |

| Legend:          |         |                   |         |                |                  |                  |             |

| R = Readable     | bit     | W = Writable      | bit     | U = Unimpler   | nented bit, read | l as '0'         |             |

| u = Bit is unch  | anged   | x = Bit is unkr   | nown    | -n/n = Value a | at POR and BO    | R/Value at all c | ther Resets |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                |                  |                  |             |

bit 7-0 **PSMCxTMRL<7:0>:** 16-bit PSMCx Time Base Counter Least Significant bits = PSMCxTMR<7:0>

#### REGISTER 24-19: PSMCxTMRH: PSMC TIME BASE COUNTER HIGH REGISTER

| R/W-0/0          | R/W-0/0 | R/W-0/0            | R/W-0/0 | R/W-0/0                                          | R/W-0/0          | R/W-0/0 | R/W-1/1 |  |

|------------------|---------|--------------------|---------|--------------------------------------------------|------------------|---------|---------|--|

|                  |         |                    | PSMCxT  | MRH<7:0>                                         |                  |         |         |  |

| bit 7            |         |                    |         |                                                  |                  |         | bit 0   |  |

|                  |         |                    |         |                                                  |                  |         |         |  |

| Legend:          |         |                    |         |                                                  |                  |         |         |  |

| R = Readable     | bit     | W = Writable       | bit     | U = Unimpler                                     | mented bit, read | as '0'  |         |  |

| u = Bit is uncha | anged   | x = Bit is unknown |         | -n/n = Value at POR and BOR/Value at all other I |                  |         |         |  |

bit 7-0 PSMCxTMRH<7:0>: 16-bit PSMCx Time Base Counter Most Significant bits

'0' = Bit is cleared

= PSMCxTMR<15:8>

'1' = Bit is set

# PIC16(L)F1784/6/7

# PIC16(L)F1784/6/7

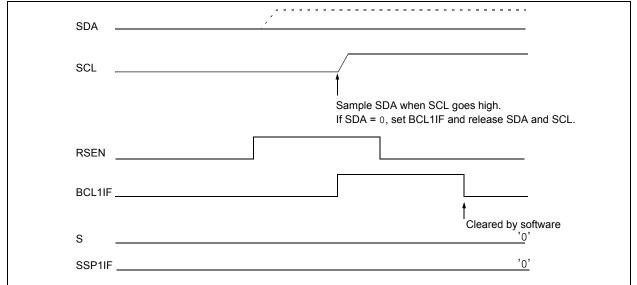

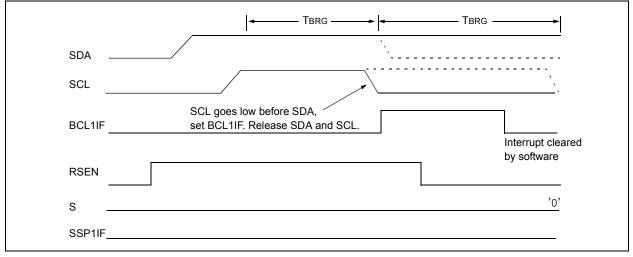

# 26.6.13.2 Bus Collision During a Repeated Start Condition

During a Repeated Start condition, a bus collision occurs if:

- a) A low level is sampled on SDA when SCL goes from low level to high level.

- SCL goes low before SDA is asserted low, indicating that another master is attempting to transmit a data '1'.

When the user releases SDA and the pin is allowed to float high, the BRG is loaded with SSPADD and counts down to zero. The SCL pin is then deasserted and when sampled high, the SDA pin is sampled. If SDA is low, a bus collision has occurred (i.e., another master is attempting to transmit a data '0', Figure 26-35). If SDA is sampled high, the BRG is reloaded and begins counting. If SDA goes from high-to-low before the BRG times out, no bus collision occurs because no two masters can assert SDA at exactly the same time.

If SCL goes from high-to-low before the BRG times out and SDA has not already been asserted, a bus collision occurs. In this case, another master is attempting to transmit a data '1' during the Repeated Start condition, see Figure 26-36.

If, at the end of the BRG time-out, both SCL and SDA are still high, the SDA pin is driven low and the BRG is reloaded and begins counting. At the end of the count, regardless of the status of the SCL pin, the SCL pin is driven low and the Repeated Start condition is complete.

FIGURE 26-36: BUS COLLISION DURING A REPEATED START CONDITION (CASE 1)

#### 27.4.4 BREAK CHARACTER SEQUENCE

The EUSART module has the capability of sending the special Break character sequences that are required by the LIN bus standard. A Break character consists of a Start bit, followed by 12 '0' bits and a Stop bit.

To send a Break character, set the SENDB and TXEN bits of the TXSTA register. The Break character transmission is then initiated by a write to the TXREG. The value of data written to TXREG will be ignored and all '0's will be transmitted.

The SENDB bit is automatically reset by hardware after the corresponding Stop bit is sent. This allows the user to preload the transmit FIFO with the next transmit byte following the Break character (typically, the Sync character in the LIN specification).

The TRMT bit of the TXSTA register indicates when the transmit operation is active or idle, just as it does during normal transmission. See Figure 27-9 for the timing of the Break character sequence.

#### 27.4.4.1 Break and Sync Transmit Sequence

The following sequence will start a message frame header made up of a Break, followed by an auto-baud Sync byte. This sequence is typical of a LIN bus master.

- 1. Configure the EUSART for the desired mode.

- 2. Set the TXEN and SENDB bits to enable the Break sequence.

- 3. Load the TXREG with a dummy character to initiate transmission (the value is ignored).

- 4. Write '55h' to TXREG to load the Sync character into the transmit FIFO buffer.

- 5. After the Break has been sent, the SENDB bit is reset by hardware and the Sync character is then transmitted.

When the TXREG becomes empty, as indicated by the TXIF, the next data byte can be written to TXREG.

#### **FIGURE 27-9:** SEND BREAK CHARACTER SEQUENCE Write to TXREG Dummy Write **BRG** Output (Shift Clock) TX (pin) Start bit bit 0 bit 1 Stop bit Break TXIF bit (Transmit Interrupt Flag) TRMT bit (Transmit Shift Empty Flag) SENDB Sampled Here Auto Cleared SENDB (send Break control bit)

#### 27.4.5 RECEIVING A BREAK CHARACTER

The Enhanced EUSART module can receive a Break character in two ways.

The first method to detect a Break character uses the FERR bit of the RCSTA register and the received data as indicated by RCREG. The Baud Rate Generator is assumed to have been initialized to the expected baud rate.

A Break character has been received when;

- RCIF bit is set

- · FERR bit is set

- RCREG = 00h

The second method uses the Auto-Wake-up feature described in **Section 27.4.3** "**Auto-Wake-up on Break**". By enabling this feature, the EUSART will sample the next two transitions on RX/DT, cause an RCIF interrupt, and receive the next data byte followed by another interrupt.

Note that following a Break character, the user will typically want to enable the Auto-Baud Detect feature. For both methods, the user can set the ABDEN bit of the BAUDCON register before placing the EUSART in Sleep mode.

DS40001637C-page 356

| Mnemonic,<br>Operands |      |                                       | Cycle   | 14-Bit Opcode |      |      |      | Status       |       |

|-----------------------|------|---------------------------------------|---------|---------------|------|------|------|--------------|-------|

|                       |      | Description                           |         | MS<br>b       |      |      | LSb  | Affecte<br>d | Notes |

| CONTROL OPERATIONS    |      |                                       |         |               |      |      |      |              |       |

| BRA                   | k    | Relative Branch                       | 2       | 11            | 001k | kkkk | kkkk |              |       |

| BRW                   | -    | Relative Branch with W                | 2       | 00            | 0000 | 0000 | 1011 |              |       |

| CALL                  | k    | Call Subroutine                       | 2       | 10            | 0kkk | kkkk | kkkk |              |       |

| CALLW                 | -    | Call Subroutine with W                | 2       | 00            | 0000 | 0000 | 1010 |              |       |

| GOTO                  | k    | Go to address                         | 2       | 10            | 1kkk | kkkk | kkkk |              |       |

| RETFIE                | k    | Return from interrupt                 | 2       | 00            | 0000 | 0000 | 1001 |              |       |

| RETLW                 | k    | Return with literal in W              | 2       | 11            | 0100 | kkkk | kkkk |              |       |

| RETUR                 | -    | Return from Subroutine                | 2       | 00            | 0000 | 0000 | 1000 |              |       |

| Ν                     |      |                                       |         |               |      |      |      |              |       |

|                       |      | INHERENT OPER                         | ATIONS  |               |      |      |      |              |       |

| CLR-                  | _    | Clear Watchdog Timer                  | 1       | 00            | 0000 | 0110 | 0100 | TO, PD       |       |

| WDT                   | -    | No Operation                          | 1       | 00            | 0000 | 0000 | 0000 |              |       |

| NOP                   | _    | Load OPTION_REG register with W       | 1       | 00            | 0000 | 0110 | 0010 |              |       |

| OPTION                | -    | Software device Reset                 | 1       | 00            | 0000 | 0000 | 0001 |              |       |

| RESET                 | -    | Go into Standby mode                  | 1       | 00            | 0000 | 0110 | 0011 | TO, PD       |       |

| SLEEP                 | f    | Load TRIS register with W             | 1       | 00            | 0000 | 0110 | Offf |              |       |

| TRIS                  |      |                                       |         |               |      |      |      |              |       |

|                       |      | C-COMPILER OPT                        | TIMIZED |               |      |      |      |              |       |

| ADDFS                 | n, k | Add Literal k to FSRn                 | 1       | 11            | 0001 | 0nkk | kkkk |              |       |

| R                     | n mm | Move Indirect FSRn to W with pre/post | 1       | 00            | 0000 | 0001 | 0nm  | Z            | 2, 3  |

| MOVIW                 |      | inc/dec modifier, mm                  |         |               |      |      | m    |              |       |

|                       | k[n] | Move INDFn to W, Indexed Indirect.    | 1       | 11            | 1111 | 0nkk | kkkk | Z            | 2     |

|                       | n mm | Move W to Indirect FSRn with pre/post | 1       | 00            | 0000 | 0001 | lnmm |              | 2, 3  |

| MOVWI                 |      | inc/dec modifier, mm                  |         | 11            | 1111 |      | kkkk |              |       |

|                       | k[n] | Move W to INDFn, Indexed Indirect.    | 1       | ΤT            | 1111 | 1nkk |      |              | 2     |

#### TABLE 29-4: ENHANCED MID-RANGE INSTRUCTION SET (CONTINUED)

**Note 1:** If the Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

**2:** If this instruction addresses an INDF register and the MSb of the corresponding FSR is set, this instruction will require one additional instruction cycle.

3: See Table in the MOVIW and MOVWI instruction descriptions.

### 29.2 Instruction Descriptions

| ADDFSR           | Add Literal to FSRn                                                                                                |

|------------------|--------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] ADDFSR FSRn, k                                                                                           |

| Operands:        | -32 ≤ k ≤ 31<br>n Î [ 0, 1]                                                                                        |

| Operation:       | $FSR(n) + k \rightarrow FSR(n)$                                                                                    |

| Status Affected: | None                                                                                                               |

| Description:     | The signed 6-bit literal 'k' is<br>added to the contents of the<br>FSRnH:FSRnL register pair.                      |

|                  | FSRn is limited to the range<br>0000h - FFFFh. Moving beyond<br>these bounds will cause the FSR<br>to wrap-around. |

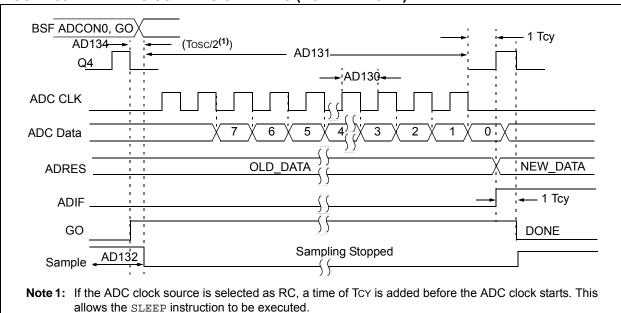

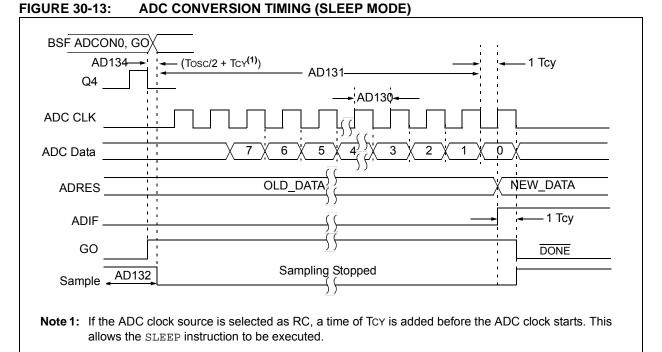

#### FIGURE 30-12: ADC CONVERSION TIMING (NORMAL MODE)

### 32.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> X IDE Software

Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB X SIM Software Simulator

- · Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- Third-party development tools

#### 32.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac  $OS^{®}$  X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users.

Feature-Rich Editor:

- Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- · Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- · Call graph window

- Project-Based Workspaces:

- Multiple projects

- Multiple tools

- Multiple configurations

- · Simultaneous debugging sessions

- File History and Bug Tracking:

- Local file history feature

- · Built-in support for Bugzilla issue tracker