Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PSMC, PWM, WDT                                |

| Number of I/O              | 24                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 11x12b; D/A 1x8b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1786-e-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.0 DEVICE OVERVIEW

The PIC16(L)F1784/6/7 are described within this data sheet. The block diagram of these devices are shown in Figure 1-1. The available peripherals are shown in Table 1-1, and the pin out descriptions are shown in Table 1-2.

| TABLE 1-1: DEVICE PERIPHERAL SUMMARY |

|--------------------------------------|

|--------------------------------------|

| Peripheral                      | PIC16(L)F1782    | PIC16(L)F1783 | PIC16(L)F1784 | PIC16(L)F1786 | PIC16(L)F1787 | PIC16(L)F1788 | PIC16(L)F1789 |   |

|---------------------------------|------------------|---------------|---------------|---------------|---------------|---------------|---------------|---|

| Analog-to-Digital Converter (AD | •                | •             | •             | ٠             | ٠             | •             | •             |   |

| Fixed Voltage Reference (FVR)   |                  | •             | •             | •             | ٠             | •             | •             | • |

| Reference Clock Module          | •                | •             | •             | ٠             | ٠             | •             | •             |   |

| Temperature Indicator           |                  | •             | •             | •             | ٠             | ٠             | •             | • |

| Capture/Compare/PWM (CCP/E      | CCP) Modules     |               |               |               |               |               |               |   |

|                                 | CCP1             | •             | •             | •             | ٠             | ٠             | •             | • |

|                                 | CCP2             | •             | •             | •             | ٠             | ٠             | •             | • |

|                                 | CCP3             |               |               | •             | ٠             | ٠             | •             | • |

| Comparators                     |                  |               |               |               |               |               |               |   |

|                                 | C1               | •             | •             | •             | ٠             | ٠             | •             | • |

|                                 | C2               | •             | •             | •             | ٠             | ٠             | •             | • |

|                                 | C3               | •             | •             | •             | ٠             | •             | •             | • |

|                                 | C4               |               |               | ٠             | ٠             | ٠             | •             | • |

| Digital-to-Analog Converter (DA | C)               |               |               |               |               |               |               |   |

|                                 | (8-bit DAC) D1   | •             | •             | •             | ٠             | ٠             | •             | • |

|                                 | (5-bit DAC) D2   |               |               |               |               |               |               | • |

|                                 | (5-bit DAC) D3   |               |               |               |               |               |               | • |

|                                 | (5-bit DAC) D4   |               |               |               |               |               |               | • |

| Enhanced Universal Synchronous  | s/Asynchronous F | Receiver/     | Transmi       | tter (EUS     | SART)         |               |               |   |

|                                 | EUSART           | •             | •             | ٠             | ٠             | ٠             | •             | • |

| Master Synchronous Serial Ports | 6                |               |               |               |               |               |               |   |

|                                 | MSSP             | •             | •             | •             | ٠             | ٠             | •             | • |

| Op Amp                          | •                |               |               |               |               |               |               |   |

|                                 | Op Amp 1         | •             | •             | •             | ٠             | ٠             | •             | • |

|                                 | Op Amp 2         | •             | •             | •             | •             | •             | •             | • |

|                                 | Op Amp 3         |               |               | •             |               | ٠             |               | • |

| Programmable Switch Mode Con    | ntroller (PSMC)  |               |               |               |               |               |               |   |

|                                 | PSMC1            | •             | •             | •             | ٠             | •             | •             | • |

|                                 | PSMC2            | •             | •             | •             | •             | •             | •             | • |

|                                 | PSMC3            |               |               | •             | ٠             | ٠             | •             | • |

|                                 | PSMC4            |               |               |               |               |               | •             | • |

| Timers                          | •                |               |               |               |               |               |               |   |

|                                 | Timer0           | •             | •             | •             | ٠             | ٠             | •             | • |

|                                 | Timer1           | •             | •             | •             | ٠             | ٠             | •             | • |

|                                 | Timer2           | •             | •             | •             | •             | •             | •             | • |

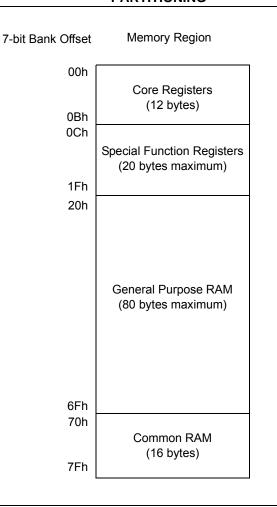

#### 3.3.1 SPECIAL FUNCTION REGISTER

The Special Function Registers (SFR) are registers used by the application to control the desired operation of peripheral functions in the device. The SFR occupies the 20 bytes after the core registers of every data memory bank (addresses x0Ch/x8Ch through x1Fh/x9Fh). The registers associated with the operation of each peripheral are described in the corresponding peripheral chapters of this data sheet.

#### 3.3.2 GENERAL PURPOSE RAM

There are up to 80 bytes of General Purpose Registers (GPR) in each data memory bank. The GPR occupies the space immediately after the SFR of selected data memory banks. The number of banks selected depends on the total amount of GPR space available in the device.

#### 3.3.2.1 Linear Access to GPR

The general purpose RAM can be accessed in a non-banked method via the FSRs. This can simplify access to large memory structures. See **Section 3.6.2** "Linear Data Memory" for more information.

#### 3.3.3 COMMON RAM

There are 16 bytes of common RAM accessible from all banks.

#### FIGURE 3-3: BANKED MEMORY PARTITIONING

#### 5.1 Power-On Reset (POR)

The POR circuit holds the device in Reset until VDD has reached an acceptable level for minimum operation. Slow rising VDD, fast operating speeds or analog performance may require greater than minimum VDD. The PWRT, BOR or MCLR features can be used to extend the start-up period until all device operation conditions have been met.

#### 5.1.1 POWER-UP TIMER (PWRT)

The Power-up Timer provides a nominal 64 ms time-out on POR or Brown-out Reset.

The device is held in Reset as long as PWRT is active. The PWRT delay allows additional time for the VDD to rise to an acceptable level. The Power-up Timer is enabled by clearing the PWRTE bit in Configuration Words.

The Power-up Timer starts after the release of the POR and BOR.

For additional information, refer to Application Note AN607, *"Power-up Trouble Shooting"* (DS00607).

### 5.2 Brown-Out Reset (BOR)

The BOR circuit holds the device in Reset when VDD reaches a selectable minimum level. Between the POR and BOR, complete voltage range coverage for execution protection can be implemented.

The Brown-out Reset module has four operating modes controlled by the BOREN<1:0> bits in Configuration Words. The four operating modes are:

- · BOR is always on

- · BOR is off when in Sleep

- · BOR is controlled by software

- · BOR is always off

Refer to Table 5-1 for more information.

The Brown-out Reset voltage level is selectable by configuring the BORV bit in Configuration Words.

A VDD noise rejection filter prevents the BOR from triggering on small events. If VDD falls below VBOR for a duration greater than parameter TBORDC, the device will reset. See Figure 5-2 for more information.

| BOREN<1:0> | SBOREN | Device Mode | BOR Mode | Instruction Execution upon:<br>Release of POR or Wake-up from Sleep |

|------------|--------|-------------|----------|---------------------------------------------------------------------|

| 11         | х      | Х           | Active   | Waits for BOR ready <sup>(1)</sup> (BORRDY = 1)                     |

| 1.0        |        | Awake       | Active   | Weite for BOD ready (BODDDV = 1)                                    |

| 10         | Х      | Sleep       | Disabled | Waits for BOR ready (BORRDY = 1)                                    |

| 0.1        | 1      | х           | Active   | Waits for BOR ready <sup>(1)</sup> (BORRDY = 1)                     |

| 01         | 0      | х           | Disabled | Regine immediately (RORDDY =)                                       |

| 00         | Х      | х           | Disabled | Begins immediately (BORRDY = $x$ )                                  |

#### TABLE 5-1:BOR OPERATING MODES

Note 1: In these specific cases, "Release of POR" and "Wake-up from Sleep", there is no delay in start-up. The BOR ready flag, (BORRDY = 1), will be set before the CPU is ready to execute instructions because the BOR circuit is forced on by the BOREN<1:0> bits.

#### 5.2.1 BOR IS ALWAYS ON

When the BOREN bits of Configuration Words are programmed to '11', the BOR is always on. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is active during Sleep. The BOR does not delay wake-up from Sleep.

#### 5.2.2 BOR IS OFF IN SLEEP

When the BOREN bits of Configuration Words are programmed to '10', the BOR is on, except in Sleep. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is not active during Sleep. The device wake-up will be delayed until the BOR is ready.

#### 5.2.3 BOR CONTROLLED BY SOFTWARE

When the BOREN bits of Configuration Words are programmed to '01', the BOR is controlled by the SBOREN bit of the BORCON register. The device start-up is not delayed by the BOR ready condition or the VDD level.

BOR protection begins as soon as the BOR circuit is ready. The status of the BOR circuit is reflected in the BORRDY bit of the BORCON register.

BOR protection is unchanged by Sleep.

### 9.3 Register Definitions: Voltage Regulator Control

#### REGISTER 9-1: VREGCON: VOLTAGE REGULATOR CONTROL REGISTER<sup>(1)</sup>

| U-0              | U-0 | U-0           | U-0 | U-0           | U-0             | R/W-0/0 | R/W-1/1  |

|------------------|-----|---------------|-----|---------------|-----------------|---------|----------|

|                  | _   | _             | _   | _             | _               | VREGPM  | Reserved |

| bit 7            |     | ·             |     |               |                 |         | bit 0    |

|                  |     |               |     |               |                 |         |          |

| Legend:          |     |               |     |               |                 |         |          |

| R – Roodabla bit |     | M = M/ritable | hit | II – Unimplor | monted hit read |         |          |

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

|----------------------|----------------------|-------------------------------------------------------|

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-2 Unimplemented: Read as '0'

bit 1 VREGPM: Voltage Regulator Power Mode Selection bit

- 1 = Low-Power Sleep mode enabled in Sleep<sup>(2)</sup>

Draws lowest current in Sleep, slower wake-up

- Normal-Power mode enabled in Sleep<sup>(2)</sup>

Draws higher current in Sleep, faster wake-up

- bit 0 Reserved: Read as '1'. Maintain this bit set.

Note 1: "F" devices only.

2: See Section 30.0 "Electrical Specifications".

| Name    | Bit 7                                                                               | Bit 6    | Bit 5    | Bit 4    | Bit 3      | Bit 2    | Bit 1    | Bit 0    | Register on<br>Page |  |  |

|---------|-------------------------------------------------------------------------------------|----------|----------|----------|------------|----------|----------|----------|---------------------|--|--|

| INTCON  | GIE                                                                                 | PEIE     | TMR0IE   | INTE     | IOCIE      | TMR0IF   | INTF     | RAIF     | 93                  |  |  |

| IOCBF   | IOCBF7                                                                              | IOCBF6   | IOCBF5   | IOCBF4   | IOCBF3     | IOCBF2   | IOCBF1   | IOCBF0   | 159                 |  |  |

| IOCBN   | IOCBN7                                                                              | IOCBN6   | IOCBN5   | IOCBN4   | IOCBN3     | IOCBN2   | IOCBN1   | IOCBN0   | 158                 |  |  |

| IOCBP   | IOCBP7                                                                              | IOCBP6   | IOCBP5   | IOCBP4   | IOCBP3     | IOCBP2   | IOCBP1   | IOCBP0   | 158                 |  |  |

| PIE1    | TMR1GIE                                                                             | ADIE     | RCIE     | TXIE     | SSP1IE     | CCP1IE   | TMR2IE   | TMR1IE   | 94                  |  |  |

| PIE2    | OSFIE                                                                               | C2IE     | C1IE     | EEIE     | BCL1IE     | C4IE     | C3IE     | CCP2IE   | 95                  |  |  |

| PIE3    | _                                                                                   | —        | _        | CCP3IE   | _          | —        | _        | —        | 96                  |  |  |

| PIE4    | _                                                                                   | PSMC3TIE | PSMC2TIE | PSMC1TIE | _          | PSMC3SIE | PSMC2SIE | PSMC1SIE | 97                  |  |  |

| PIR1    | TMR1GIF                                                                             | ADIF     | RCIF     | TXIF     | SSP1IF     | CCP1IF   | TMR2IF   | TMR1IF   | 94                  |  |  |

| PIR2    | OSFIF                                                                               | C2IF     | C1IF     | EEIF     | BCL1IF     | C4IF     | C3IF     | CCP2IF   | 99                  |  |  |

| PIR3    | _                                                                                   | —        |          | CCP3IF   | _          | —        |          | —        | 100                 |  |  |

| PIR4    | _                                                                                   | PSMC3TIF | PSMC2TIF | PSMC1TIF | —          | PSMC3SIF | PSMC2SIF | PSMC1SIF | 101                 |  |  |

| STATUS  | —                                                                                   | —        | _        | TO       | PD         | Z        | DC       | С        | 27                  |  |  |

| VREGCON | —                                                                                   | —        | —        | —        | —          | —        | VREGPM   | Reserved | 106                 |  |  |

| WDTCON  | _                                                                                   | —        |          | ١        | WDTPS<4:0> | >        |          | SWDTEN   | 110                 |  |  |

| Logondu | - unimplemented leastion, read as '0'. Shaded calls are not used in Dewar Down mode |          |          |          |            |          |          |          |                     |  |  |

#### TABLE 9-1: SUMMARY OF REGISTERS ASSOCIATED WITH POWER-DOWN MODE

Legend: — = unimplemented location, read as '0'. Shaded cells are not used in Power-Down mode.

|        | •••    |       |            |       |       |       |       |        |                     |

|--------|--------|-------|------------|-------|-------|-------|-------|--------|---------------------|

| Name   | Bit 7  | Bit 6 | Bit 5      | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0  | Register<br>on Page |

| OSCCON | SPLLEN |       | IRCF       | <3:0> |       | —     | SCS   | 82     |                     |

| STATUS | —      | _     | —          | TO    | PD    | Z     | DC    | С      | 27                  |

| WDTCON | —      | —     | WDTPS<4:0> |       |       |       |       | SWDTEN | 110                 |

### TABLE 11-3: SUMMARY OF REGISTERS ASSOCIATED WITH WATCHDOG TIMER

**Legend:** x = unknown, u = unchanged, – = unimplemented locations read as '0'. Shaded cells are not used by Watchdog Timer.

#### TABLE 11-4: SUMMARY OF CONFIGURATION WORD WITH WATCHDOG TIMER

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4  | Bit 11/3 | Bit 10/2   | Bit 9/1 | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|-----------|----------|------------|---------|---------|---------------------|

|         | 13:8 | _       | _       | FCMEN    | IESO      | CLKOUTEN | BOREN<1:0> |         | CPD     | 54                  |

| CONFIG1 | 7:0  | CP      | MCLRE   | PWRTE    | WDTE<1:0> |          | FOSC<2:0>  |         |         | 54                  |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by Watchdog Timer.

# 12.6 Write Verify

Depending on the application, good programming practice may dictate that the value written to the data EEPROM or program memory should be verified (see Example 12-7) to the desired value to be written. Example 12-7 shows how to verify a write to EEPROM.

#### EXAMPLE 12-7: EEPROM WRITE VERIFY

| BANKSEI | l eedatl  | ;                    |

|---------|-----------|----------------------|

| MOVF    | EEDATL, W | ;EEDATL not changed  |

|         |           | ;from previous write |

| BSF     | EECON1, R | ) ;YES, Read the     |

|         |           | ;value written       |

| XORWF   | EEDATL, W | ;                    |

| BTFSS   | STATUS, Z | ;Is data the same    |

| GOTO    | WRITE_ERR | ;No, handle error    |

| :       |           | ;Yes, continue       |

| 1       |           |                      |

| R/W-0/0                 | R/W-0/0               | R/W-0/0                                                                                                                                                          | R/W/HC-0/0                       | R/W-x/q           | R/W-0/0          | R/S/HC-0/0       | R/S/HC-0/0     |  |  |  |  |

|-------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|-------------------|------------------|------------------|----------------|--|--|--|--|

| EEPGD                   | CFGS                  | LWLO                                                                                                                                                             | FREE                             | WRERR             | WREN             | WR               | RD             |  |  |  |  |

| bit 7                   |                       |                                                                                                                                                                  |                                  |                   |                  |                  | bit C          |  |  |  |  |

| Logondi                 |                       |                                                                                                                                                                  |                                  |                   |                  |                  |                |  |  |  |  |

| Legend:<br>R = Readable | hit                   | W = Writable                                                                                                                                                     | hit                              | II – Unimploy     | nonted hit rea   | d oo 'O'         |                |  |  |  |  |

| S = Bit can or          |                       | x = Bit is unk                                                                                                                                                   |                                  | •                 | nented bit, read | R/Value at all o | ther Beesta    |  |  |  |  |

| '1' = Bit is set        |                       |                                                                                                                                                                  |                                  |                   |                  |                  | Inel Resels    |  |  |  |  |

|                         |                       | '0' = Bit is cle                                                                                                                                                 |                                  |                   | eared by hardv   | Vale             |                |  |  |  |  |

| bit 7                   | EEPGD: Flas           | sh Program/Da                                                                                                                                                    | ta EEPROM M                      | emory Select      | bit              |                  |                |  |  |  |  |

|                         |                       | s program spa<br>s data EEPRO                                                                                                                                    | ce Flash memo<br>M memory        | ory               |                  |                  |                |  |  |  |  |

| bit 6                   | CFGS: Flash           | Program/Data                                                                                                                                                     | EEPROM or C                      | Configuration S   | Select bit       |                  |                |  |  |  |  |

|                         |                       | •                                                                                                                                                                | n, User ID and I                 | •                 |                  |                  |                |  |  |  |  |

|                         |                       |                                                                                                                                                                  | m or data EEPI                   | ROM memory        |                  |                  |                |  |  |  |  |

| bit 5                   |                       | Write Latches                                                                                                                                                    | •                                |                   |                  |                  |                |  |  |  |  |

|                         |                       |                                                                                                                                                                  |                                  |                   | EPGD = 1 (prog   |                  |                |  |  |  |  |

|                         |                       | next WR con<br>ated.                                                                                                                                             | imand does no                    | ot initiate a w   | rite; only the p | program memoi    | ry latches are |  |  |  |  |

|                         |                       |                                                                                                                                                                  | nand writes a v                  | alue from EEI     | DATH:EEDATL      | into program m   | emory latches  |  |  |  |  |

|                         |                       |                                                                                                                                                                  |                                  |                   | program memo     |                  | 2              |  |  |  |  |

|                         | <u> If CFGS = 0 a</u> | and EEPGD = (                                                                                                                                                    | <u>):</u> (Accessing d           | ata EEPROM        | )                |                  |                |  |  |  |  |

|                         |                       |                                                                                                                                                                  |                                  |                   | e to the data El | EPROM.           |                |  |  |  |  |

| bit 4                   | FREE: Progr           | FREE: Program Flash Erase Enable bit                                                                                                                             |                                  |                   |                  |                  |                |  |  |  |  |

|                         |                       | -                                                                                                                                                                |                                  |                   | EPGD = 1 (prog   |                  |                |  |  |  |  |

|                         |                       |                                                                                                                                                                  | operation on t                   | he next WR c      | ommand (clear    | ed by hardware   | after comple   |  |  |  |  |

|                         |                       | of erase).<br>forms a write o                                                                                                                                    | peration on the                  | next WR com       | mand             |                  |                |  |  |  |  |

|                         |                       |                                                                                                                                                                  |                                  |                   | inana.           |                  |                |  |  |  |  |

|                         |                       |                                                                                                                                                                  | <u>):</u> (Accessing d           |                   |                  |                  |                |  |  |  |  |

|                         | •                     |                                                                                                                                                                  |                                  | will initiate bot | h a erase cycle  | and a write cyc  | cle.           |  |  |  |  |

| bit 3                   |                       | PROM Error F                                                                                                                                                     | •                                |                   |                  |                  |                |  |  |  |  |

|                         |                       | 1 = Condition indicates an improper program or erase sequence attempt or termination (bit is set<br>automatically on any set attempt (write '1') of the WR bit). |                                  |                   |                  |                  |                |  |  |  |  |

|                         |                       |                                                                                                                                                                  | operation comp                   |                   |                  |                  |                |  |  |  |  |

| bit 2                   | WREN: Prog            | ram/Erase Ena                                                                                                                                                    | able bit                         |                   |                  |                  |                |  |  |  |  |

|                         |                       | rogram/erase o                                                                                                                                                   |                                  |                   |                  |                  |                |  |  |  |  |

|                         | 0 = Inhibits p        | programming/e                                                                                                                                                    | rasing of progra                 | am Flash and      | data EEPROM      |                  |                |  |  |  |  |

| bit 1                   | WR: Write Co          |                                                                                                                                                                  |                                  |                   |                  |                  |                |  |  |  |  |

|                         |                       |                                                                                                                                                                  |                                  |                   | /erase operatio  |                  | malata         |  |  |  |  |

|                         |                       |                                                                                                                                                                  | set (not cleare                  |                   |                  | operation is co  | mpiete.        |  |  |  |  |

|                         |                       |                                                                                                                                                                  |                                  |                   | OM is complet    | e and inactive.  |                |  |  |  |  |

| bit 0                   | RD: Read Co           | ontrol bit                                                                                                                                                       |                                  |                   |                  |                  |                |  |  |  |  |

|                         | 1 = Initiates         | an program F                                                                                                                                                     | lash or data E                   | EPROM read        | d. Read takes    | one cycle. RD    | is cleared in  |  |  |  |  |

|                         |                       |                                                                                                                                                                  | an only be set<br>ram Flash or d |                   |                  |                  |                |  |  |  |  |

|                         |                       |                                                                                                                                                                  |                                  |                   |                  |                  |                |  |  |  |  |

### REGISTER 12-5: EECON1: EEPROM CONTROL 1 REGISTER

| ADC Clock Period (TAD) |           |                             | Device Frequency (Fosc)     |                             |                             |                             |                               |

|------------------------|-----------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|-------------------------------|

| ADC<br>Clock Source    | ADCS<2:0> | 32 MHz                      | 20 MHz                      | 16 MHz                      | 8 MHz                       | 4 MHz                       | 1 MHz                         |

| Fosc/2                 | 000       | 62.5ns <sup>(2)</sup>       | 100 ns <sup>(2)</sup>       | 125 ns <sup>(2)</sup>       | 250 ns <sup>(2)</sup>       | 500 ns <sup>(2)</sup>       | 2.0 μs                        |

| Fosc/4                 | 100       | 125 ns <sup>(2)</sup>       | 200 ns <sup>(2)</sup>       | 250 ns <sup>(2)</sup>       | 500 ns <sup>(2)</sup>       | 1.0 μs                      | 4.0 μs                        |

| Fosc/8                 | 001       | 0.5 μs <sup>(2)</sup>       | 400 ns <sup>(2)</sup>       | 0.5 μs <sup>(2)</sup>       | 1.0 μs                      | 2.0 μs                      | 8.0 μs <sup>(3)</sup>         |

| Fosc/16                | 101       | 800 ns                      | 800 ns                      | 1.0 μs                      | 2.0 μs                      | 4.0 μs                      | 16.0 μs <b><sup>(3)</sup></b> |

| Fosc/32                | 010       | 1.0 μs                      | 1.6 μs                      | 2.0 μs                      | 4.0 μs                      | 8.0 μs <sup>(3)</sup>       | 32.0 μs <sup>(3)</sup>        |

| Fosc/64                | 110       | 2.0 μs                      | 3.2 μs                      | 4.0 μs                      | 8.0 μs <sup>(3)</sup>       | 16.0 μs <sup>(3)</sup>      | 64.0 μs <sup>(3)</sup>        |

| Frc                    | x11       | 1.0-6.0 μs <sup>(1,4)</sup>   |

Legend: Shaded cells are outside of recommended range.

Note 1: The FRC source has a typical TAD time of 1.6  $\mu$ s for VDD.

2: These values violate the minimum required TAD time.

3: For faster conversion times, the selection of another clock source is recommended.

4: The ADC clock period (TAD) and total ADC conversion time can be minimized when the ADC clock is derived from the system clock FOSC. However, the FRC oscillator source must be used when conversions are to be performed with the device in Sleep mode.

# 21.2 Register Definitions: Option Register

# REGISTER 21-1: OPTION\_REG: OPTION REGISTER

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         u = Bit is unchanged       x = Bit is unknown       -n/n = Value at POR and BOR/Value at all other Res         1' = Bit is set       '0' = Bit is cleared         bit 7       WPUEN: Weak Pull-Up Enable bit         1 = All weak pull-ups are disabled (except MCLR, if it is enabled)         0 = Weak pull-ups are enabled by individual WPUx latch values         bit 6       INTEDG: Interrupt Edge Select bit         1 = Interrupt on rising edge of INT pin         0 = Interrupt on rising edge of INT pin         0 = Interrupt on Clock Source Select bit         1 = Transition on T0CKI pin         0 = Interrupt on Source Edge Select bit         1 = Increment on high-to-low transition on T0CKI pin         0 = Increment on high-to-low transition on T0CKI pin         0 = Increment on low-to-high transition on T0CKI pin         0 = Increment on low-to-high transition on T0CKI pin         0 = Prescaler is not assigned to the Timer0 module         0 = Prescaler is assigned to the Timer0 module         0 = Prescaler is assigned to the Timer0 module         0 = Prescaler is assigned to the Timer0 module         0 = Prescaler is assigned to the Timer0 module         0 = Prescaler is assigned to the Timer0 module         0 = Prescaler is assigned to t   | R/W-1/1      | R/W-1/1          | R/W-1/1           | R/W-1/1         | R/W-1/1        | R/W-1/1          | R/W-1/1          | R/W-1/1      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------------------|-------------------|-----------------|----------------|------------------|------------------|--------------|

| u = Bit is unchanged       x = Bit is unknown       -n/n = Value at POR and BOR/Value at all other Res         1' = Bit is set       '0' = Bit is cleared       -n/n = Value at POR and BOR/Value at all other Res         bit 7       WPUEN:       Weak Pull-Up Enable bit       -         1 = All weak pull-ups are disabled (except MCLR, if it is enabled)       0 = weak pull-ups are enabled by individual WPUx latch values         bit 6       INTEDG: Interrupt Edge Select bit       -         1 = Interrupt on rising edge of INT pin       0 = Interrupt on falling edge of INT pin         0 = Interrupt on falling edge of INT pin       0 = Interrupt on TOCKI pin         0 = Internal instruction cycle clock (Fosc/4)       -         bit 4       TMROSE: Timer0 Source Edge Select bit         1 = Increment on high-to-low transition on TOCKI pin       0 = Increment on high-to-low transition on TOCKI pin         0 = Increment on low-to-high transition on TOCKI pin       0 = Increment on low-to-high transition on TOCKI pin         bit 3       PSA: Prescaler Assignment bit         1 = Prescaler is not assigned to the Timer0 module       0 = Prescaler is assigned to the Timer0 module         0 = Prescaler is assigned to the Timer0 module       0 = Prescaler is assigned to the Timer0 module         0 = Prescaler is assigned to the Timer0 Rate       Bit Value | VPUEN        | INTEDG           | TMR0CS            | TMR0SE          | PSA            |                  | PS<2:0>          |              |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         u = Bit is unchanged       x = Bit is unknown       -n/n = Value at POR and BOR/Value at all other Res         1' = Bit is set       '0' = Bit is cleared         Dit 7       WPUEN: Weak Pull-Up Enable bit         1 = All weak pull-ups are disabled (except MCLR, if it is enabled)         0 = Weak pull-ups are enabled by individual WPUx latch values         Dit 6       INTEDG: Interrupt Edge Select bit         1 = Interrupt on rising edge of INT pin         0 = Interrupt on falling edge of INT pin         0 = Interrupt on TOCKI pin         0 = Internal instruction cycle clock (Fosc/4)         Dit 4         TMROSE: Timer0 Source Edge Select bit         1 = Increment on high-to-low transition on T0CKI pin         0 = Increment on low-to-high transition on T0CKI pin         0 = Increment on signed to the Timer0 module         0 = Prescaler Assignment bit         1 = Prescaler is not assigned to the Timer0 module         0 = Prescaler is assigned to the Timer0 module         0 = Prescaler Rate Select bits         Bit Value       Timer0 Rate                                                                                                                                                                                                                          | ,            |                  |                   |                 |                |                  |                  | bit (        |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         u = Bit is unchanged       x = Bit is unknown       -n/n = Value at POR and BOR/Value at all other Res         1' = Bit is set       '0' = Bit is cleared         bit 7       WPUEN: Weak Pull-Up Enable bit         1 = All weak pull-ups are disabled (except MCLR, if it is enabled)         0 = Weak pull-ups are enabled by individual WPUx latch values         bit 6       INTEDG: Interrupt Edge Select bit         1 = Interrupt on rising edge of INT pin         0 = Interrupt on falling edge of INT pin         0 = Interrupt on TOCKI pin         0 = Internal instruction cycle clock (Fosc/4)         bit 4         TMROSE: Timer0 Source Edge Select bit         1 = Increment on high-to-low transition on T0CKI pin         0 = Increment on now-to-high transition on T0CKI pin         0 = Increment on signed to the Timer0 module         0 = Prescaler Assignment bit         1 = Prescaler Assignment bit         1 = Prescaler is not assigned to the Timer0 module         0 = Prescaler is assigned to the Timer0 module         0 = Prescaler Rate Select bits         Bit Value         Bit Value                                                                                                                                                                                     | end:         |                  |                   |                 |                |                  |                  |              |

| u = Bit is unchanged       x = Bit is unknown       -n/n = Value at POR and BOR/Value at all other Res         1' = Bit is set       '0' = Bit is cleared       -n/n = Value at POR and BOR/Value at all other Res         bit 7       WPUEN:       Weak Pull-Up Enable bit       -         1 = All weak pull-ups are disabled (except MCLR, if it is enabled)       0 = Weak pull-ups are enabled by individual WPUx latch values         bit 6       INTEDG: Interrupt Edge Select bit       1 = Interrupt on rising edge of INT pin         0 = Interrupt on rising edge of INT pin       0 = Interrupt on falling edge of INT pin         0 = Interrupt on TOCKI pin       0 = Internal instruction cycle clock (Fosc/4)         bit 4       TMROSE: Timer0 Source Edge Select bit         1 = Increment on high-to-low transition on TOCKI pin       0 = Increment on high-to-low transition on TOCKI pin         bit 3       PSA: Prescaler Assignment bit         1 = Prescaler is not assigned to the Timer0 module       0 = Prescaler is assigned to the Timer0 module         0 = Prescaler is assigned to the Timer0 module       0 = Prescaler is assigned to the Timer0 module         0 = Prescaler is assigned to the Timer0 module       0 = Prescaler is assigned to the Timer0 module                                                                                                     |              | pit V            | W = Writable      | bit             | U = Unimpler   | mented bit, read | d as '0'         |              |

| 1' = Bit is set       '0' = Bit is cleared         bit 7       WPUEN: Weak Pull-Up Enable bit         1 = All weak pull-ups are disabled (except MCLR, if it is enabled)         0 = Weak pull-ups are enabled by individual WPUx latch values         bit 6       INTEDG: Interrupt Edge Select bit         1 = Interrupt on rising edge of INT pin         0 = Interrupt on falling edge of INT pin         0 = Interrupt on TOCKI pin         0 = Internal instruction cycle clock (Fosc/4)         bit 4         TMROSE: Timer0 Source Edge Select bit         1 = Increment on high-to-low transition on TOCKI pin         0 = Increment on low-to-high transition on TOCKI pin         0 = Increment on low-to-high transition on TOCKI pin         0 = Increment on signed to the Timer0 module         0 = Prescaler is not assigned to the Timer0 module         0 = Prescaler is assigned to the Timer0 module         0 = Prescaler is assigned to the Timer0 module         0 = Prescaler is assigned to the Timer0 module         0 = Prescaler is assigned to the Timer0 module         0 = Prescaler is assigned to the Timer0 module         0 = Prescaler is assigned to the Timer0 module         0 = Prescaler is assigned to the Timer0 module                                                                                                                                           | Bit is uncha | inged            | x = Bit is unkr   | iown            | -n/n = Value a | at POR and BC    | R/Value at all c | other Resets |

| 1 = All weak pull-ups are disabled (except MCLR, if it is enabled)         0 = Weak pull-ups are enabled by individual WPUx latch values         bit 6       INTEDG: Interrupt Edge Select bit         1 = Interrupt on rising edge of INT pin         0 = Interrupt on falling edge of INT pin         0 = Interrupt on falling edge of INT pin         0 = Interrupt on falling edge of INT pin         bit 5       TMROCS: Timer0 Clock Source Select bit         1 = Transition on TOCKI pin         0 = Internal instruction cycle clock (Fosc/4)         bit 4       TMROSE: Timer0 Source Edge Select bit         1 = Increment on high-to-low transition on TOCKI pin         0 = Increment on low-to-high transition on TOCKI pin         0 = Increment on low-to-high transition on TOCKI pin         0 = Increment on low-to-high transition on TOCKI pin         0 = Prescaler is not assigned to the Timer0 module         0 = Prescaler is assigned to the Timer0 module         0 = Prescaler is assigned to the Timer0 module         0 = Prescaler Rate Select bits         Bit Value       Timer0 Rate                                                                                                                                                                                                                                                                                     |              | -                | '0' = Bit is clea | ared            |                |                  |                  |              |

| 1 = All weak pull-ups are disabled (except MCLR, if it is enabled)         0 = Weak pull-ups are enabled by individual WPUx latch values         bit 6       INTEDG: Interrupt Edge Select bit         1 = Interrupt on rising edge of INT pin         0 = Interrupt on falling edge of INT pin         0 = Interrupt on falling edge of INT pin         0 = Interrupt on falling edge of INT pin         bit 5       TMROCS: Timer0 Clock Source Select bit         1 = Transition on TOCKI pin         0 = Internal instruction cycle clock (Fosc/4)         bit 4       TMROSE: Timer0 Source Edge Select bit         1 = Increment on high-to-low transition on TOCKI pin         0 = Increment on low-to-high transition on TOCKI pin         0 = Increment on low-to-high transition on TOCKI pin         0 = Increment on low-to-high transition on TOCKI pin         0 = Prescaler is not assigned to the Timer0 module         0 = Prescaler is assigned to the Timer0 module         0 = Prescaler is assigned to the Timer0 module         0 = Prescaler Rate Select bits         Bit Value       Timer0 Rate                                                                                                                                                                                                                                                                                     |              |                  |                   |                 |                |                  |                  |              |

| <ul> <li>0 = Weak pull-ups are enabled by individual WPUx latch values</li> <li>bit 6 INTEDG: Interrupt Edge Select bit         <ol> <li>1 = Interrupt on rising edge of INT pin</li> <li>0 = Interrupt on falling edge of INT pin</li> <li>0 = Interrupt on falling edge of INT pin</li> <li>0 = Interrupt on TOCKI pin</li> <li>0 = Internal instruction cycle clock (Fosc/4)</li> </ol> </li> <li>bit 4 TMROSE: Timer0 Source Edge Select bit         <ol> <li>1 = Increment on high-to-low transition on TOCKI pin</li> <li>0 = Increment on low-to-high transition on TOCKI pin</li> <li>0 = Increment on low-to-high transition on TOCKI pin</li> <li>0 = Prescaler is not assigned to the Timer0 module</li> <li>0 = Prescaler Rate Select bits</li> <li>Bit Value Timer0 Rate</li> </ol> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ,            |                  |                   |                 |                |                  |                  |              |

| bit 6       INTEDG: Interrupt Edge Select bit         1 = Interrupt on rising edge of INT pin         0 = Interrupt on falling edge of INT pin         bit 5       TMROCS: Timer0 Clock Source Select bit         1 = Transition on T0CKI pin         0 = Internal instruction cycle clock (Fosc/4)         bit 4       TMROSE: Timer0 Source Edge Select bit         1 = Increment on high-to-low transition on T0CKI pin         0 = Increment on low-to-high transition on T0CKI pin         0 = Increment on low-to-high transition on T0CKI pin         0 = Increment on low-to-high transition on T0CKI pin         0 = Increment on low-to-high transition on T0CKI pin         0 = Prescaler Assignment bit         1 = Prescaler is not assigned to the Timer0 module         0 = Prescaler is assigned to the Timer0 module         0 = Prescaler Rate Select bits         Bit Value       Timer0 Rate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |              |                  |                   | · · ·           |                | ,                |                  |              |

| 1 = Interrupt on rising edge of INT pin         0 = Interrupt on falling edge of INT pin         bit 5         TMR0CS: Timer0 Clock Source Select bit         1 = Transition on T0CKI pin         0 = Internal instruction cycle clock (Fosc/4)         bit 4         TMR0SE: Timer0 Source Edge Select bit         1 = Increment on high-to-low transition on T0CKI pin         0 = Increment on low-to-high transition on T0CKI pin         0 = Increment on low-to-high transition on T0CKI pin         0 = Increment on low-to-high transition on T0CKI pin         0 = Increment on low-to-high transition on T0CKI pin         0 = Increment on low-to-high transition on T0CKI pin         0 = Increment on low-to-high transition on T0CKI pin         0 = Increment on low-to-high transition on T0CKI pin         0 = Increment on low-to-high transition on T0CKI pin         0 = Prescaler is not assigned to the Timer0 module         0 = Prescaler is assigned to the Timer0 module         0 = Prescaler Rate Select bits         Bit Value       Timer0 Rate                                                                                                                                                                                                                                                                                                                                |              | -                | •                 | •               | al WPUx latch  | values           |                  |              |

| <ul> <li>0 = Interrupt on falling edge of INT pin</li> <li>bit 5 TMR0CS: Timer0 Clock Source Select bit         <ol> <li>1 = Transition on T0CKI pin</li> <li>0 = Internal instruction cycle clock (Fosc/4)</li> </ol> </li> <li>bit 4 TMR0SE: Timer0 Source Edge Select bit         <ol> <li>1 = Increment on high-to-low transition on T0CKI pin</li> <li>0 = Increment on low-to-high transition on T0CKI pin</li> <li>0 = Increment is not assigned to the Timer0 module</li> <li>0 = Prescaler is assigned to the Timer0 module</li> <li>0 = Prescaler Rate Select bits</li> </ol> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | i            |                  |                   |                 |                |                  |                  |              |

| bit 5 <b>TMROCS</b> : Timer0 Clock Source Select bit<br>1 = Transition on T0CKI pin<br>0 = Internal instruction cycle clock (Fosc/4)<br>bit 4 <b>TMROSE</b> : Timer0 Source Edge Select bit<br>1 = Increment on high-to-low transition on T0CKI pin<br>0 = Increment on low-to-high transition on T0CKI pin<br>bit 3 <b>PSA</b> : Prescaler Assignment bit<br>1 = Prescaler is not assigned to the Timer0 module<br>0 = Prescaler is assigned to the Timer0 module<br>bit 2-0 <b>PS&lt;2:0&gt;:</b> Prescaler Rate Select bits<br><u>Bit Value</u> Timer0 Rate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |              |                  |                   |                 |                |                  |                  |              |

| 1 = Transition on T0CKI pin         0 = Internal instruction cycle clock (Fosc/4)         bit 4         TMR0SE: Timer0 Source Edge Select bit         1 = Increment on high-to-low transition on T0CKI pin         0 = Increment on low-to-high transition on T0CKI pin         bit 3       PSA: Prescaler Assignment bit         1 = Prescaler is not assigned to the Timer0 module         0 = Prescaler is assigned to the Timer0 module         0 = Prescaler Rate Select bits         Bit Value         Timer0 Rate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | :            |                  | •••               | -               |                |                  |                  |              |

| 0 = Internal instruction cycle clock (Fosc/4)         bit 4       TMR0SE: Timer0 Source Edge Select bit         1 = Increment on high-to-low transition on T0CKI pin         0 = Increment on low-to-high transition on T0CKI pin         bit 3       PSA: Prescaler Assignment bit         1 = Prescaler is not assigned to the Timer0 module         0 = Prescaler is assigned to the Timer0 module         bit 2-0       PS<2:0>: Prescaler Rate Select bits         Bit Value       Timer0 Rate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | )            |                  |                   |                 |                |                  |                  |              |

| 1 = Increment on high-to-low transition on T0CKI pin         0 = Increment on low-to-high transition on T0CKI pin         bit 3 <b>PSA:</b> Prescaler Assignment bit         1 = Prescaler is not assigned to the Timer0 module         0 = Prescaler is assigned to the Timer0 module         bit 2-0 <b>PS&lt;2:0&gt;:</b> Prescaler Rate Select bits         Bit Value       Timer0 Rate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |              |                  | •                 | clock (Fosc/4   | +)             |                  |                  |              |

| 1 = Increment on high-to-low transition on T0CKI pin         0 = Increment on low-to-high transition on T0CKI pin         bit 3 <b>PSA:</b> Prescaler Assignment bit         1 = Prescaler is not assigned to the Timer0 module         0 = Prescaler is assigned to the Timer0 module         bit 2-0 <b>PS&lt;2:0&gt;:</b> Prescaler Rate Select bits         Bit Value       Timer0 Rate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Ļ            | TMR0SE: Time     | er0 Source Ec     | lae Select bit  | ,              |                  |                  |              |

| bit 3 PSA: Prescaler Assignment bit 1 = Prescaler is not assigned to the Timer0 module 0 = Prescaler is assigned to the Timer0 module bit 2-0 PS<2:0>: Prescaler Rate Select bits Bit Value Timer0 Rate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |              |                  |                   | •               | T0CKI pin      |                  |                  |              |

| 1 = Prescaler is not assigned to the Timer0 module         0 = Prescaler is assigned to the Timer0 module         bit 2-0 <b>PS&lt;2:0&gt;:</b> Prescaler Rate Select bits         Bit Value       Timer0 Rate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |              | 0 = Increment of | on low-to-high    | n transition on | T0CKI pin      |                  |                  |              |

| 0 = Prescaler is assigned to the Timer0 module<br>bit 2-0 <b>PS&lt;2:0&gt;:</b> Prescaler Rate Select bits<br><u>Bit Value</u> Timer0 Rate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5            | PSA: Prescale    | r Assignment      | bit             |                |                  |                  |              |

| bit 2-0 <b>PS&lt;2:0&gt;:</b> Prescaler Rate Select bits           Bit Value         Timer0 Rate           Bit Value         Timer0 Rate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              | 6                |                   |                 |                |                  |                  |              |

| Bit Value Timer0 Rate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |                  | •                 |                 | odule          |                  |                  |              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | :-0          | PS<2:0>: Pres    | caler Rate Se     | lect bits       |                |                  |                  |              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |              | Bit Va           | alue Timer0       | Rate            |                |                  |                  |              |

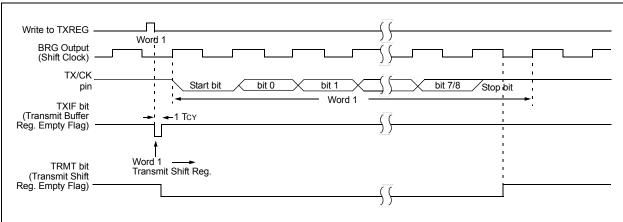

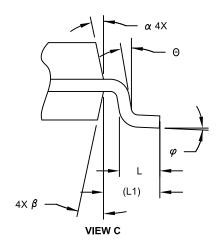

| 000 1:2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |              | 0.0              | 0 1:2             |                 |                |                  |                  |              |