#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PSMC, PWM, WDT                                |

| Number of I/O              | 24                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 1K x 8                                                                     |

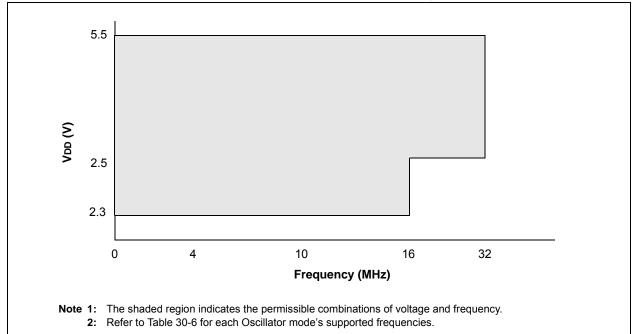

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 11x12b; D/A 1x8b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 28-SPDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1786-e-sp |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Name                                              | Function       | Input<br>Type | Output<br>Type | Description                                  |

|---------------------------------------------------|----------------|---------------|----------------|----------------------------------------------|

| RC5/PSMC1F/SDO <sup>(1)</sup>                     | RC5            | TTL/ST        | CMOS           | General purpose I/O.                         |

|                                                   | PSMC1F         | _             | CMOS           | PSMC1 output F.                              |

|                                                   | SDO            | _             | CMOS           | SPI data output.                             |

| RC6/PSMC2A/TX <sup>(1)</sup> /CK <sup>(1)</sup>   | RC6            | TTL/ST        | CMOS           | General purpose I/O.                         |

|                                                   | PSMC2A         | _             | CMOS           | PSMC2 output A.                              |

|                                                   | ТХ             | _             | CMOS           | EUSART asynchronous transmit.                |

|                                                   | СК             | ST            | CMOS           | EUSART synchronous clock.                    |

| RC7/PSMC2B/RX <sup>(1)</sup> /DT <sup>(1)</sup> / | RC7            | TTL/ST        | CMOS           | General purpose I/O.                         |

| C4OUT <sup>(4)</sup>                              | PSMC2B         | _             | CMOS           | PSMC2 output B.                              |

|                                                   | RX             | ST            | —              | EUSART asynchronous input.                   |

|                                                   | DT             | ST            | CMOS           | EUSART synchronous data.                     |

|                                                   | C4OUT          | —             | CMOS           | Comparator C4 output.                        |

| RD0 <sup>(3)</sup> /OPA3IN+                       | RD0            | TTL/ST        | CMOS           | General purpose I/O.                         |

|                                                   | OPA3IN+        | AN            | —              | Operational Amplifier 3 non-inverting input. |

| RD1 <sup>(3)</sup> /AN21/C1IN4-/C2IN4-/           | RD1            | TTL/ST        | CMOS           | General purpose I/O.                         |

| C3IN4-/C4IN4-/OPA3OUT                             | AN21           | AN            | _              | ADC Channel 21 input.                        |

|                                                   | C1IN4-         | AN            | —              | Comparator C4 negative input.                |

|                                                   | C2IN4-         | AN            | —              | Comparator C4 negative input.                |

|                                                   | C3IN4-         | AN            | —              | Comparator C4 negative input.                |

|                                                   | C4IN4-         | AN            | _              | Comparator C4 negative input.                |

|                                                   | <b>OPA3OUT</b> | —             | AN             | Operational Amplifier 3 output.              |

| RD2 <sup>(3)</sup> /OPA3IN-                       | RD2            | TTL/ST        | CMOS           | General purpose I/O.                         |

|                                                   | OPA3IN-        | AN            | _              | Operational Amplifier 3 inverting input.     |

| RD3 <sup>(3)</sup>                                | RD3            | TTL/ST        | CMOS           | General purpose I/O.                         |

| RD4 <sup>(3)</sup> /PSMC3F                        | RD4            | TTL/ST        | CMOS           | General purpose I/O.                         |

|                                                   | PSMC3F         | _             | CMOS           | PSMC3 output F.                              |

| RD5 <sup>(3)</sup> /PSMC3E                        | RD5            | TTL/ST        | CMOS           | General purpose I/O.                         |

|                                                   | PSMC3E         | _             | CMOS           | PSMC3 output E.                              |

| RD6 <sup>(3)</sup> /C3OUT/PSMC3D                  | RD6            | TTL/ST        | CMOS           | General purpose I/O.                         |

|                                                   | C3OUT          | —             | CMOS           | Comparator C3 output.                        |

|                                                   | PSMC3D         | _             | CMOS           | PSMC3 output D.                              |

| RD7 <sup>(3)</sup> /C4OUT/PSMC3C                  | RD6            | TTL/ST        | CMOS           | General purpose I/O.                         |

|                                                   | C4OUT          | —             | CMOS           | Comparator C4 output.                        |

|                                                   | PSMC3C         | —             | CMOS           | PSMC3 output C.                              |

| RE0 <sup>(3)</sup> /AN5/CCP3 <sup>(1)</sup>       | RE0            | TTL/ST        | —              | General purpose input.                       |

| · · · · ·                                         | AN5            | AN            | —              | ADC Channel 5 input.                         |

|                                                   | CCP3           | ST            | CMOS           | Capture/Compare/PWM3.                        |

| RE1 <sup>(3)</sup> /AN6/PSMC3B                    | RE1            | TTL/ST        | CMOS           | General purpose I/O.                         |

|                                                   | AN6            | AN            | —              | ADC Channel 6 input.                         |

|                                                   |                |               |                |                                              |

TABLE 1-2: PIC16(L)F1784/6/7 PINOUT DESCRIPTION (CONTINUED)

Legend: AN = Analog input or output CMOS = CMOS compatible input or output OD = Open Drain

TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels  $I^2C^{TM}$  = Schmitt Trigger input with  $I^2C$ HV = High Voltage XTAL = Crystal levels

Note 1: Pin functions can be assigned to one of two locations via software. See *Register* 13-1.

2: All pins have interrupt-on-change functionality.

3: PIC16(L)F1784/7 only.

4: PIC16(L)F1786 only.

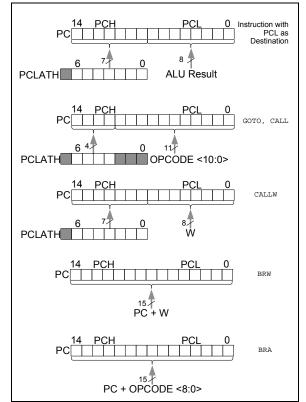

## 3.4 PCL and PCLATH

The Program Counter (PC) is 15 bits wide. The low byte comes from the PCL register, which is a readable and writable register. The high byte (PC<14:8>) is not directly readable or writable and comes from PCLATH. On any Reset, the PC is cleared. Figure 3-4 shows the five situations for the loading of the PC.

FIGURE 3-4: LOADING OF PC IN DIFFERENT SITUATIONS

#### 3.4.1 MODIFYING PCL

Executing any instruction with the PCL register as the destination simultaneously causes the Program Counter PC<14:8> bits (PCH) to be replaced by the contents of the PCLATH register. This allows the entire contents of the program counter to be changed by writing the desired upper 7 bits to the PCLATH register. When the lower 8 bits are written to the PCL register, all 15 bits of the program counter will change to the values contained in the PCLATH register.

### 3.4.2 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When performing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256-byte block). Refer to Application Note AN556, *"Implementing a Table Read"* (DS00556).

## 3.4.3 COMPUTED FUNCTION CALLS

A computed function CALL allows programs to maintain tables of functions and provide another way to execute state machines or look-up tables. When performing a table read using a computed function CALL, care should be exercised if the table location crosses a PCL memory boundary (each 256-byte block).

If using the CALL instruction, the PCH<2:0> and PCL registers are loaded with the operand of the CALL instruction. PCH<6:3> is loaded with PCLATH<6:3>.

The CALLW instruction enables computed calls by combining PCLATH and W to form the destination address. A computed CALLW is accomplished by loading the W register with the desired address and executing CALLW. The PCL register is loaded with the value of W and PCH is loaded with PCLATH.

## 3.4.4 BRANCHING

The branching instructions add an offset to the PC. This allows relocatable code and code that crosses page boundaries. There are two forms of branching, BRW and BRA. The PC will have incremented to fetch the next instruction in both cases. When using either branching instruction, a PCL memory boundary may be crossed.

If using BRW, load the W register with the desired unsigned address and execute BRW. The entire PC will be loaded with the address PC + 1 + W.

If using BRA, the entire PC will be loaded with PC + 1 +, the signed value of the operand of the BRA instruction.

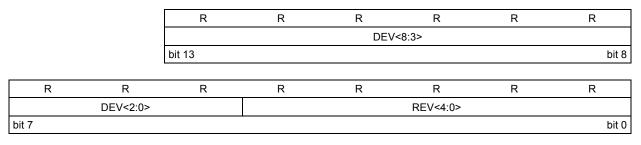

## 4.6 Device ID and Revision ID

The memory location 8006h is where the Device ID and Revision ID are stored. The upper nine bits hold the Device ID. The lower five bits hold the Revision ID. See **Section 12.5 "User ID, Device ID and Configuration Word Access**" for more information on accessing these memory locations.

Development tools, such as device programmers and debuggers, may be used to read the Device ID and Revision ID.

## 4.7 Register Definitions: Device and Revision

#### REGISTER 4-3: DEVID: DEVICE ID REGISTER

## Legend:

R = Readable bit '1' = Bit is set

bit 13-5 **DEV<8:0>:** Device ID bits

| Devries     | DEVICEID<13:0> Values |          |  |  |  |  |

|-------------|-----------------------|----------|--|--|--|--|

| Device      | DEV<8:0>              | REV<4:0> |  |  |  |  |

| PIC16F1784  | 10 1010 010           | х хххх   |  |  |  |  |

| PIC16LF1784 | 10 1010 111           | x xxxx   |  |  |  |  |

| PIC16F1786  | 10 1010 011           | x xxxx   |  |  |  |  |

| PIC16LF1786 | 10 1011 000           | x xxxx   |  |  |  |  |

| PIC16F1787  | 10 1010 100           | x xxxx   |  |  |  |  |

| PIC16LF1787 | 10 1011 001           | x xxxx   |  |  |  |  |

'0' = Bit is cleared

bit 4-0 R

REV<4:0>: Revision ID bits

These bits are used to identify the revision (see Table under DEV<8:0> above).

| U-0              | U-0                                                                                      | U-0                                      | R/W-0/0 | U-0                                                   | U-0 | U-0 | U-0   |  |

|------------------|------------------------------------------------------------------------------------------|------------------------------------------|---------|-------------------------------------------------------|-----|-----|-------|--|

| —                | —                                                                                        | —                                        | CCP3IE  | —                                                     | —   | —   | —     |  |

| bit 7            |                                                                                          |                                          |         |                                                       |     |     | bit 0 |  |

|                  |                                                                                          |                                          |         |                                                       |     |     |       |  |

| Legend:          |                                                                                          |                                          |         |                                                       |     |     |       |  |

| R = Readable     | bit                                                                                      | W = Writable                             | bit     | U = Unimplemented bit, read as '0'                    |     |     |       |  |

| u = Bit is unch  | nanged                                                                                   | x = Bit is unkn                          | iown    | -n/n = Value at POR and BOR/Value at all other Resets |     |     |       |  |

| '1' = Bit is set |                                                                                          | '0' = Bit is clea                        | ared    |                                                       |     |     |       |  |

| bit 7-5          | Unimplemen                                                                               | ted: Read as '                           | )'      |                                                       |     |     |       |  |

| bit 4            | •                                                                                        | <b>CCP3IE:</b> CCP3 Interrupt Enable bit |         |                                                       |     |     |       |  |

|                  | <ul><li>1 = Enables the CCP3 interrupt</li><li>0 = Disables the CCP3 interrupt</li></ul> |                                          |         |                                                       |     |     |       |  |

| bit 3-0          | 3-0 <b>Unimplemented:</b> Read as '0'                                                    |                                          |         |                                                       |     |     |       |  |

# REGISTER 8-4: PIE3: PERIPHERAL INTERRUPT ENABLE REGISTER 3

# 13.8 Register Definitions: PORTC

### **REGISTER 13-19: PORTC: PORTC REGISTER**

| R/W-x/u | R/W-x/u           | R/W-x/u                                  | R/W-x/u            | R/W-x/u                                                                   | R/W-x/u                                                                                                 | R/W-x/u                                                                                                                     |

|---------|-------------------|------------------------------------------|--------------------|---------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| RC6     | RC5               | RC4                                      | RC3                | RC2                                                                       | RC1                                                                                                     | RC0                                                                                                                         |

|         |                   |                                          |                    |                                                                           |                                                                                                         | bit 0                                                                                                                       |

|         |                   |                                          |                    |                                                                           |                                                                                                         |                                                                                                                             |

|         |                   |                                          |                    |                                                                           |                                                                                                         |                                                                                                                             |

| t       | W = Writable I    | oit                                      | U = Unimplen       | nented bit, read                                                          | as '0'                                                                                                  |                                                                                                                             |

| nged    | x = Bit is unkn   | own                                      | -n/n = Value a     | at POR and BO                                                             | R/Value at all o                                                                                        | ther Resets                                                                                                                 |

|         | '0' = Bit is clea | ared                                     |                    |                                                                           |                                                                                                         |                                                                                                                             |

|         | t                 | t W = Writable I<br>nged x = Bit is unkn | t W = Writable bit | t W = Writable bit U = Unimpler<br>nged x = Bit is unknown -n/n = Value a | t W = Writable bit U = Unimplemented bit, read<br>aged x = Bit is unknown $-n/n = Value at POR and BOI$ | t W = Writable bit U = Unimplemented bit, read as '0'<br>nged x = Bit is unknown -n/n = Value at POR and BOR/Value at all o |

bit 7-0 RC<7:0>: PORTC General Purpose I/O Pin bits<sup>(1)</sup> 1 = Port pin is ≥ VIH 0 = Port pin is ≤ VIL

#### REGISTER 13-20: TRISC: PORTC TRI-STATE REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| TRISC7  | TRISC6  | TRISC5  | TRISC4  | TRISC3  | TRISC2  | TRISC1  | TRISC0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

**TRISC<7:0>:** PORTC Tri-State Control bits 1 = PORTC pin configured as an input (tri-stated)

0 = PORTC pin configured as an output

#### REGISTER 13-21: LATC: PORTC DATA LATCH REGISTER

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

| LATC7   | LATC6   | LATC5   | LATC4   | LATC3   | LATC2   | LATC1   | LATC0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

### bit 7-0 LATC<7:0>: PORTC Output Latch Value bits<sup>(1)</sup>

**Note 1:** Writes to PORTC are actually written to corresponding LATC register. Reads from PORTC register is return of actual I/O pin values.

**Note 1:** Writes to PORTC are actually written to corresponding LATC register. Reads from PORTC register is return of actual I/O pin values.

### 13.11.7 PORTE FUNCTIONS AND OUTPUT PRIORITIES<sup>(1)</sup>

Each PORTE pin is multiplexed with other functions. The pins, their combined functions and their output priorities are shown in Table 13-11.

When multiple outputs are enabled, the actual pin control goes to the peripheral with the highest priority. Analog input and some digital input functions are not included in the list below. These input functions can remain active when the pin is configured as an output. Certain digital input functions override other port functions and are included in the priority list.

**Note 1:** Applies to 40/44-pin devices only.

## TABLE 13-11: PORTE OUTPUT PRIORITY

| Pin Name | Function Priority <sup>(1)</sup> |

|----------|----------------------------------|

| RE0      | CCP3<br>RE0                      |

| RE1      | PSMC3B<br>RE1                    |

| RE2      | PSMC3A<br>RE2                    |

Note 1: Priority listed from highest to lowest.

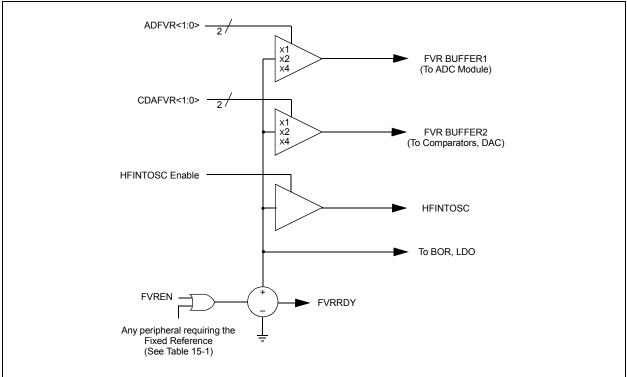

## TABLE 15-1: PERIPHERALS REQUIRING THE FIXED VOLTAGE REFERENCE (FVR)

| Peripheral  | Conditions                                                      | Description                                                  |

|-------------|-----------------------------------------------------------------|--------------------------------------------------------------|

| HFINTOSC    | FOSC<2:0> = 100 and<br>IRCF<3:0> ≠ 000x                         | INTOSC is active and device is not in Sleep                  |

|             | BOREN<1:0> = 11                                                 | BOR always enabled                                           |

| BOR         | BOREN<1:0> = 10 and BORFS = 1                                   | BOR disabled in Sleep mode, BOR Fast Start enabled.          |

|             | BOREN<1:0> = 01 and BORFS = 1                                   | BOR under software control, BOR Fast Start enabled           |

| LDO         | All PIC16F1784/6/7 devices, when<br>VREGPM = 1 and not in Sleep | The device runs off of the ULP regulator when in Sleep mode. |

| PSMC 64 MHz | PxSRC<1:0>                                                      | 64 MHz clock forces HFINTOSC on during Sleep.                |

| Absolute ADC Value | • •                     | Initude Result<br>ADRMD = 0 | 2's Compliment Result<br>ADFM = 1, ADRMD = 0 |                        |  |

|--------------------|-------------------------|-----------------------------|----------------------------------------------|------------------------|--|

| (decimal)          | ADRESH<br>(ADRES<15:8>) | ADRESL<br>(ADRES<7:0>)      | ADRESH<br>(ADRES<15:8>)                      | ADRESL<br>(ADRES<7:0>) |  |

| + 4095             | 1111 1111               | 1111 000 <u>0</u>           | 0000 1111                                    | 1111 1111              |  |

| + 2355             | 1001 0011               | 0011 000 <u>0</u>           | 0000 1001                                    | 0011 0011              |  |

| + 0001             | 0000 0000               | 0001 000 <u>0</u>           | 0000 0000                                    | 0000 0001              |  |

| 0000               | 0000 0000               | 0000 000 <u>0</u>           | 0000 0000                                    | 0000 0000              |  |

| - 0001             | 0000 0000               | 0001 000 <u>1</u>           | 1111 1111                                    | 1111 1111              |  |

| - 4095             | 1111 1111               | 1111 000 <u>1</u>           | 1111 0000                                    | 0000 0001              |  |

| - 4096             | 0000 0000               | 0000 000 <u>1</u>           | 1111 0000                                    | 0000 0000              |  |

## TABLE 17-2: ADC OUTPUT RESULTS FORMAT

**Note 1:** For the RSD ADC, the raw 13-bits from the ADC is presented in 2's compliment format, so no data translation is required for 2's compliment results.

**2:** For the SAR ADC, the raw 13-bits from the ADC is presented in sign and magnitude format, so no data translation is required for sign and magnitude results

# 22.7 Timer1 Interrupt

The Timer1 register pair (TMR1H:TMR1L) increments to FFFFh and rolls over to 0000h. When Timer1 rolls over, the Timer1 interrupt flag bit of the PIR1 register is set. To enable the interrupt on rollover, you must set these bits:

- TMR1ON bit of the T1CON register

- TMR1IE bit of the PIE1 register

- PEIE bit of the INTCON register

- GIE bit of the INTCON register

The interrupt is cleared by clearing the TMR1IF bit in the Interrupt Service Routine.

Note: The TMR1H:TMR1L register pair and the TMR1IF bit should be cleared before enabling interrupts.

## 22.8 Timer1 Operation During Sleep

Timer1 can only operate during Sleep when setup in Asynchronous Counter mode. In this mode, an external crystal or clock source can be used to increment the counter. To set up the timer to wake the device:

- TMR1ON bit of the T1CON register must be set

- TMR1IE bit of the PIE1 register must be set

- · PEIE bit of the INTCON register must be set

- T1SYNC bit of the T1CON register must be set

- TMR1CS bits of the T1CON register must be configured

- T1OSCEN bit of the T1CON register must be configured

The device will wake-up on an overflow and execute the next instructions. If the GIE bit of the INTCON register is set, the device will call the Interrupt Service Routine.

Timer1 oscillator will continue to operate in Sleep regardless of the  $\overline{\text{T1SYNC}}$  bit setting.

## 22.9 CCP Capture/Compare Time Base

The CCP modules use the TMR1H:TMR1L register pair as the time base when operating in Capture or Compare mode.

In Capture mode, the value in the TMR1H:TMR1L register pair is copied into the CCPR1H:CCPR1L register pair on a configured event.

In Compare mode, an event is triggered when the value CCPR1H:CCPR1L register pair matches the value in the TMR1H:TMR1L register pair. This event can be a Auto-conversion Trigger.

For more information, see Section 25.0 "Capture/Compare/PWM Modules".

## 22.10 CCP Auto-Conversion Trigger

When any of the CCP's are configured to trigger a auto-conversion, the trigger will clear the TMR1H:TMR1L register pair. This auto-conversion does not cause a Timer1 interrupt. The CCP module may still be configured to generate a CCP interrupt.

In this mode of operation, the CCPR1H:CCPR1L register pair becomes the period register for Timer1.

Timer1 should be synchronized and Fosc/4 should be selected as the clock source in order to utilize the Auto-conversion Trigger. Asynchronous operation of Timer1 can cause a Auto-conversion Trigger to be missed.

In the event that a write to TMR1H or TMR1L coincides with a Auto-conversion Trigger from the CCP, the write will take precedence.

For more information, see **Section 25.2.4** "Auto-Conversion Trigger".

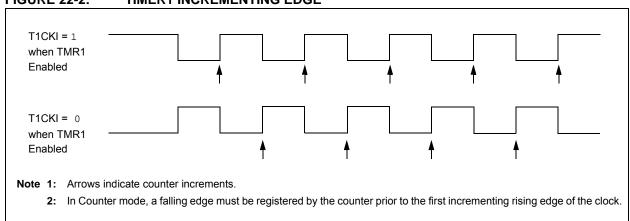

## FIGURE 22-2: TIMER1 INCREMENTING EDGE

# REGISTER 24-18: PSMCxTMRL: PSMC TIME BASE COUNTER LOW REGISTER

| R/W-0/0          | R/W-0/0 | R/W-0/0           | R/W-0/0 | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0     |

|------------------|---------|-------------------|---------|----------------|------------------|------------------|-------------|

|                  |         |                   | PSMCxT  | MRL<7:0>       |                  |                  |             |

| bit 7            |         |                   |         |                |                  |                  | bit 0       |

|                  |         |                   |         |                |                  |                  |             |

| Legend:          |         |                   |         |                |                  |                  |             |

| R = Readable     | bit     | W = Writable      | bit     | U = Unimpler   | nented bit, read | l as '0'         |             |

| u = Bit is unch  | anged   | x = Bit is unkr   | nown    | -n/n = Value a | at POR and BO    | R/Value at all c | ther Resets |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                |                  |                  |             |

bit 7-0 **PSMCxTMRL<7:0>:** 16-bit PSMCx Time Base Counter Least Significant bits = PSMCxTMR<7:0>

## REGISTER 24-19: PSMCxTMRH: PSMC TIME BASE COUNTER HIGH REGISTER

| R/W-0/0                                                       | R/W-0/0 | R/W-0/0      | R/W-0/0 | R/W-0/0      | R/W-0/0          | R/W-0/0          | R/W-1/1     |

|---------------------------------------------------------------|---------|--------------|---------|--------------|------------------|------------------|-------------|

|                                                               |         |              | PSMCxT  | MRH<7:0>     |                  |                  |             |

| bit 7                                                         |         |              |         |              |                  |                  | bit 0       |

|                                                               |         |              |         |              |                  |                  |             |

| Legend:                                                       |         |              |         |              |                  |                  |             |

| R = Readable b                                                | bit     | W = Writable | bit     | U = Unimpler | nented bit, read | as '0'           |             |

| u = Bit is unchanged x = Bit is unknown -n/n = Value at POR a |         |              |         |              | at POR and BO    | R/Value at all o | ther Resets |

bit 7-0 PSMCxTMRH<7:0>: 16-bit PSMCx Time Base Counter Most Significant bits

'0' = Bit is cleared

= PSMCxTMR<15:8>

'1' = Bit is set

## 25.3 PWM Overview

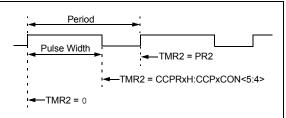

Pulse-Width Modulation (PWM) is a scheme that provides power to a load by switching quickly between fully on and fully off states. The PWM signal resembles a square wave where the high portion of the signal is considered the on state and the low portion of the signal is considered the off state. The high portion, also known as the pulse width, can vary in time and is defined in steps. A larger number of steps applied, which lengthens the pulse width, also supplies more power to the load. Lowering the number of steps applied, which shortens the pulse width, supplies less power. The PWM period is defined as the duration of one complete cycle or the total amount of on and off time combined.

PWM resolution defines the maximum number of steps that can be present in a single PWM period. A higher resolution allows for more precise control of the pulse width time and in turn the power that is applied to the load.

The term duty cycle describes the proportion of the on time to the off time and is expressed in percentages, where 0% is fully off and 100% is fully on. A lower duty cycle corresponds to less power applied and a higher duty cycle corresponds to more power applied.

Figure 25-3 shows a typical waveform of the PWM signal.

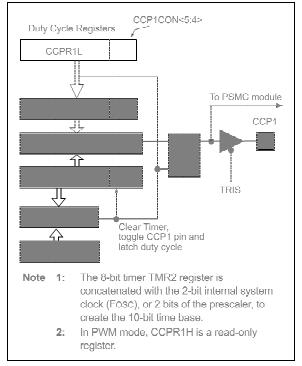

### 25.3.1 STANDARD PWM OPERATION

The standard PWM function described in this section is available and identical for all CCP modules.

The standard PWM mode generates a Pulse-Width Modulation (PWM) signal on the CCPx pin with up to 10 bits of resolution. The period, duty cycle, and resolution are controlled by the following registers:

- · PR2 registers

- · T2CON registers

- · CCPRxL registers

- · CCPxCON registers

Figure 25-4 shows a simplified block diagram of PWM operation.

- Note 1: The corresponding TRIS bit must be cleared to enable the PWM output on the CCPx pin.

- 2: Clearing the CCPxCON register will relinquish control of the CCPx pin.

#### FIGURE 25-3: CCP PWM OUTPUT SIGNAL

#### SIMPLIFIED PWM BLOCK DIAGRAM

# PIC16(L)F1784/6/7

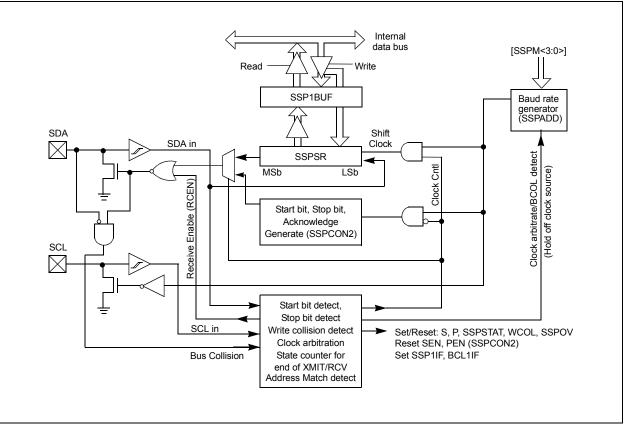

The I<sup>2</sup>C interface supports the following modes and features:

- · Master mode

- Slave mode

- Byte NACKing (Slave mode)

- · Limited multi-master support

- 7-bit and 10-bit addressing

- · Start and Stop interrupts

- Interrupt masking

- Clock stretching

- · Bus collision detection

- · General call address matching

- Address masking

- · Address Hold and Data Hold modes

- Selectable SDA hold times

Figure 26-2 is a block diagram of the  $I^2C$  interface module in Master mode. Figure 26-3 is a diagram of the  $I^2C$  interface module in Slave mode.

## FIGURE 26-2: MSSP BLOCK DIAGRAM (I<sup>2</sup>C<sup>™</sup> MASTER MODE)

# 26.4 I<sup>2</sup>C MODE OPERATION

All MSSP I<sup>2</sup>C communication is byte oriented and shifted out MSb first. Six SFR registers and two interrupt flags interface the module with the PIC<sup>®</sup> microcontroller and user software. Two pins, SDA and SCL, are exercised by the module to communicate with other external I<sup>2</sup>C devices.

#### 26.4.1 BYTE FORMAT

All communication in  $I^2C$  is done in 9-bit segments. A byte is sent from a master to a slave or vice-versa, followed by an Acknowledge bit sent back. After the 8th falling edge of the SCL line, the device outputting data on the SDA changes that pin to an input and reads in an acknowledge value on the next clock pulse.

The clock signal, SCL, is provided by the master. Data is valid to change while the SCL signal is low, and sampled on the rising edge of the clock. Changes on the SDA line while the SCL line is high define special conditions on the bus, explained below.

#### 26.4.2 DEFINITION OF I<sup>2</sup>C TERMINOLOGY

There is language and terminology in the description of  $I^2C$  communication that have definitions specific to  $I^2C$ . That word usage is defined below and may be used in the rest of this document without explanation. This table was adapted from the Philips  $I^2C$  specification.

#### 26.4.3 SDA AND SCL PINS

Selection of any  $l^2C$  mode with the SSPEN bit set, forces the SCL and SDA pins to be open-drain. These pins should be set by the user to inputs by setting the appropriate TRIS bits.

Note: Data is tied to output zero when an I<sup>2</sup>C mode is enabled.

#### 26.4.4 SDA HOLD TIME

The hold time of the SDA pin is selected by the SDAHT bit of the SSPCON3 register. Hold time is the time SDA is held valid after the falling edge of SCL. Setting the SDAHT bit selects a longer 300 ns minimum hold time and may help on buses with large capacitance.

## TABLE 26-2:I<sup>2</sup>C BUS TERMS

| TABLE 20-2. IC BUS TERWIS |                                                                                                                                                                                                    |  |  |  |  |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| TERM                      | Description                                                                                                                                                                                        |  |  |  |  |

| Transmitter               | The device which shifts data out onto the bus.                                                                                                                                                     |  |  |  |  |

| Receiver                  | The device which shifts data in from the bus.                                                                                                                                                      |  |  |  |  |

| Master                    | The device that initiates a transfer,<br>generates clock signals and<br>terminates a transfer.                                                                                                     |  |  |  |  |

| Slave                     | The device addressed by the master.                                                                                                                                                                |  |  |  |  |

| Multi-master              | A bus with more than one device that can initiate data transfers.                                                                                                                                  |  |  |  |  |

| Arbitration               | Procedure to ensure that only one master at a time controls the bus. Winning arbitration ensures that the message is not corrupted.                                                                |  |  |  |  |

| Synchronization           | Procedure to synchronize the clocks of two or more devices on the bus.                                                                                                                             |  |  |  |  |

| Idle                      | No master is controlling the bus,<br>and both SDA and SCL lines are<br>high.                                                                                                                       |  |  |  |  |

| Active                    | Any time one or more master devices are controlling the bus.                                                                                                                                       |  |  |  |  |

| Addressed<br>Slave        | Slave device that has received a matching address and is actively being clocked by a master.                                                                                                       |  |  |  |  |

| Matching<br>Address       | Address byte that is clocked into a slave that matches the value stored in SSPADD.                                                                                                                 |  |  |  |  |

| Write Request             | Slave receives a matching address with R/W bit clear, and is ready to clock in data.                                                                                                               |  |  |  |  |

| Read Request              | Master sends an address byte with<br>the R/W bit set, indicating that it<br>wishes to clock data out of the<br>Slave. This data is the next and all<br>following bytes until a Restart or<br>Stop. |  |  |  |  |

| Clock Stretching          | When a device on the bus hold SCL low to stall communication.                                                                                                                                      |  |  |  |  |

| Bus Collision             | Any time the SDA line is sampled<br>low by the module while it is out-<br>putting and expected high state.                                                                                         |  |  |  |  |

## 26.5.3 SLAVE TRANSMISSION

When the  $R/\overline{W}$  bit of the incoming address byte is set and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is set. The received address is loaded into the SSPBUF register, and an ACK pulse is sent by the slave on the ninth bit.

Following the ACK, slave hardware clears the CKP bit and the SCL pin is held low (see **Section 26.5.6** "**Clock Stretching**" for more detail). By stretching the clock, the master will be unable to assert another clock pulse until the slave is done preparing the transmit data.

The transmit data must be loaded into the SSPBUF register which also loads the SSPSR register. Then the SCL pin should be released by setting the CKP bit of the SSPCON1 register. The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time.

The ACK pulse from the master-receiver is latched on the rising edge of the ninth SCL input pulse. This ACK value is copied to the ACKSTAT bit of the SSPCON2 register. If ACKSTAT is set (not ACK), then the data transfer is complete. In this case, when the not ACK is latched by the slave, the slave goes idle and waits for another occurrence of the Start bit. If the SDA line was low (ACK), the next transmit data must be loaded into the SSPBUF register. Again, the SCL pin must be released by setting bit CKP.

An MSSP interrupt is generated for each data transfer byte. The SSP1IF bit must be cleared by software and the SSPSTAT register is used to determine the status of the byte. The SSP1IF bit is set on the falling edge of the ninth clock pulse.

#### 26.5.3.1 Slave Mode Bus Collision

A slave receives a Read request and begins shifting data out on the SDA line. If a bus collision is detected and the SBCDE bit of the SSPCON3 register is set, the BCL1IF bit of the PIR register is set. Once a bus collision is detected, the slave goes idle and waits to be addressed again. User software can use the BCL1IF bit to handle a slave bus collision.

## 26.5.3.2 7-bit Transmission

A master device can transmit a read request to a slave, and then clock data out of the slave. The list below outlines what software for a slave will need to do to accomplish a standard transmission. Figure 26-17 can be used as a reference to this list.

- 1. Master sends a Start condition on SDA and SCL.

- 2. S bit of SSPSTAT is set; SSP1IF is set if interrupt on Start detect is enabled.

- Matching address with R/W bit set is received by the Slave setting SSP1IF bit.

- 4. Slave hardware generates an ACK and sets SSP1IF.

- 5. SSP1IF bit is cleared by user.

- 6. Software reads the received address from SSPBUF, clearing BF.

- 7.  $R/\overline{W}$  is set so CKP was automatically cleared after the ACK.

- 8. The slave software loads the transmit data into SSPBUF.

- 9. CKP bit is set releasing SCL, allowing the master to clock the data out of the slave.

- 10. SSP1IF is set after the ACK response from the master is loaded into the ACKSTAT register.

- 11. SSP1IF bit is cleared.

- 12. The slave software checks the ACKSTAT bit to see if the master wants to clock out more data.

- **Note 1:** If the master ACKs the clock will be stretched.

- ACKSTAT is the only bit updated on the rising edge of SCL (9th) rather than the falling.

- 13. Steps 9-13 are repeated for each transmitted byte.

- 14. If the master sends a not ACK; the clock is not held, but SSP1IF is still set.

- 15. The master sends a Restart condition or a Stop.

- 16. The slave is no longer addressed.

## 26.6.10 SLEEP OPERATION

While in Sleep mode, the I<sup>2</sup>C slave module can receive addresses or data and when an address match or complete byte transfer occurs, wake the processor from Sleep (if the MSSP interrupt is enabled).

## 26.6.11 EFFECTS OF A RESET

A Reset disables the MSSP module and terminates the current transfer.

## 26.6.12 MULTI-MASTER MODE

In Multi-Master mode, the interrupt generation on the detection of the Start and Stop conditions allows the determination of when the bus is free. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the I<sup>2</sup>C bus may be taken when the P bit of the SSPSTAT register is set, or the bus is Idle, with both the S and P bits clear. When the bus is busy, enabling the SSP interrupt will generate the interrupt when the Stop condition occurs.

In multi-master operation, the SDA line must be monitored for arbitration to see if the signal level is the expected output level. This check is performed by hardware with the result placed in the BCL1IF bit.

The states where arbitration can be lost are:

- Address Transfer

- Data Transfer

- A Start Condition

- A Repeated Start Condition

- An Acknowledge Condition

## 26.6.13 MULTI -MASTER COMMUNICATION, BUS COLLISION AND BUS ARBITRATION

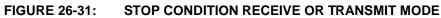

Multi-Master mode support is achieved by bus arbitration. When the master outputs address/data bits onto the SDA pin, arbitration takes place when the master outputs a '1' on SDA, by letting SDA float high and another master asserts a '0'. When the SCL pin floats high, data should be stable. If the expected data on SDA is a '1' and the data sampled on the SDA pin is '0', then a bus collision has taken place. The master will set the Bus Collision Interrupt Flag, BCL1IF and reset the I<sup>2</sup>C port to its Idle state (Figure 26-31).

If a transmit was in progress when the bus collision occurred, the transmission is halted, the BF flag is cleared, the SDA and SCL lines are deasserted and the SSPBUF can be written to. When the user services the bus collision Interrupt Service Routine and if the  $I^2C$  bus is free, the user can resume communication by asserting a Start condition.

If a Start, Repeated Start, Stop or Acknowledge condition was in progress when the bus collision occurred, the condition is aborted, the SDA and SCL lines are deasserted and the respective control bits in the SSPCON2 register are cleared. When the user services the bus collision Interrupt Service Routine and if the I<sup>2</sup>C bus is free, the user can resume communication by asserting a Start condition.

The master will continue to monitor the SDA and SCL pins. If a Stop condition occurs, the SSP1IF bit will be set.

A write to the SSPBUF will start the transmission of data at the first data bit, regardless of where the transmitter left off when the bus collision occurred.

In Multi-Master mode, the interrupt generation on the detection of Start and Stop conditions allows the determination of when the bus is free. Control of the  $I^2C$  bus can be taken when the P bit is set in the SSPSTAT register, or the bus is Idle and the S and P bits are cleared.

| R-0/0            | R-1/1                       | U-0                                | R/W-0/0         | R/W-0/0          | U-0              | R/W-0/0           | R/W-0/0       |  |

|------------------|-----------------------------|------------------------------------|-----------------|------------------|------------------|-------------------|---------------|--|

| ABDOVF           | RCIDL                       | —                                  | SCKP            | BRG16            | —                | WUE               | ABDEN         |  |

| bit 7            |                             |                                    |                 |                  |                  |                   | bit 0         |  |

|                  |                             |                                    |                 |                  |                  |                   |               |  |

| Legend:          |                             |                                    |                 |                  |                  |                   |               |  |

| R = Readable     | bit                         | W = Writable                       | bit             | U = Unimpler     | mented bit, rea  | d as '0'          |               |  |

| u = Bit is unch  | nanged                      | x = Bit is unk                     | nown            | -n/n = Value     | at POR and BO    | OR/Value at all o | ther Resets   |  |

| '1' = Bit is set |                             | '0' = Bit is cle                   | ared            |                  |                  |                   |               |  |

|                  |                             |                                    |                 |                  |                  |                   |               |  |

| bit 7            |                             | to-Baud Deteo                      | t Overflow bit  |                  |                  |                   |               |  |

|                  | Asynchronou                 |                                    |                 |                  |                  |                   |               |  |

|                  |                             | d timer overflo<br>d timer did not |                 |                  |                  |                   |               |  |

|                  | Synchronous                 |                                    | overnow         |                  |                  |                   |               |  |

|                  | Don't care                  |                                    |                 |                  |                  |                   |               |  |

| bit 6            | RCIDL: Rece                 | ive Idle Flag b                    | it              |                  |                  |                   |               |  |

|                  | <u>Asynchronou</u>          | <u>s mode</u> :                    |                 |                  |                  |                   |               |  |

|                  | 1 = Receiver                |                                    |                 |                  |                  |                   |               |  |

|                  |                             | as been receiv                     | ed and the re   | ceiver is receiv | ring             |                   |               |  |

|                  | Synchronous<br>Don't care   | <u>moue</u> .                      |                 |                  |                  |                   |               |  |

| bit 5            |                             | ted: Read as                       | 0'              |                  |                  |                   |               |  |

| bit 4            | -                           | nronous Clock                      |                 | bit              |                  |                   |               |  |

|                  | Asynchronou                 |                                    |                 |                  |                  |                   |               |  |

|                  |                             | inverted data t<br>non-inverted d  |                 |                  |                  |                   |               |  |

|                  | <u>Synchronous</u>          |                                    |                 |                  |                  |                   |               |  |

|                  |                             | ocked on rising<br>ocked on fallin |                 |                  |                  |                   |               |  |

| bit 3            |                             | it Baud Rate C                     |                 | JIUUK            |                  |                   |               |  |

| DIL 3            |                             | ud Rate Gene                       |                 |                  |                  |                   |               |  |

|                  |                             | id Rate Genera                     |                 |                  |                  |                   |               |  |

| bit 2            | Unimplemen                  | ted: Read as                       | 0'              |                  |                  |                   |               |  |

| bit 1            | WUE: Wake-                  | up Enable bit                      |                 |                  |                  |                   |               |  |

|                  | <u>Asynchronou</u>          | s mode:                            |                 |                  |                  |                   |               |  |

|                  | 1 = Receiver                | is waiting for a                   | a falling edge. | No character     | will be received | d, byte RCIF wil  | l be set. WUE |  |

|                  |                             | natically clear a                  |                 | et.              |                  |                   |               |  |

|                  | 0 = Receiver<br>Synchronous | is operating no                    | ormally         |                  |                  |                   |               |  |

|                  | Don't care                  | <u>moue</u> .                      |                 |                  |                  |                   |               |  |

| bit 0            |                             | o-Baud Detect                      | Enable bit      |                  |                  |                   |               |  |

|                  | ABDEN. Auto                 |                                    |                 |                  |                  |                   |               |  |

|                  | -                           |                                    | e is enabled (c | lears when au    | to-baud is com   | inlete)           |               |  |

|                  |                             | ud Detect mod                      |                 |                  |                  |                   |               |  |

|                  | Synchronous                 |                                    |                 |                  |                  |                   |               |  |

|                  | Don't care                  |                                    |                 |                  |                  |                   |               |  |

# REGISTER 27-3: BAUDCON: BAUD RATE CONTROL REGISTER

| MOVIW      | Move INDFn to W                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:    | [ <i>label</i> ] MOVIW ++FSRn<br>[ <i>label</i> ] MOVIWFSRn<br>[ <i>label</i> ] MOVIW FSRn++<br>[ <i>label</i> ] MOVIW FSRn<br>[ <i>label</i> ] MOVIW k[FSRn]                                                                                                                                                                                                                                                                                           |

| Operands:  | $\begin{array}{l} n \in [0,1] \\ mm \in [00,01,10,11] \\ -32 \leq k \leq 31 \end{array}$                                                                                                                                                                                                                                                                                                                                                                |

| Operation: | $\begin{split} &\text{INDFn} \rightarrow W \\ &\text{Effective address is determined by} \\ &\text{•} \ &\text{FSR + 1 (preincrement)} \\ &\text{•} \ &\text{FSR - 1 (predecrement)} \\ &\text{•} \ &\text{FSR + k (relative offset)} \\ &\text{After the Move, the FSR value will} \\ &\text{be either:} \\ &\text{•} \ &\text{FSR + 1 (all increments)} \\ &\text{•} \ &\text{FSR - 1 (all decrements)} \\ &\text{•} \ &\text{Unchanged} \end{split}$ |

Status Affected: Ζ

| Mode          | Syntax | mm |

|---------------|--------|----|

| Preincrement  | ++FSRn | 00 |

| Predecrement  | FSRn   | 01 |

| Postincrement | FSRn++ | 10 |

| Postdecrement | FSRn   | 11 |

Description:

This instruction is used to move data between W and one of the indirect registers (INDFn). Before/ after this move, the pointer (FSRn) is updated by pre/post incrementing/decrementing it.

**Note:** The INDFn registers are not physical registers. Any instruction that accesses an INDFn register actually accesses the register at the address specified by the FSRn.

FSRn is limited to the range 0000h - FFFFh. Incrementing/ decrementing it beyond these bounds will cause it to wraparound.

| MOVLB                | Move literal to BSR                                                  |

|----------------------|----------------------------------------------------------------------|

| Syntax:              | [ <i>label</i> ] MOVLB k                                             |

| Operands:            | $0 \le k \le 31$                                                     |

| Operation:           | $k \rightarrow BSR$                                                  |

| Status Affected:     | None                                                                 |

| Description:         | The 5-bit literal 'k' is loaded into the Bank Select Register (BSR). |

| MOVLP                | Move literal to PCLATH                                               |

|                      |                                                                      |

| Syntax:              | [ <i>label</i> ]MOVLP k                                              |

| Syntax:<br>Operands: | [ <i>label</i> ] MOVLP   k<br>0 ≤ k ≤ 127                            |

| 5                    |                                                                      |

| Operands:            | $0 \le k \le 127$                                                    |

| MOVLW            | Move literal to W                                                                         |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] MOVLW k                                                                  |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                         |  |  |  |  |

| Operation:       | $k \rightarrow (W)$                                                                       |  |  |  |  |

| Status Affected: | None                                                                                      |  |  |  |  |

| Description:     | The 8-bit literal 'k' is loaded into W register. The "don't cares" will assemble as '0's. |  |  |  |  |

| Words:           | 1                                                                                         |  |  |  |  |

| Cycles:          | 1                                                                                         |  |  |  |  |

| Example:         | MOVLW 0x5A                                                                                |  |  |  |  |

|                  | After Instruction<br>W = 0x5A                                                             |  |  |  |  |

| MOVWF            | Move W to f                                                                                               |

|------------------|-----------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVWF f                                                                                  |

| Operands:        | $0 \leq f \leq 127$                                                                                       |

| Operation:       | $(W) \rightarrow (f)$                                                                                     |

| Status Affected: | None                                                                                                      |

| Description:     | Move data from W register to register 'f'.                                                                |

| Words:           | 1                                                                                                         |

| Cycles:          | 1                                                                                                         |

| Example:         | MOVWF OPTION_REG                                                                                          |

|                  | Before Instruction<br>OPTION_REG = 0xFF<br>W = 0x4F<br>After Instruction<br>OPTION_REG = 0x4F<br>W = 0x4F |

# PIC16(L)F1784/6/7

## **30.4** Thermal Considerations

| Param<br>No. | Sym.      | Characteristic                         | Тур. | Units | Conditions                                               |

|--------------|-----------|----------------------------------------|------|-------|----------------------------------------------------------|

| TH01         | θJA       | Thermal Resistance Junction to Ambient | 60   | °C/W  | 28-pin SPDIP package                                     |

|              |           |                                        | 80   | °C/W  | 28-pin SOIC package                                      |

|              |           |                                        | 90   | °C/W  | 28-pin SSOP package                                      |

|              |           |                                        | 27.5 | °C/W  | 28-pin QFN 6x6mm package                                 |

|              |           |                                        | 47.2 | °C/W  | 40-pin DIP package                                       |

|              |           |                                        | 41   | °C/W  | 40-pin UQFN 5x5                                          |

|              |           |                                        | 46   | °C/W  | 44-pin TQFP package                                      |

|              |           |                                        | 24.4 | °C/W  | 44-pin QFN 8x8mm package                                 |

| ТН02 θ.j     | θJC       | Thermal Resistance Junction to Case    | 31.4 | °C/W  | 28-pin SPDIP package                                     |

|              |           |                                        | 24   | °C/W  | 28-pin SOIC package                                      |

|              |           |                                        | 24   | °C/W  | 28-pin SSOP package                                      |

|              |           |                                        | 24   | °C/W  | 28-pin QFN 6x6mm package                                 |

|              |           |                                        | 24.7 | °C/W  | 40-pin DIP package                                       |

|              |           |                                        | 5.5  | °C/W  | 40-pin UQFN 5x5                                          |

|              |           |                                        | 14.5 | °C/W  | 44-pin TQFP package                                      |

|              |           |                                        | 20   | °C/W  | 44-pin QFN 8x8mm package                                 |

| ГН03         | TJMAX     | Maximum Junction Temperature           | 150  | °C    |                                                          |

| ГН04         | PD        | Power Dissipation                      | _    | W     | PD = PINTERNAL + PI/O                                    |

| TH05         | PINTERNAL | Internal Power Dissipation             | _    | W     | PINTERNAL = IDD x VDD <sup>(1)</sup>                     |

| ГН06         | Pi/o      | I/O Power Dissipation                  | _    | W     | $PI/O = \Sigma (IOL * VOL) + \Sigma (IOH * (VDD - VOH))$ |

| ГН07         | Pder      | Derated Power                          | _    | W     | Pder = PDmax (Tj - Ta)/θja <sup>(2)</sup>                |

Standard Operating Conditions (unless otherwise stated)

**Note 1:** IDD is current to run the chip alone without driving any load on the output pins.

**2:** TA = Ambient Temperature

**3:** T<sub>J</sub> = Junction Temperature

## TABLE 30-17: DIGITAL-TO-ANALOG CONVERTER (DAC) SPECIFICATIONS

| Operating    | <b>Operating Conditions:</b> VDD = 3V, Temperature = 25°C (unless otherwise stated). |                              |      |         |       |       |          |  |  |

|--------------|--------------------------------------------------------------------------------------|------------------------------|------|---------|-------|-------|----------|--|--|

| Param<br>No. | Sym.                                                                                 | Characteristics              | Min. | Тур.    | Max.  | Units | Comments |  |  |

| DAC01*       | CLSB                                                                                 | Step Size                    | —    | VDD/256 |       | V     |          |  |  |

| DAC02*       | CACC                                                                                 | Absolute Accuracy            | _    | —       | ± 1.5 | LSb   |          |  |  |

| DAC03*       | CR                                                                                   | Unit Resistor Value (R)      | _    | 600     | _     | Ω     |          |  |  |

| DAC04*       | CST                                                                                  | Settling Time <sup>(1)</sup> | —    | —       | 10    | μS    |          |  |  |

\* These parameters are characterized but not tested.

**Note 1:** Settling time measured while DACR<7:0> transitions from '0x00' to '0xFF'.

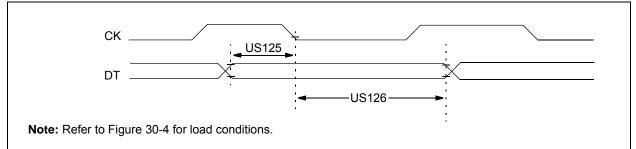

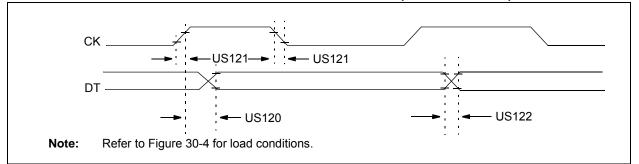

### FIGURE 30-14: EUSART SYNCHRONOUS TRANSMISSION (MASTER/SLAVE) TIMING

## TABLE 30-18: EUSART SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Standard Operating Conditions (unless otherwise stated) |                              |                                   |                |     |      |       |            |  |

|---------------------------------------------------------|------------------------------|-----------------------------------|----------------|-----|------|-------|------------|--|

| Param.<br>No.                                           | Symbol                       | Characteristic                    | Characteristic |     | Max. | Units | Conditions |  |

| US120                                                   | TCKH2DTV                     | SYNC XMIT (Master and Slave)      | 3.0-5.5V       | —   | 80   | ns    |            |  |

|                                                         | Clock high to data-out valid | 1.8-5.5V                          | _              | 100 | ns   |       |            |  |

| US121                                                   | TCKRF                        | Clock out rise time and fall time | 3.0-5.5V       | —   | 45   | ns    |            |  |

|                                                         |                              | (Master mode)                     | 1.8-5.5V       | —   | 50   | ns    |            |  |

| US122                                                   | TDTRF                        | Data-out rise time and fall time  | 3.0-5.5V       | —   | 45   | ns    |            |  |

|                                                         |                              |                                   | 1.8-5.5V       | _   | 50   | ns    |            |  |

## FIGURE 30-15: EUSART SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING