Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PSMC, PWM, WDT                                |

| Number of I/O              | 24                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 1K x 8                                                                     |

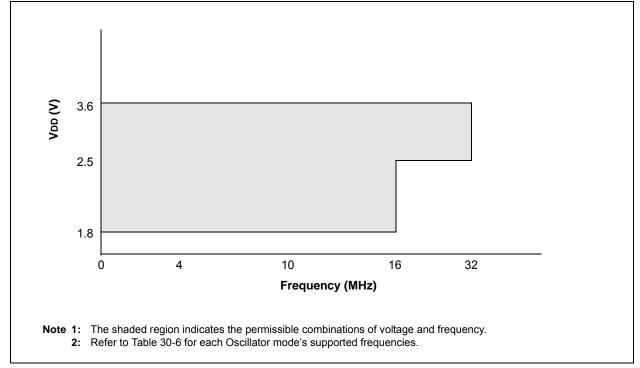

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 11x12b; D/A 1x8b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 28-SPDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1786-i-sp |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABL | E 2:        | 4           | 0/44-F      | PIN AL     | LOCA | TION TAB           | LE (PIC                              | 6(L)F17 | 84/7)     |                |                                  |                     |                                        |                                          |            |         |                        |

|------|-------------|-------------|-------------|------------|------|--------------------|--------------------------------------|---------|-----------|----------------|----------------------------------|---------------------|----------------------------------------|------------------------------------------|------------|---------|------------------------|

| 0]   | 40-Pin PDIP | 40-Pin UQFN | 44-Pin TQFP | 44-Pin QFN | ADC  | Reference          | Comparator                           | Op Amps | 8-bit DAC | Timers         | PSMC                             | ССР                 | EUSART                                 | dssm                                     | Interrupt  | dn-llnd | Basic                  |

| RA0  | 2           | 17          | 19          | 19         | AN0  | I                  | C1IN0-<br>C2IN0-<br>C3IN0-<br>C4IN0- | _       | _         |                | I                                | _                   |                                        |                                          | IOC        | Y       | -                      |

| RA1  | 3           | 18          | 20          | 20         | AN1  | _                  | C1IN1-<br>C2IN1-<br>C3IN1-<br>C4IN1- | OPA1OUT | _         |                | _                                | _                   | _                                      | _                                        | IOC        | Y       |                        |

| RA2  | 4           | 19          | 21          | 21         | AN2  | DAC1VREF-<br>VREF- | C1IN0+<br>C2IN0+<br>C3IN0+<br>C4IN0+ |         | DAC1OUT1  | _              | _                                | -                   | _                                      | _                                        | IOC        | Y       | _                      |

| RA3  | 5           | 20          | 22          | 22         | AN3  | DAC1VREF+<br>VREF+ | C1IN1+                               | -       | —         | _              | _                                | —                   | _                                      | _                                        | IOC        | Y       | _                      |

| RA4  | 6           | 21          | 23          | 23         | —    | _                  | C10UT                                | OPA1IN+ |           | T0CKI          | _                                | —                   | -                                      | _                                        | IOC        | Y       | _                      |

| RA5  | 7           | 22          | 24          | 24         | AN4  |                    | C2OUT                                | OPA1IN- | _         | _              |                                  | —                   | _                                      | SS                                       | IOC        | Y       | _                      |

| RA6  | 14          | 29          | 31          | 33         | _    |                    | C2OUT <sup>(1)</sup>                 | _       | _         | _              |                                  | _                   |                                        |                                          | IOC        | Y       | VCAP<br>CLKOUT<br>OSC2 |

| RA7  | 13          | 28          | 30          | 32         | _    |                    |                                      | —       | _         |                | PSMC1CLK<br>PSMC2CLK<br>PSMC3CLK | —                   |                                        |                                          | IOC        | Y       | CLKIN<br>OSC1          |

| RB0  | 33          | 8           | 8           | 9          | AN12 |                    | C2IN1+                               | —       | —         | _              | PSMC1IN<br>PSMC2IN<br>PSMC3IN    | CCP1 <sup>(1)</sup> |                                        |                                          | INT<br>IOC | Y       | _                      |

| RB1  | 34          | 9           | 9           | 10         | AN10 | _                  | C1IN3-<br>C2IN3-<br>C3IN3-<br>C4IN3- | OPA2OUT | _         | _              | _                                | _                   | _                                      | _                                        | IOC        | Y       |                        |

| RB2  | 35          | 10          | 10          | 11         | AN8  | —                  | —                                    | OPA2IN- | —         | —              | —                                | —                   | —                                      | —                                        | IOC        | Y       | CLKR                   |

| RB3  | 36          | 11          | 11          | 12         | AN9  |                    | C1IN2-<br>C2IN2-<br>C3IN2-           | OPA2IN+ | —         | _              | _                                | CCP2 <sup>(1)</sup> |                                        |                                          | IOC        | Y       | _                      |

| RB4  | 37          | 12          | 14          | 14         | AN11 |                    | C3IN1+                               | -       | —         | _              |                                  | —                   |                                        |                                          | IOC        | Y       |                        |

| RB5  | 38          | 13          | 15          | 15         | AN13 | _                  | C4IN2-                               | —       | —         | T1G            |                                  | CCP3 <sup>(1)</sup> |                                        | SDO <sup>(1)</sup>                       | IOC        | Y       |                        |

| RB6  | 39          | 14          | 16          | 16         | -    | —                  | C4IN1+                               | —       | _         | _              | _                                | —                   | TX <sup>(1)</sup><br>CK <sup>(1)</sup> | SDA <sup>(1)</sup><br>SDI <sup>(1)</sup> | IOC        | Y       | ICSPCLK                |

| RB7  | 40          | 15          | 17          | 17         | -    | _                  | _                                    | _       | DAC1OUT2  | _              | _                                | —                   | RX <sup>(1)</sup><br>DT <sup>(1)</sup> | SCL <sup>(1)</sup><br>SCK <sup>(1)</sup> | IOC        | Y       | ICSPDAT                |

| RC0  | 15          | 30          | 32          | 34         |      |                    | _                                    | _       | -         | T1CKI<br>T1OSO | PSMC1A                           | —                   | —                                      | —                                        | IOC        | Y       | —                      |

## 40/44-PIN ALLOCATION TABLE (PIC16(L)E1784/7)

Note 1: Alternate pin function selected with the APFCON1 (Register 13-1) and APFCON2 (Register 13-2) registers.

PIC16(L)F1782/3

| IAD                | LE 3-12.             | SPECIAL        | FUNCTIC           | IN REGIS         | IER SUMM          |                         |                           |                       |                    |                      |                                 |

|--------------------|----------------------|----------------|-------------------|------------------|-------------------|-------------------------|---------------------------|-----------------------|--------------------|----------------------|---------------------------------|

| Addr               | Name                 | Bit 7          | Bit 6             | Bit 5            | Bit 4             | Bit 3                   | Bit 2                     | Bit 1                 | Bit 0              | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

| Banl               | k 0                  |                |                   |                  |                   |                         |                           |                       |                    |                      | •                               |

| 00Ch               | PORTA                | PORTA Data L   | atch when wr      | itten: PORTA p   | ins when read     |                         |                           |                       |                    | xxxx xxxx            | uuuu uuuu                       |

| 00Dh               | PORTB                | PORTB Data L   | atch when wi      | itten: PORTB p   | oins when read    |                         |                           |                       |                    | xxxx xxxx            | uuuu uuuu                       |

| 00Eh               | PORTC                | PORTC Data L   | _atch when w      | ritten: PORTC p  | oins when read    |                         |                           |                       |                    | xxxx xxxx            | uuuu uuuu                       |

| 00Fh               | PORTD <sup>(3)</sup> | PORTD Data L   | _atch when w      | ritten: PORTD p  | oins when read    |                         |                           |                       |                    | xxxx xxxx            | uuuu uuuu                       |

| 010h               | PORTE                | _              |                   | _                | _                 | RE3                     | RE2 <sup>(3)</sup>        | RE1 <sup>(3)</sup>    | RE0 <sup>(3)</sup> | xxxx                 | uuuu                            |

| 011h               | PIR1                 | TMR1GIF        | ADIF              | RCIF             | TXIF              | SSP1IF                  | CCP1IF                    | TMR2IF                | TMR1IF             | 0000 0000            | 0000 0000                       |

| 012h               | PIR2                 | OSFIF          | C2IF              | C1IF             | EEIF              | BCL1IF                  | C4IF                      | C3IF                  | CCP2IF             | 0000 0-00            | 0000 0-00                       |

| 13h                | PIR3                 | _              | _                 | _                | CCP3IF            | _                       | _                         | _                     | _                  | 0                    | 0000 0000                       |

| 014h               | PIR4                 |                | PSMC3TIF          | PSMC2TIF         | PSMC1TIF          | _                       | PSMC3SIF                  | PSMC2SIF              | PSMC1SIF           | -000 -000            | -000 -000                       |

| 015h               | TMR0                 | Timer0 Module  |                   |                  |                   |                         |                           |                       |                    | xxxx xxxx            | uuuu uuuu                       |

| 016h               | TMR1L                |                |                   | st Significant B | yte of the 16-bi  | t TMR1 Regist           | er                        |                       |                    | xxxx xxxx            | uuuu uuuu                       |

| 017h               | TMR1H                |                |                   | •                | yte of the 16-bit | •                       |                           |                       |                    | XXXX XXXX            | uuuu uuuu                       |

| 018h               | T1CON                | TMR1CS1        | TMR1CS0           | T1CKPS1          | T1CKPS0           | T10SCEN                 | TISYNC                    | _                     | TMR10N             | 0000 00-0            | uuuu uu-u                       |

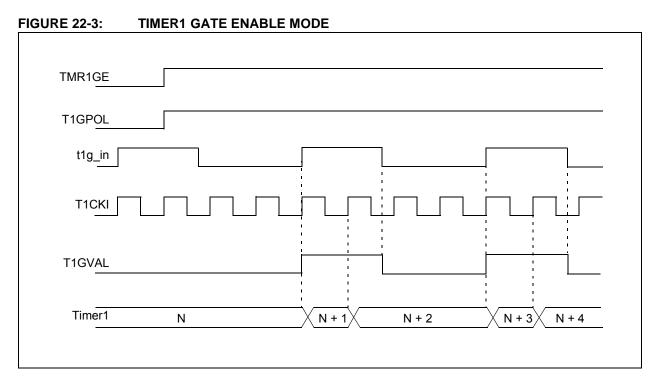

| 019h               | T1GCON               | TMR1GE         | T1GPOL            | T1GTM            | T1GSPM            | T <u>1GGO</u> /<br>DONE | T1GVAL                    | T1GS                  | S<1:0>             | 0000 0x00            | uuuu uxuu                       |

| 016h               | TMR2                 | Holding Dogist | for for the Log   | at Significant P | yte of the 16-bi  | -                       | or                        |                       |                    |                      |                                 |

|                    |                      |                |                   |                  |                   |                         |                           |                       |                    | XXXX XXXX            | uuuu uuuu                       |

| 017h               | PR2                  | Holding Regist | ter for the ivios | · ·              | te of the 16-bit  | TIVIRZ Registe          | 1                         | TOOLO                 | 0.10               | XXXX XXXX            | uuuu uuuu                       |

| 018h               | T2CON                |                |                   | 12001            | PS<3:0>           |                         | TMR2ON                    | T2CKP                 | PS<1:0>            | -000 0000            | -000 0000                       |

| 01Dh<br>to<br>01Fh | _                    | Unimplemente   | d                 |                  |                   |                         |                           |                       |                    | -                    | -                               |

| Ban                | k 1                  |                |                   |                  |                   |                         |                           |                       |                    |                      |                                 |

| 08Ch               | TRISA                | PORTA Data D   | Direction Regi    | ster             |                   |                         |                           |                       |                    | 1111 1111            | 1111 1111                       |

| 08Dh               | TRISB                | PORTB Data     | Direction Regi    | ster             |                   |                         |                           |                       |                    | 1111 1111            | 1111 1111                       |

| 08Eh               | TRISC                | PORTC Data     |                   |                  |                   |                         |                           |                       |                    | 1111 1111            | 1111 1111                       |

| 08Fh               | TRISD <sup>(3)</sup> | PORTD Data     |                   |                  |                   |                         |                           |                       |                    | 1111 1111            |                                 |

| 090h               | TRISE                | _              | _                 | _                | _                 | (2)                     | TRISE2 <sup>(3)</sup>     | TRISE1 <sup>(3)</sup> | TRISE0(3)          | 1111                 | 1111                            |

| 091h               | PIE1                 | TMR1GIE        | ADIE              | RCIE             | TXIE              | SSP1IE                  | CCP1IE                    | TMR2IE                | TMR1IE             | 0000 0000            |                                 |

| 092h               | PIE2                 | OSFIE          | C2IE              | C1IE             | EEIE              | BCL1IE                  | C4IE                      | C3IE                  | CCP2IE             | 0000 0-00            |                                 |

| 093h               | PIE3                 | _              | _                 | _                | CCP3IE            | _                       | _                         | _                     | _                  | 0                    | 0000 0000                       |

| 094h               | PIE4                 | _              | PSMC3TIE          | PSMC2TIE         | PSMC1TIE          | _                       | PSMC3SIE                  | PSMC2SIE              | PSMC1SIE           | -000 -000            | -000 -000                       |

| 095h               | OPTION_REG           | WPUEN          | INTEDG            | TMR0CS           | TMR0SE            | PSA                     |                           | PS<2:0>               |                    | 1111 1111            |                                 |

| 096h               | PCON                 | STKOVF         | STKUNF            | _                | RWDT              | RMCLR                   | RI                        | POR                   | BOR                | 00-1 11qq            |                                 |

| 097h               | WDTCON               | _              | _                 |                  |                   | NDTPS<4:0>              |                           |                       | SWDTEN             | 01 0110              |                                 |

| 098h               | OSCTUNE              |                |                   |                  |                   | TUN<                    | 5:0>                      |                       | ONDIEN             |                      | 00 0000                         |

| 099h               | OSCCON               | SPLLEN         |                   | IRCE             | -<3:0>            |                         |                           | SCS                   | <1:0>              |                      | 0011 1-00                       |

| 09Ah               | OSCSTAT              | T10SCR         | PLLR              | OSTS             | HFIOFR            | HFIOFL                  | MFIOFR                    | LFIOFR                | HFIOFS             | 00q000               | -                               |

| 09An               | ADRESL               | A/D Result Re  |                   | 0010             |                   |                         |                           |                       | 1111010            | xxxx xxxx            | uuuu uuuu                       |

| 09Bh               | ADRESH               | A/D Result Re  | •                 |                  |                   |                         |                           |                       |                    |                      |                                 |

|                    | ADRESH<br>ADCON0     |                | giater i Tigri    |                  | 040-4.0           |                         |                           |                       | ADON               | XXXX XXXX            |                                 |

| 09Dh               |                      | ADRMD          |                   | 1000-00-0        | CHS<4:0>          |                         |                           | GO/DONE               |                    | 0000 0000            |                                 |

| 09Eh               | ADCON1               | ADFM           | TDIOO             | ADCS<2:0>        |                   | _                       | ADNREF                    |                       | EF<1:0>            | 0000 -000            |                                 |

| 09Fh               | ADCON2               |                | TRIGS             | EL<3:0>          |                   |                         | CHSN<br>d, read as '0', r | 153:02                |                    | 000000               | 000000                          |

#### **TABLE 3-12**: SPECIAL FUNCTION REGISTER SUMMARY

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'. Legend:

These registers can be addressed from any bank. Unimplemented, read as '1'. PIC16(L)F1784/7 only. Note 1:

2:

3:

PIC16F1784/6/7 only. 4:

#### SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED) **TABLE 3-12:**

| IABI     | ABLE 3-12: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED) |                 |              |           |           |          |                |          |         |                   |                                 |  |  |

|----------|----------------------------------------------------------|-----------------|--------------|-----------|-----------|----------|----------------|----------|---------|-------------------|---------------------------------|--|--|

| Addr     | Name                                                     | Bit 7           | Bit 6        | Bit 5     | Bit 4     | Bit 3    | Bit 2          | Bit 1    | Bit 0   | Value on POR, BOR | Value on<br>all other<br>Resets |  |  |

| Ban      | k 16                                                     |                 |              |           |           |          |                |          |         |                   |                                 |  |  |

| 80Ch     |                                                          |                 |              |           |           |          |                |          |         |                   |                                 |  |  |

| <br>810h | _                                                        | Unimplemente    | a            |           |           |          |                |          |         | _                 | _                               |  |  |

| 811h     | PSMC1CON                                                 | PSMC1EN         | PSMC1LD      | PSMC1DBFE | PSMC1DBRE |          | P1MOD          | )E<3:0>  |         | 0000 0000         | 0000 0000                       |  |  |

| 812h     | PSMC1MDL                                                 | P1MDLEN         | P1MDLPOL     | P1MDLBIT  | —         |          | P1MSR          | C<3:0>   |         | 000- 0000         | 000- 0000                       |  |  |

| 813h     | PSMC1SYNC                                                | P1POFST         | P1PRPOL      | P1DCPOL   | —         | —        | —              | P1SYN    | IC<1:0> | 00000             | 00000                           |  |  |

| 814h     | PSMC1CLK                                                 | —               | _            | P1CPF     | RE<1:0>   | _        | _              | P1CSR    | RC<1:0> | 0000              | 0000                            |  |  |

| 815h     | PSMC10EN                                                 | —               | _            | P10EF     | P10EE     | P10ED    | P10EC          | P10EB    | P10EA   | 00 0000           | 00 0000                         |  |  |

| 816h     | PSMC1POL                                                 | _               | P1INPOL      | P1POLF    | P1POLE    | P1POLD   | P1POLC         | P1POLB   | P1POLA  | -000 0000         | -000 0000                       |  |  |

| 817h     | PSMC1BLNK                                                | _               | _            | P1FEB     | M<1:0>    | _        | _              | P1REB    | M<1:0>  | 0000              | 0000                            |  |  |

| 818h     | PSMC1REBS                                                | P1REBIN         | —            | —         | P1REBSC4  | P1REBSC3 | P1REBSC2       | P1REBSC1 | —       | 00 000-           | 00 000-                         |  |  |

| 819h     | PSMC1FEBS                                                | P1FEBIN         | —            | —         | P1FEBSC4  | P1FEBSC3 | P1FEBSC2       | P1FEBSC1 | —       | 00 000-           | 00 000-                         |  |  |

| 81Ah     | PSMC1PHS                                                 | P1PHSIN         | —            | —         | P1PHSC4   | P1PHSC3  | P1PHSC2        | P1PHSC1  | P1PHST  | 00 0000           | 00 0000                         |  |  |

| 81Bh     | PSMC1DCS                                                 | P1DCSIN         | _            | _         | P1DCSC4   | P1DCSC3  | P1DCSC2        | P1DCSC1  | P1DCST  | 00 0000           | 00 0000                         |  |  |

| 81Ch     | PSMC1PRS                                                 | P1PRSIN         | —            | -         | P1PRSC4   | P1PRSC3  | P1PRSC2        | P1PRSC1  | P1PRST  | 00 0000           | 00 0000                         |  |  |

| 81Dh     | PSMC1ASDC                                                | P1ASE           | P1ASDEN      | P1ARSEN   | —         | —        | —              | —        | P1ASDOV | 0000              | 0000                            |  |  |

| 81Eh     | PSMC1ASDL                                                | _               | _            | P1ASDLF   | P1ASDLE   | P1ASDLD  | P1ASDLC        | P1ASDLB  | P1ASDLA | 00 0000           | 00 0000                         |  |  |

| 81Fh     | PSMC1ASDS                                                | P1ASDSIN        | —            | _         | P1ASDSC4  | P1ASDSC3 | P1ASDSC2       | P1ASDSC1 | _       | 00 000-           | 00 000-                         |  |  |

| 820h     | PSMC1INT                                                 | P1TOVIE         | P1TPHIE      | P1TDCIE   | P1TPRIE   | P1TOVIF  | P1TPHIF        | P1TDCIF  | P1TPRIF | 0000 0000         | 0000 0000                       |  |  |

| 821h     | PSMC1PHL                                                 | Phase Low Co    | unt          |           |           |          |                |          |         | 0000 0000         | 0000 0000                       |  |  |

| 822h     | PSMC1PHH                                                 | Phase High Co   |              |           |           |          |                |          |         | 0000 0000         | 0000 0000                       |  |  |

| 823h     | PSMC1DCL                                                 | Duty Cycle Lov  | w Count      |           |           |          |                |          |         | 0000 0000         | 0000 0000                       |  |  |

| 824h     | PSMC1DCH                                                 | Duty Cycle Hig  | ·            |           |           |          |                |          |         | 0000 0000         | 0000 0000                       |  |  |

| 825h     | PSMC1PRL                                                 | Period Low Co   |              |           |           |          |                |          |         | 0000 0000         | 0000 0000                       |  |  |

| 826h     | PSMC1PRH                                                 | Period High Co  |              |           |           |          |                |          |         | 0000 0000         | 0000 0000                       |  |  |

| 827h     | PSMC1TMRL                                                | Time base Lov   |              |           |           |          |                |          |         | 0000 0001         | 0000 0001                       |  |  |

| 828h     | PSMC1TMRH                                                | Time base Hig   |              |           |           |          |                |          |         | 0000 0000         | 0000 0000                       |  |  |

| 829h     | PSMC1DBR                                                 | rising Edge De  |              |           |           |          |                |          |         | 0000 0000         | 0000 0000                       |  |  |

| 82Ah     | PSMC1DBF                                                 | Falling Edge D  |              |           |           |          |                |          |         | 0000 0000         | 0000 0000                       |  |  |

| 82Bh     | PSMC1BLKR                                                | rising Edge Bla | -            |           |           |          |                |          |         | 0000 0000         | 0000 0000                       |  |  |

| 82Ch     | PSMC1BLKF                                                | Falling Edge B  | lanking Coun |           |           |          |                |          |         | 0000 0000         | 0000 0000                       |  |  |

| 82Dh     | PSMC1FFA                                                 | —               | —            | _         | _         |          | tional Frequer |          |         | 0000              | 0000                            |  |  |

| 82Eh     | PSMC1STR0                                                | _               | —            | P1STRF    | P1STRE    | P1STRD   | P1STRC         | P1STRB   | P1STRA  | 00 0001           | 00 0001                         |  |  |

| 82Fh     | PSMC1STR1                                                | P1SYNC          | —            | —         | —         | —        | —              | P1LSMEN  | P1HSMEN | 000               | 000                             |  |  |

| 830h     | —                                                        | Unimplemente    | d            |           |           |          |                |          |         | —                 | —                               |  |  |

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'. These registers can be addressed from any bank. Unimplemented, read as '1'. Legend:

Note

1: 2:

PIC16(L)F1784/7 only.

3:

4: PIC16F1784/6/7 only.

| TABLE 3-12: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED) |                |                 |               |           |           |          |                |                |         |                      |                                 |

|-----------------------------------------------------------|----------------|-----------------|---------------|-----------|-----------|----------|----------------|----------------|---------|----------------------|---------------------------------|

| Addr                                                      | Name           | Bit 7           | Bit 6         | Bit 5     | Bit 4     | Bit 3    | Bit 2          | Bit 1          | Bit 0   | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

| Bank                                                      | 16 (Continued) | )               |               |           | •         |          |                |                |         |                      |                                 |

| 831h                                                      | PSMC2CON       | PSMC2EN         | PSMC2LD       | PSMC2DBFE | PSMC2DBRE |          | P2MOE          | )E<3:0>        |         | 0000 0000            | 0000 0000                       |

| 832h                                                      | PSMC2MDL       | P2MDLEN         | P2MDLPOL      | P2MDLBIT  | _         |          | P2MSR          | C<3:0>         |         | 000- 0000            | 000- 0000                       |

| 833h                                                      | PSMC2SYNC      | P2POFST         | P2PRPOL       | P2DCPOL   | _         | —        | _              | P2SYN          | C<1:0>  | 00000                | 00000                           |

| 834h                                                      | PSMC2CLK       | —               | _             | P2CPF     | RE<1:0>   | —        | —              | P2CSR          | C<1:0>  | 0000                 | 0000                            |

| 835h                                                      | PSMC2OEN       | _               | _             | _         | —         | _        | _              | P2OEB          | P2OEA   | 00                   | 00                              |

| 836h                                                      | PSMC2POL       | —               | P2INPOL       | —         | —         | —        | —              | P2POLB         | P2POLA  | -000                 | -000                            |

| 837h                                                      | PSMC2BLNK      | —               | —             | P2FEB     | M<1:0>    | —        | —              | P2REB          | M<1:0>  | 0000                 | 0000                            |

| 838h                                                      | PSMC2REBS      | P2REBIN         | _             | —         | P2REBSC4  | P2REBSC3 | P2REBSC2       | P2REBSC1       | _       | 00 000-              | 00 000-                         |

| 839h                                                      | PSMC2FEBS      | P2FEBIN         | _             | —         | P2FEBSC4  | P2FEBSC3 | P2FEBSC2       | P2FEBSC1       | _       | 00 000-              | 00 000-                         |

| 83Ah                                                      | PSMC2PHS       | P2PHSIN         | _             | —         | P2PHSC4   | P2PHSC3  | P2PHSC2        | P2PHSC1        | P2PHST  | 00 0000              | 00 0000                         |

| 83Bh                                                      | PSMC2DCS       | P2DCSIN         | _             | —         | P2DCSC4   | P2DCSC3  | P2DCSC2        | P2DCSC1        | P2DCST  | 00 0000              | 00 0000                         |

| 83Ch                                                      | PSMC2PRS       | P2PRSIN         | —             | —         | P2PRSC4   | P2PRSC3  | P2PRSC2        | P2PRSC1        | P2PRST  | 00 0000              | 00 0000                         |

| 83Dh                                                      | PSMC2ASDC      | P2ASE           | P2ASDEN       | P2ARSEN   | —         | _        | _              | _              | P2ASDOV | 0000                 | 0000                            |

| 83Eh                                                      | PSMC2ASDL      | —               | _             | P2ASDLF   | P2ASDLE   | P2ASDLD  | P2ASDLC        | P2ASDLB        | P2ASDLA | 00 0000              | 00 0000                         |

| 83Fh                                                      | PSMC2ASDS      | P2ASDSIN        | _             | —         | P2ASDSC4  | P2ASDSC3 | P2ASDSC2       | P2ASDSC1       | —       | 00 000-              | 00 000-                         |

| 840h                                                      | PSMC2INT       | P2TOVIE         | P2TPHIE       | P2TDCIE   | P2TPRIE   | P2TOVIF  | P2TPHIF        | P2TDCIF        | P2TPRIF | 0000 0000            | 0000 0000                       |

| 841h                                                      | PSMC2PHL       | Phase Low Co    | unt           |           |           |          |                |                |         | 0000 0000            | 0000 0000                       |

| 842h                                                      | PSMC2PHH       | Phase High Co   | ount          |           |           |          |                |                |         | 0000 0000            | 0000 0000                       |

| 843h                                                      | PSMC2DCL       | Duty Cycle Lov  | w Count       |           |           |          |                |                |         | 0000 0000            | 0000 0000                       |

| 844h                                                      | PSMC2DCH       | Duty Cycle Hig  | gh Count      |           |           |          |                |                |         | 0000 0000            | 0000 0000                       |

| 845h                                                      | PSMC2PRL       | Period Low Co   | ount          |           |           |          |                |                |         | 0000 0000            | 0000 0000                       |

| 846h                                                      | PSMC2PRH       | Period High Co  | ount          |           |           |          |                |                |         | 0000 0000            | 0000 0000                       |

| 847h                                                      | PSMC2TMRL      | Time base Lov   | v Counter     |           |           |          |                |                |         | 0000 0001            | 0000 0001                       |

| 848h                                                      | PSMC2TMRH      | Time base Hig   | h Counter     |           |           |          |                |                |         | 0000 0000            | 0000 0000                       |

| 849h                                                      | PSMC2DBR       | rising Edge De  | ad-band Cou   | nter      |           |          |                |                |         | 0000 0000            | 0000 0000                       |

| 84Ah                                                      | PSMC2DBF       | Falling Edge D  | ead-band Co   | unter     |           |          |                |                |         | 0000 0000            | 0000 0000                       |

| 84Bh                                                      | PSMC2BLKR      | rising Edge Bla | anking Counte | er        |           |          |                |                |         | 0000 0000            | 0000 0000                       |

| 84Ch                                                      | PSMC2BLKF      | Falling Edge B  | lanking Coun  | ter       |           | r        |                |                |         | 0000 0000            | 0000 0000                       |

| 84Dh                                                      | PSMC2FFA       | —               | —             | —         | —         | Frac     | tional Frequer | icy Adjust Reg | ister   | 0000                 | 0000                            |

| 84Eh                                                      | PSMC2STR0      | —               | —             | —         | —         | —        | —              | P2STRB         | P2STRA  | 01                   | 01                              |

| 84Fh                                                      | PSMC2STR1      | P2SYNC          | —             | —         | -         | —        | —              | P2LSMEN        | P2HSMEN | 000                  | 000                             |

| 850h                                                      | _              | Unimplemente    | d             |           |           |          |                |                |         | —                    | -                               |

TABLE 3-12: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Legend:

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

**Note 1:** These registers can be addressed from any bank.

2: Unimplemented, read as '1'.

3: PIC16(L)F1784/7 only.

4: PIC16F1784/6/7 only.

## 11.1 Independent Clock Source

The WDT derives its time base from the 31 kHz LFINTOSC internal oscillator. Time intervals in this chapter are based on a nominal interval of 1 ms. See **Section 30.0 "Electrical Specifications**" for the LFINTOSC tolerances.

# 11.2 WDT Operating Modes

The Watchdog Timer module has four operating modes controlled by the WDTE<1:0> bits in Configuration Words. See Table 11-1.

#### 11.2.1 WDT IS ALWAYS ON

When the WDTE bits of Configuration Words are set to '11', the WDT is always on.

WDT protection is active during Sleep.

#### 11.2.2 WDT IS OFF IN SLEEP

When the WDTE bits of Configuration Words are set to '10', the WDT is on, except in Sleep.

WDT protection is not active during Sleep.

#### 11.2.3 WDT CONTROLLED BY SOFTWARE

When the WDTE bits of Configuration Words are set to '01', the WDT is controlled by the SWDTEN bit of the WDTCON register.

WDT protection is unchanged by Sleep. See Table 11-1 for more details.

| WDTE<1:0> | SWDTEN | Device<br>Mode | WDT<br>Mode |  |

|-----------|--------|----------------|-------------|--|

| 11        | х      | Х              | Active      |  |

| 10        |        | Awake          | Active      |  |

| 10        | Х      | Sleep          | Disabled    |  |

| 0.1       | 1      | х              | Active      |  |

| 01        | 0      | ~              | Disabled    |  |

| 00        | х      | Х              | Disabled    |  |

## TABLE 11-2: WDT CLEARING CONDITIONS

#### 11.3 Time-Out Period

The WDTPS bits of the WDTCON register set the time-out period from 1 ms to 256 seconds (nominal). After a Reset, the default time-out period is two seconds.

# 11.4 Clearing the WDT

The WDT is cleared when any of the following conditions occur:

- Any Reset

- CLRWDT instruction is executed

- Device enters Sleep

- · Device wakes up from Sleep

- · Oscillator fail

- · WDT is disabled

- Oscillator Start-up TImer (OST) is running

See Table 11-2 for more information.

## 11.5 Operation During Sleep

When the device enters Sleep, the WDT is cleared. If the WDT is enabled during Sleep, the WDT resumes counting.

When the device exits Sleep, the WDT is cleared again. The WDT remains clear until the OST, if enabled, completes. See **Section 6.0** "Oscillator **Module (with Fail-Safe Clock Monitor)**" for more information on the OST.

When a WDT time-out occurs while the device is in Sleep, no Reset is generated. Instead, the device wakes up and resumes operation. The TO and PD bits in the STATUS register are changed to indicate the event. See **Section 3.0** "**Memory Organization**" and Status Register (Register 3-1) for more information.

| WDT                          |  |  |  |

|------------------------------|--|--|--|

|                              |  |  |  |

|                              |  |  |  |

| Cleared                      |  |  |  |

| Cleared                      |  |  |  |

|                              |  |  |  |

|                              |  |  |  |

| Cleared until the end of OST |  |  |  |

| Unaffected                   |  |  |  |

|                              |  |  |  |

# 13.0 I/O PORTS

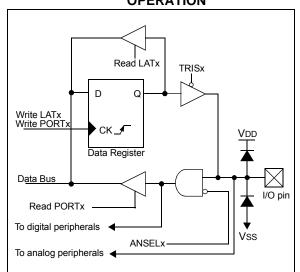

Each port has three standard registers for its operation. These registers are:

- TRISx registers (data direction)

- PORTx registers (reads the levels on the pins of the device)

- LATx registers (output latch)

Some ports may have one or more of the following additional registers. These registers are:

- ANSELx (analog select)

- WPUx (weak pull-up)

In general, when a peripheral is enabled on a port pin, that pin cannot be used as a general purpose output. However, the pin can still be read.

## TABLE 13-1: PORT AVAILABILITY PER DEVICE

| Device          | PORTA | PORTB | PORTC | PORTD | PORTE |

|-----------------|-------|-------|-------|-------|-------|

| PIC16(L)F1786   | •     | •     | •     |       | •     |

| PIC16(L)F1784/7 | ٠     | ٠     | •     | •     | •     |

The Data Latch (LATx registers) is useful for read-modify-write operations on the value that the I/O pins are driving.

A write operation to the LATx register has the same effect as a write to the corresponding PORTx register. A read of the LATx register reads of the values held in the I/O PORT latches, while a read of the PORTx register reads the actual I/O pin value.

Ports that support analog inputs have an associated ANSELx register. When an ANSEL bit is set, the digital input buffer associated with that bit is disabled. Disabling the input buffer prevents analog signal levels on the pin between a logic high and low from causing excessive current in the logic input circuitry. A simplified model of a generic I/O port, without the interfaces to other peripherals, is shown in Figure 13-1.

## FIGURE 13-1: GENERIC I/O PORT OPERATION

| Name    | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------------------|

| ANSELD  |         |         | -       | -       | —       | ANSD2   | ANSD1   | ANSD0   | 147                 |

| INLVLD  | INLVLD7 | INLVLD6 | INLVLD5 | INLVLD4 | INLVLD3 | INLVLD2 | INLVLD1 | INLVLD0 | 148                 |

| LATD    | LATD7   | LATD6   | LATD5   | LATD4   | LATD3   | LATD2   | LATD1   | LATD0   | 146                 |

| ODCOND  | ODD7    | ODD6    | ODD5    | ODD4    | ODD3    | ODD2    | ODD1    | ODD0    | 148                 |

| PORTD   | RD7     | RD6     | RD5     | RD4     | RD3     | RD2     | RD1     | RD0     | 146                 |

| SLRCOND | SLRD7   | SLRD6   | SLRD5   | SLRD4   | SLRD3   | SLRD2   | SLRD1   | SLRD0   | 148                 |

| TRISD   | TRISD7  | TRISD6  | TRISD5  | TRISD4  | TRISD3  | TRISD2  | TRISD1  | TRISD0  | 146                 |

| WPUD    | WPUD7   | WPUD6   | WPUD5   | WPUD4   | WPUD3   | WPUD2   | WPUD1   | WPUD0   | 147                 |

TABLE 13-10: SUMMARY OF REGISTERS ASSOCIATED WITH PORTD

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTD.

# 14.6 Register Definitions: Interrupt-on-Change Control

#### **REGISTER 14-1: IOCxP: INTERRUPT-ON-CHANGE POSITIVE EDGE REGISTER**

| R/W-0/0          | R/W-0/0                                 | R/W-0/0           | R/W-0/0 | R/W-0/0                            | R/W-0/0                                               | R/W-0/0 | R/W-0/0 |  |  |  |  |

|------------------|-----------------------------------------|-------------------|---------|------------------------------------|-------------------------------------------------------|---------|---------|--|--|--|--|

| IOCxP7           | IOCxP6                                  | IOCxP5            | IOCxP4  | IOCxP3                             | IOCxP2                                                | IOCxP1  | IOCxP0  |  |  |  |  |

| bit 7            |                                         |                   |         |                                    |                                                       |         | bit 0   |  |  |  |  |

|                  |                                         |                   |         |                                    |                                                       |         |         |  |  |  |  |

| Legend:          |                                         |                   |         |                                    |                                                       |         |         |  |  |  |  |

| R = Readable     | bit                                     | W = Writable      | bit     | U = Unimplemented bit, read as '0' |                                                       |         |         |  |  |  |  |

| u = Bit is uncha | u = Bit is unchanged x = Bit is unknown |                   |         |                                    | -n/n = Value at POR and BOR/Value at all other Resets |         |         |  |  |  |  |

| '1' = Bit is set |                                         | '0' = Bit is clea | ared    |                                    |                                                       |         |         |  |  |  |  |

bit 7-0 IOCxP<7:0>: Interrupt-on-Change Positive Edge Enable bits<sup>(1)</sup>

- 1 = Interrupt-on-Change enabled on the pin for a positive going edge. Associated Status bit and interrupt flag will be set upon detecting an edge.

- 0 = Interrupt-on-Change disabled for the associated pin.

Note 1: For IOCEP register, bit 3 (IOCEP3) is the only implemented bit in the register.

# REGISTER 14-2: IOCxN: INTERRUPT-ON-CHANGE NEGATIVE EDGE REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| IOCxN7  | IOCxN6  | IOCxN5  | IOCxN4  | IOCxN3  | IOCxN2  | IOCxN1  | IOCxN0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 IOCxN<7:0>: Interrupt-on-Change Negative Edge Enable bits<sup>(1)</sup>

1 = Interrupt-on-Change enabled on the pin for a negative going edge. Associated Status bit and interrupt flag will be set upon detecting an edge.

0 = Interrupt-on-Change disabled for the associated pin.

Note 1: For IOCEN register, bit 3 (IOCEN3) is the only implemented bit in the register.

# 15.4 Register Definitions: FVR Control

#### REGISTER 15-1: FVRCON: FIXED VOLTAGE REFERENCE CONTROL REGISTER

| R/W-0/0         | R-q/q                                                                                                                                                                                                                 | R/W-0/0                                                                                                                                       | R/W-0/0                                                        | R/W-0/0                                                                                     | R/W-0/0                                                                                             | R/W-0/0                                                                     | R/W-0/0      |  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|--------------|--|

| FVREN           | FVRRDY <sup>(1)</sup>                                                                                                                                                                                                 | TSEN                                                                                                                                          | TSRNG                                                          | CDAF                                                                                        | /R<1:0>                                                                                             | ADFV                                                                        | R<1:0>       |  |

| bit 7           |                                                                                                                                                                                                                       |                                                                                                                                               |                                                                |                                                                                             |                                                                                                     |                                                                             | bit (        |  |

|                 |                                                                                                                                                                                                                       |                                                                                                                                               |                                                                |                                                                                             |                                                                                                     |                                                                             |              |  |

| Legend:         |                                                                                                                                                                                                                       |                                                                                                                                               |                                                                |                                                                                             |                                                                                                     |                                                                             |              |  |

| R = Readabl     | e bit                                                                                                                                                                                                                 | W = Writable                                                                                                                                  | bit                                                            | U = Unimpler                                                                                | nented bit, read                                                                                    | as '0'                                                                      |              |  |

| u = Bit is unc  | hanged                                                                                                                                                                                                                | x = Bit is unki                                                                                                                               | nown                                                           | -n/n = Value a                                                                              | at POR and BO                                                                                       | R/Value at all c                                                            | other Resets |  |

| '1' = Bit is se | t                                                                                                                                                                                                                     | '0' = Bit is cle                                                                                                                              | ared                                                           | q = Value dep                                                                               | pends on condit                                                                                     | ion                                                                         |              |  |

| bit 7           | 1 = Fixed Vo                                                                                                                                                                                                          | d Voltage Refe<br>Itage Referenc<br>Itage Referenc                                                                                            | e is enabled                                                   | bit                                                                                         |                                                                                                     |                                                                             |              |  |

| bit 6           | <ul> <li>FVRRDY: Fixed Voltage Reference Ready Flag bit<sup>(1)</sup></li> <li>1 = Fixed Voltage Reference output is ready for use</li> <li>0 = Fixed Voltage Reference output is not ready or not enabled</li> </ul> |                                                                                                                                               |                                                                |                                                                                             |                                                                                                     |                                                                             |              |  |

| bit 5           | 1 = Tempera                                                                                                                                                                                                           | <b>TSEN:</b> Temperature Indicator Enable bit <sup>(3)</sup><br>1 = Temperature Indicator is enabled<br>0 = Temperature Indicator is disabled |                                                                |                                                                                             |                                                                                                     |                                                                             |              |  |

| bit 4           | 1 = VOUT = V                                                                                                                                                                                                          | perature Indica<br>′DD - 4V⊤ (High<br>′DD - 2V⊤ (Low                                                                                          | Range)                                                         | election bit <sup>(3)</sup>                                                                 |                                                                                                     |                                                                             |              |  |

| bit 3-2         | CDAFVR<1:0<br>11 = Compar<br>10 = Compar<br>01 = Compar                                                                                                                                                               | )>: Comparator<br>ator and DAC<br>ator and DAC<br>ator and DAC                                                                                | and DAC Fix<br>Fixed Voltage<br>Fixed Voltage<br>Fixed Voltage | Reference Per<br>Reference Per<br>Reference Per                                             | erence Selectio<br>ipheral output is<br>ipheral output is<br>ipheral output is<br>ipheral output is | s 4x (4.096V) <sup>(2</sup><br>s 2x (2.048V) <sup>(2</sup><br>s 1x (1.024V) |              |  |

| bit 1-0         | 11 = ADC Fix<br>10 = ADC Fix<br>01 = ADC Fix                                                                                                                                                                          | ed Voltage Re<br>ed Voltage Re<br>ed Voltage Re                                                                                               | ference Perip<br>ference Perip<br>ference Perip                | nce Selection t<br>heral output is<br>heral output is<br>heral output is<br>heral output is | 4x (4.096V) <sup>(2)</sup><br>2x (2.048V) <sup>(2)</sup><br>1x (1.024V)                             |                                                                             |              |  |

|                 | VRRDY is always                                                                                                                                                                                                       |                                                                                                                                               | •                                                              | ם סע                                                                                        |                                                                                                     |                                                                             |              |  |

- 2: Fixed Voltage Reference output cannot exceed VDD.

- 3: See Section 16.0 "Temperature Indicator Module" for additional information.

#### TABLE 15-2: SUMMARY OF REGISTERS ASSOCIATED WITH FIXED VOLTAGE REFERENCE

| Name   | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2   | Bit 1 | Bit 0  | Register<br>on page |

|--------|-------|--------|-------|-------|-------|---------|-------|--------|---------------------|

| FVRCON | FVREN | FVRRDY | TSEN  | TSRNG | CDAFV | ′R<1:0> | ADFVF | R<1:0> | 162                 |

Legend: Shaded cells are not used with the Fixed Voltage Reference.

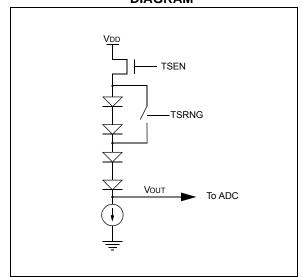

# 16.0 TEMPERATURE INDICATOR MODULE

This family of devices is equipped with a temperature circuit designed to measure the operating temperature of the silicon die. The circuit's range of operating temperature falls between -40°C and +85°C. The output is a voltage that is proportional to the device temperature. The output of the temperature indicator is internally connected to the device ADC.

The circuit may be used as a temperature threshold detector or a more accurate temperature indicator, depending on the level of calibration performed. A one-point calibration allows the circuit to indicate a temperature closely surrounding that point. A two-point calibration allows the circuit to sense the entire range of temperature more accurately. Reference Application Note AN1333, *"Use and Calibration of the Internal Temperature Indicator"* (DS01333) for more details regarding the calibration process.

# 16.1 Circuit Operation

Figure 16-1 shows a simplified block diagram of the temperature circuit. The proportional voltage output is achieved by measuring the forward voltage drop across multiple silicon junctions.

Equation 16-1 describes the output characteristics of the temperature indicator.

# EQUATION 16-1: VOUT RANGES

High Range: VOUT = VDD - 4VT

Low Range: VOUT = VDD - 2VT

The temperature sense circuit is integrated with the Fixed Voltage Reference (FVR) module. See **Section 15.0 "Fixed Voltage Reference (FVR)"** for more information.

The circuit is enabled by setting the TSEN bit of the FVRCON register. When disabled, the circuit draws no current.

The circuit operates in either high or low range. The high range, selected by setting the TSRNG bit of the FVRCON register, provides a wider output voltage. This provides more resolution over the temperature range, but may be less consistent from part to part. This range requires a higher bias voltage to operate and thus, a higher VDD is needed.

The low range is selected by clearing the TSRNG bit of the FVRCON register. The low range generates a lower voltage drop and thus, a lower bias voltage is needed to operate the circuit. The low range is provided for lowvoltage operation.

# FIGURE 16-1: TEMPERATURE CIRCUIT DIAGRAM

# 16.2 Minimum Operating VDD

When the temperature circuit is operated in low range, the device may be operated at any operating voltage that is within specifications.

When the temperature circuit is operated in high range, the device operating voltage, VDD, must be high enough to ensure that the temperature circuit is correctly biased.

Table 16-1 shows the recommended minimum  $\mathsf{V}\mathsf{D}\mathsf{D}$  vs. range setting.

## TABLE 16-1: RECOMMENDED VDD VS. RANGE

| Min. VDD, TSRNG = 1 | Min. VDD, TSRNG = 0 |

|---------------------|---------------------|

| 3.6V                | 1.8V                |

# 16.3 Temperature Output

The output of the circuit is measured using the internal Analog-to-Digital Converter. A channel is reserved for the temperature circuit output. Refer to **Section 17.0 "Analog-to-Digital Converter (ADC) Module"** for detailed information.

# 16.4 ADC Acquisition Time

To ensure accurate temperature measurements, the user must wait at least 200  $\mu$ s after the ADC input multiplexer is connected to the temperature indicator output before the conversion is performed. In addition, the user must wait 200  $\mu$ s between sequential conversions of the temperature indicator output.

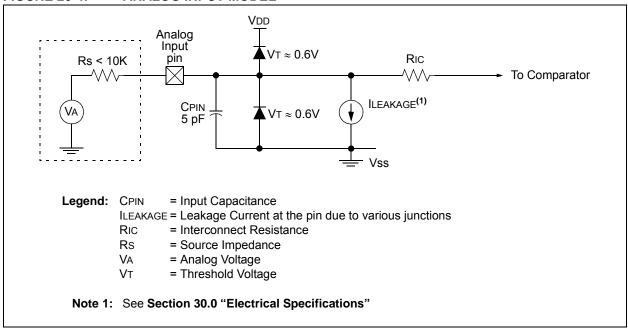

#### 17.4 **ADC Acquisition Requirements**

For the ADC to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The Analog Input model is shown in Figure 17-4. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), refer to Figure 17-4. The maximum recommended impedance for analog sources is 10 k $\Omega$ . As the

source impedance is decreased, the acquisition time may be decreased. After the analog input channel is selected (or changed), an ADC acquisition must be done before the conversion can be started. To calculate the minimum acquisition time, Equation 17-1 may be used. This equation assumes that 1/2 LSb error is used (4,096 steps for the ADC). The 1/2 LSb error is the maximum error allowed for the ADC to meet its specified resolution.

## EQUATION 17-1: ACQUISITION TIME EXAMPLE

Assumptions: Temperature =

$$50^{\circ}C$$

and external impedance of  $10k\Omega 5.0V$  VDD

$TACQ = Amplifier Settling Time + Hold Capacitor Charging Time + Temperature Coefficient$

$= TAMP + TC + TCOFF$

$= 2\mu s + TC + [(Temperature - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$

The value for TC can be approximated with the following equations:

$$V_{APPLIED}\left(1 - \frac{1}{(2^{n+1}) - 1}\right) = V_{CHOLD} ; [1] V_{CHOLD} charged to within 1/2 lsb$$

$$V_{APPLIED}\left(1 - e^{\frac{-Tc}{RC}}\right) = V_{CHOLD} ; [2] V_{CHOLD} charge response to V_{APPLIED} V_{APPLIED}\left(1 - e^{\frac{-Tc}{RC}}\right) = V_{APPLIED}\left(1 - \frac{1}{(2^{n+1}) - 1}\right) ; combining [1] and [2]$$

Note: Where n = number of bits of the ADC.

Solving for TC:

ł

$$Tc = -C_{HOLD}(RIC + RSS + RS) \ln(1/8191)$$

= -10pF(1k\Omega + 7k\Omega + 10k\Omega) \ln(0.000122)

= 1.62\mus

Therefore:

$$TACQ = 2\mu s + 1.62\mu s + [(50^{\circ}C - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$$

= 4.87\mu s

Note 1: The reference voltage (VREF) has no effect on the equation, since it cancels itself out.

2: Maximum source impedance feeding the input pin should be considered so that the pin leakage does not cause a voltage divider, thereby limiting the absolute accuracy.

# 18.4 Register Definitions: Op Amp Control

# REGISTER 18-1: OPAxCON: OPERATIONAL AMPLIFIERS (OPAx) CONTROL REGISTERS

| R/W-0/0              | R/W-0/0    | U-0                                          | U-0  | U-0                                                   | U-0 | R/W-0/0 | R/W-0/0     |  |  |

|----------------------|------------|----------------------------------------------|------|-------------------------------------------------------|-----|---------|-------------|--|--|

| OPAxEN               | OPAxSP     | _                                            |      |                                                       |     | OPAxC   | OPAxCH<1:0> |  |  |

| pit 7                |            |                                              |      |                                                       |     |         | bit (       |  |  |

|                      |            |                                              |      |                                                       |     |         |             |  |  |

| Legend:              |            |                                              |      |                                                       |     |         |             |  |  |

| R = Readable bit     |            | W = Writable bit                             |      | U = Unimplemented bit, read as '0'                    |     |         |             |  |  |

| u = Bit is unchanged |            | x = Bit is unkr                              | nown | -n/n = Value at POR and BOR/Value at all other Resets |     |         |             |  |  |

| '1' = Bit is se      | t          | '0' = Bit is clea                            | ared | q = Value depends on condition                        |     |         |             |  |  |

| bit 7                | OPAxEN: Or | o Amp Enable b                               | it   |                                                       |     |         |             |  |  |

|                      | 1 = Op amp | -                                            |      | active power                                          |     |         |             |  |  |

| bit 6                | OPAxSP: Op | <b>OPAxSP:</b> Op Amp Speed/Power Select bit |      |                                                       |     |         |             |  |  |

| bit 6   | OPAxSP: Op Amp Speed/Power Select bit                    |

|---------|----------------------------------------------------------|

|         | 1 = Comparator operates in high GBWP mode                |

|         | 0 = Reserved. Do not use.                                |

| bit 5-2 | Unimplemented: Read as '0'                               |

| bit 1-0 | OPAxCH<1:0>: Non-inverting Channel Selection bits        |

|         | 11 = Non-inverting input connects to FVR Buffer 2 output |

|         | 10 = Non-inverting input connects to DAC_output          |

|         | $_{0x}$ = Non-inverting input connects to OPAxIN+ pin    |

|         |                                                          |

# TABLE 18-1: SUMMARY OF REGISTERS ASSOCIATED WITH OP AMPS

| Name     | Bit 7                                                                              | Bit 6                                     | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0   | Register<br>on Page |

|----------|------------------------------------------------------------------------------------|-------------------------------------------|--------|--------|--------|--------|--------|---------|---------------------|

| ANSELA   | ANSA7                                                                              | _                                         | ANSA5  | ANSA4  | ANSA3  | ANSA2  | ANSA1  | ANSA0   | 132                 |

| ANSELB   | —                                                                                  | ANSB6 ANSB5 ANSB4 ANSB3 ANSB2 ANSB1 ANSB0 |        |        |        |        |        |         | 138                 |

| DAC1CON0 | DAC1EN — DAC10E1 DAC10E2 DAC1PSS<1:0> — DAC1NSS                                    |                                           |        |        |        |        |        |         | 186                 |

| DAC1CON1 | DAC1R<7:0>                                                                         |                                           |        |        |        |        |        |         | 186                 |

| OPA1CON  | OPA1EN                                                                             | OPA1SP                                    | _      | —      | —      | —      | OPA1P0 | CH<1:0> | 182                 |

| OPA2CON  | OPA2EN         OPA2SP         —         —         —         —         OPA2PCH<1:0> |                                           |        |        |        |        |        | 182     |                     |

| TRISA    | TRISA7                                                                             | TRISA6                                    | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0  | 131                 |

| TRISB    | TRISB7                                                                             | TRISB6                                    | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0  | 137                 |

| TRISC    | TRISC7                                                                             | TRISC6                                    | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0  | 142                 |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by op amps.

**Note 1:** PIC16(L)F1784/7 only

# 20.10 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 20-4. Since the analog input pins share their connection with a digital input, they have reverse biased ESD protection diodes to VDD and Vss. The analog input, therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up may occur.

A maximum source impedance of  $10 \text{ k}\Omega$  is recommended for the analog sources. Also, any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current to minimize inaccuracies introduced.

- Note 1: When reading a PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert as an analog input, according to the input specification.

- 2: Analog levels on any pin defined as a digital input, may cause the input buffer to consume more current than is specified.

# 20.10.1 ALTERNATE PIN LOCATIONS

This module incorporates I/O pins that can be moved to other locations with the use of the alternate pin function register APFCON. To determine which pins can be moved and what their default locations are upon a Reset, see **Section 13.1 "Alternate Pin Function**" for more information.

#### FIGURE 20-4: ANALOG INPUT MODEL

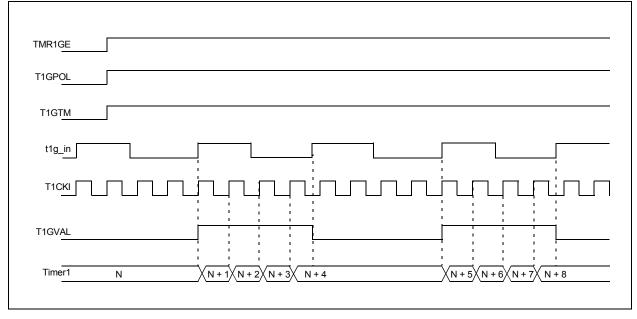

# FIGURE 22-4: TIMER1 GATE TOGGLE MODE

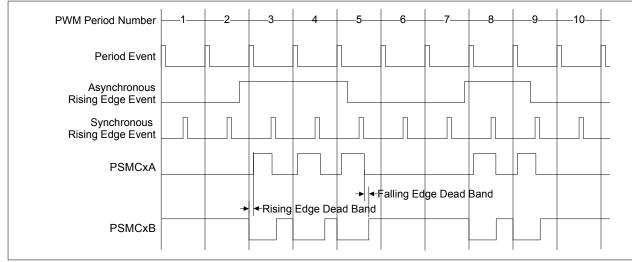

# 24.3.8 PULSE-SKIPPING PWM WITH COMPLEMENTARY OUTPUTS

The pulse-skipping PWM is used to generate a series of fixed-length pulses that may or not be triggered at each period event. If any of the sources enabled to generate a rising edge event are high when a period event occurs, a pulse will be generated. If the rising edge sources are low at the period event, no pulse will be generated.