Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2000                       |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PSMC, PWM, WDT                                 |

| Number of I/O              | 24                                                                          |

| Program Memory Size        | 14KB (8K x 14)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 11x12b; D/A 1x8b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 28-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1786t-i-ss |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| IADE |             |             |             |            |      |           | · -                                  | - ( )   | , , ,     |        | /      |      |          |            |           |         |             |

|------|-------------|-------------|-------------|------------|------|-----------|--------------------------------------|---------|-----------|--------|--------|------|----------|------------|-----------|---------|-------------|

| Q    | 40-Pin PDIP | 40-Pin UQFN | 44-Pin TQFP | 44-Pin QFN | ADC  | Reference | Comparator                           | Op Amps | 8-bit DAC | Timers | PSMC   | ССР  | EUSART   | MSSP       | Interrupt | dn-IInd | Basic       |

| RC1  | 16          | 31          | 35          | 35         | —    |           |                                      | —       | —         | T10SI  | PSMC1B | CCP2 | —        | —          | IOC       | Y       | _           |

| RC2  | 17          | 32          | 36          | 36         | —    | —         |                                      | _       | —         | _      | PSMC1C | CCP1 | —        | _          | IOC       | Υ       |             |

| RC3  | 18          | 33          | 37          | 37         | —    | —         |                                      | -       | —         | _      | PSMC1D | _    | _        | SCL<br>SCK | IOC       | Y       | —           |

| RC4  | 23          | 38          | 42          | 42         | -    | —         | -                                    | -       | _         | -      | PSMC1E | —    |          | SDI<br>SDA | IOC       | Y       | —           |

| RC5  | 24          | 39          | 43          | 43         | —    | —         | —                                    | —       | _         | —      | PSMC1F | —    | —        | SDO        | IOC       | Y       | —           |

| RC6  | 25          | 40          | 44          | 44         | —    | —         | -                                    | -       | —         |        | PSMC2A | -    | TX<br>CK | —          | IOC       | Y       | —           |

| RC7  | 26          | 1           | 1           | 1          | -    | —         |                                      | —       | _         | —      | PSMC2B | —    | RX<br>DT | —          | IOC       | Y       | —           |

| RD0  | 19          | 34          | 38          | 38         | —    | —         | -                                    | OPA3IN+ | _         | —      | —      | _    | _        | _          | —         | Y       | —           |

| RD1  | 20          | 35          | 39          | 39         | AN21 | _         | C1IN4-<br>C2IN4-<br>C3IN4-<br>C4IN4- | OPA3OUT | _         |        | _      | _    | _        | _          | _         | Y       | _           |

| RD2  | 21          | 36          | 40          | 40         | —    | —         | -                                    | OPA3IN- | _         | —      | —      | —    | —        | _          | —         | Y       | _           |

| RD3  | 22          | 37          | 41          | 41         | —    | _         | _                                    | —       | _         | —      | —      | _    | —        | —          | _         | Y       |             |

| RD4  | 27          | 2           | 2           | 2          | —    | —         | _                                    |         | _         | —      | PSMC3F | —    | —        |            | —         | Y       | —           |

| RD5  | 28          | 3           | 3           | 3          | —    |           | _                                    | —       | _         | —      | PSMC3E | —    | —        |            | —         | Y       |             |

| RD6  | 29          | 4           | 4           | 4          |      | —         | C3OUT                                | —       | _         | —      | PSMC3D | —    | —        | —          |           | Y       | —           |

| RD7  | 30          | 5           | 5           | 5          | —    | —         | C4OUT                                | -       | _         | -      | PSMC3C | _    | _        | _          |           | Y       | _           |

| RE0  | 8           | 23          | 25          | 25         | AN5  | —         | —                                    | _       | _         | —      | —      | CCP3 | —        | _          | —         | Y       | —           |

| RE1  | 9           | 24          | 26          | 26         | AN6  |           | _                                    | -       | _         | -      | PSMC3B | _    | _        | _          |           | Y       | _           |

| RE2  | 10          | 25          | 27          | 27         | AN7  | —         | —                                    |         |           | —      | PSMC3A | —    | -        | —          | —         | Y       | —           |

| RE3  | 1           | 16          | 18          | 18         | —    | —         | -                                    | —       | —         | —      | —      | —    | —        | —          | IOC       | Y       | MCLR<br>VPP |

| VDD  | 11,32       | 7,26        | 7,28        | 7,8,<br>28 | -    | —         |                                      | —       | —         | —      | —      | —    | -        | —          | -         |         | Vdd         |

| Vss  | 12,31       | 6,27        | 6,29        | 6,30,      | —    | _         | -                                    | —       | _         | —      | —      | —    | —        | _          | —         | _       | Vss         |

|      |             |             |             |            |      |           |                                      |         |           |        |        |      |          |            |           |         |             |

#### TABLE 2: 40/44-PIN ALLOCATION TABLE (PIC16(L)F1784/7) (Continued)

Note 1: Alternate pin function selected with the APFCON1 (Register 13-1) and APFCON2 (Register 13-2) registers.

#### **TABLE 1-2:** PIC16(L)F1784/6/7 PINOUT DESCRIPTION (CONTINUED)

| Name                           | Function                      | Input<br>Type | Output<br>Type       | Description                         |

|--------------------------------|-------------------------------|---------------|----------------------|-------------------------------------|

| RE2 <sup>(3)</sup> /AN7/PSMC3A | RE2                           | TTL/ST        | CMOS                 | General purpose I/O.                |

|                                | AN7 AN — ADC Channel 7 input. |               | ADC Channel 7 input. |                                     |

|                                | PSMC3A                        | —             | CMOS                 | PSMC3 output A.                     |

| RE3/MCLR/VPP                   | RE3                           | TTL/ST        |                      | General purpose input.              |

|                                | MCLR                          | ST            |                      | Master Clear with internal pull-up. |

|                                | Vpp                           | HV            | _                    | Programming voltage.                |

| Vdd                            | Vdd                           | Power         |                      | Positive supply.                    |

| Vss                            | Vss                           | Power         | _                    | Ground reference.                   |

**Legend:** AN = Analog input or output CMOS = CMOS compatible input or output

OD = Open Drain

TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels I<sup>2</sup>C<sup>™</sup> = Schmitt Trigger input with I<sup>2</sup>C HV = High Voltage XTAL = Crystal levels

Note 1: Pin functions can be assigned to one of two locations via software. See Register 13-1.

2: All pins have interrupt-on-change functionality.

3: PIC16(L)F1784/7 only.

4: PIC16(L)F1786 only.

#### 2.1 Automatic Interrupt Context Saving

During interrupts, certain registers are automatically saved in shadow registers and restored when returning from the interrupt. This saves stack space and user code. See **8.5 "Automatic Context Saving**", for more information.

#### 2.2 16-level Stack with Overflow and Underflow

These devices have an external stack memory 15 bits wide and 16 words deep. A Stack Overflow or Underflow will set the appropriate bit (STKOVF or STKUNF) in the PCON register, and if enabled will cause a software Reset. See **Section 3.5 "Stack"** for more details.

#### 2.3 File Select Registers

There are two 16-bit File Select Registers (FSR). FSRs can access all file registers and program memory, which allows one Data Pointer for all memory. When an FSR points to program memory, there is one additional instruction cycle in instructions using INDF to allow the data to be fetched. General purpose memory can now also be addressed linearly, providing the ability to access contiguous data larger than 80 bytes. There are also new instructions to support the FSRs. See **Section 3.6 "Indirect Addressing"** for more details.

#### 2.4 Instruction Set

There are 49 instructions for the enhanced mid-range CPU to support the features of the CPU. See **Section 29.0 "Instruction Set Summary**" for more details.

#### 5.12 Determining the Cause of a Reset

Upon any Reset, multiple bits in the STATUS and PCON register are updated to indicate the cause of the Reset. Table 5-3 and Table 5-4 show the Reset conditions of these registers.

| STKOVF | STKUNF | RWDT | RMCLR | RI | POR | BOR | то | PD | Condition                                                         |

|--------|--------|------|-------|----|-----|-----|----|----|-------------------------------------------------------------------|

| 0      | 0      | 1    | 1     | 1  | 0   | x   | 1  | 1  | Power-on Reset                                                    |

| 0      | 0      | 1    | 1     | 1  | 0   | x   | 0  | x  | Illegal, $\overline{\text{TO}}$ is set on $\overline{\text{POR}}$ |

| 0      | 0      | 1    | 1     | 1  | 0   | x   | x  | 0  | Illegal, $\overline{PD}$ is set on $\overline{POR}$               |

| 0      | 0      | u    | 1     | 1  | u   | 0   | 1  | 1  | Brown-out Reset                                                   |

| u      | u      | 0    | u     | u  | u   | u   | 0  | u  | WDT Reset                                                         |

| u      | u      | u    | u     | u  | u   | u   | 0  | 0  | WDT Wake-up from Sleep                                            |

| u      | u      | u    | u     | u  | u   | u   | 1  | 0  | Interrupt Wake-up from Sleep                                      |

| u      | u      | u    | 0     | u  | u   | u   | u  | u  | MCLR Reset during normal operation                                |

| u      | u      | u    | 0     | u  | u   | u   | 1  | 0  | MCLR Reset during Sleep                                           |

| u      | u      | u    | u     | 0  | u   | u   | u  | u  | RESET Instruction Executed                                        |

| 1      | u      | u    | u     | u  | u   | u   | u  | u  | Stack Overflow Reset (STVREN = 1)                                 |

| u      | 1      | u    | u     | u  | u   | u   | u  | u  | Stack Underflow Reset (STVREN = 1)                                |

TABLE 5-3: RESET STATUS BITS AND THEIR SIGNIFICANCE

#### TABLE 5-4: RESET CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 0000h                 | 1 1000             | 00 110x          |

| MCLR Reset during normal operation | 0000h                 | u uuuu             | uu Ouuu          |

| MCLR Reset during Sleep            | 0000h                 | 1 Ouuu             | uu Ouuu          |

| WDT Reset                          | 0000h                 | 0 uuuu             | uu uuuu          |

| WDT Wake-up from Sleep             | PC + 1                | 0 Ouuu             | uu uuuu          |

| Brown-out Reset                    | 0000h                 | 1 luuu             | 00 11u0          |

| Interrupt Wake-up from Sleep       | PC + 1 <sup>(1)</sup> | 1 Ouuu             | uu uuuu          |

| RESET Instruction Executed         | 0000h                 | u uuuu             | uu u0uu          |

| Stack Overflow Reset (STVREN = 1)  | 0000h                 | u uuuu             | lu uuuu          |

| Stack Underflow Reset (STVREN = 1) | 0000h                 | u uuuu             | ul uuuu          |

Legend: u = unchanged, x = unknown, - = unimplemented bit, reads as '0'.

**Note 1:** When the wake-up is due to an interrupt and Global Enable bit (GIE) is set, the return address is pushed on the stack and PC is loaded with the interrupt vector (0004h) after execution of PC + 1.

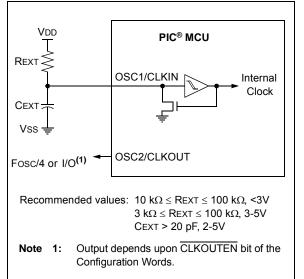

#### 6.2.1.6 External RC Mode

The external Resistor-Capacitor (RC) modes support the use of an external RC circuit. This allows the designer maximum flexibility in frequency choice while keeping costs to a minimum when clock accuracy is not required.

The RC circuit connects to OSC1. OSC2/CLKOUT is available for general purpose I/O or CLKOUT. The function of the OSC2/CLKOUT pin is determined by the CLKOUTEN bit in Configuration Words.

Figure 6-6 shows the external RC mode connections.

FIGURE 6-6: EXTERNAL RC MODES

The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values and the operating temperature. Other factors affecting the oscillator frequency are:

- threshold voltage variation

- component tolerances

- · packaging variations in capacitance

The user also needs to take into account variation due to tolerance of external RC components used.

#### 6.2.2 INTERNAL CLOCK SOURCES

The device may be configured to use the internal oscillator block as the system clock by performing one of the following actions:

- Program the FOSC<2:0> bits in Configuration Words to select the INTOSC clock source, which will be used as the default system clock upon a device Reset.

- Write the SCS<1:0> bits in the OSCCON register to switch the system clock source to the internal oscillator during run-time. See Section 6.3 "Clock Switching"for more information.

In **INTOSC** mode, OSC1/CLKIN is available for general purpose I/O. OSC2/CLKOUT is available for general purpose I/O or CLKOUT.

The function of the OSC2/CLKOUT pin is determined by the CLKOUTEN bit in Configuration Words.

The internal oscillator block has two independent oscillators and a dedicated Phase-Lock Loop, HFPLL that can produce one of three internal system clock sources.

- The HFINTOSC (High-Frequency Internal Oscillator) is factory calibrated and operates at 16 MHz. The HFINTOSC source is generated from the 500 kHz MFINTOSC source and the dedicated Phase-Lock Loop, HFPLL. The frequency of the HFINTOSC can be user-adjusted via software using the OSCTUNE register (Register 6-3).

- 2. The **MFINTOSC** (Medium-Frequency Internal Oscillator) is factory calibrated and operates at 500 kHz. The frequency of the MFINTOSC can be user-adjusted via software using the OSCTUNE register (Register 6-3).

- 3. The **LFINTOSC** (Low-Frequency Internal Oscillator) is uncalibrated and operates at 31 kHz.

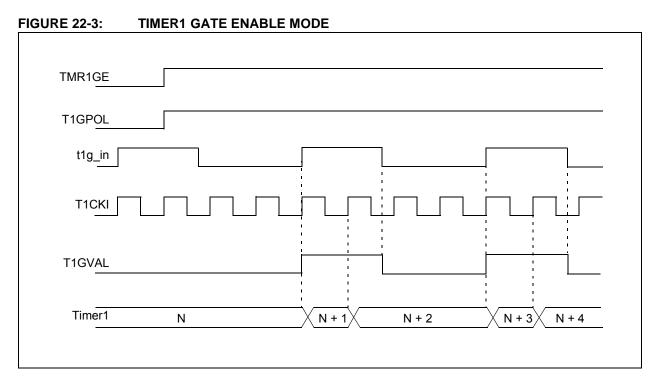

#### 22.6.2 TIMER1 GATE SOURCE SELECTION

Timer1 gate source selections are shown in Table 22-4. Source selection is controlled by the T1GSS bits of the T1GCON register. The polarity for each available source is also selectable. Polarity selection is controlled by the T1GPOL bit of the T1GCON register.

| TABLE 22-4: | TIMER1 GATE SOURCES |

|-------------|---------------------|

|-------------|---------------------|

| T1GSS | Timer1 Gate Source                                                        |

|-------|---------------------------------------------------------------------------|

| 00    | Timer1 Gate Pin                                                           |

| 01    | Overflow of Timer0<br>(TMR0 increments from FFh to 00h)                   |

| 10    | Comparator 1 Output sync_C1OUT<br>(optionally Timer1 synchronized output) |

| 11    | Comparator 2 Output sync_C2OUT<br>(optionally Timer1 synchronized output) |

#### 22.6.2.1 T1G Pin Gate Operation

The T1G pin is one source for Timer1 gate control. It can be used to supply an external source to the Timer1 gate circuitry.

#### 22.6.2.2 Timer0 Overflow Gate Operation

When Timer0 increments from FFh to 00h, a low-to-high pulse will automatically be generated and internally supplied to the Timer1 gate circuitry.

#### 22.6.2.3 Comparator C1 Gate Operation

The output resulting from a Comparator 1 operation can be selected as a source for Timer1 gate control. The Comparator 1 output (sync\_C1OUT) can be synchronized to the Timer1 clock or left asynchronous. For more information see **Section 20.4.1 "Comparator Output Synchronization"**.

#### 22.6.2.4 Comparator C2 Gate Operation

The output resulting from a Comparator 2 operation can be selected as a source for Timer1 gate control. The Comparator 2 output (sync\_C2OUT) can be synchronized to the Timer1 clock or left asynchronous. For more information see **Section 20.4.1 "Comparator Output Synchronization**".

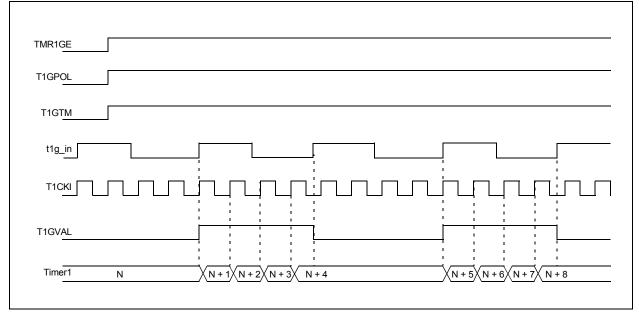

#### 22.6.3 TIMER1 GATE TOGGLE MODE

When Timer1 Gate Toggle mode is enabled, it is possible to measure the full-cycle length of a Timer1 gate signal, as opposed to the duration of a single level pulse.

The Timer1 gate source is routed through a flip-flop that changes state on every incrementing edge of the signal. See Figure 22-4 for timing details.

Timer1 Gate Toggle mode is enabled by setting the T1GTM bit of the T1GCON register. When the T1GTM bit is cleared, the flip-flop is cleared and held clear. This is necessary in order to control which edge is measured.

| Note: | Enabling Toggle mode at the same time       |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|

|       | as changing the gate polarity may result in |  |  |  |  |

|       | indeterminate operation.                    |  |  |  |  |

## 22.6.4 TIMER1 GATE SINGLE-PULSE MODE

When Timer1 Gate Single-Pulse mode is enabled, it is possible to capture a single-pulse gate event. Timer1 Gate Single-Pulse mode is enabled by first setting the T1GSPM bit in the T1GCON register. Next, the T1GGO/DONE bit in the T1GCON register must be set. The Timer1 will be fully enabled on the next incrementing edge. On the next trailing edge of the pulse, the T1GGO/DONE bit will automatically be cleared. No other gate events will be allowed to increment Timer1 until the T1GGO/DONE bit is once again set in software. See Figure 22-5 for timing details.

If the Single-Pulse Gate mode is disabled by clearing the T1GSPM bit in the T1GCON register, the T1GGO/DONE bit should also be cleared.

Enabling the Toggle mode and the Single-Pulse mode simultaneously will permit both sections to work together. This allows the cycle times on the Timer1 gate source to be measured. See Figure 22-6 for timing details.

#### 22.6.5 TIMER1 GATE VALUE

When Timer1 Gate Value Status is utilized, it is possible to read the most current level of the gate control value. The value is accessible by reading the T1GVAL bit in the T1GCON register. The T1GVAL bit is valid even when the Timer1 gate is not enabled (TMR1GE bit is cleared).

#### 22.6.6 TIMER1 GATE EVENT INTERRUPT

When Timer1 Gate Event Interrupt is enabled, it is possible to generate an interrupt upon the completion of a gate event. When the falling edge of T1GVAL occurs, the TMR1GIF flag bit in the PIR1 register will be set. If the TMR1GIE bit in the PIE1 register is set, then an interrupt will be recognized.

The TMR1GIF flag bit operates even when the Timer1 gate is not enabled (TMR1GE bit is cleared).

#### FIGURE 22-4: TIMER1 GATE TOGGLE MODE

#### 24.2.7 ASYNCHRONOUS INPUTS

The PSMC module supports asynchronous inputs alone or in combination with the synchronous inputs. asynchronous inputs include:

- Analog

- sync\_C1OUT

- sync\_C2OUT

- sync\_C3OUT

- sync\_C4OUT

- Digital

- PSMCxIN pin

#### 24.2.7.1 Comparator Inputs

The outputs of any combination of the synchronized comparators may be used to trigger any of the three events as well as auto-shutdown.

The event triggers on the rising edge of the comparator output. Except for auto-shutdown, the event input is not level sensitive.

#### 24.2.7.2 PSMCxIN Pin Input

The PSMCxIN pin may be used to trigger PSMC events. Data is passed through straight to the PSMC module without any synchronization to a system clock. This is so that input blanking may be applied to any external circuit using the module.

The event triggers on the rising edge of the PSMCxIN signal.

#### 24.2.7.3 Asynchronous Polarity

Polarity control is available for the period and duty-cycle asynchronous event inputs. Polarity control is necessary when the same signal is used as the source for both events. Inverting the polarity of one event relative to the other enables starting the period on one edge of the signal and terminating the duty-cycle on the opposite edge. Polarity is controlled with the PxPRPOL and PxDCPOL bits of the PSMCxSYNC register. Inverting the asynchronous input with these controls inverts all enabled asynchronous inputs for the corresponding event.

#### 24.2.8 INPUT BLANKING

Input blanking is a function whereby the inputs from any selected asynchronous input may be driven inactive for a short period of time. This is to prevent electrical transients from the turn-on/off of power components from generating a false event.

Blanking is initiated by either or both:

- Rising event

- Falling event

Blanked inputs are suppressed from causing all asynchronous events, including:

- Rising

- Falling

- Period

- Shutdown

Rising edge and falling edge blanking are controlled independently. The following features are available for blanking:

- · Blanking enable

- · Blanking time counters

- · Blanking mode

The following Blanking modes are available:

- Blanking disabled

- Immediate blanking

The Falling Edge Blanking mode is set with the PxFEBM<1:0> bits of the PSMCx Blanking Control (PSMCxBLNK) register (Register 24-9).

The Rising Edge Blanking mode is set with the PxREBM<1:0> bits of the PSMCx Blanking Control (PSMCxBLNK) register (Register 24-9).

#### 24.2.8.1 Blanking Disabled

With blanking disabled, the asynchronous inputs are passed to the PSMC module without any intervention.

#### 24.2.8.2 Immediate Blanking

With Immediate blanking, a counter is used to determine the blanking period. The desired blanking time is measured in psmc\_clk periods. A rising edge event will start incrementing the rising edge blanking counter. A falling edge event will start incrementing the falling edge blanking counter.

The rising edge blanking time is set with the PSMC Rising Edge Blanking Time (PSMCxBLKR) register (Register 24-29). The inputs to be blanked are selected with the PSMC Rising Edge Blanked Source (PSMCxREBS) register (Register 24-10). During rising edge blanking, the selected blanked sources are suppressed for falling edge as well as rising edge, auto-shutdown and period events.

The falling edge blanking time is set with the PSMC Falling Edge Blanking Time (PSMCxBLKF) register (Register 24-30). The inputs to be blanked are selected with the PSMC Falling Edge Blanked Source (PSMCxFEBS) register (Register 24-11). During falling edge blanking, the selected blanked sources are suppressed for rising edge, as well as falling edge, auto-shutdown, and period events.

The blanking counters are incremented on the rising edge of psmc\_clk. Blanked sources are suppressed until the counter value equals the blanking time register causing the blanking to terminate.

As the rising and falling edge events are from asynchronous inputs, there may be some uncertainty in the actual blanking time implemented in each cycle. The maximum uncertainty is equal to one psmc\_clk period.

#### REGISTER 24-22: PSMCxDCL: PSMC DUTY CYCLE COUNT LOW BYTE REGISTER

| R/W-0/0          | R/W-0/0 | R/W-0/0           | R/W-0/0 | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0     |

|------------------|---------|-------------------|---------|----------------|------------------|------------------|-------------|

|                  |         |                   | PSMCx   | DCL<7:0>       |                  |                  |             |

| bit 7            |         |                   |         |                |                  |                  | bit 0       |

|                  |         |                   |         |                |                  |                  |             |

| Legend:          |         |                   |         |                |                  |                  |             |

| R = Readable     | bit     | W = Writable      | bit     | U = Unimpler   | nented bit, read | as '0'           |             |

| u = Bit is uncha | anged   | x = Bit is unkr   | iown    | -n/n = Value a | at POR and BO    | R/Value at all c | ther Resets |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                |                  |                  |             |

bit 7-0

**PSMCxDCL<7:0>:** 16-bit Duty Cycle Count Least Significant bits = PSMCxDC<7:0>

#### REGISTER 24-23: PSMCxDCH: PSMC DUTY CYCLE COUNT HIGH REGISTER

| R/W-0/0     | R/W-0/0       | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |

|-------------|---------------|---------|---------|---------|---------|---------|---------|--|

|             | PSMCxDCH<7:0> |         |         |         |         |         |         |  |

| bit 7 bit 0 |               |         |         |         |         |         | bit 0   |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **PSMCxDCH<7:0>:** 16-bit Duty Cycle Count Most Significant bits = PSMCxDC<15:8>

#### 25.0 CAPTURE/COMPARE/PWM MODULES

The Capture/Compare/PWM module is a peripheral that allows the user to time and control different events, and to generate Pulse-Width Modulation (PWM) signals. In Capture mode, the peripheral allows the timing of the duration of an event. The Compare mode allows the user to trigger an external event when a predetermined amount of time has expired. The PWM mode can generate Pulse-Width Modulated signals of varying frequency and duty cycle.

This family of devices contains two standard Capture/Compare/PWM modules (CCP1, CCP2 and CCP3).

The Capture and Compare functions are identical for all CCP modules.

- Note 1: In devices with more than one CCP module, it is very important to pay close attention to the register names used. A number placed after the module acronym is used to distinguish between separate modules. For example, the CCP1CON and CCP2CON control the same operational aspects of two completely different CCP modules.

- 2: Throughout this section, generic references to a CCP module in any of its operating modes may be interpreted as being equally applicable to CCPx module. Register names, module signals, I/O pins, and bit names may use the generic designator 'x' to indicate the use of a numeral to distinguish a particular module, when required.

© 2012-2014 Microchip Technology Inc.

#### 26.5.4 SLAVE MODE 10-BIT ADDRESS RECEPTION

This section describes a standard sequence of events for the MSSP module configured as an  $I^2C$  slave in 10-bit Addressing mode.

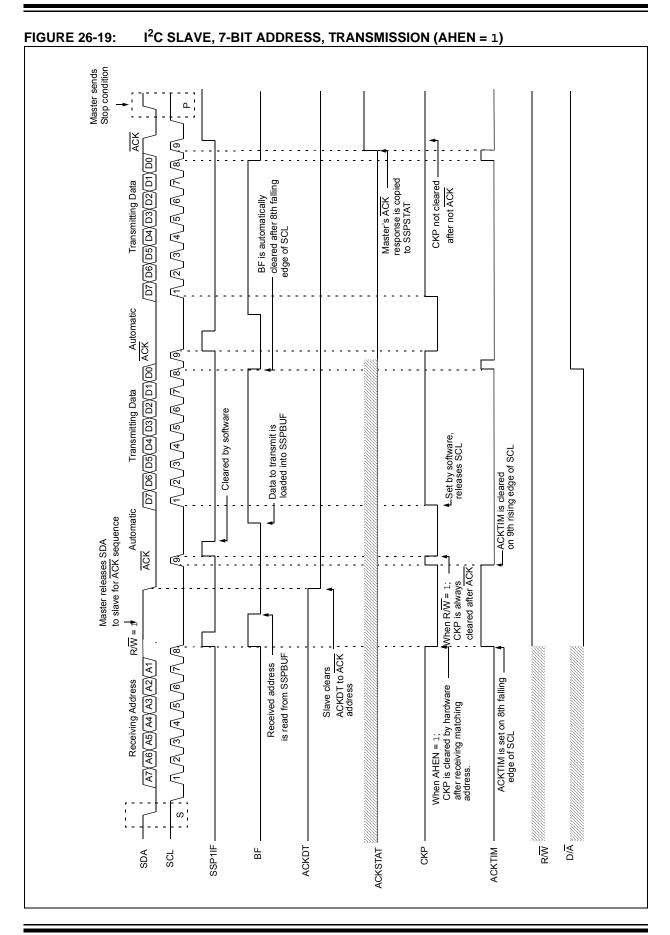

Figure 26-19 is used as a visual reference for this description.

This is a step by step process of what must be done by slave software to accomplish I<sup>2</sup>C communication.

- 1. Bus starts Idle.

- Master sends Start condition; S bit of SSPSTAT is set; SSP1IF is set if interrupt on Start detect is enabled.

- 3. Master sends matching high address with R/W bit clear; UA bit of the SSPSTAT register is set.

- 4. Slave sends ACK and SSP1IF is set.

- 5. Software clears the SSP1IF bit.

- 6. Software reads received address from SSPBUF clearing the BF flag.

- 7. Slave loads low address into SSPADD, releasing SCL.

- 8. Master sends matching low address byte to the slave; UA bit is set.

**Note:** Updates to the SSPADD register are not allowed until after the ACK sequence.

- 9. Slave sends ACK and SSP1IF is set.

- **Note:** If the low address does not match, SSP1IF and UA are still set so that the slave software can set SSPADD back to the high address. BF is not set because there is no match. CKP is unaffected.

- 10. Slave clears SSP1IF.

- 11. Slave reads the received matching address from SSPBUF clearing BF.

- 12. Slave loads high address into SSPADD.

- Master clocks a data byte to the slave and clocks out the slaves ACK on the 9th SCL pulse; SSP1IF is set.

- 14. If SEN bit of SSPCON2 is set, CKP is cleared by hardware and the clock is stretched.

- 15. Slave clears SSP1IF.

- 16. Slave reads the received byte from SSPBUF clearing BF.

- 17. If SEN is set the slave sets CKP to release the SCL.

- 18. Steps 13-17 repeat for each received byte.

- 19. Master sends Stop to end the transmission.

### 26.5.5 10-BIT ADDRESSING WITH ADDRESS OR DATA HOLD

Reception using 10-bit addressing with AHEN or DHEN set is the same as with 7-bit modes. The only difference is the need to update the SSPADD register using the UA bit. All functionality, specifically when the CKP bit is cleared and SCL line is held low are the same. Figure 26-20 can be used as a reference of a slave in 10-bit addressing with AHEN set.

Figure 26-21 shows a standard waveform for a slave transmitter in 10-bit Addressing mode.

#### 26.6.2 CLOCK ARBITRATION

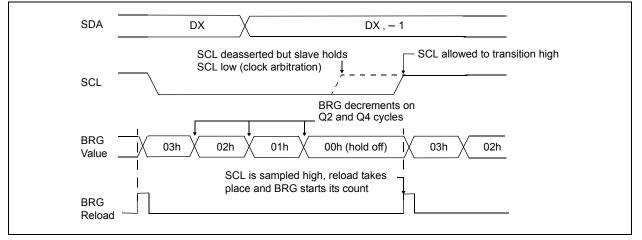

Clock arbitration occurs when the master, during any receive, transmit or Repeated Start/Stop condition, releases the SCL pin (SCL allowed to float high). When the SCL pin is allowed to float high, the Baud Rate Generator (BRG) is suspended from counting until the SCL pin is actually sampled high. When the SCL pin is sampled high, the Baud Rate Generator is reloaded with the contents of SSPADD<7:0> and begins counting. This ensures that the SCL high time will always be at least one BRG rollover count in the event that the clock is held low by an external device (Figure 26-25).

#### FIGURE 26-25: BAUD RATE GENERATOR TIMING WITH CLOCK ARBITRATION

#### 26.6.3 WCOL STATUS FLAG

If the user writes the SSPBUF when a Start, Restart, Stop, Receive or Transmit sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write does not occur). Any time the WCOL bit is set it indicates that an action on SSPBUF was attempted while the module was not idle.

| Note: | Because queueing of events is not       |  |  |  |  |  |

|-------|-----------------------------------------|--|--|--|--|--|

|       | allowed, writing to the lower 5 bits of |  |  |  |  |  |

|       | SSPCON2 is disabled until the Start     |  |  |  |  |  |

|       | condition is complete.                  |  |  |  |  |  |

| R/W-0/0          | R/W-0/0                                                                                                                                      | R/W-0/0                                                                                                              | R/W-0/0        | R/W-0/0       | R-0/0            | R-0/0            | R-0/0       |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|----------------|---------------|------------------|------------------|-------------|--|--|

| SPEN             | RX9                                                                                                                                          | SREN                                                                                                                 | CREN           | ADDEN         | FERR             | OERR             | RX9D        |  |  |

| bit 7            |                                                                                                                                              |                                                                                                                      |                |               |                  |                  | bit 0       |  |  |

|                  |                                                                                                                                              |                                                                                                                      |                |               |                  |                  |             |  |  |

| Legend:          |                                                                                                                                              |                                                                                                                      |                |               |                  |                  |             |  |  |

| R = Readable     | e bit                                                                                                                                        | W = Writable                                                                                                         | bit            | U = Unimple   | mented bit, read | l as '0'         |             |  |  |

| u = Bit is unc   | hanged                                                                                                                                       | x = Bit is unk                                                                                                       | nown           | -n/n = Value  | at POR and BO    | R/Value at all o | ther Resets |  |  |

| '1' = Bit is set | 1                                                                                                                                            | '0' = Bit is cle                                                                                                     | ared           |               |                  |                  |             |  |  |

| hit 7            | CDEN: Corio                                                                                                                                  | l Dort Enchla h                                                                                                      | :1             |               |                  |                  |             |  |  |

| bit 7            |                                                                                                                                              | <b>SPEN:</b> Serial Port Enable bit<br>1 = Serial port enabled (configures RX/DT and TX/CK pins as serial port pins) |                |               |                  |                  |             |  |  |

|                  |                                                                                                                                              | ort disabled (he                                                                                                     |                |               |                  |                  |             |  |  |

| bit 6            | <b>RX9:</b> 9-bit R                                                                                                                          | eceive Enable I                                                                                                      | oit            |               |                  |                  |             |  |  |

|                  |                                                                                                                                              | 9-bit reception<br>8-bit reception                                                                                   |                |               |                  |                  |             |  |  |

| bit 5            |                                                                                                                                              | e Receive Enal                                                                                                       | ole bit        |               |                  |                  |             |  |  |

|                  | Asynchronous mode:                                                                                                                           |                                                                                                                      |                |               |                  |                  |             |  |  |

|                  | Don't care                                                                                                                                   |                                                                                                                      |                |               |                  |                  |             |  |  |

|                  | Synchronous mode – Master:                                                                                                                   |                                                                                                                      |                |               |                  |                  |             |  |  |

|                  | <ol> <li>Enables single receive</li> <li>Disables single receive</li> </ol>                                                                  |                                                                                                                      |                |               |                  |                  |             |  |  |

|                  | 0 = Disables single receive<br>This bit is cleared after reception is complete.                                                              |                                                                                                                      |                |               |                  |                  |             |  |  |

|                  | Synchronous mode – Slave                                                                                                                     |                                                                                                                      |                |               |                  |                  |             |  |  |

|                  | Don't care                                                                                                                                   |                                                                                                                      |                |               |                  |                  |             |  |  |

| bit 4            | CREN: Continuous Receive Enable bit                                                                                                          |                                                                                                                      |                |               |                  |                  |             |  |  |

|                  | Asynchronous mode:                                                                                                                           |                                                                                                                      |                |               |                  |                  |             |  |  |

|                  | 1 = Enables receiver<br>0 = Disables receiver                                                                                                |                                                                                                                      |                |               |                  |                  |             |  |  |

|                  | Synchronous mode:                                                                                                                            |                                                                                                                      |                |               |                  |                  |             |  |  |

|                  | 1 = Enables continuous receive until enable bit CREN is cleared (CREN overrides SREN)                                                        |                                                                                                                      |                |               |                  |                  |             |  |  |

|                  | 0 = Disables                                                                                                                                 | s continuous re                                                                                                      | ceive          |               |                  |                  |             |  |  |

| bit 3            | ADDEN: Address Detect Enable bit                                                                                                             |                                                                                                                      |                |               |                  |                  |             |  |  |

|                  | Asynchronous mode 9-bit (RX9 = 1):                                                                                                           |                                                                                                                      |                |               |                  |                  |             |  |  |

|                  | 1 = Enables address detection, enable interrupt and load the receive buffer when RSR<8> is set                                               |                                                                                                                      |                |               |                  |                  |             |  |  |

|                  | 0 = Disables address detection, all bytes are received and ninth bit can be used as parity bit<br><u>Asynchronous mode 8-bit (RX9 = 0)</u> : |                                                                                                                      |                |               |                  |                  |             |  |  |

|                  | Don't care                                                                                                                                   | ·                                                                                                                    | <i>-</i>       |               |                  |                  |             |  |  |

| bit 2            | FERR: Fram                                                                                                                                   | ing Error bit                                                                                                        |                |               |                  |                  |             |  |  |

|                  | 1 = Framing<br>0 = No frami                                                                                                                  |                                                                                                                      | ipdated by rea | ding RCREG    | register and rec | eive next valid  | byte)       |  |  |

| bit 1            | OERR: Over                                                                                                                                   | run Error bit                                                                                                        |                |               |                  |                  |             |  |  |

|                  | 1 = Overrun<br>0 = No over                                                                                                                   | error (can be c<br>run error                                                                                         | leared by clea | ring bit CREN | )                |                  |             |  |  |

|                  |                                                                                                                                              |                                                                                                                      | I D I I        |               |                  |                  |             |  |  |

| bit 0            |                                                                                                                                              | bit of Received                                                                                                      | i Data         |               |                  |                  |             |  |  |

#### REGISTER 27-2: RCSTA: RECEIVE STATUS AND CONTROL REGISTER

## FIGURE 29-1: GENERAL FORMAT FOR INSTRUCTIONS

|                                                                                  | operation:<br>6 | <b>s</b><br>0 |

|----------------------------------------------------------------------------------|-----------------|---------------|

| OPCODE d                                                                         | f (I            | FILE #)       |

| d = 0 for destination W<br>d = 1 for destination f<br>f = 7-bit file register ad | dress           |               |

| Bit-oriented file register op<br>13 10 9                                         | erations<br>76  | 0             |

| OPCODE b (B                                                                      | -               | (FILE #)      |

| b = 3-bit bit address<br>f = 7-bit file register ad                              | dress           |               |

| Literal and control operation                                                    | ons             |               |

| General                                                                          |                 |               |

| 13 8                                                                             | 7               | 0             |

| OPCODE                                                                           | K               | (literal)     |

| k = 8-bit immediate va                                                           | ue              |               |

| CALL and GOTO instructions                                                       | only            |               |

| <u>13</u> 11 10                                                                  | ,               | 0             |

| OPCODE                                                                           | k (literal      | )             |

| k = 11-bit immediate va                                                          | lue             |               |

|                                                                                  |                 |               |

| MOVLP instruction only<br>13                                                     | 76              | 0             |

| OPCODE                                                                           |                 | (literal)     |

|                                                                                  | -               |               |

| k = 7-bit immediate val                                                          | le              |               |

| MOVLB instruction only                                                           |                 |               |

| 13                                                                               | 54              | 0             |

| OPCODE                                                                           |                 | k (literal)   |

| k = 5-bit immediate val                                                          | Je              |               |

| BRA instruction only                                                             |                 |               |

| 13 9 8                                                                           | 5               | 0             |

| OPCODE                                                                           | k               | (literal)     |

| k = 9-bit immediate va                                                           | ue              |               |

| FSR Offset instructions                                                          |                 |               |

| 13 7                                                                             | 65              | 0             |

| OPCODE                                                                           | n               | k (literal)   |

| n = appropriate FSR<br>k = 6-bit immediate va                                    | ue              |               |

| FSR Increment instructions 13                                                    | 3               | 2 1 0         |

| OPCODE                                                                           |                 | n m (mode)    |

|                                                                                  |                 | •             |

| n = appropriate FSR<br>m = 2-bit mode value                                      |                 |               |

|                                                                                  |                 | 0             |

| RETFIE           | Return from Interrupt                                                                                                                                                                                              |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] RETFIE                                                                                                                                                                                                     |  |  |  |  |

| Operands:        | None                                                                                                                                                                                                               |  |  |  |  |

| Operation:       | $\begin{array}{l} TOS \to PC, \\ 1 \to GIE \end{array}$                                                                                                                                                            |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                               |  |  |  |  |

| Description:     | Return from Interrupt. Stack is<br>POPed and Top-of-Stack (TOS) is<br>loaded in the PC. Interrupts are<br>enabled by setting Global<br>Interrupt Enable bit, GIE<br>(INTCON<7>). This is a 2-cycle<br>instruction. |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                  |  |  |  |  |

| Cycles:          | 2                                                                                                                                                                                                                  |  |  |  |  |

| Example:         | RETFIE                                                                                                                                                                                                             |  |  |  |  |

|                  | After Interrupt<br>PC = TOS<br>GIE = 1                                                                                                                                                                             |  |  |  |  |

| RETURN           | Return from Subroutine                                                                                                                                   |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] RETURN                                                                                                                                           |  |  |  |  |  |

| Operands:        | None                                                                                                                                                     |  |  |  |  |  |

| Operation:       | $TOS \rightarrow PC$                                                                                                                                     |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                     |  |  |  |  |  |

| Description:     | Return from subroutine. The stack<br>is POPed and the top of the stack<br>(TOS) is loaded into the program<br>counter. This is a 2-cycle<br>instruction. |  |  |  |  |  |

| RETLW            | Return with literal in W                                                                                                                 |                  |                                                                                                                                                      |              |       |          |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------|----------|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                                                                 | RLF              | Rotate Left f through Carry                                                                                                                          |              |       |          |

| Operands:        | $0 \le k \le 255$                                                                                                                        | Syntax:          | [ label ]                                                                                                                                            |              | RLF   | f,d      |

| Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow$ PC                                                                                             | Operands:        | $0 \le f \le 1$<br>$d \in [0,1]$                                                                                                                     |              |       |          |

| Status Affected: | None                                                                                                                                     | Operation:       | See des                                                                                                                                              | cription I   | oelow | 1        |

| Description:     | The W register is loaded with the                                                                                                        | Status Affected: | С                                                                                                                                                    |              |       |          |

|                  | 8-bit literal 'k'. The program<br>counter is loaded from the top of<br>the stack (the return address).<br>This is a 2-cycle instruction. | Description:     | The contents of register 'f' are<br>rotated one bit to the left through<br>the Carry flag. If 'd' is '0', the<br>result is placed in the W register. |              |       |          |

| Words:           | 1                                                                                                                                        |                  |                                                                                                                                                      | 1', the re   |       | s stored |

| Cycles:          | 2                                                                                                                                        |                  |                                                                                                                                                      | register "   |       | t f      |

| Example:         | CALL TABLE;W contains                                                                                                                    |                  | <b>-</b>                                                                                                                                             |              | Regis |          |

| ·                | table                                                                                                                                    | Words:           | 1                                                                                                                                                    |              |       |          |

|                  | <pre>;offset value ,W now has table value</pre>                                                                                          | Cycles:          | 1                                                                                                                                                    |              |       |          |

| TABLE            | • , w now has cable value                                                                                                                | Example:         | RLF                                                                                                                                                  | REG1,        | 0     |          |

|                  | •                                                                                                                                        | Example.         | Before Instruction                                                                                                                                   |              |       |          |

|                  | ADDWF PC ;W = offset<br>RETLW kl ;Begin table<br>RETLW k2 ;                                                                              |                  | Belore I                                                                                                                                             | REG1<br>0110 | =     | 1110     |

|                  | •                                                                                                                                        |                  |                                                                                                                                                      | С            | =     | 0        |

|                  | •                                                                                                                                        |                  | After Ins                                                                                                                                            |              |       |          |

|                  | RETLW kn ; End of table                                                                                                                  |                  |                                                                                                                                                      | REG1<br>0110 | =     | 1110     |

|                  | Defense la stancetica                                                                                                                    |                  |                                                                                                                                                      | W            | =     | 1100     |

|                  | Before Instruction<br>W = 0x07                                                                                                           |                  |                                                                                                                                                      | 1100<br>~    |       | -        |

|                  | After Instruction<br>W = value of k8                                                                                                     |                  |                                                                                                                                                      | C            | =     | 1        |

| Standard       | Operating             | Conditions (unless         | otherwise stated | l)         |      |                                      |                                             |  |

|----------------|-----------------------|----------------------------|------------------|------------|------|--------------------------------------|---------------------------------------------|--|

| Param.<br>No.  | Symbol                | Characteristic             |                  | Min.       | Max. | Units                                | Conditions                                  |  |

| SP100*         | Тнідн                 | Clock high time            | 100 kHz mode     | 4.0        |      | μS                                   | Device must operate at a minimum of 1.5 MHz |  |

|                |                       |                            | 400 kHz mode     | 0.6        | _    | μS                                   | Device must operate at a minimum of 10 MHz  |  |

|                |                       |                            | SSP module       | 1.5TCY     | _    |                                      |                                             |  |

| SP101*         | SP101* TLOW           | Clock low time             | 100 kHz mode     | 4.7        | _    | μS                                   | Device must operate at a minimum of 1.5 MHz |  |

|                |                       |                            | 400 kHz mode     | 1.3        | _    | μS                                   | Device must operate at a minimum of 10 MHz  |  |

|                |                       |                            | SSP module       | 1.5TCY     | _    |                                      |                                             |  |

| SP102* Tr      | SDA and SCL rise time | 100 kHz mode               | —                | 1000       | ns   |                                      |                                             |  |

|                |                       | 400 kHz mode               | 20 + 0.1Св       | 300        | ns   | CB is specified to be from 10-400 pF |                                             |  |

| SP103*         | TF                    | SDA and SCL fall time      | 100 kHz mode     | —          | 250  | ns                                   |                                             |  |

|                |                       |                            | 400 kHz mode     | 20 + 0.1Св | 250  | ns                                   | CB is specified to be from 10-400 pF        |  |

| SP106* THD:DAT | Data input hold time  | 100 kHz mode               | 0                | _          | ns   |                                      |                                             |  |

|                |                       | 400 kHz mode               | 0                | 0.9        | μs   |                                      |                                             |  |

| SP107* TSU:DA  | TSU:DAT               | AT Data input setup time   | 100 kHz mode     | 250        | _    | ns                                   | (Note 2)                                    |  |

|                |                       |                            | 400 kHz mode     | 100        | _    | ns                                   |                                             |  |

| SP109* TAA     | ΤΑΑ                   | Output valid from<br>clock | 100 kHz mode     | _          | 3500 | ns                                   | (Note 1)                                    |  |

|                |                       |                            | 400 kHz mode     |            | _    | ns                                   |                                             |  |

| SP110* TBUF    | TBUF                  | Bus free time              | 100 kHz mode     | 4.7        | _    | μs                                   | Time the bus must be free                   |  |

|                |                       |                            | 400 kHz mode     | 1.3        | —    | μS                                   | before a new transmission<br>can start      |  |

| SP111          | Св                    | Bus capacitive loadir      | ng               | _          | 400  | pF                                   |                                             |  |

### TABLE 30-22: I<sup>2</sup>C<sup>™</sup> BUS DATA REQUIREMENTS

These parameters are characterized but not tested.

**Note 1:** As a transmitter, the device must provide this internal minimum delay time to bridge the undefined region (min. 300 ns) of the falling edge of SCL to avoid unintended generation of Start or Stop conditions.

2: A Fast mode (400 kHz) I<sup>2</sup>C<sup>™</sup> bus device can be used in a Standard mode (100 kHz) I<sup>2</sup>C bus system, but the requirement Tsu:DAT ≥ 250 ns must then be met. This will automatically be the case if the device does not stretch the low period of the SCL signal. If such a device does stretch the low period of the SCL signal, it must output the next data bit to the SDA line TR max. + Tsu:DAT = 1000 + 250 = 1250 ns (according to the Standard mode I<sup>2</sup>C bus specification), before the SCL line is released.

Note: Unless otherwise noted, VIN = 5V, Fosc = 300 kHz, CIN = 0.1  $\mu$ F, TA = 25°C.

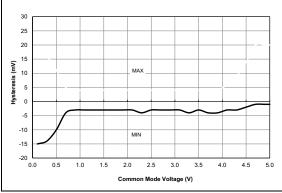

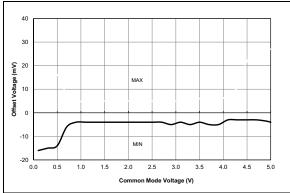

**FIGURE 31-120:** Comparator Offset, NP Mode (CxSP = 1), VDD = 5.0V, Typical Measured Values at 25°C, PIC16F1784/6/7 Only.

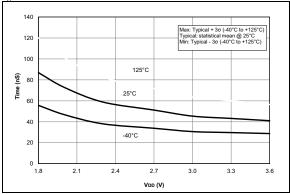

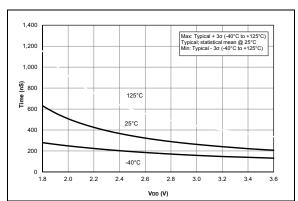

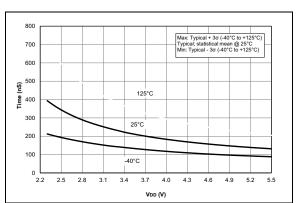

**FIGURE 31-122:** Comparator Response Time Over Voltage, NP Mode (CxSP = 1), Typical Measured Values, PIC16LF1784/6/7 Only.

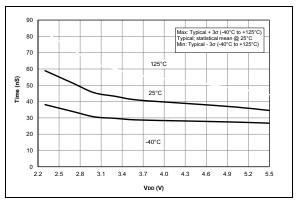

**FIGURE 31-124:** Comparator Output Filter Delay Time Over Temp., NP Mode (CxSP = 1), Typical Measured Values, PIC16LF1784/6/7 Only.

**FIGURE 31-121:** Comparator Offset, NP Mode (CxSP = 1), VDD = 5.0V, Typical Measured Values From -40°C to 125°C, PIC16F1784/6/7 Only.

**FIGURE 31-123:** Comparator Response Time Over Voltage, NP Mode (CxSP = 1), Typical Measured Values, PIC16F1784/6/7 Only.

**FIGURE 31-125:** Comparator Output Filter Delay Time Over Temp., NP Mode (CxSP = 1), Typical Measured Values, PIC16F1784/6/7 Only.

Note: Unless otherwise noted, VIN = 5V, Fosc = 300 kHz, CIN = 0.1  $\mu$ F, TA = 25°C.

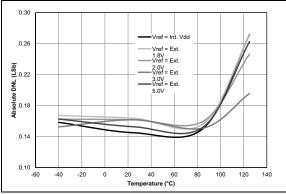

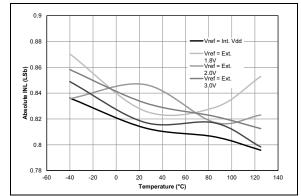

FIGURE 31-132: Absolute Value of DAC DNL Error, VDD = 5.0V, PIC16F1784/6/7 Only.

**FIGURE 31-133:** Absolute Value of DAC INL Error, VDD = 5.0V, PIC16F1784/6/7 Only.

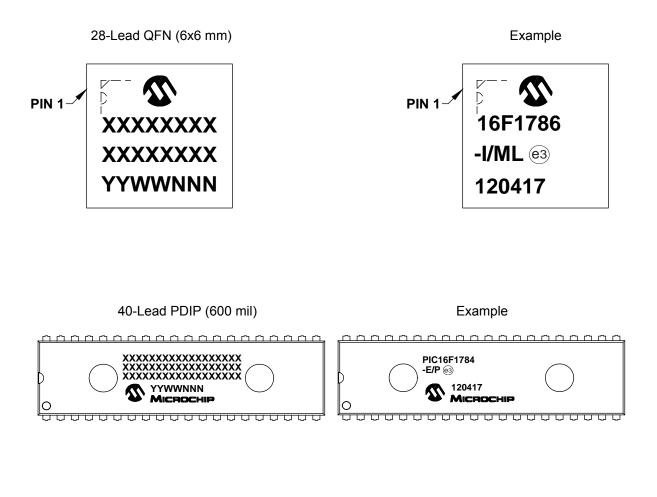

**Package Marking Information (Continued)**

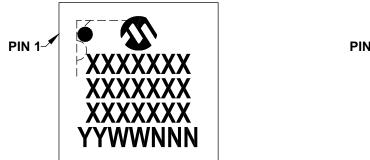

40-Lead UQFN (5x5x0.5 mm)

Example