Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2 0 0 0 0 0                |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PSMC, PWM, WDT                                |

| Number of I/O              | 35                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 14x12b; D/A 1x8b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

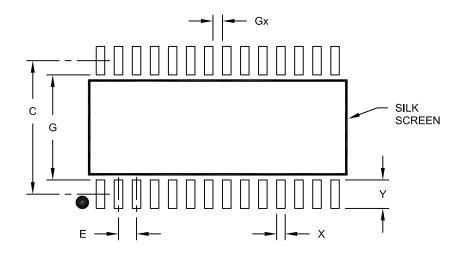

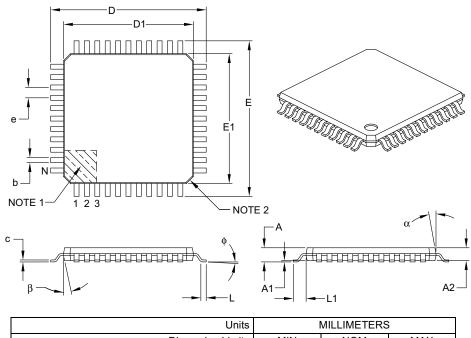

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 40-UFQFN Exposed Pad                                                       |

| Supplier Device Package    | 40-UQFN (5x5)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1787-e-mv |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Value on Value on Addr Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Name all other POR, BOR Resets Bank 16 (Continued) PSMC3LD **P3DBRE** 851h PSMC3CON PSMC3EN **P3DBFE** P3MODE<3:0> 0000 0000 0000 0000 PSMC3MDL P3MDLEN 852h P3MDLPOL P3MDLBIT P3MSRC<3:0> \_ 000- 0000 000 -0000 --00 853h PSMC3SYNC **P3POFST P3PRPOL P3DCPOL** \_ P3SYNC<1:0> 000---00 000-P3CPRE<1:0> P3CSRC<1:0> 854h PSMC3CLK -00 --00 -00 --00 855h PSMC3OEN P3OEB P3OEA --00 --00 \_ \_ \_ \_ \_ \_ 856h PSMC3POL **P3INPOL P3POLB** P3POLA \_ -0----00 -0----00 857h PSMC3BLNK P3FEBM<1:0> P3REBM<1:0> --00 --00 --00 --00 858h PSMC3REBS **P3REBSIN** P3REBSC4 P3REBSC3 P3REBSC2 P3REBSC1 0--0 000-0--0 000 P3FEBSC2 859h PSMC3FEBS **P3FEBSIN** P3FEBSC4 P3FEBSC3 P3FEBSC1 0--0 000-0--0 000-85Ah PSMC3PHS **P3PHSIN** P3PHSC4 P3PHSC3 P3PHSC2 P3PHSC1 **P3PHST** 0--0 0000 0--0 0000 PSMC3DCS P3DCSC1 85Bh **P3DCSIN** P3DCSC4 P3DCSC3 P3DCSC2 0--0 0000 P3DCST 0--0 0000 P3PRSC4 P3PRSC3 P3PRSC2 P3PRSC1 85Ch PSMC3PRS **P3PRSIN P3PRST** 0--0 0000 0--0 0000 PSMC3ASDC **P3ARSEN** 85Dh P3ASE **P3ASDEN P3ASDOV** 000- ---0 000----0 \_ 85Eh PSMC3ASDL \_ **P3ASDLB P3ASDLA** ------00 \_\_\_\_ --00 85Fh PSMC3ASDS **P3ASDSIN** P3ASDSC4 P3ASDSC3 P3ASDSC2 P3ASDSC1 0--0 000-0--0 000 860h PSMC3INT **P3TOVIE P3TPHIE P3TDCIE P3TPRIE P3TOVIF** P3TPHIF P3TDCIF P3TPRIF 0000 0000 0000 0000 861h PSMC3PHL Phase Low Count 0000 0000 0000 0000 PSMC3PHH Phase High Count 862h 0000 0000 0000 0000 863h PSMC3DCL Duty Cycle Low Count 0000 0000 0000 0000 864h PSMC3DCH **Duty Cycle High Count** 0000 0000 0000 0000 865h PSMC3PRL Period Low Count 0000 0000 0000 0000 866h PSMC3PRH Period High Count 0000 0000 0000 0000 867h PSMC3TMRL Time base Low Counter 0000 0001 0000 0001 PSMC3TMRH 868h Time base High Counter 0000 0000 0000 0000 869h PSMC3DBR Rising Edge Dead-band Counter 0000 0000 0000 0000 PSMC3DBF 86Ah Falling Edge Dead-band Counter 0000 0000 0000 0000 86Bh PSMC3BLKR Rising Edge Blanking Counter 0000 0000 0000 0000 86Ch PSMC3BLKF Falling Edge Blanking Counter 0000 0000 0000 0000 86Dh PSMC3FFA 0000 Fractional Frequency Adjust Register ----0000 86Eh PSMC3STR0 P3STRA **P3STRB** -01 --01 **P3HSMEN** 86Fh PSMC3STR1 **P3LSMEN** P3SSYNC 0 - - ---00 0-----00

#### TABLE 3-12: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Bank 17-30

Note

| x0Ch |    |               |   |   |

|------|----|---------------|---|---|

| or   |    |               |   |   |

| x8Ch |    |               |   |   |

| to   | _  | Unimplemented | — | — |

| x1Fh |    |               |   |   |

| or   |    |               |   |   |

| x9Fh |    |               |   |   |

| 1    | -l |               |   |   |

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved.

Shaded locations are unimplemented, read as '0'.

1: These registers can be addressed from any bank.

2: Unimplemented, read as '1'.

3: PIC16(L)F1784/7 only.

4: PIC16F1784/6/7 only.

| Name   | Bit 7  | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1 | Bit 0  | Register<br>on Page |  |

|--------|--------|--------|-------|-------|-------|--------|-------|--------|---------------------|--|

| BORCON | SBOREN | BORFS  | _     |       | _     |        |       | BORRDY | 61                  |  |

| PCON   | STKOVF | STKUNF | _     | RWDT  | RMCLR | RI     | POR   | BOR    | 65                  |  |

| STATUS |        |        | _     | TO    | PD    | Z      | DC    | С      | 27                  |  |

| WDTCON | —      | —      |       | V     |       | SWDTEN | 110   |        |                     |  |

#### TABLE 5-5: SUMMARY OF REGISTERS ASSOCIATED WITH RESETS

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by Resets.

| R/W-0/0      | ) R/W-0/0                                                              | R-0/0                                                     | R-0/0                                             | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0     |  |  |  |

|--------------|------------------------------------------------------------------------|-----------------------------------------------------------|---------------------------------------------------|----------------|------------------|------------------|-------------|--|--|--|

| TMR1G        | F ADIF                                                                 | RCIF                                                      | TXIF                                              | SSP1IF         | CCP1IF           | TMR2IF           | TMR1IF      |  |  |  |

| bit 7        |                                                                        |                                                           |                                                   |                |                  |                  | bit         |  |  |  |

|              |                                                                        |                                                           |                                                   |                |                  |                  |             |  |  |  |

| Legend:      |                                                                        |                                                           |                                                   |                |                  |                  |             |  |  |  |

| R = Reada    | ble bit                                                                | W = Writable                                              | bit                                               | U = Unimpler   | mented bit, reac | l as '0'         |             |  |  |  |

| u = Bit is u | nchanged                                                               | x = Bit is unk                                            | nown                                              | -n/n = Value a | at POR and BO    | R/Value at all c | ther Resets |  |  |  |

| '1' = Bit is | set                                                                    | '0' = Bit is cle                                          | ared                                              |                |                  |                  |             |  |  |  |

| bit 7        | TMR1GIF:                                                               | : Timer1 Gate Inte                                        | errupt Flag bit                                   |                |                  |                  |             |  |  |  |

|              |                                                                        | pt is pending<br>pt is not pending                        |                                                   |                |                  |                  |             |  |  |  |

| bit 6        |                                                                        | C Converter Interi                                        | upt Flag bit                                      |                |                  |                  |             |  |  |  |

|              | 1 = Interru                                                            | pt is pending<br>pt is not pending                        |                                                   |                |                  |                  |             |  |  |  |

| bit 5        |                                                                        | SART Receive Int                                          | errupt Flag bi                                    | t              |                  |                  |             |  |  |  |

|              |                                                                        | pt is pending                                             |                                                   |                |                  |                  |             |  |  |  |

|              |                                                                        | pt is not pending                                         |                                                   |                |                  |                  |             |  |  |  |

| bit 4        | TXIF: EUSART Transmit Interrupt Flag bit                               |                                                           |                                                   |                |                  |                  |             |  |  |  |

|              | 1 = Interrupt is pending<br>0 = Interrupt is not pending               |                                                           |                                                   |                |                  |                  |             |  |  |  |

| bit 3        | <b>SSP1IF:</b> S                                                       | SSP1IF: Synchronous Serial Port (MSSP) Interrupt Flag bit |                                                   |                |                  |                  |             |  |  |  |

|              |                                                                        | pt is pending<br>pt is not pending                        |                                                   |                |                  |                  |             |  |  |  |

| bit 2        | CCP1IF: (                                                              | CCP1 Interrupt Fla                                        | ag bit                                            |                |                  |                  |             |  |  |  |

|              |                                                                        | pt is pending                                             |                                                   |                |                  |                  |             |  |  |  |

|              |                                                                        | pt is not pending                                         |                                                   |                |                  |                  |             |  |  |  |

| bit 1        |                                                                        | Timer2 to PR2 Inte                                        | errupt Flag bit                                   |                |                  |                  |             |  |  |  |

|              |                                                                        | pt is pending<br>pt is not pending                        |                                                   |                |                  |                  |             |  |  |  |

| bit 0        |                                                                        | Timer1 Overflow I                                         | nterrupt Flag I                                   | oit            |                  |                  |             |  |  |  |

|              |                                                                        | pt is pending                                             |                                                   |                |                  |                  |             |  |  |  |

|              |                                                                        | pt is not pending                                         |                                                   |                |                  |                  |             |  |  |  |

| Note:        | condition occur<br>its correspondin<br>Enable bit, GIE<br>User softwar | errupt flag bits                                          | e state of<br>he Global<br>I register.<br>ure the |                |                  |                  |             |  |  |  |

### REGISTER 8-6: PIR1: PERIPHERAL INTERRUPT REQUEST REGISTER 1

### 12.3 Flash Program Memory Overview

It is important to understand the Flash program memory structure for erase and programming operations. Flash program memory is arranged in rows. A row consists of a fixed number of 14-bit program memory words. A row is the minimum block size that can be erased by user software.

Flash program memory may only be written or erased if the destination address is in a segment of memory that is not write-protected, as defined in bits WRT<1:0> of Configuration Words.

After a row has been erased, the user can reprogram all or a portion of this row. Data to be written into the program memory row is written to 14-bit wide data write latches. These write latches are not directly accessible to the user, but may be loaded via sequential writes to the EEDATH:EEDATL register pair.

| Note: | If the user wants to modify only a portion |

|-------|--------------------------------------------|

|       | of a previously programmed row, then the   |

|       | contents of the entire row must be read    |

|       | and saved in RAM prior to the erase.       |

The number of data write latches may not be equivalent to the number of row locations. During programming, user software may need to fill the set of write latches and initiate a programming operation multiple times in order to fully reprogram an erased row. For example, a device with a row size of 32 words and eight write latches will need to load the write latches with data and initiate a programming operation four times.

The size of a program memory row and the number of program memory write latches may vary by device. See Table 12-1 for details.

# 12.3.1 READING THE FLASH PROGRAM MEMORY

To read a program memory location, the user must:

- 1. Write the Least and Most Significant address bits to the EEADRH:EEADRL register pair.

- 2. Clear the CFGS bit of the EECON1 register.

- 3. Set the EEPGD control bit of the EECON1 register.

- 4. Then, set control bit RD of the EECON1 register.

Once the read control bit is set, the program memory Flash controller will use the second instruction cycle to read the data. This causes the second instruction immediately following the "BSF EECON1, RD" instruction to be ignored. The data is available in the very next cycle, in the EEDATH:EEDATL register pair; therefore, it can be read as two bytes in the following instructions.

EEDATH:EEDATL register pair will hold this value until another read or until it is written to by the user.

- Note 1: The two instructions following a program memory read are required to be NOPS. This prevents the user from executing a two-cycle instruction on the next instruction after the RD bit is set.

- 2: Flash program memory can be read regardless of the setting of the CP bit.

#### TABLE 12-1: FLASH MEMORY ORGANIZATION BY DEVICE

| Device            | Erase Block (Row) Size/Boundary | Number of Write Latches/Boundary |  |  |

|-------------------|---------------------------------|----------------------------------|--|--|

| PIC16(L)F1784/6/7 | 32 words, EEADRL<4:0> = 00000   | 32 words, EEADRL<4:0> = 00000    |  |  |

#### 13.11 PORTE Registers

RE3 is input only, and also functions as MCLR. The MCLR feature can be disabled via a configuration fuse. RE3 also supplies the programming voltage. The TRIS bit for RE3 (TRISE3) always reads '1'.

#### 13.11.1 DATA REGISTER

PORTE is an 8-bit wide bidirectional port. The corresponding data direction register is TRISE (Register 13-35). Setting a TRISE bit (= 1) will make the corresponding PORTE pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISE bit (= 0) will make the corresponding PORTE pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). Example 13-1 shows how to initialize an I/O port.

Reading the PORTE register (Register 13-34) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATE).

#### 13.11.2 DIRECTION CONTROL

The TRISE register (Register 13-35) controls the PORTE pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISE register are maintained set when using them as analog inputs. I/O pins configured as analog inputs always read '0'.

#### 13.11.3 OPEN DRAIN CONTROL

The ODCONE register (Register 13-31) controls the open-drain feature of the port. Open drain operation is independently selected for each pin. When an ODCONE bit is set, the corresponding port output becomes an open drain driver capable of sinking current only. When an ODCONE bit is cleared, the corresponding port output pin is the standard push-pull drive capable of sourcing and sinking current.

#### 13.11.4 SLEW RATE CONTROL

The SLRCOND register (Register 13-32) controls the slew rate option for each port pin. Slew rate control is independently selectable for each port pin. When an SLRCOND bit is set, the corresponding port pin drive is slew rate limited. When an SLRCOND bit is cleared, The corresponding port pin drive slews at the maximum rate possible.

#### 13.11.5 INPUT THRESHOLD CONTROL

The INLVLD register (Register 13-33) controls the input voltage threshold for each of the available PORTD input pins. A selection between the Schmitt Trigger CMOS or the TTL Compatible thresholds is available. The input threshold is important in determining the value of a read of the PORTD register and also the

level at which an interrupt-on-change occurs, if that feature is enabled. See Section 30.1 "DC Characteristics: PIC16(L)F1784/6/7-I/E (Industrial, Extended)" for more information on threshold levels.

| Note: | Changing the input threshold selection<br>should be performed while all peripheral |

|-------|------------------------------------------------------------------------------------|

|       | modules are disabled. Changing the                                                 |

|       | threshold level during the time a module is                                        |

|       | active may inadvertently generate a tran-                                          |

|       | sition associated with an input pin, regard-                                       |

|       | less of the actual voltage level on that pin.                                      |

#### 13.11.6 INPUT THRESHOLD CONTROL

The INLVLE register (Register 13-41) controls the input voltage threshold for each of the available PORTE input pins. A selection between the Schmitt Trigger CMOS or the TTL Compatible thresholds is available. The input threshold is important in determining the value of a read of the PORTE register and also the level at which an interrupt-on-change occurs, if that feature is enabled. See **Section TABLE 30-1: "Supply Voltage"** for more information on threshold levels.

Note: Changing the input threshold selection should be performed while all peripheral modules are disabled. Changing the threshold level during the time a module is active may inadvertently generate a transition associated with an input pin, regardless of the actual voltage level on that pin.

| R/W-x/u                           | R/W-x/u | R/W-x/u           | R/W-x/u | R/W-x/u                                                 | R/W-x/u          | R/W-x/u  | R/W-x/u |  |

|-----------------------------------|---------|-------------------|---------|---------------------------------------------------------|------------------|----------|---------|--|

|                                   |         |                   | AD<     | 11:4>                                                   |                  |          |         |  |

| bit 7                             |         |                   |         |                                                         |                  |          | bit 0   |  |

|                                   |         |                   |         |                                                         |                  |          |         |  |

| Legend:                           |         |                   |         |                                                         |                  |          |         |  |

| R = Readable bit W = Writable bit |         |                   |         | U = Unimpler                                            | nented bit, read | d as '0' |         |  |

| u = Bit is unch                   | anged   | x = Bit is unkn   | nown    | vn -n/n = Value at POR and BOR/Value at all other Reset |                  |          |         |  |

| '1' = Bit is set                  |         | '0' = Bit is clea | ared    |                                                         |                  |          |         |  |

#### **REGISTER 17-4:** ADRESH: ADC RESULT REGISTER HIGH (ADRESH) ADFM = 0

bit 7-0 AD<11:4>: ADC Result Register bits Upper 8 bits of 12-bit conversion result

#### **REGISTER 17-5:** ADRESL: ADC RESULT REGISTER LOW (ADRESL) ADFM = 0

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         | AD<     | 3:0>    |         | —       | —       | —       | ADSIGN  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-4 AD<3:0>: ADC Result Register bits Lower 4 bits of 12-bit conversion result

bit 3-1 Extended LSb bits: These are cleared to zero by DC conversion.

bit 0 ADSIGN: ADC Result Sign bit

| R/W-0/0          | R/W-0/0                                                                                                                                                                         | R/W-0/0                                                                          | U-0          | R/W-0/0                            | R/W-0/0          | R/W-0/0           | R/W-0/0      |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|--------------|------------------------------------|------------------|-------------------|--------------|--|--|

| PxMDLEN          | PxMDLPOL                                                                                                                                                                        | PxMDLBIT                                                                         | _            |                                    | PxMSR            | C<3:0>            |              |  |  |

| bit 7            |                                                                                                                                                                                 |                                                                                  |              |                                    |                  |                   | bit          |  |  |

|                  |                                                                                                                                                                                 |                                                                                  |              |                                    |                  |                   |              |  |  |

| Legend:          |                                                                                                                                                                                 |                                                                                  |              |                                    |                  |                   |              |  |  |

| R = Readable     | bit                                                                                                                                                                             | W = Writable b                                                                   | it           | U = Unimpler                       | nented bit, read | l as '0'          |              |  |  |

| u = Bit is unch  | anged                                                                                                                                                                           | x = Bit is unkno                                                                 | own          | -n/n = Value a                     | at POR and BO    | R/Value at all o  | other Resets |  |  |

| '1' = Bit is set |                                                                                                                                                                                 | '0' = Bit is clea                                                                | red          |                                    |                  |                   |              |  |  |

| bit 7            | PxMDLEN: P                                                                                                                                                                      | SMC Periodic N                                                                   | Iodulation I | Mode Enable bit                    |                  |                   |              |  |  |

|                  |                                                                                                                                                                                 |                                                                                  |              | elected by PxMS                    | SRC<3:0> is in i | ts active state ( | see PxMPOL   |  |  |

|                  |                                                                                                                                                                                 | module is alway                                                                  |              |                                    |                  |                   |              |  |  |

| bit 6            |                                                                                                                                                                                 | PSMC Periodic                                                                    |              | •                                  |                  |                   |              |  |  |

|                  |                                                                                                                                                                                 |                                                                                  |              | Modulation sour<br>Modulation sour |                  |                   |              |  |  |

| bit 5            | <ul> <li>0 = PSMCx is active when the PSMCx Modulation source output equals logic '1' (active-high)</li> <li>PxMDLBIT: PSMC Periodic Modulation Software Control bit</li> </ul> |                                                                                  |              |                                    |                  |                   |              |  |  |

|                  | PxMDLEN = 1 AND PxMSRC<3:0> = 0000                                                                                                                                              |                                                                                  |              |                                    |                  |                   |              |  |  |

|                  | 1 = PSMCx is active when the PxMDLPOL equals logic '0'                                                                                                                          |                                                                                  |              |                                    |                  |                   |              |  |  |

|                  | 0 = PSMCx is active when the PxMDLPOL equals logic '1'                                                                                                                          |                                                                                  |              |                                    |                  |                   |              |  |  |

|                  | PxMDLEN = 0 OR (PxMDLEN = 1 and PxMSRC<3:0> <> '0000')<br>Does not affect module operation                                                                                      |                                                                                  |              |                                    |                  |                   |              |  |  |

| bit 4            |                                                                                                                                                                                 | ted: Read as '0'                                                                 |              |                                    |                  |                   |              |  |  |

| bit 3-0          | PxMSRC<3:0> PSMC Periodic Modulation Source Selection bits                                                                                                                      |                                                                                  |              |                                    |                  |                   |              |  |  |

|                  | 1111 = Reserved                                                                                                                                                                 |                                                                                  |              |                                    |                  |                   |              |  |  |

|                  | 1110 = Reserved                                                                                                                                                                 |                                                                                  |              |                                    |                  |                   |              |  |  |

|                  | 1101 = Reserved                                                                                                                                                                 |                                                                                  |              |                                    |                  |                   |              |  |  |

|                  | 1100 = Reserved<br>1011 = Reserved                                                                                                                                              |                                                                                  |              |                                    |                  |                   |              |  |  |

|                  | 1011 = Reserved                                                                                                                                                                 |                                                                                  |              |                                    |                  |                   |              |  |  |

|                  | 1001 = Reserved                                                                                                                                                                 |                                                                                  |              |                                    |                  |                   |              |  |  |

|                  | 1000 = PSMCx Modulation Source is PSMCxIN pin                                                                                                                                   |                                                                                  |              |                                    |                  |                   |              |  |  |

|                  | 0111 = Reserved                                                                                                                                                                 |                                                                                  |              |                                    |                  |                   |              |  |  |

|                  |                                                                                                                                                                                 | 0110 = PSMCx Modulation Source is CCP2<br>0101 = PSMCx Modulation Source is CCP1 |              |                                    |                  |                   |              |  |  |

|                  | 0100 = Rese                                                                                                                                                                     |                                                                                  |              |                                    |                  |                   |              |  |  |

|                  |                                                                                                                                                                                 | Cx Modulation S                                                                  |              |                                    |                  |                   |              |  |  |

|                  |                                                                                                                                                                                 | Cx Modulation S<br>Cx Modulation S                                               |              |                                    |                  |                   |              |  |  |

|                  |                                                                                                                                                                                 |                                                                                  |              |                                    |                  |                   |              |  |  |

### REGISTER 24-2: PSMCxMDL: PSMC MODULATION CONTROL REGISTER

| R/W-0/0                                      | R/W-0/0                                                                                                                                                                                                                                    | R/W-0/0                    | U-0                            | U-0                                     | U-0              | R/W-0/0          | R/W-0/0     |  |  |  |

|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--------------------------------|-----------------------------------------|------------------|------------------|-------------|--|--|--|

| P3POFS1                                      | F P3PRPOL                                                                                                                                                                                                                                  | P3DCPOL                    | _                              | —                                       | —                | P3SYN            | C<1:0>      |  |  |  |

| bit 7                                        |                                                                                                                                                                                                                                            | •                          |                                | •                                       |                  |                  | bit         |  |  |  |

| Logond:                                      |                                                                                                                                                                                                                                            |                            |                                |                                         |                  |                  |             |  |  |  |

| Legend:<br>R = Readable bit W = Writable bit |                                                                                                                                                                                                                                            |                            |                                | U = Unimpler                            | nented bit, read | as '0'           |             |  |  |  |

| u = Bit is un                                | changed                                                                                                                                                                                                                                    | x = Bit is unkr            | nown                           | -n/n = Value a                          | at POR and BOI   | R/Value at all o | ther Resets |  |  |  |

| '1' = Bit is s                               | et                                                                                                                                                                                                                                         | '0' = Bit is clea          | ared                           |                                         |                  |                  |             |  |  |  |

| bit 6                                        | P3PRPOL: P<br>1 = Selecter                                                                                                                                                                                                                 | SMC3 Period F              | Polarity Even<br>s period ever | nt inputs are inve                      | erted            | π                |             |  |  |  |

| bit 5                                        |                                                                                                                                                                                                                                            | -                          | •                              | nt inputs are not<br>larity Control bit |                  |                  |             |  |  |  |

|                                              | 1 = Selecte                                                                                                                                                                                                                                | d asynchronous             | s duty-cycle                   | event inputs are                        | inverted         |                  |             |  |  |  |

| bit 4-2                                      | Unimplemen                                                                                                                                                                                                                                 | Unimplemented: Read as '0' |                                |                                         |                  |                  |             |  |  |  |

| bit 1-0                                      | P3SYNC<1:0                                                                                                                                                                                                                                 | <b>)&gt;:</b> PSMC3 Per    | iod Synchror                   | nization Mode bi                        | its              |                  |             |  |  |  |

|                                              | <ul> <li>11 = Reserved – Do not use</li> <li>10 = PSMC3 is synchronized with the PSMC2 module (sync_in comes from PSMC2 sync_out)</li> <li>01 = PSMC3 is synchronized with the PSMC1 module (sync_in comes from PSMC1 sync_out)</li> </ul> |                            |                                |                                         |                  |                  |             |  |  |  |

#### REGISTER 24-5: PSMC3SYNC: PSMC3 SYNCHRONIZATION CONTROL REGISTER

- 00 = PSMC3 is synchronized with period event

- 00 1 SW03 is synchronized with period even

| U-0                                                               | R/W-0/0           | R/W-0/0               | R/W-0/0               | R/W-0/0               | R/W-0/0               | R/W-0/0          | R/W-0/0     |

|-------------------------------------------------------------------|-------------------|-----------------------|-----------------------|-----------------------|-----------------------|------------------|-------------|

| _                                                                 | PxPOLIN           | PxPOLF <sup>(1)</sup> | PxPOLE <sup>(1)</sup> | PxPOLD <sup>(1)</sup> | PxPOLC <sup>(1)</sup> | PxPOLB           | PxPOLA      |

| bit 7                                                             |                   |                       |                       |                       |                       |                  | bit 0       |

|                                                                   |                   |                       |                       |                       |                       |                  |             |

| Legend:                                                           |                   |                       |                       |                       |                       |                  |             |

| R = Readable                                                      | e bit             | W = Writable          | bit                   | U = Unimpler          | mented bit, read      | as '0'           |             |

| u = Bit is unc                                                    | hanged            | x = Bit is unkr       | nown                  | -n/n = Value a        | at POR and BOI        | R/Value at all o | ther Resets |

| '1' = Bit is se                                                   | t                 | '0' = Bit is clea     | ared                  |                       |                       |                  |             |

|                                                                   |                   |                       |                       |                       |                       |                  |             |

| bit 7                                                             | Unimplemen        | ted: Read as '        | 0'                    |                       |                       |                  |             |

| bit 6                                                             | PxPOLIN: PS       | SMCxIN Polarit        | y bit                 |                       |                       |                  |             |

|                                                                   | 1 = PSMCx         | IN input is activ     | e-low                 |                       |                       |                  |             |

|                                                                   | 0 = PSMCx         | IN input is activ     | e-high                |                       |                       |                  |             |

| bit 5-0 <b>PxPOLy:</b> PSMCx Output y Polarity bit <sup>(1)</sup> |                   |                       |                       |                       |                       |                  |             |

|                                                                   | 1 = PWM P         | SMCx output y         | is active-low         |                       |                       |                  |             |

|                                                                   | 0 = PWM P         | SMCx output y         | is active-high        |                       |                       |                  |             |

| Note 1: Th                                                        | nese bits are not | implemented c         | on PSMC2.             |                       |                       |                  |             |

#### REGISTER 24-8: PSMCxPOL: PSMC POLARITY CONTROL REGISTER

| REGISTER 24-9: | PSMCxBLNK: PSMC BLANKING CONTROL REGISTER |

|----------------|-------------------------------------------|

| U-0   | U-0 | R/W-0/0 | R/W-0/0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 |

|-------|-----|---------|---------|-----|-----|---------|---------|

| —     | —   | PxFEBM1 | PxFEBM0 | _   | —   | PxREBM1 | PxREBM0 |

| bit 7 |     |         |         |     |     |         | bit 0   |

| Legend:                                                      |           |                            |                                                     |  |  |  |  |

|--------------------------------------------------------------|-----------|----------------------------|-----------------------------------------------------|--|--|--|--|

| R = Readable bit<br>u = Bit is unchanged<br>'1' = Bit is set |           | W = Writable bit           | U = Unimplemented bit, read as '0'                  |  |  |  |  |

|                                                              |           | x = Bit is unknown         | -n/n = Value at POR and BOR/Value at all other Rese |  |  |  |  |

|                                                              |           | '0' = Bit is cleared       |                                                     |  |  |  |  |

| bit 7-6                                                      | Unimplor  | nented: Read as '0'        |                                                     |  |  |  |  |

| DIL 7-0                                                      | Unimplei  | nemeu. Reau as 0           |                                                     |  |  |  |  |

| bit 5-4                                                      | PxFEBM<   | <1:0> PSMC Falling Edge B  | lanking Mode bits                                   |  |  |  |  |

|                                                              | 11 = Rese | served – do not use        |                                                     |  |  |  |  |

|                                                              | 10 = Rese | 10 = Reserved – do not use |                                                     |  |  |  |  |

|                                                              |           |                            |                                                     |  |  |  |  |

- 01 = Immediate blanking

- 00 = No blanking

- bit 3-2 Unimplemented: Read as '0'

- bit 1-0 PxREBM<1:0> PSMC Rising Edge Blanking Mode bits

- 11 = Reserved do not use

- 10 = Reserved do not use

- 01 = Immediate blanking

- 00 = No blanking

#### 26.6.6 I<sup>2</sup>C MASTER MODE TRANSMISSION

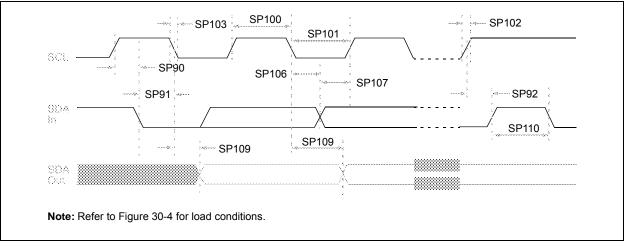

Transmission of a data byte, a 7-bit address or the other half of a 10-bit address is accomplished by simply writing a value to the SSPBUF register. This action will set the Buffer Full flag bit, BF and allow the Baud Rate Generator to begin counting and start the next transmission. Each bit of address/data will be shifted out onto the SDA pin after the falling edge of SCL is asserted. SCL is held low for one Baud Rate Generator rollover count (TBRG). Data should be valid before SCL is released high. When the SCL pin is released high, it is held that way for TBRG. The data on the SDA pin must remain stable for that duration and some hold time after the next falling edge of SCL. After the eighth bit is shifted out (the falling edge of the eighth clock), the BF flag is cleared and the master releases SDA. This allows the slave device being addressed to respond with an ACK bit during the ninth bit time if an address match occurred, or if data was received properly. The status of ACK is written into the ACKSTAT bit on the rising edge of the ninth clock. If the master receives an Acknowledge, the Acknowledge Status bit, ACKSTAT, is cleared. If not, the bit is set. After the ninth clock, the SSP1IF bit is set and the master clock (Baud Rate Generator) is suspended until the next data byte is loaded into the SSPBUF, leaving SCL low and SDA unchanged (Figure 26-27).

After the write to the SSPBUF, each bit of the address will be shifted out on the falling edge of SCL until all seven address bits and the R/W bit are completed. On the falling edge of the eighth clock, the master will release the SDA pin, allowing the slave to respond with an Acknowledge. On the falling edge of the ninth clock, the master will sample the SDA pin to see if the address was recognized by a slave. The status of the ACK bit is loaded into the ACKSTAT Status bit of the SSPCON2 register. Following the falling edge of the ninth clock transmission of the address, the SSP1IF is set, the BF flag is cleared and the Baud Rate Generator is turned off until another write to the SSPBUF takes place, holding SCL low and allowing SDA to float.

#### 26.6.6.1 BF Status Flag

In Transmit mode, the BF bit of the SSPSTAT register is set when the CPU writes to SSPBUF and is cleared when all 8 bits are shifted out.

#### 26.6.6.2 WCOL Status Flag

If the user writes the SSPBUF when a transmit is already in progress (i.e., SSPSR is still shifting out a data byte), the WCOL is set and the contents of the buffer are unchanged (the write does not occur).

WCOL must be cleared by software before the next transmission.

#### 26.6.6.3 ACKSTAT Status Flag

In Transmit mode, the ACKSTAT bit of the SSPCON2 register is cleared when the slave has sent an Acknowledge ( $\overrightarrow{ACK} = 0$ ) and is set when the slave does not Acknowledge ( $\overrightarrow{ACK} = 1$ ). A slave sends an Acknowledge when it has recognized its address (including a general call), or when the slave has properly received its data.

26.6.6.4 Typical transmit sequence:

- 1. The user generates a Start condition by setting the SEN bit of the SSPCON2 register.

- 2. SSP1IF is set by hardware on completion of the Start.

- 3. SSP1IF is cleared by software.

- 4. The MSSP module will wait the required start time before any other operation takes place.

- 5. The user loads the SSPBUF with the slave address to transmit.

- 6. Address is shifted out the SDA pin until all 8 bits are transmitted. Transmission begins as soon as SSPBUF is written to.

- The MSSP module shifts in the ACK bit from the slave device and writes its value into the ACKSTAT bit of the SSPCON2 register.

- 8. The MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSP1IF bit.

- 9. The user loads the SSPBUF with eight bits of data.

- 10. Data is shifted out the SDA pin until all 8 bits are transmitted.

- 11. The MSSP module shifts in the ACK bit from the slave device and writes its value into the ACKSTAT bit of the SSPCON2 register.

- 12. Steps 8-11 are repeated for all transmitted data bytes.

- The user generates a Stop or Restart condition by setting the PEN or RSEN bits of the SSP-CON2 register. Interrupt is generated once the Stop/Restart condition is complete.

## 26.8 Register Definitions: MSSP Control

| R/W-0/0                 | R/W-0/0                                                                                                                                                                                  | R-0/0                                                                                                                                                                   | R-0/0             | R-0/0            | R-0/0                | R-0/0               | R-0/0        |  |  |  |  |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------------|----------------------|---------------------|--------------|--|--|--|--|

| SMP                     | CKE                                                                                                                                                                                      | D/A                                                                                                                                                                     | Р                 | S                | R/W                  | UA                  | BF           |  |  |  |  |

| bit 7                   |                                                                                                                                                                                          |                                                                                                                                                                         |                   |                  |                      |                     | bit          |  |  |  |  |

| o a o a d o             |                                                                                                                                                                                          |                                                                                                                                                                         |                   |                  |                      |                     |              |  |  |  |  |

| Legend:<br>R = Readable | bit                                                                                                                                                                                      | W = Writable b                                                                                                                                                          | it                | U = Unimpleme    | ented bit, read as   | '0'                 |              |  |  |  |  |

| u = Bit is uncha        |                                                                                                                                                                                          | x = Bit is unkno                                                                                                                                                        |                   | •                | POR and BOR/V        |                     | Resets       |  |  |  |  |

| '1' = Bit is set        |                                                                                                                                                                                          | '0' = Bit is clea                                                                                                                                                       |                   |                  |                      |                     |              |  |  |  |  |

|                         |                                                                                                                                                                                          |                                                                                                                                                                         |                   |                  |                      |                     |              |  |  |  |  |

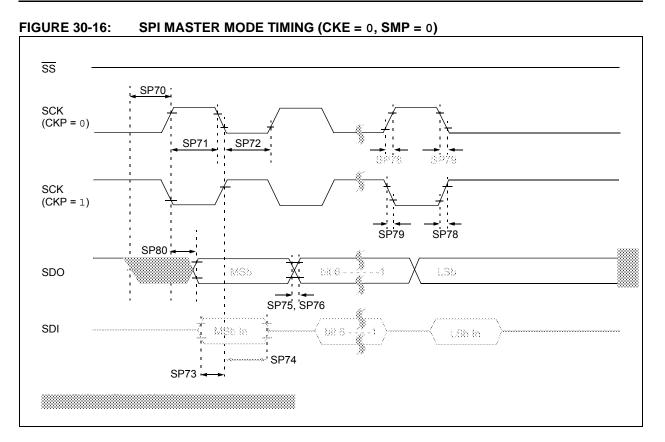

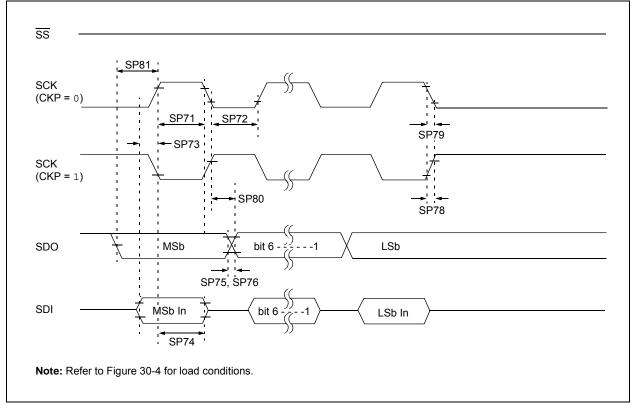

| bit 7                   | SMP: SPI Data                                                                                                                                                                            | a Input Sample b                                                                                                                                                        | it                |                  |                      |                     |              |  |  |  |  |

|                         | SPI Master mo                                                                                                                                                                            |                                                                                                                                                                         |                   |                  |                      |                     |              |  |  |  |  |

|                         | 1 = Input data sampled at end of data output time                                                                                                                                        |                                                                                                                                                                         |                   |                  |                      |                     |              |  |  |  |  |

|                         | 0 = Input data sampled at middle of data output time<br>SPI Slave mode:                                                                                                                  |                                                                                                                                                                         |                   |                  |                      |                     |              |  |  |  |  |

|                         | <u>SPI Slave mode:</u><br>SMP must be cleared when SPI is used in Slave mode                                                                                                             |                                                                                                                                                                         |                   |                  |                      |                     |              |  |  |  |  |

|                         | In I <sup>2</sup> C Master or Slave mode:                                                                                                                                                |                                                                                                                                                                         |                   |                  |                      |                     |              |  |  |  |  |

|                         | <ul> <li>1 = Slew rate control disabled for standard speed mode (100 kHz and 1 MHz)</li> <li>0 = Slew rate control enabled for high speed mode (400 kHz)</li> </ul>                      |                                                                                                                                                                         |                   |                  |                      |                     |              |  |  |  |  |

| oit 6                   |                                                                                                                                                                                          |                                                                                                                                                                         | 0                 | · · · · ·        |                      |                     |              |  |  |  |  |

|                         | CKE: SPI Clock Edge Select bit (SPI mode only)<br>In SPI Master or Slave mode:                                                                                                           |                                                                                                                                                                         |                   |                  |                      |                     |              |  |  |  |  |

|                         | 1 = Transmit occurs on transition from active to Idle clock state                                                                                                                        |                                                                                                                                                                         |                   |                  |                      |                     |              |  |  |  |  |

|                         | 0 = Transmit occurs on transition from Idle to active clock state                                                                                                                        |                                                                                                                                                                         |                   |                  |                      |                     |              |  |  |  |  |

|                         | In I <sup>2</sup> C™ mode only:<br>1 = Enable input logic so that thresholds are compliant with SMBus specification                                                                      |                                                                                                                                                                         |                   |                  |                      |                     |              |  |  |  |  |

|                         | 0 = Disable SMBus specific inputs                                                                                                                                                        |                                                                                                                                                                         |                   |                  |                      |                     |              |  |  |  |  |

| bit 5                   | D/A: Data/Add                                                                                                                                                                            | D/A: Data/Address bit (I <sup>2</sup> C mode only)                                                                                                                      |                   |                  |                      |                     |              |  |  |  |  |

|                         |                                                                                                                                                                                          |                                                                                                                                                                         |                   | smitted was data |                      |                     |              |  |  |  |  |

|                         |                                                                                                                                                                                          | hat the last byte                                                                                                                                                       | received or trans | smitted was addr | ess                  |                     |              |  |  |  |  |

| bit 4                   | P: Stop bit                                                                                                                                                                              | . This bit is slear                                                                                                                                                     |                   | CD maaduda ia di |                      |                     |              |  |  |  |  |

|                         | (I <sup>2</sup> C mode only. This bit is cleared when the MSSP module is disabled, SSPEN is cleared.)<br>1 = Indicates that a Stop bit has been detected last (this bit is '0' on Reset) |                                                                                                                                                                         |                   |                  |                      |                     |              |  |  |  |  |

|                         | <ul> <li>I = Indicates that a Stop bit has been detected last (this bit is '0' on Reset)</li> <li>0 = Stop bit was not detected last</li> </ul>                                          |                                                                                                                                                                         |                   |                  |                      |                     |              |  |  |  |  |

| bit 3                   | S: Start bit                                                                                                                                                                             |                                                                                                                                                                         |                   |                  |                      |                     |              |  |  |  |  |

|                         | (I <sup>2</sup> C mode only. This bit is cleared when the MSSP module is disabled, SSPEN is cleared.)                                                                                    |                                                                                                                                                                         |                   |                  |                      |                     |              |  |  |  |  |

|                         | 1 = Indicates that a Start bit has been detected last (this bit is '0' on Reset)                                                                                                         |                                                                                                                                                                         |                   |                  |                      |                     |              |  |  |  |  |

|                         |                                                                                                                                                                                          | as not detected la                                                                                                                                                      |                   |                  |                      |                     |              |  |  |  |  |

| bit 2                   |                                                                                                                                                                                          | rite bit information                                                                                                                                                    |                   |                  | natch. This hit is a | only valid from the | addross mate |  |  |  |  |

|                         | to the next Sta                                                                                                                                                                          | This bit holds the R/W bit information following the last address match. This bit is only valid from the address match to the next Start bit, Stop bit, or not ACK bit. |                   |                  |                      |                     |              |  |  |  |  |

|                         | In I <sup>2</sup> C Slave m<br>1 = Read                                                                                                                                                  | iode:                                                                                                                                                                   |                   |                  |                      |                     |              |  |  |  |  |

|                         | 0 = Write                                                                                                                                                                                |                                                                                                                                                                         |                   |                  |                      |                     |              |  |  |  |  |

|                         | In I <sup>2</sup> C Master                                                                                                                                                               |                                                                                                                                                                         |                   |                  |                      |                     |              |  |  |  |  |

|                         | 1 = Transmit                                                                                                                                                                             |                                                                                                                                                                         |                   |                  |                      |                     |              |  |  |  |  |

|                         |                                                                                                                                                                                          | is not in progress<br>his bit with SEN                                                                                                                                  |                   | CEN or ACKEN M   | vill indicate if the | MSSP is in Idle m   | node         |  |  |  |  |

| bit 1                   |                                                                                                                                                                                          | ddress bit (10-bit                                                                                                                                                      |                   |                  |                      |                     |              |  |  |  |  |

|                         |                                                                                                                                                                                          |                                                                                                                                                                         |                   | address in the S | SPADD register       |                     |              |  |  |  |  |

|                         | 0 = Address d                                                                                                                                                                            |                                                                                                                                                                         |                   |                  |                      |                     |              |  |  |  |  |

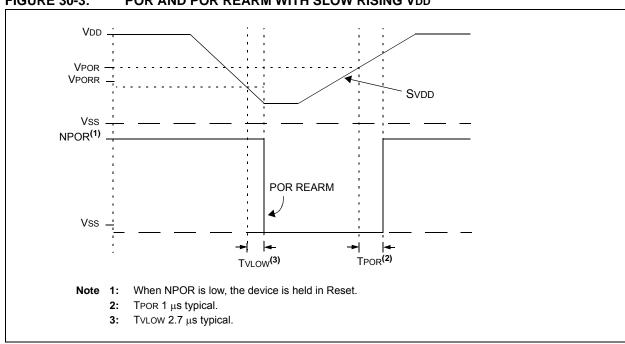

#### FIGURE 30-3: POR AND POR REARM WITH SLOW RISING VDD

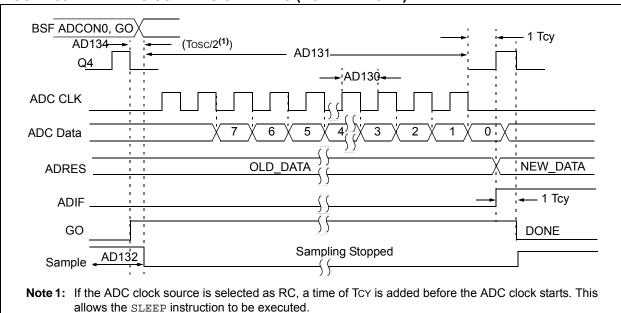

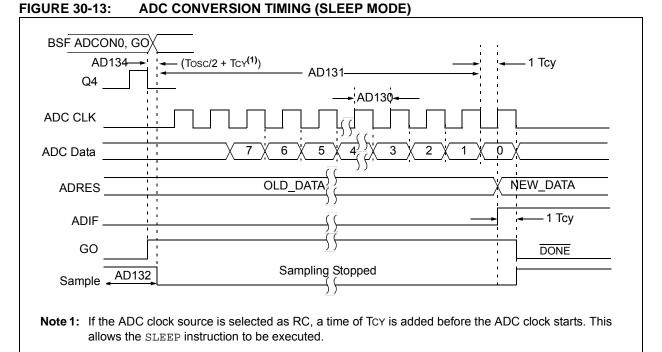

#### FIGURE 30-12: ADC CONVERSION TIMING (NORMAL MODE)

#### TABLE 30-17: DIGITAL-TO-ANALOG CONVERTER (DAC) SPECIFICATIONS

| Operating    | <b>Operating Conditions:</b> VDD = 3V, Temperature = 25°C (unless otherwise stated). |                              |      |         |       |       |          |  |  |  |

|--------------|--------------------------------------------------------------------------------------|------------------------------|------|---------|-------|-------|----------|--|--|--|

| Param<br>No. | Sym.                                                                                 | Characteristics              | Min. | Тур.    | Max.  | Units | Comments |  |  |  |

| DAC01*       | CLSB                                                                                 | Step Size                    | —    | VDD/256 |       | V     |          |  |  |  |

| DAC02*       | CACC                                                                                 | Absolute Accuracy            | _    | —       | ± 1.5 | LSb   |          |  |  |  |

| DAC03*       | CR                                                                                   | Unit Resistor Value (R)      | _    | 600     | _     | Ω     |          |  |  |  |