Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | HC08                                                                    |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 8MHz                                                                    |

| Connectivity               | -                                                                       |

| Peripherals                | LVD, POR, PWM                                                           |

| Number of I/O              | 5                                                                       |

| Program Memory Size        | 1.5KB (1.5K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 128 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                             |

| Data Converters            | -                                                                       |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

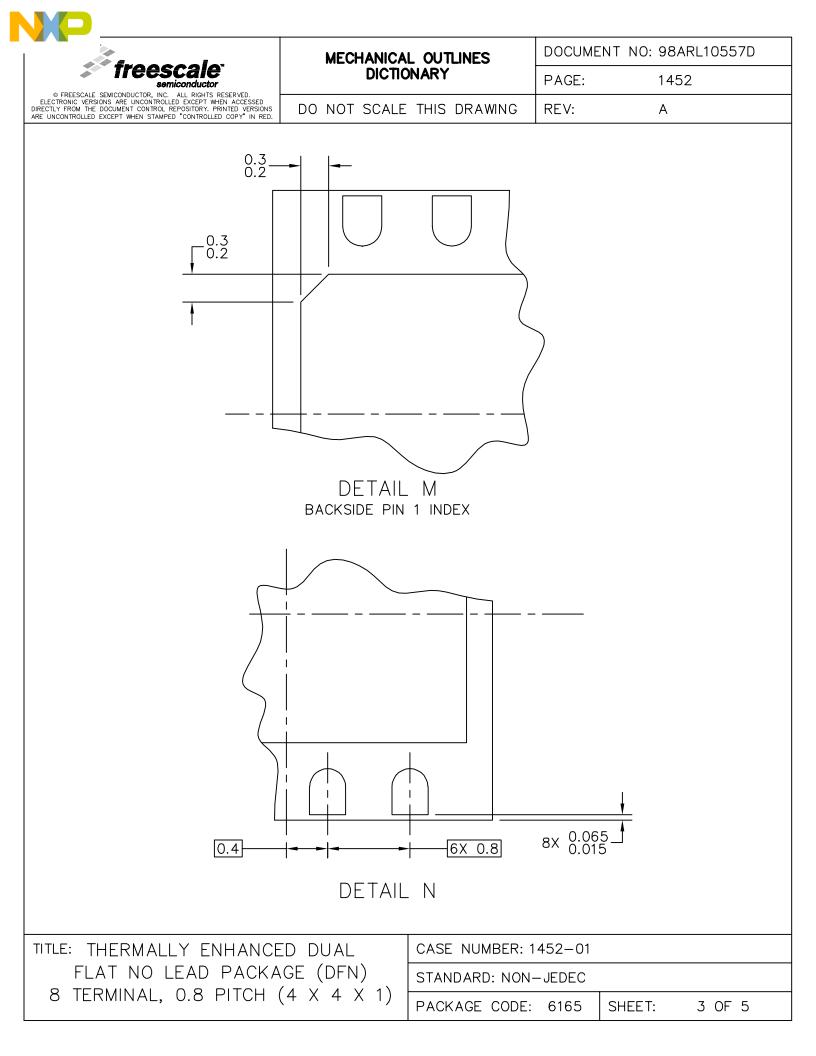

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 8-SOIC (0.209", 5.30mm Width)                                           |

| Supplier Device Package    | 8-SO                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc68hc908qt1cdw |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Chapter 12 Input/Output Ports (PORTS)

| 12.1   | Introduction                          | 97 |

|--------|---------------------------------------|----|

|        | Port A                                |    |

| 12.2.1 | Port A Data Register                  | 98 |

| 12.2.2 |                                       | 98 |

| 12.2.3 | Port A Input Pullup Enable Register   | 99 |

|        | Port B 1                              | 00 |

| 12.3.1 |                                       |    |

| 12.3.2 |                                       |    |

| 12.3.3 | Port B Input Pullup Enable Register 1 | 02 |

# Chapter 13 System Integration Module (SIM)

| 13.1 Intr | roduction                               | 103 |

|-----------|-----------------------------------------|-----|

| 13.2 RS   | T and IRQ Pins Initialization           | 104 |

| 13.3 SIN  | M Bus Clock Control and Generation      | 104 |

| 13.3.1    | Bus Timing                              |     |

| 13.3.2    | Clock Start-Up from POR                 | 105 |

| 13.3.3    | Clocks in Stop Mode and Wait Mode       | 105 |

| 13.4 Re   | set and System Initialization           | 105 |

| 13.4.1    | External Pin Reset                      |     |

| 13.4.2    | Active Resets from Internal Sources     | 106 |

| 13.4.2.1  | Power-On Reset                          |     |

| 13.4.2.2  | Computer Operating Properly (COP) Reset |     |

| 13.4.2.3  | Illegal Opcode Reset                    |     |

| 13.4.2.4  | Illegal Address Reset                   |     |

| 13.4.2.5  | Low-Voltage Inhibit (LVI) Reset         |     |

|           | M Counter                               |     |

| 13.5.1    | SIM Counter During Power-On Reset       |     |

| 13.5.2    | SIM Counter During Stop Mode Recovery   |     |

| 13.5.3    | SIM Counter and Reset States            |     |

|           | ception Control                         |     |

| 13.6.1    | Interrupts                              |     |

| 13.6.1.1  | Hardware Interrupts                     |     |

| 13.6.1.2  | SWI Instruction                         |     |

| 13.6.2    | Interrupt Status Registers              |     |

| 13.6.2.1  | Interrupt Status Register 1             |     |

| 13.6.2.2  | Interrupt Status Register 2             |     |

| 13.6.2.3  | Interrupt Status Register 3             |     |

| 13.6.3    | Reset                                   |     |

| 13.6.4    | Break Interrupts                        |     |

| 13.6.5    | Status Flag Protection in Break Mode    |     |

|           | w-Power Modes                           |     |

| 13.7.1    | Wait Mode                               |     |

| 13.7.2    | Stop Mode                               | 115 |

#### Input/Output (I/O) Section

| Addr.                 | Register Name                                         |                 | Bit 7                     | 6               | 5      | 4                           | 3              | 2      | 1     | Bit 0    |  |

|-----------------------|-------------------------------------------------------|-----------------|---------------------------|-----------------|--------|-----------------------------|----------------|--------|-------|----------|--|

|                       | TIM Counter Register Low                              | Read:           | Bit 7                     | Bit 6           | Bit 5  | Bit 4                       | Bit 3          | Bit 2  | Bit 1 | Bit 0    |  |

| \$0022                | (TCNTL)                                               | Write:          |                           |                 |        |                             |                |        |       |          |  |

|                       | See page 128.                                         | Reset:          | 0                         | 0               | 0      | 0                           | 0              | 0      | 0     | 0        |  |

| \$0023                | TIM Counter Modulo<br>Register High (TMODH)           | Read:<br>Write: | Bit 15                    | Bit 14          | Bit 13 | Bit 12                      | Bit 11         | Bit 10 | Bit 9 | Bit 8    |  |

|                       | See page 129.                                         | Reset:          | 1                         | 1               | 1      | 1                           | 1              | 1      | 1     | 1        |  |

| \$0024                | TIM Counter Modulo<br>Register Low (TMODL)            | Read:<br>Write: | Bit 7                     | Bit 6           | Bit 5  | Bit 4                       | Bit 3          | Bit 2  | Bit 1 | Bit 0    |  |

|                       | See page 129.                                         | Reset:          | 1                         | 1               | 1      | 1                           | 1              | 1      | 1     | 1        |  |

| \$0025                | TIM Channel 0 Status and<br>Control Register (TSC0)   | Read:<br>Write: | CH0F<br>0                 | CH0IE           | MS0B   | MS0A                        | ELS0B          | ELS0A  | TOV0  | CH0MAX   |  |

| Ψ00 <u>2</u> 0        | See page 130.                                         | Reset:          | 0                         | 0               | 0      | 0                           | 0              | 0      | 0     | 0        |  |

| \$0026                | TIM Channel 0<br>Register High (TCH0H)                | Read:<br>Write: | Bit 15                    | Bit 14          | Bit 13 | Bit 12                      | Bit 11         | Bit 10 | Bit 9 | Bit 8    |  |

|                       | See page 132.                                         | Reset:          |                           |                 |        | Indetermina                 | te after reset |        |       | <u> </u> |  |

| \$0027                | TIM Channel 0<br>Register Low (TCH0L)                 | Read:<br>Write: | Bit 7                     | Bit 6           | Bit 5  | Bit 4                       | Bit 3          | Bit 2  | Bit 1 | Bit 0    |  |

|                       | See page 132.                                         | Reset:          |                           |                 | 1      | Indeterminate after reset   |                |        |       |          |  |

|                       | TIM Channel 1 Status and<br>Control Register (TSC1)   | Read:           | CH1F                      | CH1IE           | 0      | MS1A                        | ELS1B          | ELS1A  | TOV1  | CH1MAX   |  |

| \$0028                |                                                       | Write:          | 0                         | OTTIL           |        | WIGHA                       |                | 22017  |       | UTTWAX   |  |

|                       | See page 130.                                         | Reset:          | 0                         | 0               | 0      | 0                           | 0              | 0      | 0     | 0        |  |

| \$0029                | TIM Channel 1<br>Register High (TCH1H)                | Read:<br>Write: | Bit 15                    | Bit 14          | Bit 13 | Bit 12                      | Bit 11         | Bit 10 | Bit 9 | Bit 8    |  |

|                       | See page 132.                                         | Reset:          | Indeterminate after reset |                 |        |                             |                |        |       |          |  |

| \$002A                | TIM Channel 1<br>Register Low (TCH1L)                 | Read:<br>Write: | Bit 7                     | Bit 6           | Bit 5  | Bit 4                       | Bit 3          | Bit 2  | Bit 1 | Bit 0    |  |

|                       | See page 132.                                         | Reset:          |                           |                 |        | Indetermina                 |                |        |       |          |  |

| \$002B<br>↓<br>\$0035 | Unimplemented                                         |                 |                           |                 |        |                             |                |        |       |          |  |

|                       |                                                       | L               |                           |                 |        |                             |                |        |       |          |  |

| \$0036                | Oscillator Status Register<br>(OSCSTAT)               | Read:<br>Write: | R                         | R               | R      | R                           | R              | R      | ECGON | ECGST    |  |

|                       | See page 96.                                          | Reset:          | 0                         | 0               | 0      | 0                           | 0              | 0      | 0     | 0        |  |

| \$0037                | Unimplemented                                         | Read:           |                           |                 |        |                             |                |        |       |          |  |

|                       |                                                       | L               |                           | •               | •      |                             |                |        |       |          |  |

| \$0038                | Oscillator Trim Register<br>(OSCTRIM)<br>See page 96. | Read:<br>Write: | TRIM7                     | TRIM6           | TRIM5  | TRIM4                       | TRIM3          | TRIM2  | TRIM1 | TRIM0    |  |

|                       | See page 90.                                          | Reset:          | 1                         | 0               | 0      | 0                           | 0              | 0      | 0     | 0        |  |

|                       |                                                       | [               |                           | = Unimplemented |        | R = Reserved U = Unaffected |                |        |       |          |  |

Figure 2-2. Control, Status, and Data Registers (Sheet 3 of 5)

# 3.5.2 Stop Mode

The ADC module is inactive after the execution of a STOP instruction. Any pending conversion is aborted. ADC conversions resume when the MCU exits stop mode. Allow one conversion cycle to stabilize the analog circuitry before using ADC data after exiting stop mode.

# 3.6 Input/Output Signals

The ADC module has four channels that are shared with I/O port A.

ADC voltage in (ADCVIN) is the input voltage signal from one of the four ADC channels to the ADC module.

# 3.7 Input/Output Registers

These I/O registers control and monitor ADC operation:

- ADC status and control register (ADSCR)

- ADC data register (ADR)

- ADC clock register (ADICLK)

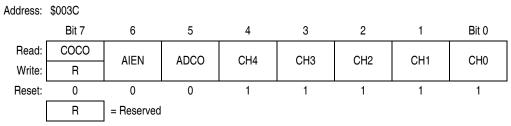

# 3.7.1 ADC Status and Control Register

The following paragraphs describe the function of the ADC status and control register (ADSCR). When a conversion is in process and the ADSCR is written, the current conversion data should be discarded to prevent an incorrect reading.

Figure 3-3. ADC Status and Control Register (ADSCR)

### COCO — Conversions Complete Bit

In non-interrupt mode (AIEN = 0), COCO is a read-only bit that is set at the end of each conversion. COCO will stay set until cleared by a read of the ADC data register. Reset clears this bit.

In interrupt mode (AIEN = 1), COCO is a read-only bit that is not set at the end of a conversion. It always reads as a 0.

1 = Conversion completed (AIEN = 0)

0 = Conversion not completed (AIEN = 0) or CPU interrupt enabled (AIEN = 1)

#### NOTE

The write function of the COCO bit is reserved. When writing to the ADSCR register, always have a 0 in the COCO bit position.

#### Computer Operating Properly (COP)

The COP counter is a free-running 6-bit counter preceded by the 12-bit system integration module (SIM) counter. If not cleared by software, the COP counter overflows and generates an asynchronous reset after 262,128 or 8176 BUSCLKX4 cycles; depending on the state of the COP rate select bit, COPRS, in configuration register 1. With a 262,128 BUSCLKX4 cycle overflow option, the internal 12.8-MHz oscillator gives a COP timeout period of 20.48 ms. Writing any value to location \$FFFF before an overflow occurs prevents a COP reset by clearing the COP counter and stages 12–5 of the SIM counter.

### NOTE

Service the COP immediately after reset and before entering or after exiting stop mode to guarantee the maximum time before the first COP counter overflow.

A COP reset pulls the  $\overline{\text{RST}}$  pin low (if the RSTEN bit is set in the CONFIG1 register) for 32 × BUSCLKX4 cycles and sets the COP bit in the reset status register (RSR). See 13.8.1 SIM Reset Status Register.

### NOTE

Place COP clearing instructions in the main program and not in an interrupt subroutine. Such an interrupt subroutine could keep the COP from generating a reset even while the main program is not working properly.

# 6.3 I/O Signals

The following paragraphs describe the signals shown in Figure 6-1.

# 6.3.1 BUSCLKX4

BUSCLKX4 is the oscillator output signal. BUSCLKX4 frequency is equal to the internal oscillator frequency, the crystal frequency, or the RC-oscillator frequency.

# 6.3.2 STOP Instruction

The STOP instruction clears the SIM counter.

# 6.3.3 COPCTL Write

Writing any value to the COP control register (COPCTL) (see 6.4 COP Control Register) clears the COP counter and clears stages 12–5 of the SIM counter. Reading the COP control register returns the low byte of the reset vector.

# 6.3.4 Power-On Reset

The power-on reset (POR) circuit in the SIM clears the SIM counter  $4096 \times BUSCLKX4$  cycles after power up.

# 6.3.5 Internal Reset

An internal reset clears the SIM counter and the COP counter.

# 6.3.6 COPD (COP Disable)

The COPD signal reflects the state of the COP disable bit (COPD) in the configuration register 1 (CONFIG1). See Chapter 5 Configuration Register (CONFIG).

Computer Operating Properly (COP)

# Chapter 7 Central Processor Unit (CPU)

# 7.1 Introduction

The M68HC08 CPU (central processor unit) is an enhanced and fully object-code-compatible version of the M68HC05 CPU. The *CPU08 Reference Manual* (document order number CPU08RM/AD) contains a description of the CPU instruction set, addressing modes, and architecture.

# 7.2 Features

Features of the CPU include:

- Object code fully upward-compatible with M68HC05 Family

- 16-bit stack pointer with stack manipulation instructions

- 16-bit index register with x-register manipulation instructions

- 8-MHz CPU internal bus frequency

- 64-Kbyte program/data memory space

- 16 addressing modes

- Memory-to-memory data moves without using accumulator

- Fast 8-bit by 8-bit multiply and 16-bit by 8-bit divide instructions

- Enhanced binary-coded decimal (BCD) data handling

- Modular architecture with expandable internal bus definition for extension of addressing range beyond 64 Kbytes

- Low-power stop and wait modes

# 7.3 CPU Registers

Figure 7-1 shows the five CPU registers. CPU registers are not part of the memory map.

**Keyboard Interrupt Module (KBI)**

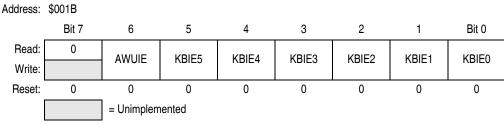

# 9.7.2 Keyboard Interrupt Enable Register

The port A keyboard interrupt enable register (KBIER) enables or disables each port A pin or auto wakeup to operate as a keyboard interrupt input.

### Figure 9-4. Keyboard Interrupt Enable Register (KBIER)

### KBIE5–KBIE0 — Port A Keyboard Interrupt Enable Bits

Each of these read/write bits enables the corresponding keyboard interrupt pin on port A to latch interrupt requests. Reset clears the keyboard interrupt enable register.

1 = KBIx pin enabled as keyboard interrupt pin

0 = KBIx pin not enabled as keyboard interrupt pin

### NOTE

AWUIE bit is not used in conjunction with the keyboard interrupt feature. To see a description of this bit, see Chapter 4 Auto Wakeup Module (AWU).

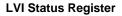

# 10.4 LVI Status Register

The LVI status register (LVISR) indicates if the  $V_{DD}$  voltage was detected below the  $V_{TRIPF}$  level while LVI resets have been disabled.

Figure 10-2. LVI Status Register (LVISR)

### LVIOUT — LVI Output Bit

This read-only flag becomes set when the  $V_{DD}$  voltage falls below the  $V_{TRIPF}$  trip voltage and is cleared when  $V_{DD}$  voltage rises above  $V_{TRIPR}$ . The difference in these threshold levels results in a hysteresis that prevents oscillation into and out of reset (see Table 10-1). Reset clears the LVIOUT bit.

| V <sub>DD</sub>                  | LVIOUT         |  |  |  |

|----------------------------------|----------------|--|--|--|

| $V_{DD} > V_{TRIPR}$             | 0              |  |  |  |

| $V_{DD} < V_{TRIPF}$             | 1              |  |  |  |

| $V_{TRIPF} < V_{DD} < V_{TRIPR}$ | Previous value |  |  |  |

Table 10-1. LVIOUT Bit Indication

# 10.5 LVI Interrupts

The LVI module does not generate interrupt requests.

# **10.6 Low-Power Modes**

The STOP and WAIT instructions put the MCU in low power-consumption standby modes.

# 10.6.1 Wait Mode

If enabled, the LVI module remains active in wait mode. If enabled to generate resets, the LVI module can generate a reset and bring the MCU out of wait mode.

# 10.6.2 Stop Mode

When the LVIPWRD bit in the configuration register is cleared and the LVISTOP bit in the configuration register is set, the LVI module remains active in stop mode. If enabled to generate resets, the LVI module can generate a reset and bring the MCU out of stop mode.

| MODULE<br>INTERRUPT  |                                                                                                                                                                                                                                                                                 |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I BIT                |                                                                                                                                                                                                                                                                                 |

| ADDRESS BUS          | DUMMY SP - 1 SP - 2 SP - 3 SP - 4 VECT H VECT L START ADDR                                                                                                                                                                                                                      |

| DATA BUS             | X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X |

| R/W                  |                                                                                                                                                                                                                                                                                 |

|                      | Figure 13-8. Interrupt Entry                                                                                                                                                                                                                                                    |

| MODULE<br>INTERRUPT_ |                                                                                                                                                                                                                                                                                 |

| I BIT                |                                                                                                                                                                                                                                                                                 |

| ADDRESS BUS          | X     SP-4     SP-3     SP-2     SP-1     SP     PC     YC+1     X     X                                                                                                                                                                                                        |

| DATA BUS             | X X X X Y PC - 1[15:8] OPCODE X Y                                                                                                                                                                                                                                               |

| R/W                  | Y                                                                                                                                                                                                                                                                               |

|                      | Elevine 42.0 Interment Deservery                                                                                                                                                                                                                                                |

#### Figure 13-9. Interrupt Recovery

#### 13.6.1.1 Hardware Interrupts

A hardware interrupt does not stop the current instruction. Processing of a hardware interrupt begins after completion of the current instruction. When the current instruction is complete, the SIM checks all pending hardware interrupts. If interrupts are not masked (I bit clear in the condition code register), and if the corresponding interrupt enable bit is set, the SIM proceeds with interrupt processing; otherwise, the next instruction is fetched and executed.

If more than one interrupt is pending at the end of an instruction execution, the highest priority interrupt is serviced first. Figure 13-10 demonstrates what happens when two interrupts are pending. If an interrupt is pending upon exit from the original interrupt service routine, the pending interrupt is serviced before the LDA instruction is executed.

The LDA opcode is prefetched by both the INT1 and INT2 return-from-interrupt (RTI) instructions. However, in the case of the INT1 RTI prefetch, this is a redundant operation.

#### NOTE

To maintain compatibility with the M6805 Family, the H register is not pushed on the stack during interrupt entry. If the interrupt service routine modifies the H register or uses the indexed addressing mode, software should save the H register and then restore it prior to exiting the routine.

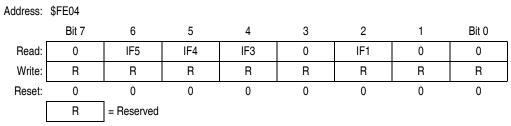

### 13.6.2.1 Interrupt Status Register 1

#### Figure 13-11. Interrupt Status Register 1 (INT1)

#### IF1 and IF3–IF5 — Interrupt Flags

These flags indicate the presence of interrupt requests from the sources shown in Table 13-3.

1 = Interrupt request present

0 = No interrupt request present

#### Bit 0, 1, 3, and 7 — Always read 0

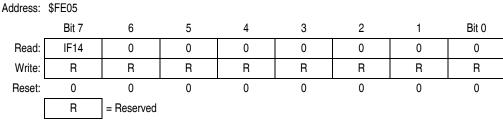

#### 13.6.2.2 Interrupt Status Register 2

### Figure 13-12. Interrupt Status Register 2 (INT2)

#### IF14 — Interrupt Flags

This flag indicates the presence of interrupt requests from the sources shown in Table 13-3. 1 = Interrupt request present

0 = No interrupt request present

#### Bit 0-6 — Always read 0

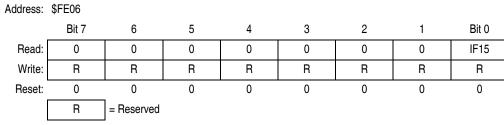

#### 13.6.2.3 Interrupt Status Register 3

#### Figure 13-13. Interrupt Status Register 3 (INT3)

#### IF15 — Interrupt Flags

These flags indicate the presence of interrupt requests from the sources shown in Table 13-3.

- 1 = Interrupt request present

- 0 = No interrupt request present

#### Bit 1–7 — Always read 0

#### System Integration Module (SIM)

### 13.6.3 Reset

All reset sources always have equal and highest priority and cannot be arbitrated.

## 13.6.4 Break Interrupts

The break module can stop normal program flow at a software programmable break point by asserting its break interrupt output. (See Chapter 15 Development Support.) The SIM puts the CPU into the break state by forcing it to the SWI vector location. Refer to the break interrupt subsection of each module to see how each module is affected by the break state.

# 13.6.5 Status Flag Protection in Break Mode

The SIM controls whether status flags contained in other modules can be cleared during break mode. The user can select whether flags are protected from being cleared by properly initializing the break clear flag enable bit (BCFE) in the break flag control register (BFCR).

Protecting flags in break mode ensures that set flags will not be cleared while in break mode. This protection allows registers to be freely read and written during break mode without losing status flag information.

Setting the BCFE bit enables the clearing mechanisms. Once cleared in break mode, a flag remains cleared even when break mode is exited. Status flags with a two-step clearing mechanism — for example, a read of one register followed by the read or write of another — are protected, even when the first step is accomplished prior to entering break mode. Upon leaving break mode, execution of the second step will clear the flag as normal.

# 13.7 Low-Power Modes

Executing the WAIT or STOP instruction puts the MCU in a low power- consumption mode for standby situations. The SIM holds the CPU in a non-clocked state. The operation of each of these modes is described below. Both STOP and WAIT clear the interrupt mask (I) in the condition code register, allowing interrupts to occur.

# 13.7.1 Wait Mode

In wait mode, the CPU clocks are inactive while the peripheral clocks continue to run. Figure 13-14 shows the timing for wait mode entry.

| ADDRESS BUS | WAIT ADDR | WAIT AD | DR + 1 | SAME | X    | SAME | _X |

|-------------|-----------|---------|--------|------|------|------|----|

| DATA BUS    | PREVIOU   | S DATA  |        |      | SAME | SAME |    |

| R/W         |           |         | y      |      |      |      |    |

NOTE: Previous data can be operand data or the WAIT opcode, depending on the last instruction.

Figure 13-14. Wait Mode Entry Timing

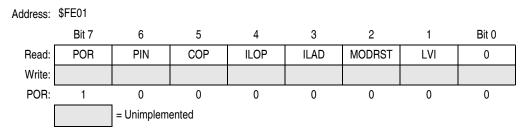

# 13.8.1 SIM Reset Status Register

The SRSR register contains flags that show the source of the last reset. The status register will automatically clear after reading SRSR. A power-on reset sets the POR bit and clears all other bits in the register. All other reset sources set the individual flag bits but do not clear the register. More than one reset source can be flagged at any time depending on the conditions at the time of the internal or external reset. For example, the POR and LVI bit can both be set if the power supply has a slow rise time.

#### Figure 13-19. SIM Reset Status Register (SRSR)

#### POR — Power-On Reset Bit

- 1 = Last reset caused by POR circuit

- 0 = Read of SRSR

#### PIN — External Reset Bit

- 1 = Last reset caused by external reset pin ( $\overline{RST}$ )

- 0 = POR or read of SRSR

#### COP — Computer Operating Properly Reset Bit

- 1 = Last reset caused by COP counter

- 0 = POR or read of SRSR

#### ILOP — Illegal Opcode Reset Bit

- 1 = Last reset caused by an illegal opcode

- 0 = POR or read of SRSR

# ILAD — Illegal Address Reset Bit (illegal attempt to fetch an opcode from an unimplemented address)

- 1 = Last reset caused by an opcode fetch from an illegal address

- 0 = POR or read of SRSR

#### MODRST — Monitor Mode Entry Module Reset Bit

- 1 = Last reset caused by monitor mode entry when vector locations \$FFFE and \$FFFF are \$FF after POR while  $\overline{IRQ} \neq V_{TST}$

- 0 = POR or read of SRSR

#### LVI — Low Voltage Inhibit Reset Bit

- 1 = Last reset caused by LVI circuit

- 0 = POR or read of SRSR

# 14.4 Functional Description

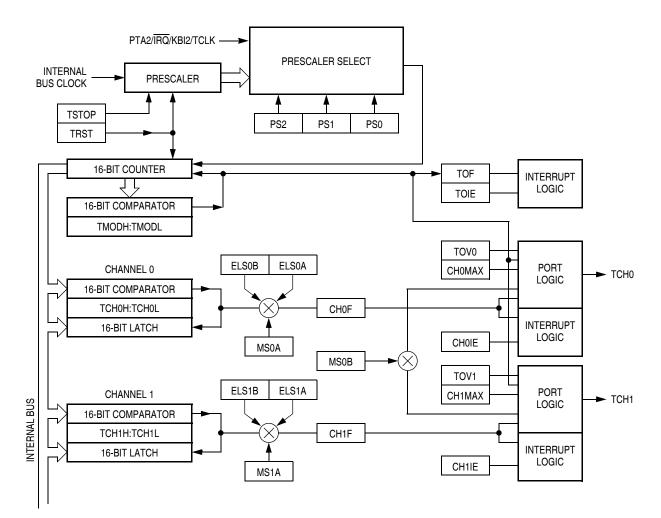

Figure 14-2 shows the structure of the TIM. The central component of the TIM is the 16-bit TIM counter that can operate as a free-running counter or a modulo up-counter. The TIM counter provides the timing reference for the input capture and output compare functions. The TIM counter modulo registers, TMODH:TMODL, control the modulo value of the TIM counter. Software can read the TIM counter value at any time without affecting the counting sequence.

The two TIM channels are programmable independently as input capture or output compare channels.

Figure 14-2. TIM Block Diagram

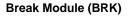

### 15.2.2.3 Break Auxiliary Register

The break auxiliary register (BRKAR) contains a bit that enables software to disable the COP while the MCU is in a state of break interrupt with monitor mode.

Figure 15-6. Break Auxiliary Register (BRKAR)

### BDCOP — Break Disable COP Bit

This read/write bit disables the COP during a break interrupt. Reset clears the BDCOP bit.

- 1 = COP disabled during break interrupt

- 0 = COP enabled during break interrupt

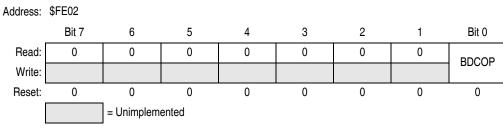

### 15.2.2.4 Break Status Register

The break status register (BSR) contains a flag to indicate that a break caused an exit from wait mode. This register is only used in emulation mode.

Figure 15-7. Break Status Register (BSR)

### SBSW — SIM Break Stop/Wait

SBSW can be read within the break state SWI routine. The user can modify the return address on the stack by subtracting one from it.

1 = Wait mode was exited by break interrupt

0 = Wait mode was not exited by break interrupt

### **15.3.1 Functional Description**

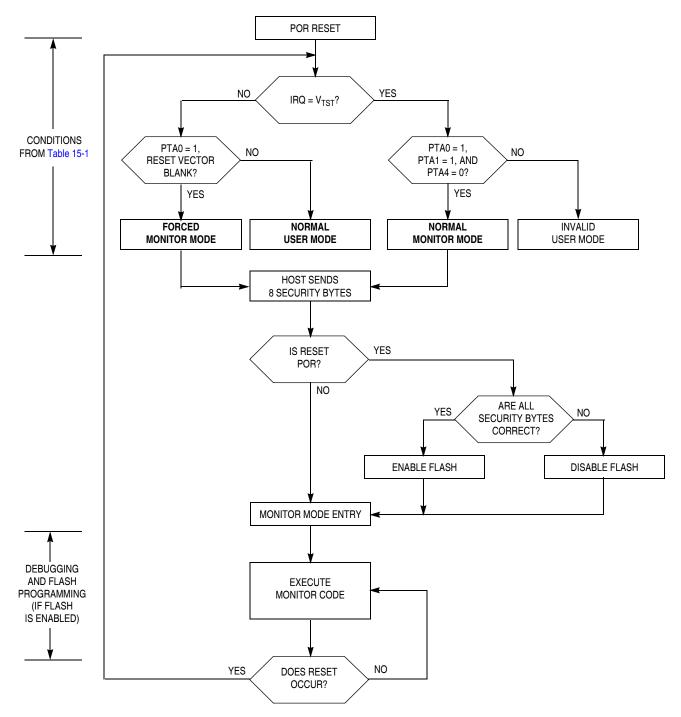

Figure 15-9 shows a simplified diagram of monitor mode entry.

The monitor module receives and executes commands from a host computer. Figure 15-10, Figure 15-11, and Figure 15-12 show example circuits used to enter monitor mode and communicate with a host computer via a standard RS-232 interface.

Figure 15-9. Simplified Monitor Mode Entry Flowchart

**Electrical Specifications**

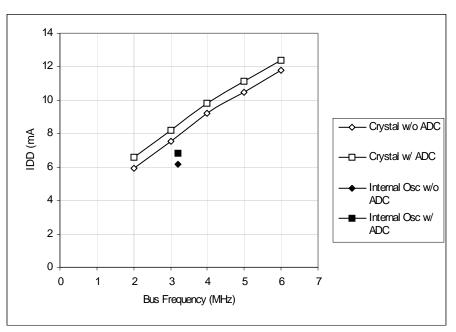

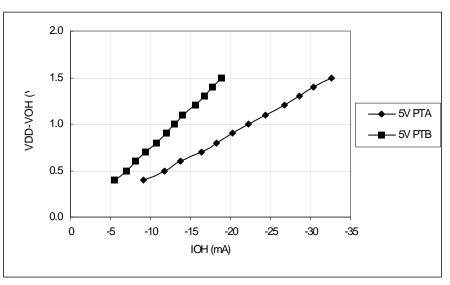

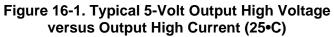

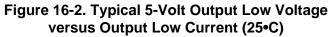

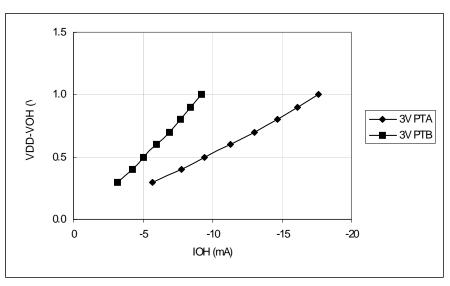

# 16.6 Typical 5-V Output Drive Characteristics

**Electrical Specifications**

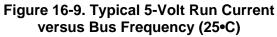

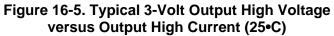

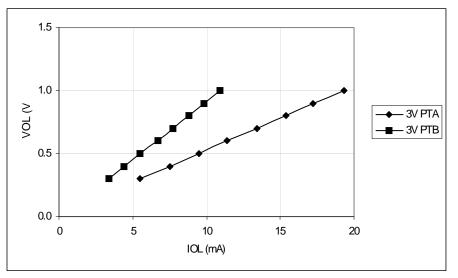

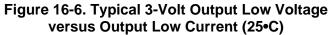

# 16.10 Typical 3.0-V Output Drive Characteristics

**Electrical Specifications**