#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                       |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | HC08                                                         |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 8MHz                                                         |

| Connectivity               | -                                                            |

| Peripherals                | LVD, POR, PWM                                                |

| Number of I/O              | 5                                                            |

| Program Memory Size        | 1.5KB (1.5K x 8)                                             |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | -                                                            |

| RAM Size                   | 128 x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                  |

| Data Converters            | -                                                            |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                            |

| Mounting Type              | Through Hole                                                 |

| Package / Case             | 8-DIP (0.300", 7.62mm)                                       |

| Supplier Device Package    | 8-PDIP                                                       |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc68hc908qt1cpe |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Features of the CPU08 include the following:

- Enhanced HC05 programming model

- Extensive loop control functions

- 16 addressing modes (eight more than the HC05)

- 16-bit index register and stack pointer

- Memory-to-memory data transfers

- Fast 8 × 8 multiply instruction

- Fast 16/8 divide instruction

- Binary-coded decimal (BCD) instructions

- Optimization for controller applications

- Efficient C language support

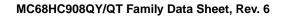

# 1.3 MCU Block Diagram

Figure 1-1 shows the structure of the MC68HC908QY4.

# **1.4 Pin Assignments**

The MC68HC908QT4, MC68HC908QT2, and MC68HC908QT1 are available in 8-pin packages and the MC68HC908QY4, MC68HC908QY2, and MC68HC908QY1 in 16-pin packages. Figure 1-2 shows the pin assignment for these packages.

**General Description**

#### Memory

- 8. Wait for time,  $t_{PROG}$  (minimum 30  $\mu$ s).

- 9. Repeat step 7 and 8 until all desired bytes within the row are programmed.

- 10. Clear the PGM  $bit^{(1)}$ .

- 11. Wait for time,  $t_{NVH}$  (minimum 5  $\mu$ s).

- 12. Clear the HVEN bit.

- 13. After time,  $t_{RCV}$  (typical 1  $\mu$ s), the memory can be accessed in read mode again.

### NOTE

The COP register at location \$FFFF should not be written between steps 5–12, when the HVEN bit is set. Since this register is located at a valid FLASH address, unpredictable behavior may occur if this location is written while HVEN is set.

This program sequence is repeated throughout the memory until all data is programmed.

### NOTE

Programming and erasing of FLASH locations cannot be performed by code being executed from the FLASH memory. While these operations must be performed in the order shown, other unrelated operations may occur between the steps. Do not exceed  $t_{PROG}$  maximum, see 16.16 Memory Characteristics.

# 2.6.5 FLASH Protection

Due to the ability of the on-board charge pump to erase and program the FLASH memory in the target application, provision is made to protect blocks of memory from unintentional erase or program operations due to system malfunction. This protection is done by use of a FLASH block protect register (FLBPR). The FLBPR determines the range of the FLASH memory which is to be protected. The range of the protected area starts from a location defined by FLBPR and ends to the bottom of the FLASH memory (\$FFFF). When the memory is protected, the HVEN bit cannot be set in either ERASE or PROGRAM operations.

### NOTE

In performing a program or erase operation, the FLASH block protect register must be read after setting the PGM or ERASE bit and before asserting the HVEN bit.

When the FLBPR is programmed with all 0 s, the entire memory is protected from being programmed and erased. When all the bits are erased (all 1's), the entire memory is accessible for program and erase.

When bits within the FLBPR are programmed, they lock a block of memory. The address ranges are shown in 2.6.6 FLASH Block Protect Register. Once the FLBPR is programmed with a value other than FF, any erase or program of the FLBPR or the protected block of FLASH memory is prohibited. Mass erase is disabled whenever any block is protected (FLBPR does not equal FF). The FLBPR itself can be erased or programmed only with an external voltage,  $V_{TST}$ , present on the IRQ pin. This voltage also allows entry from reset into the monitor mode.

<sup>2.</sup> The time between each FLASH address change, or the time between the last FLASH address programmed to clearing PGM bit, must not exceed the maximum programming time, t<sub>PROG</sub> maximum.

Configuration Register (CONFIG)

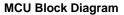

# Chapter 6 Computer Operating Properly (COP)

# 6.1 Introduction

The computer operating properly (COP) module contains a free-running counter that generates a reset if allowed to overflow. The COP module helps software recover from runaway code. Prevent a COP reset by clearing the COP counter periodically. The COP module can be disabled through the COPD bit in the configuration 1 (CONFIG1) register.

# 6.2 Functional Description

Figure 6-1. COP Block Diagram

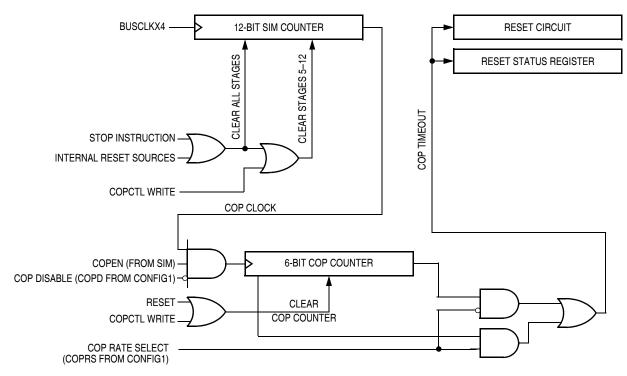

#### **Central Processor Unit (CPU)**

Figure 7-1. CPU Registers

# 7.3.1 Accumulator

The accumulator is a general-purpose 8-bit register. The CPU uses the accumulator to hold operands and the results of arithmetic/logic operations.

Figure 7-2. Accumulator (A)

# 7.3.2 Index Register

The 16-bit index register allows indexed addressing of a 64-Kbyte memory space. H is the upper byte of the index register, and X is the lower byte. H:X is the concatenated 16-bit index register.

In the indexed addressing modes, the CPU uses the contents of the index register to determine the conditional address of the operand.

The index register can serve also as a temporary data storage location.

Figure 7-3. Index Register (H:X)

#### Keyboard Interrupt Module (KBI)

RST, IRQ: Pins have internal (about 30K Ohms) pull upPTA[0:5]: High current sink and source capabilityPTA[0:5]: Pins have programmable keyboard interrupt and pull upPTB[0:7]: Not available on 8-pin devices – MC68HC908QT1, MC68HC908QT2, and MC68HC908QT4 (see note in12.1 Introduction)

ADC: Not available on the MC68HC908QY1 and MC68HC908QT1

# Figure 9-1. Block Diagram Highlighting KBI Block and Pins

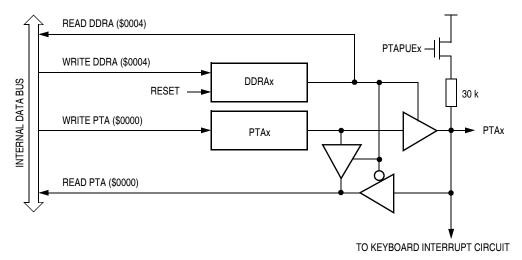

Figure 12-3 shows the port A I/O logic.

Figure 12-3. Port A I/O Circuit

**NOTE** Figure 12-3 does not apply to PTA2

When DDRAx is a 1, reading address \$0000 reads the PTAx data latch. When DDRAx is a 0, reading address \$0000 reads the voltage level on the pin. The data latch can always be written, regardless of the state of its data direction bit.

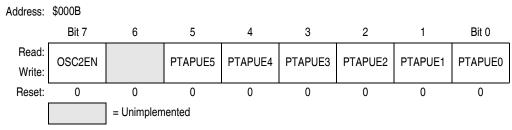

# 12.2.3 Port A Input Pullup Enable Register

The port A input pullup enable register (PTAPUE) contains a software configurable pullup device for each if the six port A pins. Each bit is individually configurable and requires the corresponding data direction register, DDRAx, to be configured as input. Each pullup device is automatically and dynamically disabled when its corresponding DDRAx bit is configured as output.

# **OSC2EN** — Enable PTA4 on OSC2 Pin

This read/write bit configures the OSC2 pin function when internal oscillator or RC oscillator option is selected. This bit has no effect for the XTAL or external oscillator options.

1 = OSC2 pin outputs the internal or RC oscillator clock (BUSCLKX4)

0 = OSC2 pin configured for PTA4 I/O, having all the interrupt and pullup functions

#### System Integration Module (SIM)

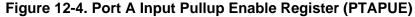

Figure 13-1. SIM Block Diagram

# 13.2 RST and IRQ Pins Initialization

RST and IRQ pins come out of reset as PTA3 and PTA2 respectively. RST and IRQ functions can be activated by programing CONFIG2 accordingly. Refer to Chapter 5 Configuration Register (CONFIG).

# **13.3 SIM Bus Clock Control and Generation**

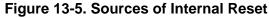

The bus clock generator provides system clock signals for the CPU and peripherals on the MCU. The system clocks are generated from an incoming clock, BUSCLKX2, as shown in Figure 13-2.

| Reset Recovery Type | Actual Number of Cycles |

|---------------------|-------------------------|

| POR/LVI             | 4163 (4096 + 64 + 3)    |

| All others          | 67 (64 + 3)             |

# 13.4.2.1 Power-On Reset

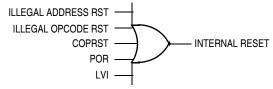

When power is first applied to the MCU, the power-on reset module (POR) generates a pulse to indicate that power on has occurred. The SIM counter counts out 4096 BUSCLKX4 cycles. Sixty-four BUSCLKX4 cycles later, the CPU and memories are released from reset to allow the reset vector sequence to occur.

At power on, the following events occur:

- A POR pulse is generated.

- The internal reset signal is asserted.

- The SIM enables the oscillator to drive BUSCLKX4.

- Internal clocks to the CPU and modules are held inactive for 4096 BUSCLKX4 cycles to allow stabilization of the oscillator.

- The POR bit of the SIM reset status register (SRSR) is set

## See Figure 13-6.

Figure 13-6. POR Recovery

System Integration Module (SIM)

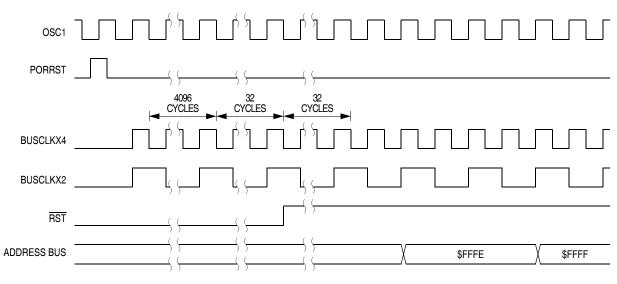

Figure 13-7. Interrupt Processing

# 14.9.3 TIM Counter Modulo Registers

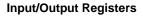

The read/write TIM modulo registers contain the modulo value for the TIM counter. When the TIM counter reaches the modulo value, the overflow flag (TOF) becomes set, and the TIM counter resumes counting from \$0000 at the next timer clock. Writing to the high byte (TMODH) inhibits the TOF bit and overflow interrupts until the low byte (TMODL) is written. Reset sets the TIM counter modulo registers.

Reset the TIM counter before writing to the TIM counter modulo registers.

# 14.9.4 TIM Channel Status and Control Registers

Each of the TIM channel status and control registers does the following:

- Flags input captures and output compares

- Enables input capture and output compare interrupts

- Selects input capture, output compare, or PWM operation

- Selects high, low, or toggling output on output compare

- Selects rising edge, falling edge, or any edge as the active input capture trigger

- Selects output toggling on TIM overflow

- Selects 0% and 100% PWM duty cycle

- Selects buffered or unbuffered output compare/PWM operation

#### Timer Interface Module (TIM)

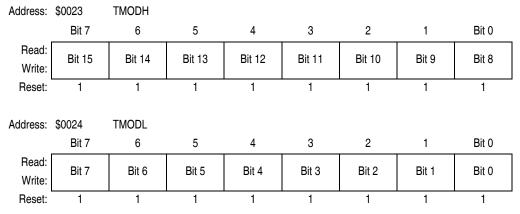

## CHxMAX — Channel x Maximum Duty Cycle Bit

When the TOVx bit is at a 1, setting the CHxMAX bit forces the duty cycle of buffered and unbuffered PWM signals to 100%. As Figure 14-8 shows, the CHxMAX bit takes effect in the cycle after it is set or cleared. The output stays at the 100% duty cycle level until the cycle after CHxMAX is cleared.

Figure 14-8. CHxMAX Latency

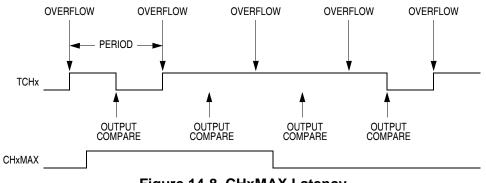

# 14.9.5 TIM Channel Registers

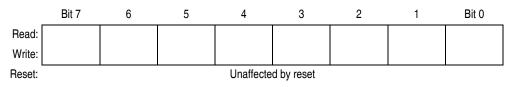

These read/write registers contain the captured TIM counter value of the input capture function or the output compare value of the output compare function. The state of the TIM channel registers after reset is unknown.

In input capture mode (MSxB:MSxA = 0:0), reading the high byte of the TIM channel x registers (TCHxH) inhibits input captures until the low byte (TCHxL) is read.

In output compare mode (MSxB:MSxA  $\neq$  0:0), writing to the high byte of the TIM channel x registers (TCHxH) inhibits output compares until the low byte (TCHxL) is written.

Figure 14-9. TIM Channel Registers (TCH0H/L:TCH1H/L)

Development Support

# 15.2.2.1 Break Status and Control Register

The break status and control register (BRKSCR) contains break module enable and status bits.

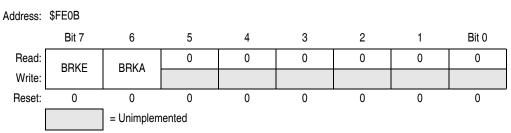

Figure 15-3. Break Status and Control Register (BRKSCR)

# BRKE — Break Enable Bit

This read/write bit enables breaks on break address register matches. Clear BRKE by writing a 0 to bit 7. Reset clears the BRKE bit.

1 = Breaks enabled on 16-bit address match

0 = Breaks disabled

# BRKA — Break Active Bit

This read/write status and control bit is set when a break address match occurs. Writing a 1 to BRKA generates a break interrupt. Clear BRKA by writing a 0 to it before exiting the break routine. Reset clears the BRKA bit.

1 = Break address match

0 = No break address match

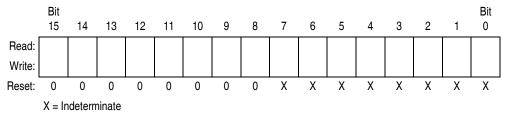

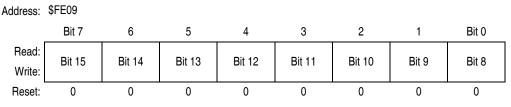

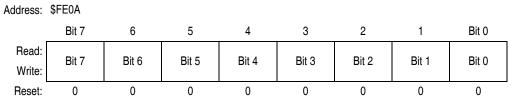

# 15.2.2.2 Break Address Registers

The break address registers (BRKH and BRKL) contain the high and low bytes of the desired breakpoint address. Reset clears the break address registers.

Figure 15-4. Break Address Register High (BRKH)

Figure 15-5. Break Address Register Low (BRKL)

**Development Support**

|         |                      |                     | Func                 | tions               |                    |                   |

|---------|----------------------|---------------------|----------------------|---------------------|--------------------|-------------------|

| Modes   | Reset<br>Vector High | Reset<br>Vector Low | Break<br>Vector High | Break<br>Vector Low | SWI<br>Vector High | SWI<br>Vector Low |

| User    | \$FFFE               | \$FFFF              | \$FFFC               | \$FFFD              | \$FFFC             | \$FFFD            |

| Monitor | \$FEFE               | \$FEFF              | \$FEFC               | \$FEFD              | \$FEFC             | \$FEFD            |

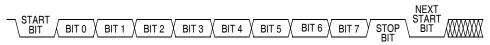

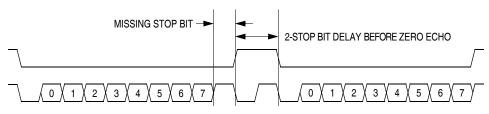

# 15.3.1.4 Data Format

Communication with the monitor ROM is in standard non-return-to-zero (NRZ) mark/space data format. Transmit and receive baud rates must be identical.

Figure 15-13. Monitor Data Format

# 15.3.1.5 Break Signal

A start bit (logic 0) followed by nine logic 0 bits is a break signal. When the monitor receives a break signal, it drives the PTA0 pin high for the duration of two bits and then echoes back the break signal.

Figure 15-14. Break Transaction

# 15.3.1.6 Baud Rate

The monitor communication baud rate is controlled by the frequency of the external or internal oscillator and the state of the appropriate pins as shown in Table 15-1.

Table 15-1 also lists the bus frequencies to achieve standard baud rates. The effective baud rate is the bus frequency divided by 256 when using an external oscillator. When using the internal oscillator in forced monitor mode, the effective baud rate is the bus frequency divided by 335.

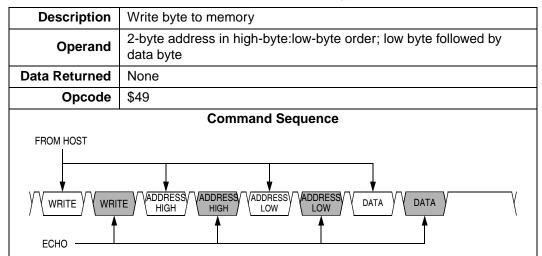

# 15.3.1.7 Commands

The monitor ROM firmware uses these commands:

- READ (read memory)

- WRITE (write memory)

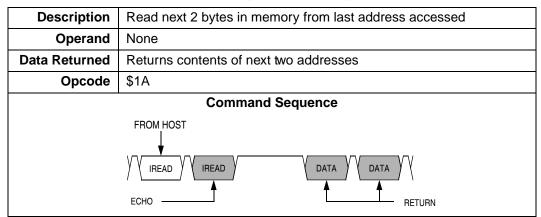

- IREAD (indexed read)

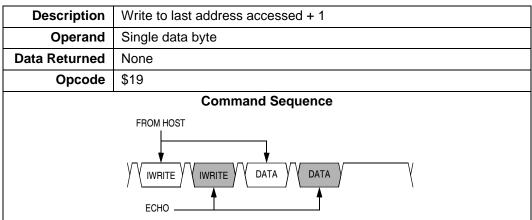

- IWRITE (indexed write)

- READSP (read stack pointer)

- RUN (run user program)

Development Support

Table 15-5. IREAD (Indexed Read) Command

# Table 15-6. IWRITE (Indexed Write) Command

A sequence of IREAD or IWRITE commands can access a block of memory sequentially over the full 64-Kbyte memory map.

**Electrical Specifications**

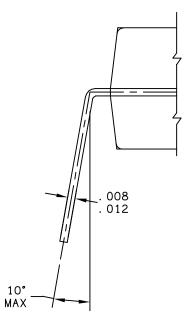

DETAIL "D"

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICAL O | UTLINE     | PRINT VERSION NO | DT TO SCALE |

|---------------------------------------------------------|--------------|------------|------------------|-------------|

| TITLE:                                                  | DO           | CUMENT NO  | ): 98ASB42420B   | REV: N      |

| 8 LD PDIP                                               | CA           | SE NUMBER  | 8: 626–06        | 19 MAY 2005 |

|                                                         | ST           | ANDARD: NO | N-JEDEC          |             |

NOTES:

- 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M 1994.

- 2. ALL DIMENSIONS ARE IN INCHES.

- 3. 626-03 TO 626-06 OBSOLETE. NEW STANDARD 626-07.

- $\triangle$  DIMENSION TO CENTER OF LEAD WHEN FORMED PARALLEL.

- A PACKAGE CONTOUR OPTIONAL (ROUND OR SQUARE CONERS). STYLE 1:

| PIN | 1. | AC | ΙN   |  |

|-----|----|----|------|--|

|     | 2. | DC | + IN |  |

|     | З. | DC | — IN |  |

|     | 4. | AC | ΙN   |  |

- 5. GROUND

- OUTPUT

AUXILIARY

- 8. VCC

| © FREESCALE SEMICONDUCTOR, INC.<br>All RIGHTS RESERVED. | MECHANICA | LOUTLINE     | PRINT VERSION NO | DT TO SCALE |

|---------------------------------------------------------|-----------|--------------|------------------|-------------|

| TITLE:                                                  |           | DOCUMENT NO  | ): 98ASB42420B   | REV: N      |

| 8 LD PDIP                                               |           | CASE NUMBER  | 8: 626–06        | 19 MAY 2005 |

|                                                         |           | STANDARD: NO | N-JEDEC          |             |

|                                                                                                                                                                                                        | MECHANICAL     | DUTLINES                      | DOCUMENT | ND: 98ASH70247A   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------------------------|----------|-------------------|

| Freescale  semiconductor  o FREESCALE SEMICIDUCTOR, INC. ALL RIGHTS RESERVED.                                                                                                                          | DICTI          |                               | PAGE:    | 948F              |

| CITRONIC VERSIONS ARE DOCUMENT CONTROL ADD EXCEPTIONS RESERVED.<br>DIRECTLY FROM THE DOCUMENT CONTROL REPOSITORY, PRINTED<br>INSIONS ARE UNCONTROLLED EXCEPT WHEN STAMPED 'CONTROLLED<br>COPY' IN RED. | DO NOT SCALE   | THIS DRAWING                  | REV:     | В                 |

| NOTES:                                                                                                                                                                                                 |                |                               |          |                   |

| 1. CONTROLLING DIMENSI                                                                                                                                                                                 | ON: MILLIMETE  | R                             |          |                   |

| 2. DIMENSIONS AND TOLE                                                                                                                                                                                 | RANCES PER AN  | NSI Y14.5M-19                 | 82.      |                   |

| 3 DIMENSION DOES NOT<br>BURRS. MOLD FLASH OF                                                                                                                                                           |                | FLASH, PROTR<br>Shall Not Ex  |          |                   |

| DIMENSION DOES NOT                                                                                                                                                                                     |                | RLEAD FLASH O<br>All Not Exce |          | SION.<br>ER SIDE. |

| 5 DIMENSION DOES NOT<br>DAMBAR PROTRUSION SI<br>THE DIMENSION AT MA                                                                                                                                    | HALL BE 0.08   |                               | ESS OF   | BLE               |

| 6. TERMINAL NUMBERS AR                                                                                                                                                                                 | E SHOWN FOR F  | REFERENCE ONL                 | Υ.       |                   |

| $\overline{/7}$ dimensions are to be                                                                                                                                                                   | E DETERMINED , | AT DATUM PLAN                 | VE       |                   |

|                                                                                                                                                                                                        |                |                               |          |                   |

|                                                                                                                                                                                                        |                |                               |          |                   |

| ITLE:                                                                                                                                                                                                  |                | CASE NUMBER: 9                |          |                   |