Welcome to **E-XFL.COM**

# What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                |

| Core Processor             | HC08                                                                    |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 8MHz                                                                    |

| Connectivity               | -                                                                       |

| Peripherals                | LVD, POR, PWM                                                           |

| Number of I/O              | 5                                                                       |

| Program Memory Size        | 1.5KB (1.5K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 128 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                             |

| Data Converters            | -                                                                       |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 8-SOIC (0.209", 5.30mm Width)                                           |

| Supplier Device Package    | 8-SO                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc68hc908qt2cdw |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Revision History**

The following revision history table summarizes changes contained in this document. For your convenience, the page number designators have been linked to the appropriate location.

# **Revision History (Sheet 1 of 3)**

| Date               | Revision<br>Level     | Description                                                                                                                                                            | Page<br>Number(s) |

|--------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| September,<br>2002 | T IN/A TIMINALIPIEASE |                                                                                                                                                                        | N/A               |

|                    |                       | 1.2 Features — Added 8-pin dual flat no lead (DFN) packages to features list.                                                                                          | 19                |

|                    |                       | Figure 1-2. MCU Pin Assignments — Figure updated to include DFN packages.                                                                                              | 21                |

|                    |                       | Figure 2-1. Memory Map — Clarified illegal address and unimplemented memory.                                                                                           | 27                |

|                    |                       | Figure 2-2. Control, Status, and Data Registers — Corrected bit definitions for Port A Data Register (PTA) and Data Direction Register A (DDRA).                       | 27                |

|                    |                       | Table 13-3. Interrupt Sources — Corrected vector addresses for keyboard interrupt and ADC conversion complete interrupt.                                               | 118               |

|                    |                       | Chapter 13 System Integration Module (SIM) — Removed reference to break status register as it is duplicated in break module.                                           | 113               |

|                    |                       | 11.3.1 Internal Oscillator and 11.3.1.1 Internal Oscillator Trimming — Clarified oscillator trim option ordering information and what to expect with untrimmed device. | 92                |

|                    |                       | Figure 11-5. Oscillator Trim Register (OSCTRIM) — Bit 1 designation corrected.                                                                                         | 98                |

| December,          | cember.               | Figure 15-13. Monitor Mode Circuit (Internal Clock, No High Voltage) — Diagram updated for clarity.                                                                    | 150               |

| 2002               | 0.1                   | Figure 12-1. I/O Port Register Summary — Corrected bit definitions for PTA7, DDRA7, and DDRA6.                                                                         | 99                |

|                    |                       | Figure 12-2. Port A Data Register (PTA) — Corrected bit definition for PTA7.                                                                                           | 100               |

|                    |                       | Figure 12-3. Data Direction Register A (DDRA) — Corrected bit definitions for DDRA7 and DDRA6.                                                                         | 101               |

|                    |                       | Figure 12-6. Port B Data Register (PTB) — Corrected bit definition for PTB1                                                                                            | 103               |

|                    |                       | Chapter 9 Keyboard Interrupt Module (KBI) — Section reworked after deletion of auto wakeup for clarity.                                                                | 83                |

|                    |                       | Chapter 4 Auto Wakeup Module (AWU) — New section added for clarity.                                                                                                    | 49                |

|                    |                       | Figure 10-1. LVI Module Block Diagram — Corrected LVI stop representation.                                                                                             | 87                |

|                    |                       | Chapter 16 Electrical Specifications — Extensive changes made to electrical specifications.                                                                            | 169               |

|                    |                       | 17.5 8-Pin Dual Flat No Lead (DFN) Package (Case #1452) — Added case outline drawing for DFN package.                                                                  | 177               |

|                    |                       | Chapter 17 Ordering Information and Mechanical Specifications — Added ordering information for DFN package.                                                            | 185               |

| January,<br>2003   | 0.2                   | 4.2 Features — Corrected third bulleted item.                                                                                                                          | 49                |

**List of Chapters**

#### Memory

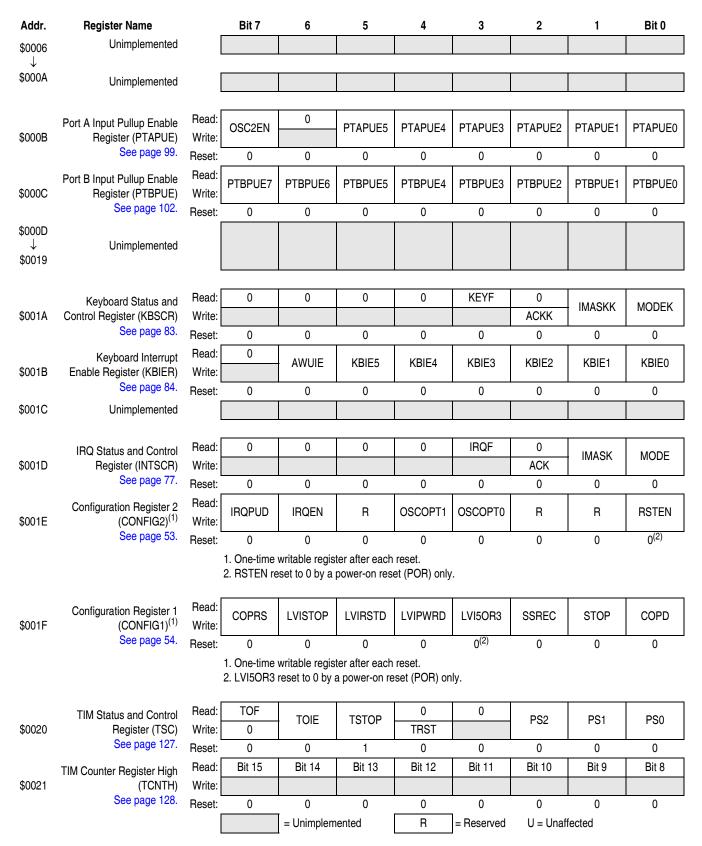

Figure 2-2. Control, Status, and Data Registers (Sheet 2 of 5)

MC68HC908QY/QT Family Data Sheet, Rev. 6

#### Memory

- 8. Wait for time,  $t_{PROG}$  (minimum 30  $\mu$ s).

- 9. Repeat step 7 and 8 until all desired bytes within the row are programmed.

- 10. Clear the PGM bit<sup>(1)</sup>.

- 11. Wait for time,  $t_{NVH}$  (minimum 5  $\mu$ s).

- 12. Clear the HVEN bit.

- 13. After time,  $t_{RCV}$  (typical 1  $\mu$ s), the memory can be accessed in read mode again.

#### NOTE

The COP register at location \$FFFF should not be written between steps 5–12, when the HVEN bit is set. Since this register is located at a valid FLASH address, unpredictable behavior may occur if this location is written while HVEN is set.

This program sequence is repeated throughout the memory until all data is programmed.

#### NOTE

Programming and erasing of FLASH locations cannot be performed by code being executed from the FLASH memory. While these operations must be performed in the order shown, other unrelated operations may occur between the steps. Do not exceed  $t_{PROG}$  maximum, see 16.16 Memory Characteristics.

# 2.6.5 FLASH Protection

Due to the ability of the on-board charge pump to erase and program the FLASH memory in the target application, provision is made to protect blocks of memory from unintentional erase or program operations due to system malfunction. This protection is done by use of a FLASH block protect register (FLBPR). The FLBPR determines the range of the FLASH memory which is to be protected. The range of the protected area starts from a location defined by FLBPR and ends to the bottom of the FLASH memory (\$FFFF). When the memory is protected, the HVEN bit cannot be set in either ERASE or PROGRAM operations.

### NOTE

In performing a program or erase operation, the FLASH block protect register must be read after setting the PGM or ERASE bit and before asserting the HVEN bit.

When the FLBPR is programmed with all 0 s, the entire memory is protected from being programmed and erased. When all the bits are erased (all 1's), the entire memory is accessible for program and erase.

When bits within the FLBPR are programmed, they lock a block of memory. The address ranges are shown in 2.6.6 FLASH Block Protect Register. Once the FLBPR is programmed with a value other than \$FF, any erase or program of the FLBPR or the protected block of FLASH memory is prohibited. Mass erase is disabled whenever any block is protected (FLBPR does not equal \$FF). The FLBPR itself can be erased or programmed only with an external voltage, V<sub>TST</sub>, present on the  $\overline{IRQ}$  pin. This voltage also allows entry from reset into the monitor mode.

MC68HC908QY/QT Family Data Sheet, Rev. 6

<sup>2.</sup> The time between each FLASH address change, or the time between the last FLASH address programmed to clearing PGM bit, must not exceed the maximum programming time, t<sub>PROG</sub> maximum.

# 8.7.1 IRQ Input Pins (IRQ)

The IRQ pin provides a maskable external interrupt source. The IRQ pin contains an internal pullup device.

# 8.8 Registers

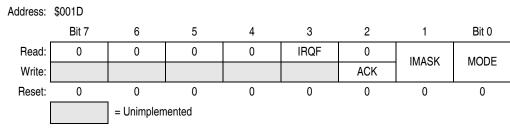

The IRQ status and control register (INTSCR) controls and monitors operation of the IRQ module. See Chapter 5 Configuration Register (CONFIG).

The INTSCR has the following functions:

- Shows the state of the IRQ flag

- Clears the IRQ latch

- Masks the IRQ interrupt request

- Controls triggering sensitivity of the IRQ interrupt pin

Figure 8-3. IRQ Status and Control Register (INTSCR)

# IRQF — IRQ Flag

This read-only status bit is set when the IRQ interrupt is pending.

- $1 = \overline{IRQ}$  interrupt pending

- $0 = \overline{IRQ}$  interrupt not pending

# ACK — IRQ Interrupt Request Acknowledge Bit

Writing a 1 to this write-only bit clears the IRQ latch. ACK always reads as 0.

# IMASK — IRQ Interrupt Mask Bit

Writing a 1 to this read/write bit disables the IRQ interrupt request.

- 1 = IRQ interrupt request disabled

- 0 = IRQ interrupt request enabled

# MODE — IRQ Edge/Level Select Bit

This read/write bit controls the triggering sensitivity of the  $\overline{IRQ}$  pin.

- $1 = \overline{IRQ}$  interrupt request on falling edges and low levels

- $0 = \overline{IRQ}$  interrupt request on falling edges only

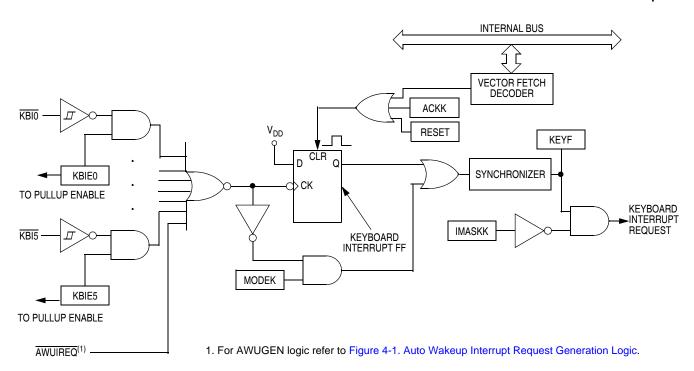

Figure 9-2. Keyboard Interrupt Block Diagram

If the MODEK bit is set, the keyboard interrupt inputs are both falling edge and low-level sensitive, and both of the following actions must occur to clear a keyboard interrupt request:

- Vector fetch or software clear A vector fetch generates an interrupt acknowledge signal to clear the interrupt request. Software may generate the interrupt acknowledge signal by writing a 1 to the ACKK bit in the keyboard status and control register (KBSCR). The ACKK bit is useful in applications that poll the keyboard interrupt inputs and require software to clear the keyboard interrupt request. Writing to the ACKK bit prior to leaving an interrupt service routine can also prevent spurious interrupts due to noise. Setting ACKK does not affect subsequent transitions on the keyboard interrupt inputs. A falling edge that occurs after writing to the ACKK bit latches another interrupt request. If the keyboard interrupt mask bit, IMASKK, is clear, the central processor unit (CPU) loads the program counter with the vector address at locations \$FFE0 and \$FFE1.

- Return of all enabled keyboard interrupt inputs to logic 1 As long as any enabled keyboard interrupt pin is at logic 0, the keyboard interrupt remains set. The auto wakeup interrupt input, AWUIREQ, will be cleared only by writing to ACKK bit in KBSCR or reset.

The vector fetch or software clear and the return of all enabled keyboard interrupt pins to logic 1 may occur in any order.

If the MODEK bit is clear, the keyboard interrupt pin is falling-edge sensitive only. With MODEK clear, a vector fetch or software clear immediately clears the keyboard interrupt request.

Reset clears the keyboard interrupt request and the MODEK bit, clearing the interrupt request even if a keyboard interrupt input stays at logic 0.

The keyboard flag bit (KEYF) in the keyboard status and control register can be used to see if a pending interrupt exists. The KEYF bit is not affected by the keyboard interrupt mask bit (IMASKK) which makes it useful in applications where polling is preferred.

# 11.3.1.1 Internal Oscillator Trimming

The 8-bit trimming register, OSCTRIM, allows a clock period adjust of +127 and -128 steps. Increasing OSCTRIM value increases the clock period. Trimming allows the internal clock frequency to be set to  $12.8 \text{ MHz} \pm 5\%$ .

All devices are factory programmed with trim values in reserved FLASH memory locations \$FFC0 and \$FFC1. The trim value is not automatically loaded into the OSCTRIM register. User software must copy the trim value from \$FFC0 or \$FFC1 into OSCTRIM if needed. The factory trim value provides the accuracy required for communication using forced monitor mode. Some production programmers erase the factory trim values, so confirm with your programmer vendor that the trim values at \$FFC0 and \$FFC1 are preserved, or are re-trimmed. Trimming the device in the user application board will provide the most accurate trim value.

# 11.3.1.2 Internal to External Clock Switching

When external clock source (external OSC, RC, or XTAL) is desired, the user must perform the following steps:

- 1. For external crystal circuits only, OSCOPT[1:0] = 1:1: To help precharge an external crystal oscillator, set PTA4 (OSC2) as an output and drive high for several cycles. This may help the crystal circuit start more robustly.

- 2. Set CONFIG2 bits OSCOPT[1:0] according to . The oscillator module control logic will then set OSC1 as an external clock input and, if the external crystal option is selected, OSC2 will also be set as the clock output.

- Create a software delay to wait the stabilization time needed for the selected clock source (crystal, resonator, RC) as recommended by the component manufacturer. A good rule of thumb for crystal oscillators is to wait 4096 cycles of the crystal frequency, i.e., for a 4-MHz crystal, wait approximately 1 msec.

- 4. After the manufacturer's recommended delay has elapsed, the ECGON bit in the OSC status register (OSCSTAT) needs to be set by the user software.

- 5. After ECGON set is detected, the OSC module checks for oscillator activity by waiting two external clock rising edges.

- 6. The OSC module then switches to the external clock. Logic provides a glitch free transition.

- 7. The OSC module first sets the ECGST bit in the OSCSTAT register and then stops the internal oscillator.

#### NOTE

Once transition to the external clock is done, the internal oscillator will only be reactivated with reset. No post-switch clock monitor feature is implemented (clock does not switch back to internal if external clock dies).

# 11.3.2 External Oscillator

The external clock option is designed for use when a clock signal is available in the application to provide a clock source to the microcontroller. The OSC1 pin is enabled as an input by the oscillator module. The clock signal is used directly to create BUSCLKX4 and also divided by two to create BUSCLKX2.

In this configuration, the OSC2 pin cannot output BUSCLKX4.So the OSC2EN bit in the port A pullup enable register will be clear to enable PTA4 I/O functions on the pin

**Oscillator Module (OSC)**

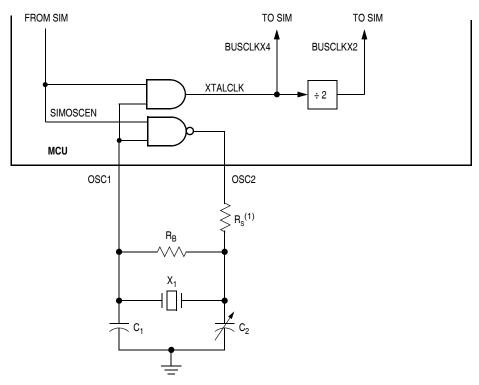

# 11.3.3 XTAL Oscillator

The XTAL oscillator circuit is designed for use with an external crystal or ceramic resonator to provide an accurate clock source. In this configuration, the OSC2 pin is dedicated to the external crystal circuit. The OSC2EN bit in the port A pullup enable register has no effect when this clock mode is selected.

In its typical configuration, the XTAL oscillator is connected in a Pierce oscillator configuration, as shown in Figure 11-2. This figure shows only the logical representation of the internal components and may not represent actual circuitry. The oscillator configuration uses five components:

- Crystal, X<sub>1</sub>

- Fixed capacitor, C<sub>1</sub>

- Tuning capacitor, C<sub>2</sub> (can also be a fixed capacitor)

- Feedback resistor, R<sub>B</sub>

- Series resistor, R<sub>s</sub> (optional)

#### NOTE

The series resistor ( $R_{\rm S}$ ) is included in the diagram to follow strict Pierce oscillator guidelines and may not be required for all ranges of operation, especially with high frequency crystals. Refer to the crystal manufacturer's data for more information.

Note 1.

R<sub>S</sub> can be zero (shorted) when used with higher-frequency crystals. Refer to manufacturer's data. See Chapter 16 Electrical Specifications for component value recommendations.

Figure 11-2. XTAL Oscillator External Connections

# 13.6.2.1 Interrupt Status Register 1

Address: \$FE04 Bit 7 5 2 Bit 0 Read: 0 IF5 IF4 IF3 0 IF1 0 0 R R R R R R Write: R R 0 0 0 0 0 Reset: 0 0 0 R = Reserved

Figure 13-11. Interrupt Status Register 1 (INT1)

# IF1 and IF3-IF5 — Interrupt Flags

These flags indicate the presence of interrupt requests from the sources shown in Table 13-3.

- 1 = Interrupt request present

- 0 = No interrupt request present

# Bit 0, 1, 3, and 7 — Always read 0

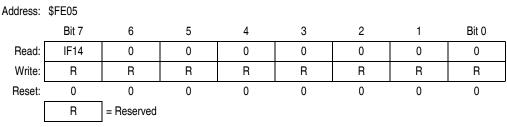

# 13.6.2.2 Interrupt Status Register 2

Figure 13-12. Interrupt Status Register 2 (INT2)

# IF14 — Interrupt Flags

This flag indicates the presence of interrupt requests from the sources shown in Table 13-3.

- 1 = Interrupt request present

- 0 = No interrupt request present

# Bit 0-6 — Always read 0

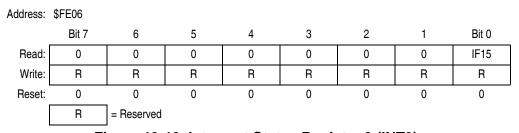

# 13.6.2.3 Interrupt Status Register 3

Figure 13-13. Interrupt Status Register 3 (INT3)

# IF15 — Interrupt Flags

These flags indicate the presence of interrupt requests from the sources shown in Table 13-3.

- 1 = Interrupt request present

- 0 = No interrupt request present

# Bit 1–7 — Always read 0

MC68HC908QY/QT Family Data Sheet, Rev. 6

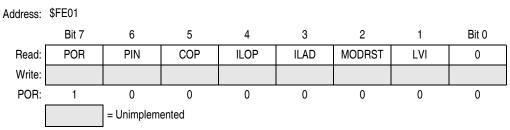

# 13.8.1 SIM Reset Status Register

The SRSR register contains flags that show the source of the last reset. The status register will automatically clear after reading SRSR. A power-on reset sets the POR bit and clears all other bits in the register. All other reset sources set the individual flag bits but do not clear the register. More than one reset source can be flagged at any time depending on the conditions at the time of the internal or external reset. For example, the POR and LVI bit can both be set if the power supply has a slow rise time.

Figure 13-19. SIM Reset Status Register (SRSR)

#### POR — Power-On Reset Bit

- 1 = Last reset caused by POR circuit

- 0 = Read of SRSR

#### PIN — External Reset Bit

- 1 = Last reset caused by external reset pin ( $\overline{RST}$ )

- 0 = POR or read of SRSR

# **COP** — Computer Operating Properly Reset Bit

- 1 = Last reset caused by COP counter

- 0 = POR or read of SRSR

# ILOP — Illegal Opcode Reset Bit

- 1 = Last reset caused by an illegal opcode

- 0 = POR or read of SRSR

# ILAD — Illegal Address Reset Bit (illegal attempt to fetch an opcode from an unimplemented address)

- 1 = Last reset caused by an opcode fetch from an illegal address

- 0 = POR or read of SRSR

# **MODRST** — Monitor Mode Entry Module Reset Bit

- 1 = Last reset caused by monitor mode entry when vector locations \$FFFE and \$FFFF are \$FF after POR while  $\overline{IRQ} \neq V_{TST}$

- 0 = POR or read of SRSR

# LVI — Low Voltage Inhibit Reset Bit

- 1 = Last reset caused by LVI circuit

- 0 = POR or read of SRSR

control the output are the ones written to last. TSC0 controls and monitors the buffered output compare function, and TIM channel 1 status and control register (TSC1) is unused. While the MS0B bit is set, the channel 1 pin, TCH1, is available as a general-purpose I/O pin.

#### NOTE

In buffered output compare operation, do not write new output compare values to the currently active channel registers. User software should track the currently active channel to prevent writing a new value to the active channel. Writing to the active channel registers is the same as generating unbuffered output compares.

# 14.4.4 Pulse Width Modulation (PWM)

By using the toggle-on-overflow feature with an output compare channel, the TIM can generate a PWM signal. The value in the TIM counter modulo registers determines the period of the PWM signal. The channel pin toggles when the counter reaches the value in the TIM counter modulo registers. The time between overflows is the period of the PWM signal

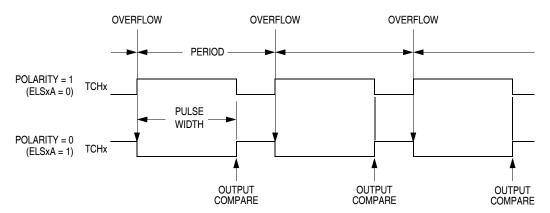

As Figure 14-3 shows, the output compare value in the TIM channel registers determines the pulse width of the PWM signal. The time between overflow and output compare is the pulse width. Program the TIM to clear the channel pin on output compare if the state of the PWM pulse is logic 1 (ELSxA = 0). Program the TIM to set the pin if the state of the PWM pulse is logic 0 (ELSxA = 1).

The value in the TIM counter modulo registers and the selected prescaler output determines the frequency of the PWM output The frequency of an 8-bit PWM signal is variable in 256 increments. Writing \$00FF (255) to the TIM counter modulo registers produces a PWM period of 256 times the internal bus clock period if the prescaler select value is 000. See 14.9.1 TIM Status and Control Register.

The value in the TIM channel registers determines the pulse width of the PWM output. The pulse width of an 8-bit PWM signal is variable in 256 increments. Writing \$0080 (128) to the TIM channel registers produces a duty cycle of 128/256 or 50%.

Figure 14-3. PWM Period and Pulse Width

**Timer Interface Module (TIM)**

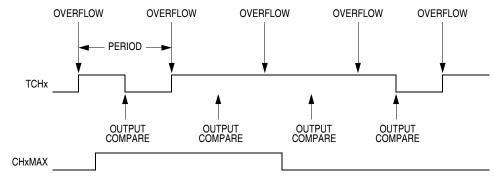

# CHxMAX — Channel x Maximum Duty Cycle Bit

When the TOVx bit is at a 1, setting the CHxMAX bit forces the duty cycle of buffered and unbuffered PWM signals to 100%. As Figure 14-8 shows, the CHxMAX bit takes effect in the cycle after it is set or cleared. The output stays at the 100% duty cycle level until the cycle after CHxMAX is cleared.

Figure 14-8. CHxMAX Latency

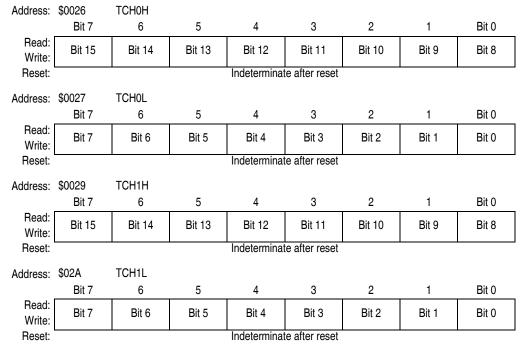

# 14.9.5 TIM Channel Registers

These read/write registers contain the captured TIM counter value of the input capture function or the output compare value of the output compare function. The state of the TIM channel registers after reset is unknown.

In input capture mode (MSxB:MSxA = 0:0), reading the high byte of the TIM channel x registers (TCHxH) inhibits input captures until the low byte (TCHxL) is read.

In output compare mode (MSxB:MSxA  $\neq$  0:0), writing to the high byte of the TIM channel x registers (TCHxH) inhibits output compares until the low byte (TCHxL) is written.

Figure 14-9. TIM Channel Registers (TCH0H/L:TCH1H/L)

MC68HC908QY/QT Family Data Sheet, Rev. 6

#### **Development Support**

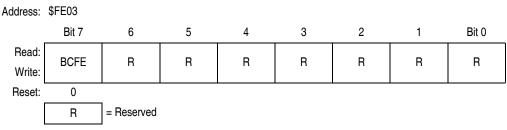

# 15.2.2.5 Break Flag Control Register

The break control register (BFCR) contains a bit that enables software to clear status bits while the MCU is in a break state.

Figure 15-8. Break Flag Control Register (BFCR)

# **BCFE** — Break Clear Flag Enable Bit

This read/write bit enables software to clear status bits by accessing status registers while the MCU is in a break state. To clear status bits during the break state, the BCFE bit must be set.

- 1 = Status bits clearable during break

- 0 = Status bits not clearable during break

#### 15.2.3 Low-Power Modes

The WAIT and STOP instructions put the MCU in low power- consumption standby modes. If enabled, the break module will remain enabled in wait and stop modes. However, since the internal address bus does not increment in these modes, a break interrupt will never be triggered.

# 15.3 Monitor Module (MON)

This subsection describes the monitor module (MON) and the monitor mode entry methods. The monitor allows debugging and programming of the microcontroller unit (MCU) through a single-wire interface with a host computer. Monitor mode entry can be achieved without use of the higher test voltage, V<sub>TST</sub>, as long as vector addresses \$FFFE and \$FFFF are blank, thus reducing the hardware requirements for in-circuit programming.

# Features include:

- Normal user-mode pin functionality on most pins

- One pin dedicated to serial communication between MCU and host computer

- Standard non-return-to-zero (NRZ) communication with host computer

- · Execution of code in random-access memory (RAM) or FLASH

- FLASH memory security feature<sup>(1)</sup>

- FLASH memory programming interface

- Use of external 9.8304 MHz oscillator to generate internal frequency of 2.4576 MHz

- Simple internal oscillator mode of operation (no external clock or high voltage)

- Monitor mode entry without high voltage, V<sub>TST</sub>, if reset vector is blank (\$FFFE and \$FFFF contain \$FF)

- Standard monitor mode entry if high voltage is applied to IRQ

MC68HC908QY/QT Family Data Sheet, Rev. 6

<sup>1.</sup> No security feature is absolutely secure. However, Freescale's strategy is to make reading or copying the FLASH difficult for unauthorized users.

# **Development Support**

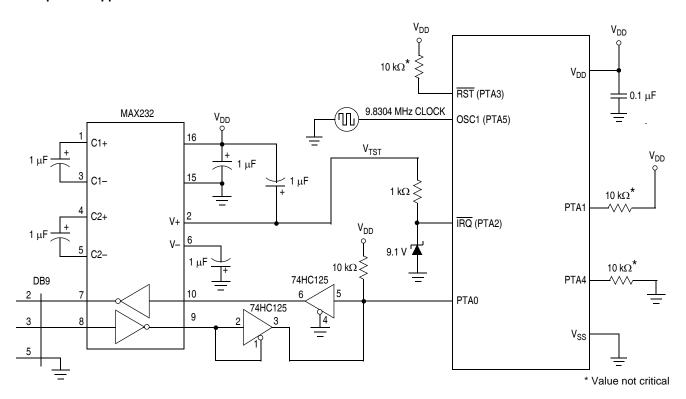

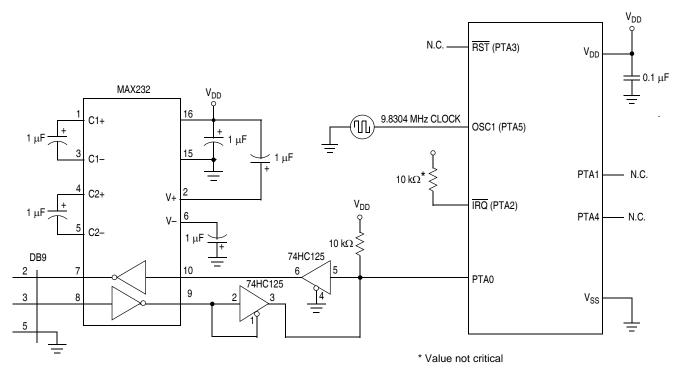

Figure 15-10. Monitor Mode Circuit (External Clock, with High Voltage)

Figure 15-11. Monitor Mode Circuit (External Clock, No High Voltage)

MC68HC908QY/QT Family Data Sheet, Rev. 6

If monitor mode was entered with  $V_{TST}$  on  $\overline{IRQ}$ , then the COP is disabled as long as  $V_{TST}$  is applied to  $\overline{IRQ}$

#### 15.3.1.2 Forced Monitor Mode

If entering monitor mode without high voltage on  $\overline{IRQ}$ , then startup port pin requirements and conditions, (PTA1/PTA4) are not in effect. This is to reduce circuit requirements when performing in-circuit programming.

#### NOTE

If the reset vector is blank and monitor mode is entered, the chip will see an additional reset cycle after the initial power-on reset (POR). Once the reset vector has been programmed, the traditional method of applying a voltage,  $V_{TST}$ , to  $\overline{IRQ}$  must be used to enter monitor mode.

If monitor mode was entered as a result of the reset vector being blank, the COP is always disabled regardless of the state of IRQ.

If the voltage applied to the  $\overline{IRQ}$  is less than  $V_{TST}$ , the MCU will come out of reset in user mode. Internal circuitry monitors the reset vector fetches and will assert an internal reset if it detects that the reset vectors are erased (\$FF). When the MCU comes out of reset, it is forced into monitor mode without requiring high voltage on the  $\overline{IRQ}$  pin. Once out of reset, the monitor code is initially executing with the internal clock at its default frequency.

If  $\overline{IRQ}$  is held high, all pins will default to regular input port functions except for PTA0 and PTA5 which will operate as a serial communication port and OSC1 input respectively (refer to Figure 15-10). That will allow the clock to be driven from an external source through OSC1 pin.

If  $\overline{\text{IRQ}}$  is held low, all pins will default to regular input port function except for PTA0 which will operate as serial communication port. Refer to Figure 15-11.

Regardless of the state of the  $\overline{IRQ}$  pin, it will not function as a port input pin in monitor mode. Bit 2 of the Port A data register will always read 0. The BIH and BIL instructions will behave as if the  $\overline{IRQ}$  pin is enabled, regardless of the settings in the configuration register. See Chapter 5 Configuration Register (CONFIG).

The COP module is disabled in forced monitor mode. Any reset other than a power-on reset (POR) will automatically force the MCU to come back to the forced monitor mode.

#### 15.3.1.3 Monitor Vectors

In monitor mode, the MCU uses different vectors for reset, SWI (software interrupt), and break interrupt than those for user mode. The alternate vectors are in the \$FE page instead of the \$FF page and allow code execution from the internal monitor firmware instead of user code.

#### NOTE

Exiting monitor mode after it has been initiated by having a blank reset vector requires a power-on reset (POR). Pulling RST (when RST pin available) low will not exit monitor mode in this situation.

Table 15-2 summarizes the differences between user mode and monitor mode regarding vectors.

# **Electrical Specifications**

# 16.8 5-V Oscillator Characteristics

| Characteristic                                                                                                                                                                            | Symbol             | Min             | Тур                | Max           | Unit |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------|--------------------|---------------|------|

| Internal oscillator frequency <sup>(1)</sup>                                                                                                                                              | fINTCLK            | _               | 12.8               | _             | MHz  |

| Deviation from trimmed Internal oscillator <sup>(2)(3)</sup> 12.8 MHz, fixed voltage, fixed temp 12.8 MHz, V <sub>DD</sub> ± 10%, 0 to 70°C 12.8 MHz, V <sub>DD</sub> ± 10%, –40 to 125°C | ACC <sub>INT</sub> | _<br>_<br>_     | ± 0.4<br>± 2<br>—  | —<br>—<br>± 5 | %    |

| Crystal frequency, XTALCLK <sup>(1)</sup>                                                                                                                                                 | foscxclk           | 1               | _                  | 24            | MHz  |

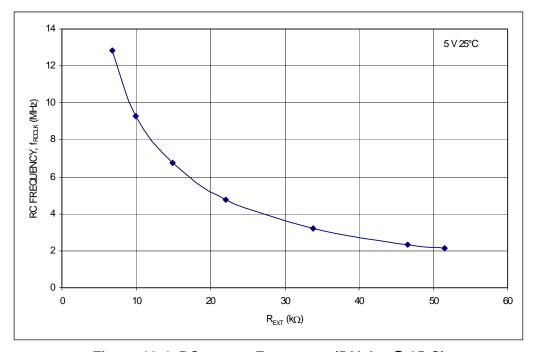

| External RC oscillator frequency, RCCLK <sup>(1)</sup>                                                                                                                                    | f <sub>RCCLK</sub> | 2               | _                  | 12            | MHz  |

| External clock reference frequency <sup>(1)</sup> (4)                                                                                                                                     | foscxclk           | dc              | _                  | 32            | MHz  |

| Crystal load capacitance <sup>(5)</sup>                                                                                                                                                   | CL                 | _               | 20                 | _             | pF   |

| Crystal fixed capacitance <sup>(3)</sup>                                                                                                                                                  | C <sub>1</sub>     | _               | 2 x C <sub>L</sub> | _             | _    |

| Crystal tuning capacitance <sup>(3)</sup>                                                                                                                                                 | C <sub>2</sub>     | _               | 2 x C <sub>L</sub> | _             | _    |

| Feedback bias resistor                                                                                                                                                                    | R <sub>B</sub>     | 0.5             | 1                  | 10            | MΩ   |

| RC oscillator external resistor                                                                                                                                                           | R <sub>EXT</sub>   | See Figure 16-4 |                    |               | _    |

| Crystal series damping resistor $f_{OSCXCLK} = 1 \text{ MHz}$ $f_{OSCXCLK} = 4 \text{ MHz}$ $f_{OSCXCLK} = 8 \text{ MHz}$                                                                 | R <sub>S</sub>     | _<br>_<br>_     | 20<br>10<br>0      | _<br>_<br>_   | kΩ   |

- Bus frequency, f<sub>OP</sub>, is oscillator frequency divided by 4.

Deviation values assumes trimming @25•C and midpoint of voltage range.

Values are based on characterization results, not tested in production.

No more than 10% duty cycle deviation from 50%.

- 5. Consult crystal vendor data sheet.

Figure 16-4. RC versus Frequency (5 Volts @ 25•C)

MC68HC908QY/QT Family Data Sheet, Rev. 6

© FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED.

ELECTRONIC VERSIONS ARE UNCONTROLLED EXCEPT WHEN ACCESSED

DIRECTLY FROM THE DOCUMENT CONTROL REPOSITORY. PRINTED VERSIONS

ARE UNCONTROLLED EXCEPT WHEN STAMPED "CONTROLLED COPY" IN RED.

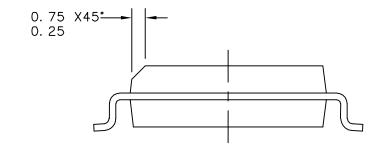

# MECHANICAL OUTLINES DICTIONARY

DO NOT SCALE THIS DRAWING

DOCUMENT NO: 98ARL10557D

PAGE: 1452

REV: A

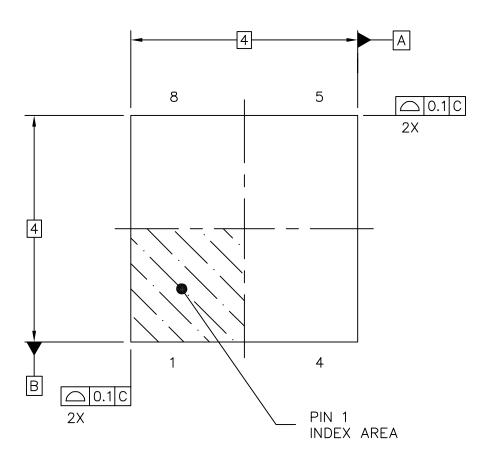

TITLE: THERMALLY ENHANCED DUAL FLAT NO LEAD PACKAGE (DFN) 8 TERMINAL, 0.8 PITCH (4 X 4 X 1)

CASE NUMBER: 1452-01

STANDARD: NON-JEDEC

PACKAGE CODE: 6165 | SHEET: 1 OF 5

© FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED.

ELECTRONIC VERSIONS ARE UNCONTROLLED EXCEPT WHEN ACCESSED

DIRECTLY FROM THE DOCUMENT CONTROL REPOSITORY, PRINTED

VERSIONS ARE UNCONTROLLED EXCEPT WHEN STAMPED "CONTROLLED

COPY" IN RED.

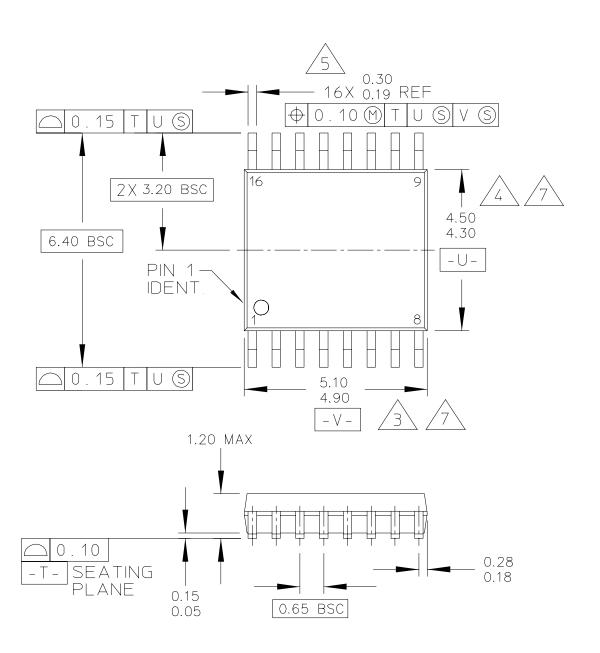

# MECHANICAL OUTLINES DICTIONARY

DO NOT SCALE THIS DRAWING

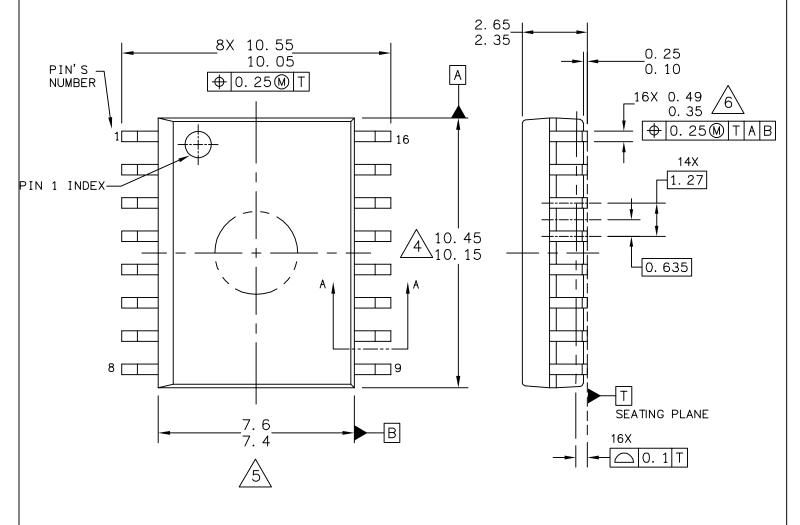

DOCUMENT NO: 98ASB42567B

PAGE: 751G

REV: E

SECTION A-A

TITLE:

16LD SOIC W/B, 1.27 PITCH CASE-OUTLINE

CASE NUMBER: 751G-05

STANDARD: JEDEC MS-013AA

PACKAGE CODE: 2003 | SHEET: 1 OF 3

# MECHANICAL OUTLINES DICTIONARY

DO NOT SCALE THIS DRAWING

DOCUMENT NO: 98ASB42567B 751G

PAGE:

REV: Ε

NOTES:

DIMENSIONS ARE IN MILLIMETERS.

DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

DATUMS A AND B TO BE DETERMINED AT THE PLANE WHERE THE BOTTOM OF THE LEADS EXIT THE PLASTIC BODY.

THIS DIMENSION DOES NOT INCLUDE MOLD FLASH, PROTRUSION OR GATE BURRS. MOLD FLASH, PROTRUSION OR GATE BURRS SHALL NOT EXCEED 0.15 MM PER SIDE. THIS DIMENSION IS DETERMINED AT THE PLANE WHERE THE BOTTOM OF THE LEADS EXIT THE PLASTIC BODY.

THIS DIMENSION DOES NOT INCLUDE INTER-LEAD FLASH OR PROTRUSIONS. INTER-LEAD FLASH AND PROTRUSIONS SHALL NOT EXCEED 0.25 MM PER SIDE. THIS DIMENSION IS DETERMINED AT THE PLANE WHERE THE BOTTOM OF THE LEADS EXIT THE PLASTIC BODY.

/6\ THIS DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL NOT CAUSE THE LEAD WIDTH TO EXCEED 0.62 mm.

TITLE:

16LD SOIC W/B, 1.27 PITCH, CASE OUTLINE

CASE NUMBER: 751G-05

STANDARD: JEDEC MS-013AA

PACKAGE CODE: 2003 SHEET: 2 OF 3

FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED.

ELECTRONIC VERSIONS ARE UNCONTROLLED EXCEPT WHEN ACCESSED DIRECTLY FROM THE DOCUMENT CONTROL REPOSITORY. PRINTED VERSIONS ARE UNCONTROLLED EXCEPT WHEN STAMPED 'CONTROLLED COPY' IN RED.

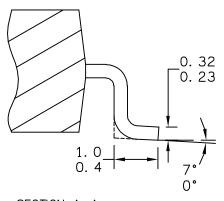

# MECHANICAL DUTLINES DICTIONARY

DO NOT SCALE THIS DRAWING

| DOCUMENT | N□: | 98ASH70247A |

|----------|-----|-------------|

| PAGE:    |     | 948F        |

В

REV:

| TITLE:                    | CASE NUMBER: 948F-01             |  |  |  |  |

|---------------------------|----------------------------------|--|--|--|--|

| 16 LD TSSOP, PITCH 0.65MM | STANDARD: JEDEC                  |  |  |  |  |

|                           | PACKAGE CODE: 6117 SHEET: 1 OF 4 |  |  |  |  |