Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                              |

|----------------------------|--------------------------------------------------------------|

| Product Status             | Obsolete                                                     |

| Core Processor             | HC08                                                         |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 8MHz                                                         |

| Connectivity               | -                                                            |

| Peripherals                | LVD, POR, PWM                                                |

| Number of I/O              | 5                                                            |

| Program Memory Size        | 1.5KB (1.5K x 8)                                             |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | -                                                            |

| RAM Size                   | 128 x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                  |

| Data Converters            | A/D 4x8b                                                     |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                           |

| Mounting Type              | Through Hole                                                 |

| Package / Case             | 8-DIP (0.300", 7.62mm)                                       |

| Supplier Device Package    | 8-PDIP                                                       |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc68hc908qt2mpe |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

MC68HC908QY4 MC68HC908QY2 MC68HC908QY2 MC68HC908QY1 MC68HC908QY1 MC68HC908QT1

**Data Sheet**

To provide the most up-to-date information, the revision of our documents on the World Wide Web will be the most current. Your printed copy may be an earlier revision. To verify you have the latest information available, refer to:

http://freescale.com/

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. This product incorporates SuperFlash® technology licensed from SST.

© Freescale Semiconductor, Inc., 2005–2010. All rights reserved.

MC68HC908QY/QT Family Data Sheet, Rev. 6

6

# **Revision History**

# **Revision History (Sheet 3 of 3)**

| Date              | Revision<br>Level                                          | Description                                                                                                                               |            |  |  |

|-------------------|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|------------|--|--|

| November,<br>2004 | 4.0                                                        | Reformatted to meet current documentation standards                                                                                       | Throughout |  |  |

|                   |                                                            | 6.3.1 BUSCLKX4 — Clarified description of BUSCLKX4                                                                                        | 58         |  |  |

|                   |                                                            | Chapter 7 Central Processor Unit (CPU) — In 7.7 Instruction Set Summary: Reworked definitions for STOP instruction Added WAIT instruction | 70<br>71   |  |  |

|                   |                                                            | 13.8.1 SIM Reset Status Register — Clarified SRSR flag setting                                                                            | 117        |  |  |

|                   |                                                            | 14.9.1 TIM Status and Control Register — Added information to TSTOP note                                                                  | 127        |  |  |

|                   |                                                            | 16.8 5-V Oscillator Characteristics — Added values for deviation from trimmed inernal oscillator                                          | 155        |  |  |

|                   |                                                            | 16.12 3-V Oscillator Characteristics — Added values for deviation from trimmed inernal oscillator                                         | 158        |  |  |

| July,<br>2005     | 5.0                                                        | Figure 5-2. Configuration Register 1 (CONFIG1) — Clarified bit definitions for COPRS.                                                     | 54         |  |  |

|                   |                                                            | Chapter 8 External Interrupt (IRQ) — Reworked for clarification.                                                                          | 73         |  |  |

|                   |                                                            | 11.3.4 RC Oscillator — Improved RC oscillator wording.                                                                                    | 93         |  |  |

|                   |                                                            | 12.1 Introduction — Added note pertaining to non-bonded port pins.                                                                        | 97         |  |  |

|                   |                                                            | 17.3 Package Dimensions — Updated package information.                                                                                    | 165        |  |  |

| March,<br>2010    | 6 () Clarity internal oscillator frim register information |                                                                                                                                           |            |  |  |

# Chapter 7 Central Processor Unit (CPU)

| 7.1          | Introduction                            | 61 |

|--------------|-----------------------------------------|----|

| 7.2          | Features                                | 61 |

| 7.3          | CPU Registers                           | 61 |

| 7.3.1        | Accumulator                             |    |

| 7.3.2        | Index Register                          |    |

| 7.3.3        | Stack Pointer                           |    |

| 7.3.4        | Program Counter                         |    |

| 7.3.5        | Condition Code Register                 |    |

| 7.4          | Arithmetic/Logic Unit (ALU)             |    |

| 7.5          | Low-Power Modes                         |    |

| 7.5.1        | Wait Mode                               |    |

| 7.5.2        | Stop Mode                               |    |

| 7.6          | CPU During Break Interrupts             |    |

| 7.7          | Instruction Set Summary                 | 66 |

| 7.8          | Opcode Map                              | 71 |

|              | Chapter 8                               |    |

|              | External Interrupt (IRQ)                |    |

| 8.1          | Introduction                            | 72 |

|              |                                         |    |

| 8.2          | Features                                |    |

| 8.3<br>8.3.1 | Functional Description                  |    |

| 8.3.2        | MODE = 1                                |    |

| 8.4          | Interrupts                              |    |

| 8.5          | Low-Power Modes                         |    |

| 8.5.1        | Wait Mode                               |    |

| 8.5.2        | Stop Mode                               |    |

| 8.6          | IRQ Module During Break Interrupts      |    |

| 8.7          | I/O Signals                             |    |

| 8.7.1        | IRQ Input Pins (IRQ)                    |    |

| 8.8          | Registers                               |    |

| 0.0          | registers                               | ′′ |

|              | Chapter 9                               |    |

|              | Keyboard Interrupt Module (KBI)         |    |

| 9.1          | Introduction                            | 79 |

| 9.2          | Features                                | 79 |

| 9.3          | Functional Description                  |    |

| 9.3.1        | Keyboard Operation                      |    |

| 9.3.2        | Keyboard Initialization                 |    |

| 9.4          | Wait Mode                               | 82 |

| 9.5          | Stop Mode                               | 82 |

| 9.6          | Keyboard Module During Break Interrupts |    |

|              |                                         |    |

MC68HC908QY/QT Family Data Sheet, Rev. 6

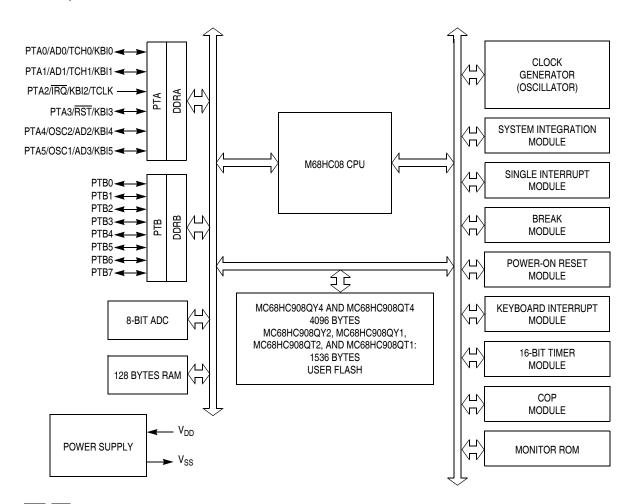

#### **General Description**

RST, IRQ: Pins have internal (about 30K Ohms) pull up

PTA[0:5]: High current sink and source capability

PTA[0:5]: Pins have programmable keyboard interrupt and pull up

PTB[0:7]: Not available on 8-pin devices – MC68HC908QT1, MC68HC908QT2, and MC68HC908QT4 (see note in 12.1 Introduction)

ADC: Not available on the MC68HC908QY1 and MC68HC908QT1

Figure 1-1. Block Diagram

MC68HC908QY/QT Family Data Sheet, Rev. 6

#### Memory

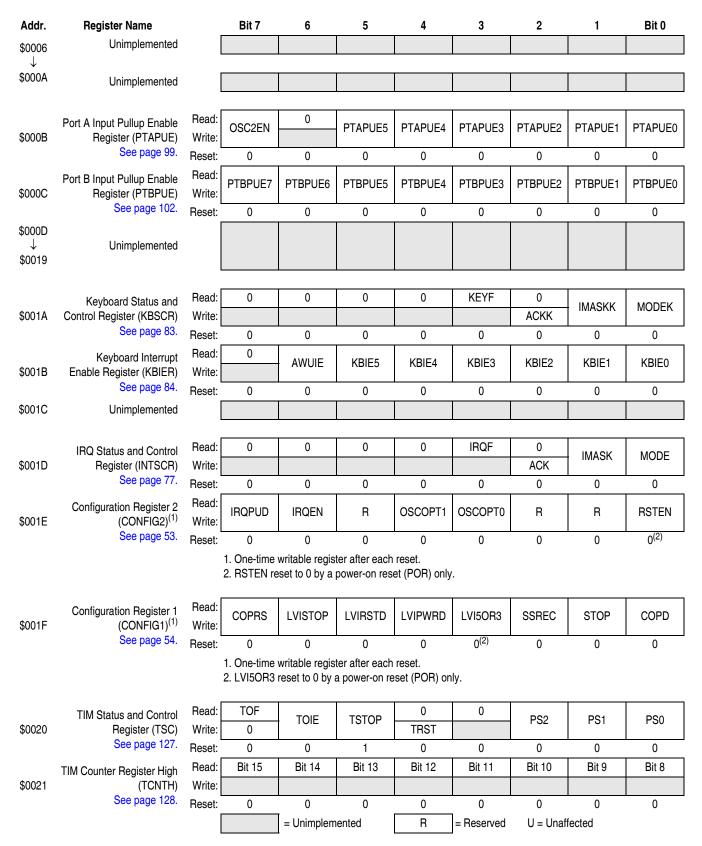

Figure 2-2. Control, Status, and Data Registers (Sheet 2 of 5)

MC68HC908QY/QT Family Data Sheet, Rev. 6

Memory

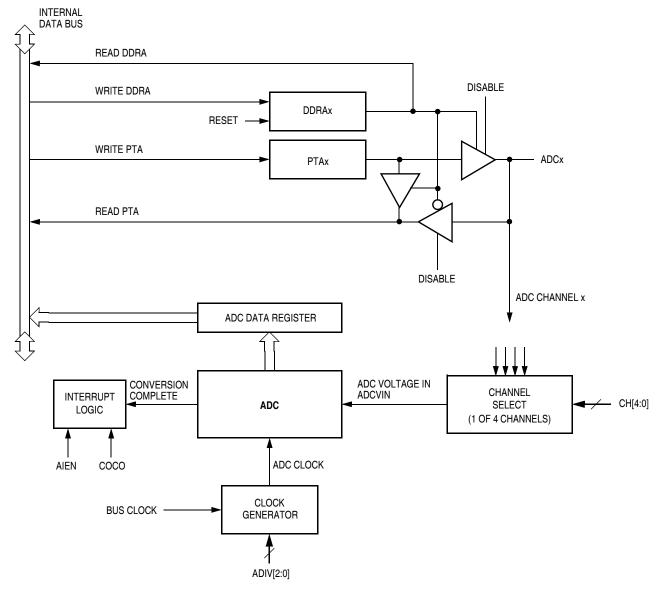

Figure 3-2. ADC Block Diagram

To protect the latch during the break state, write a 0 to the BCFE bit. With BCFE at 0 (its default state), writing to the keyboard acknowledge bit (ACKK) in the keyboard status and control register during the break state has no effect.

# 9.7 Input/Output Registers

The following I/O registers control and monitor operation of the keyboard interrupt module:

- Keyboard interrupt status and control register (KBSCR)

- Keyboard interrupt enable register (KBIER)

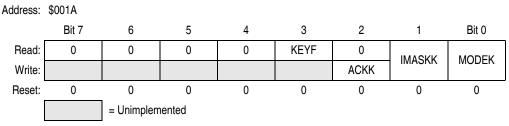

# 9.7.1 Keyboard Status and Control Register

The keyboard status and control register (KBSCR):

- Flags keyboard interrupt requests

- Acknowledges keyboard interrupt requests

- Masks keyboard interrupt requests

- Controls keyboard interrupt triggering sensitivity

Figure 9-3. Keyboard Status and Control Register (KBSCR)

#### Bits 7-4 — Not used

These read-only bits always read as 0s.

# **KEYF** — Keyboard Flag Bit

This read-only bit is set when a keyboard interrupt is pending on port A or auto wakeup. Reset clears the KEYF bit.

- 1 = Keyboard interrupt pending

- 0 = No keyboard interrupt pending

#### ACKK — Keyboard Acknowledge Bit

Writing a 1 to this write-only bit clears the keyboard interrupt request on port A and auto wakeup logic. ACKK always reads as 0. Reset clears ACKK.

### IMASKK— Keyboard Interrupt Mask Bit

Writing a 1 to this read/write bit prevents the output of the keyboard interrupt mask from generating interrupt requests on port A or auto wakeup. Reset clears the IMASKK bit.

- 1 = Keyboard interrupt requests masked

- 0 = Keyboard interrupt requests not masked

#### **MODEK** — Keyboard Triggering Sensitivity Bit

This read/write bit controls the triggering sensitivity of the keyboard interrupt pins on port A and auto wakeup. Reset clears MODEK.

- 1 = Keyboard interrupt requests on falling edges and low levels

- 0 = Keyboard interrupt requests on falling edges only

MC68HC908QY/QT Family Data Sheet, Rev. 6

# Chapter 10 Low-Voltage Inhibit (LVI)

# 10.1 Introduction

This section describes the low-voltage inhibit (LVI) module, which monitors the voltage on the  $V_{DD}$  pin and can force a reset when the  $V_{DD}$  voltage falls below the LVI trip falling voltage,  $V_{TRIPF}$ .

# 10.2 Features

Features of the LVI module include:

- Programmable LVI reset

- Programmable power consumption

- Selectable LVI trip voltage

- Programmable stop mode operation

# 10.3 Functional Description

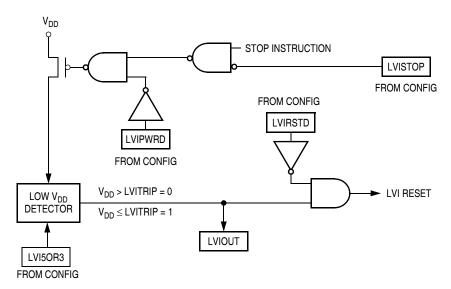

Figure 10-1 shows the structure of the LVI module. LVISTOP, LVIPWRD, LVI5OR3, and LVIRSTD are user selectable options found in the configuration register (CONFIG1). See Chapter 5 Configuration Register (CONFIG).

Figure 10-1. LVI Module Block Diagram

The LVI is enabled out of reset. The LVI module contains a bandgap reference circuit and comparator. Clearing the LVI power disable bit, LVIPWRD, enables the LVI to monitor  $V_{DD}$  voltage. Clearing the LVI reset disable bit, LVIRSTD, enables the LVI module to generate a reset when  $V_{DD}$  falls below a voltage,

Low-Voltage Inhibit (LVI)

Oscillator Module (OSC)

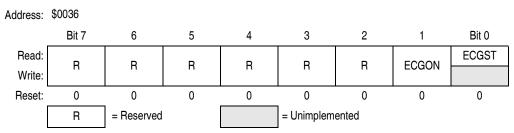

# 11.8.1 Oscillator Status Register

The oscillator status register (OSCSTAT) contains the bits for switching from internal to external clock sources.

Figure 11-4. Oscillator Status Register (OSCSTAT)

### **ECGON** — External Clock Generator On Bit

This read/write bit enables external clock generator, so that the switching process can be initiated. This bit is forced low during reset. This bit is ignored in monitor mode with the internal oscillator bypassed, PTM or CTM mode.

- 1 = External clock generator enabled

- 0 = External clock generator disabled

#### **ECGST** — External Clock Status Bit

This read-only bit indicates whether or not an external clock source is engaged to drive the system clock.

- 1 = An external clock source engaged

- 0 = An external clock source disengaged

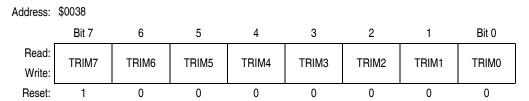

# 11.8.2 Oscillator Trim Register (OSCTRIM)

Figure 11-5. Oscillator Trim Register (OSCTRIM)

#### TRIM7-TRIM0 — Internal Oscillator Trim Factor Bits

These read/write bits change the size of the internal capacitor used by the internal oscillator. By measuring the period of the internal clock and adjusting this factor accordingly, the frequency of the internal clock can be fine tuned. Increasing (decreasing) this factor by one increases (decreases) the period by approximately 0.2% of the untrimmed period (the period for TRIM = \$80). The trimmed frequency is guaranteed not to vary by more than  $\pm 5\%$  over the full specified range of temperature and voltage. The reset value is \$80, which sets the frequency to 12.8 MHz (3.2 MHz bus speed)  $\pm 25\%$ .

Applications using the internal oscillator should copy the internal oscillator trim value at location \$FFC0 or \$FFC1 into this register to trim the clock source.

# **Chapter 12 Input/Output Ports (PORTS)**

# 12.1 Introduction

The MC68HC908QT1, MC68HC908QT2, and MC68HC908QT4 have five bidirectional input-output (I/O) pins and one input only pin. The MC68HC908QY1, MC68HC908QY2, and MC68HC908QY4 have thirteen bidirectional pins and one input only pin. All I/O pins are programmable as inputs or outputs.

#### NOTE

Connect any unused I/O pins to an appropriate logic level, either  $V_{\rm DD}$  or  $V_{\rm SS}$ . Although the I/O ports do not require termination for proper operation, termination reduces excess current consumption and the possibility of electrostatic damage.

8-pin devices have non-bonded pins. These pins should be configured either as outputs driving low or high, or as inputs with internal pullups enabled. Configuring these non-bonded pins in this manner will prevent any excess current consumption caused by floating inputs.

# 12.2 Port A

Port A is a 6-bit special function port that shares all six of its pins with the keyboard interrupt (KBI) module (see Chapter 9 Keyboard Interrupt Module (KBI)). Each port A pin also has a software configurable pullup device if the corresponding port pin is configured as an input port.

#### NOTE

PTA2 is input only.

When the  $\overline{IRQ}$  function is enabled in the configuration register 2 (CONFIG2), bit 2 of the port A data register (PTA) will always read a 0. In this case, the BIH and BIL instructions can be used to read the logic level on the PTA2 pin. When the  $\overline{IRQ}$  function is disabled, these instructions will behave as if the PTA2 pin is a logic 1. However, reading bit 2 of PTA will read the actual logic level on the pin.

A module that is active during wait mode can wake up the CPU with an interrupt if the interrupt is enabled. Stacking for the interrupt begins one cycle after the WAIT instruction during which the interrupt occurred. In wait mode, the CPU clocks are inactive. Refer to the wait mode subsection of each module to see if the module is active or inactive in wait mode. Some modules can be programmed to be active in wait mode.

Wait mode can also be exited by a reset (or break in emulation mode). A break interrupt during wait mode sets the SIM break stop/wait bit, SBSW, in the break status register (BSR). If the COP disable bit, COPD, in the configuration register is 0, then the computer operating properly module (COP) is enabled and remains active in wait mode.

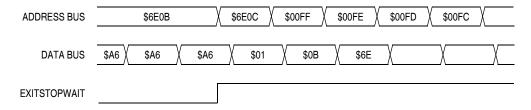

Figure 13-15 and Figure 13-16 show the timing for wait recovery.

NOTE: EXITSTOPWAIT = RST pin OR CPU interrupt OR break interrupt

Figure 13-15. Wait Recovery from Interrupt

Figure 13-16. Wait Recovery from Internal Reset

# 13.7.2 **Stop Mode**

In stop mode, the SIM counter is reset and the system clocks are disabled. An interrupt request from a module can cause an exit from stop mode. Stacking for interrupts begins after the selected stop recovery time has elapsed. Reset or break also causes an exit from stop mode.

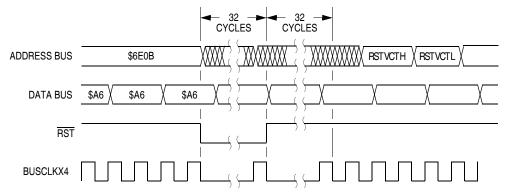

The SIM disables the oscillator signals (BUSCLKX2 and BUSCLKX4) in stop mode, stopping the CPU and peripherals. Stop recovery time is selectable using the SSREC bit in the configuration register 1 (CONFIG1). If SSREC is set, stop recovery is reduced from the normal delay of 4096 BUSCLKX4 cycles down to 32. This is ideal for the internal oscillator, RC oscillator, and external oscillator options which do not require long start-up times from stop mode.

#### NOTE

External crystal applications should use the full stop recovery time by clearing the SSREC bit.

MC68HC908QY/QT Family Data Sheet, Rev. 6

Timer Interface Module (TIM)

#### 14.4.1 TIM Counter Prescaler

The TIM clock source is one of the seven prescaler outputs or the TIM clock pin, TCLK. The prescaler generates seven clock rates from the internal bus clock. The prescaler select bits, PS[2:0], in the TIM status and control register (TSC) select the TIM clock source.

# 14.4.2 Input Capture

With the input capture function, the TIM can capture the time at which an external event occurs. When an active edge occurs on the pin of an input capture channel, the TIM latches the contents of the TIM counter into the TIM channel registers, TCHxH:TCHxL. The polarity of the active edge is programmable. Input captures can generate TIM central processor unit (CPU) interrupt requests.

# 14.4.3 Output Compare

With the output compare function, the TIM can generate a periodic pulse with a programmable polarity, duration, and frequency. When the counter reaches the value in the registers of an output compare channel, the TIM can set, clear, or toggle the channel pin. Output compares can generate TIM CPU interrupt requests.

## 14.4.3.1 Unbuffered Output Compare

Any output compare channel can generate unbuffered output compare pulses as described in 14.4.3 Output Compare. The pulses are unbuffered because changing the output compare value requires writing the new value over the old value currently in the TIM channel registers.

An unsynchronized write to the TIM channel registers to change an output compare value could cause incorrect operation for up to two counter overflow periods. For example, writing a new value before the counter reaches the old value but after the counter reaches the new value prevents any compare during that counter overflow period. Also, using a TIM overflow interrupt routine to write a new, smaller output compare value may cause the compare to be missed. The TIM may pass the new value before it is written.

Use the following methods to synchronize unbuffered changes in the output compare value on channel x:

- When changing to a smaller value, enable channel x output compare interrupts and write the new

value in the output compare interrupt routine. The output compare interrupt occurs at the end of

the current output compare pulse. The interrupt routine has until the end of the counter overflow

period to write the new value.

- When changing to a larger output compare value, enable TIM overflow interrupts and write the new

value in the TIM overflow interrupt routine. The TIM overflow interrupt occurs at the end of the

current counter overflow period. Writing a larger value in an output compare interrupt routine (at

the end of the current pulse) could cause two output compares to occur in the same counter

overflow period.

#### 14.4.3.2 Buffered Output Compare

Channels 0 and 1 can be linked to form a buffered output compare channel whose output appears on the TCH0 pin. The TIM channel registers of the linked pair alternately control the output.

Setting the MS0B bit in TIM channel 0 status and control register (TSC0) links channel 0 and channel 1. The output compare value in the TIM channel 0 registers initially controls the output on the TCH0 pin. Writing to the TIM channel 1 registers enables the TIM channel 1 registers to synchronously control the output after the TIM overflows. At each subsequent overflow, the TIM channel registers (0 or 1) that

MC68HC908QY/QT Family Data Sheet, Rev. 6

#### **Timer Interface Module (TIM)**

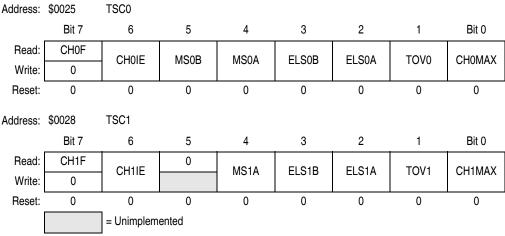

Figure 14-7. TIM Channel Status and Control Registers (TSC0:TSC1)

# CHxF — Channel x Flag Bit

When channel x is an input capture channel, this read/write bit is set when an active edge occurs on the channel x pin. When channel x is an output compare channel, CHxF is set when the value in the TIM counter registers matches the value in the TIM channel x registers.

Clear CHxF by reading the TIM channel x status and control register with CHxF set and then writing a 0 to CHxF. If another interrupt request occurs before the clearing sequence is complete, then writing a 0 to CHxF has no effect. Therefore, an interrupt request cannot be lost due to inadvertent clearing of CHxF.

Reset clears the CHxF bit. Writing a 1 to CHxF has no effect.

- 1 = Input capture or output compare on channel x

- 0 = No input capture or output compare on channel x

#### CHxIE — Channel x Interrupt Enable Bit

This read/write bit enables TIM CPU interrupt service requests on channel x. Reset clears the CHxIE bit.

- 1 = Channel x CPU interrupt requests enabled

- 0 = Channel x CPU interrupt requests disabled

#### MSxB — Mode Select Bit B

This read/write bit selects buffered output compare/PWM operation. MSxB exists only in the TIM channel 0 status and control register.

Setting MS0B disables the channel 1 status and control register and reverts TCH1 to general-purpose I/O.

Reset clears the MSxB bit.

- 1 = Buffered output compare/PWM operation enabled

- 0 = Buffered output compare/PWM operation disabled

#### MSxA — Mode Select Bit A

When ELSxB:A  $\neq$  00, this read/write bit selects either input capture operation or unbuffered output compare/PWM operation. See Table 14-3.

- 1 = Unbuffered output compare/PWM operation

- 0 = Input capture operation

MC68HC908QY/QT Family Data Sheet, Rev. 6

When the internal address bus matches the value written in the break address registers or when software writes a 1 to the BRKA bit in the break status and control register, the CPU starts a break interrupt by:

- Loading the instruction register with the SWI instruction

- Loading the program counter with \$FFFC and \$FFFD (\$FEFC and \$FEFD in monitor mode)

The break interrupt timing is:

- When a break address is placed at the address of the instruction opcode, the instruction is not executed until after completion of the break interrupt routine.

- When a break address is placed at an address of an instruction operand, the instruction is executed before the break interrupt.

- When software writes a 1 to the BRKA bit, the break interrupt occurs just before the next instruction is executed.

By updating a break address and clearing the BRKA bit in a break interrupt routine, a break interrupt can be generated continuously.

#### **CAUTION**

A break address should be placed at the address of the instruction opcode. When software does not change the break address and clears the BRKA bit in the first break interrupt routine, the next break interrupt will not be generated after exiting the interrupt routine even when the internal address bus matches the value written in the break address registers.

# 15.2.1.1 Flag Protection During Break Interrupts

The system integration module (SIM) controls whether or not module status bits can be cleared during the break state. The BCFE bit in the break flag control register (BFCR) enables software to clear status bits during the break state. See 13.8.2 Break Flag Control Register and the **Break Interrupts** subsection for each module.

#### 15.2.1.2 TIM During Break Interrupts

A break interrupt stops the timer counter.

# 15.2.1.3 COP During Break Interrupts

The COP is disabled during a break interrupt with monitor mode when BDCOP bit is set in break auxiliary register (BRKAR).

# 15.2.2 Break Module Registers

These registers control and monitor operation of the break module:

- Break status and control register (BRKSCR)

- Break address register high (BRKH)

- Break address register low (BRKL)

- Break status register (BSR)

- Break flag control register (BFCR)

#### **Electrical Specifications**

# 16.12 3-V Oscillator Characteristics

| Characteristic                                                                                                                                                                            | Symbol             | Min             | Тур                | Max           | Unit |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------|--------------------|---------------|------|

| Internal oscillator frequency <sup>(1)</sup>                                                                                                                                              | fINTCLK            | _               | 12.8               | _             | MHz  |

| Deviation from trimmed Internal oscillator <sup>(2)(3)</sup> 12.8 MHz, fixed voltage, fixed temp 12.8 MHz, V <sub>DD</sub> ± 10%, 0 to 70°C 12.8 MHz, V <sub>DD</sub> ± 10%, –40 to 125°C | ACC <sub>INT</sub> | _<br>_<br>_     | ± 0.4<br>± 2<br>—  | —<br>—<br>± 5 | %    |

| Crystal frequency, XTALCLK <sup>(1)</sup>                                                                                                                                                 | foscxclk           | 1               | _                  | 16            | MHz  |

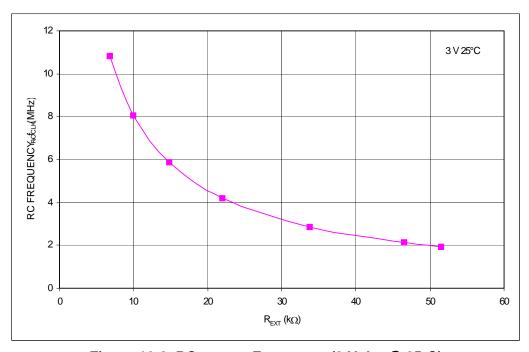

| External RC oscillator frequency, RCCLK (1)                                                                                                                                               | f <sub>RCCLK</sub> | 2               | _                  | 10            | MHz  |

| External clock reference frequency <sup>(1)</sup> (4)                                                                                                                                     | foscxclk           | dc              | _                  | 16            | MHz  |

| Crystal load capacitance <sup>(5)</sup>                                                                                                                                                   | CL                 | _               | 20                 | _             | pF   |

| Crystal fixed capacitance <sup>(3)</sup>                                                                                                                                                  | C <sub>1</sub>     | _               | 2 x C <sub>L</sub> | _             | _    |

| Crystal tuning capacitance <sup>(3)</sup>                                                                                                                                                 | C <sub>2</sub>     | _               | 2 x C <sub>L</sub> | _             | _    |

| Feedback bias resistor                                                                                                                                                                    | R <sub>B</sub>     | 0.5             | 1                  | 10            | ΜΩ   |

| RC oscillator external resistor                                                                                                                                                           | R <sub>EXT</sub>   | See Figure 16-8 |                    |               | _    |

| Crystal series damping resistor  f <sub>OSCXCLK</sub> = 1 MHz  f <sub>OSCXCLK</sub> = 4 MHz  f <sub>OSCXCLK</sub> = > 8 MHz                                                               | R <sub>S</sub>     | _<br>_<br>_     | 10<br>5<br>0       | _<br>_<br>_   | kΩ   |

- Bus frequency, f<sub>OP</sub>, is oscillator frequency divided by 4.

Deviation values assumes trimming @25•C and midpoint of voltage range.

Values are based on characterization results, not tested in production.

- 4. No more than 10% duty cycle deviation from 50%

- 5. Consult crystal vendor data sheet

Figure 16-8. RC versus Frequency (3 Volts @ 25•C)

MC68HC908QY/QT Family Data Sheet, Rev. 6

Semiconductor

© FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED.

ELECTRONIC VERSIONS ARE UNCONTROLLED EXCEPT WHEN ACCESSED

DIRECTLY FROM THE DOCUMENT CONTROL REPOSITORY, PRINTED

VERSIONS ARE UNCONTROLLED EXCEPT WHEN STAMPED "CONTROLLED

COPY" IN RED.

# MECHANICAL OUTLINES DICTIONARY

PAGE: 968

DOCUMENT NO: 98ASH70107A

DO NOT SCALE THIS DRAWING

REV: A

#### NOTES:

- 1. DIMENSIONS AND TOLERANCES PER ASME Y14.5-1994.

- 2. CONTROLLING DIMENSION: MILLIMETER.

3. DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS AND ARE MEASURED AT THE PARTING LINE. MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEDD 0.15mm PER SIDE.

4. TERMINAL NUMBERS ARE SHOWN FOR REFERENCE ONLY.

THE LEAD WIDTH DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION SHALL BE 0.08mm TOTAL IN EXCESS OF THE LEAD WIDTH DIMENSION AT MAXIMUM MATERIAL CONDITION.

DAMBAR CANNOT BE LOCATED ON THE LOWER RADIUS OR THE FOOT. MINIMUM SPACE BETWEEN PROTRUSIONS AND ADJACENT LEAD TO BE 0.46mm.

TITLE:

8 LEAD MFP

STANDARD: E1AJ

PACKAGE CODE: 6003 SHEET: 3 OF 4

\*\*Semiconductor\*\*

© FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED.

ELECTRONIC VERSIONS ARE UNCONTROLLED EXCEPT WHEN ACCESSED

DIRECTLY FROM THE DOCUMENT CONTROL REPOSITORY, PRINTED

VERSIONS ARE UNCONTROLLED EXCEPT WHEN STAMPED "CONTROLLED

COPY" IN RED.

# MECHANICAL OUTLINES DICTIONARY

DO NOT SCALE THIS DRAWING

DOCUMENT NO: 98ARL10557D

PAGE: 1452

REV: A

#### NOTES:

1. ALL DIMENSIONS ARE IN MILLIMETERS.

2. INTERPRET DIMENSIONS AND TOLERANCES PER ASME Y14.5M-1994.

3. THE COMPLETE JEDEC DESIGNATOR FOR THIS PACKAGE IS: HP-VFDFP-N.

COPLANARITY APPLIES TO LEADS AND DIE ATTACH PAD.

FLAT NO LEAD PACKAGE (DFN)

8 TERMINAL, 0. 8 PITCH(4 X 4 X 1)

CASE NUMBER: 1452-01

STANDARD: NON-JEDEC

PACKAGE CODE: 6165 | SHEET: 4 OF 5