#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                       |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | HC08                                                         |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 8MHz                                                         |

| Connectivity               | -                                                            |

| Peripherals                | LVD, POR, PWM                                                |

| Number of I/O              | 5                                                            |

| Program Memory Size        | 4KB (4K x 8)                                                 |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | -                                                            |

| RAM Size                   | 128 × 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                  |

| Data Converters            | A/D 4x8b                                                     |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                           |

| Mounting Type              | Through Hole                                                 |

| Package / Case             | 8-DIP (0.300", 7.62mm)                                       |

| Supplier Device Package    | 8-PDIP                                                       |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc68hc908qt4mpe |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Table of Contents**

| 3.6   | Input/Output Signals            | 45 |

|-------|---------------------------------|----|

| 3.7   | Input/Output Registers          | 45 |

|       | ADC Status and Control Register |    |

| 3.7.2 | ADC Data Register.              | 47 |

| 3.7.3 | ADC Input Clock Register        | 47 |

## Chapter 4 Auto Wakeup Module (AWU)

|       |                                        | • | , |        |

|-------|----------------------------------------|---|---|--------|

| 4.1   | Introduction                           |   |   | <br>49 |

| 4.2   | Features                               |   |   | <br>49 |

| 4.3   | Functional Description                 |   |   | <br>49 |

| 4.4   | Wait Mode                              |   |   | <br>50 |

| 4.5   | Stop Mode                              |   |   | <br>50 |

| 4.6   | Input/Output Registers                 |   |   | <br>51 |

| 4.6.1 | 1 Port A I/O Register                  |   |   | <br>51 |

| 4.6.2 | 2 Keyboard Status and Control Register |   |   | <br>51 |

| 4.6.3 | 3 Keyboard Interrupt Enable Register   |   |   | <br>52 |

# Chapter 5 Configuration Register (CONFIG)

| 5.1 | Introduction           | 53 |

|-----|------------------------|----|

| 5.2 | Functional Description | 53 |

## Chapter 6 Computer Operating Properly (COP)

| 6.1   | Introduction                 | 57              |

|-------|------------------------------|-----------------|

| 6.2   | Functional Description       | 57              |

| 6.3   | I/O Signals                  | 58              |

| 6.3.1 | BUSCLKX4                     | <mark>58</mark> |

| 6.3.2 | STOP Instruction             | <b>58</b>       |

| 6.3.3 | COPCTL Write                 | 58              |

| 6.3.4 | Power-On Reset.              | 58              |

| 6.3.5 | Internal Reset               | 58              |

| 6.3.6 | COPD (COP Disable).          |                 |

| 6.3.7 | COPRS (COP Rate Select)      | 59              |

| 6.4   | COP Control Register         | 59              |

| 6.5   | Interrupts                   | 59              |

| 6.6   | Monitor Mode                 | 59              |

| 6.7   | Low-Power Modes              | 59              |

| 6.7.1 | Wait Mode                    | 59              |

| 6.7.2 | Stop Mode                    | 59              |

| 6.8   | COP Module During Break Mode | 59              |

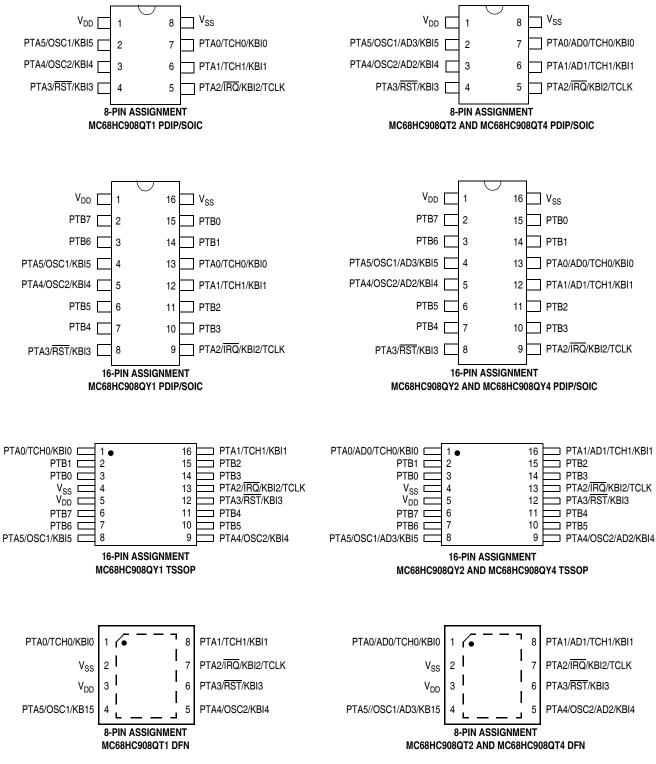

**Pin Assignments**

**General Description**

## **1.5 Pin Functions**

Table 1-2 provides a description of the pin functions.

| Pin<br>Name             | Description                                                                                                         | Input/Output     |

|-------------------------|---------------------------------------------------------------------------------------------------------------------|------------------|

| $V_{DD}$                | Power supply                                                                                                        | Power            |

| V <sub>SS</sub>         | Power supply ground                                                                                                 | Power            |

|                         | PTA0 — General purpose I/O port                                                                                     | Input/Output     |

| PTA0                    | AD0 — A/D channel 0 input                                                                                           | Input            |

|                         | TCH0 — Timer Channel 0 I/O                                                                                          | Input/Output     |

|                         | KBI0 — Keyboard interrupt input 0                                                                                   | Input            |

|                         | PTA1 — General purpose I/O port                                                                                     | Input/Output     |

| PTA1                    | AD1 — A/D channel 1 input                                                                                           | Input            |

| FIAT                    | TCH1 — Timer Channel 1 I/O                                                                                          | Input/Output     |

|                         | KBI1 — Keyboard interrupt input 1                                                                                   | Input            |

|                         | PTA2 — General purpose input-only port                                                                              | Input            |

| PTA2                    | IRQ — External interrupt with programmable pullup and Schmitt trigger input                                         | Input            |

| ΠΑΖ                     | KBI2 — Keyboard interrupt input 2                                                                                   | Input            |

|                         | TCLK — Timer clock input                                                                                            | Input            |

|                         | PTA3 — General purpose I/O port                                                                                     | Input/Output     |

| PTA3                    | RST — Reset input, active low with internal pullup and Schmitt trigger                                              | Input            |

|                         | KBI3 — Keyboard interrupt input 3                                                                                   | Input            |

|                         | PTA4 — General purpose I/O port                                                                                     | Input/Output     |

| PTA4                    | OSC2 —XTAL oscillator output (XTAL option only)<br>RC or internal oscillator output (OSC2EN = 1 in PTAPUE register) | Output<br>Output |

|                         | AD2 — A/D channel 2 input                                                                                           | Input            |

|                         | KBI4 — Keyboard interrupt input 4                                                                                   | Input            |

|                         | PTA5 — General purpose I/O port                                                                                     | Input/Output     |

| PTA5                    | OSC1 — XTAL, RC, or external oscillator input                                                                       | Input            |

| F IAU                   | AD3 — A/D channel 3 input                                                                                           | Input            |

|                         | KBI5 — Keyboard interrupt input 5                                                                                   | Input            |

| PTB[0:7] <sup>(1)</sup> | 8 general-purpose I/O ports                                                                                         | Input/Output     |

## Table 1-2. Pin Functions

1. The PTB pins are not available on the 8-pin packages (see note in 12.1 Introduction).

| Vector Priority | Vector           | Address | Vector                                |

|-----------------|------------------|---------|---------------------------------------|

| Lowest          | IF15             | \$FFDE  | ADC conversion complete vector (high) |

| ▲               | 1613             | \$FFDF  | ADC conversion complete vector (low)  |

|                 | IF14             | \$FFE0  | Keyboard vector (high)                |

|                 | 1614             | \$FFE1  | Keyboard vector (low)                 |

|                 | IF13<br>↓<br>IF6 | _       | Not used                              |

|                 | 155              | \$FFF2  | TIM overflow vector (high)            |

|                 | IF5              | \$FFF3  | TIM overflow vector (low)             |

|                 | IF4              | \$FFF4  | TIM Channel 1 vector (high)           |

|                 |                  | \$FFF5  | TIM Channel 1 vector (low)            |

|                 | IF3              | \$FFF6  | TIM Channel 0 vector (high)           |

|                 |                  | \$FFF7  | TIM Channel 0 vector (low)            |

|                 | IF2              | —       | Not used                              |

|                 | IF1              | \$FFFA  | IRQ vector (high)                     |

|                 |                  | \$FFFB  | IRQ vector (low)                      |

|                 |                  | \$FFFC  | SWI vector (high)                     |

|                 | _                | \$FFFD  | SWI vector (low)                      |

| ♥               |                  | \$FFFE  | Reset vector (high)                   |

| Highest         |                  | \$FFFF  | Reset vector (low)                    |

Table 2-1. Vector Addresses

## 2.5 Random-Access Memory (RAM)

Addresses \$0080–\$00FF are RAM locations. The location of the stack RAM is programmable. The 16-bit stack pointer allows the stack to be anywhere in the 64-Kbyte memory space.

## NOTE

For correct operation, the stack pointer must point only to RAM locations.

Before processing an interrupt, the central processor unit (CPU) uses five bytes of the stack to save the contents of the CPU registers.

## NOTE

For M6805, M146805, and M68HC05 compatibility, the H register is not stacked.

During a subroutine call, the CPU uses two bytes of the stack to store the return address. The stack pointer decrements during pushes and increments during pulls.

## NOTE

Be careful when using nested subroutines. The CPU may overwrite data in the RAM during a subroutine or during the interrupt stacking operation.

#### Auto Wakeup Module (AWU)

## Bits 7-4 — Not used

These read-only bits always read as 0s.

## **KEYF** — Keyboard Flag Bit

This read-only bit is set when a keyboard interrupt is pending on port A or auto wakeup. Reset clears the KEYF bit.

1 = Keyboard/auto wakeup interrupt pending

0 = No keyboard/auto wakeup interrupt pending

## ACKK — Keyboard Acknowledge Bit

Writing a 1 to this write-only bit clears the keyboard/auto wakeup interrupt request on port A and auto wakeup logic. ACKK always reads as 0.Reset clears ACKK.

## IMASKK— Keyboard Interrupt Mask Bit

Writing a 1 to this read/write bit prevents the output of the keyboard interrupt mask from generating interrupt requests on port A or auto wakeup. Reset clears the IMASKK bit.

1 = Keyboard/auto wakeup interrupt requests masked

0 = Keyboard/auto wakeup interrupt requests not masked

## NOTE

MODEK is not used in conjuction with the auto wakeup feature. To see a description of this bit, see 9.7.1 Keyboard Status and Control Register.

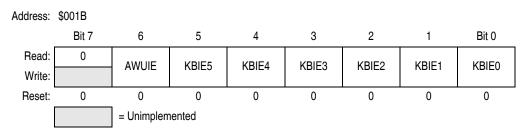

## 4.6.3 Keyboard Interrupt Enable Register

The keyboard interrupt enable register (KBIER) enables or disables the auto wakeup to operate as a keyboard/auto wakeup interrupt input.

## Figure 4-4. Keyboard Interrupt Enable Register (KBIER)

## AWUIE — Auto Wakeup Interrupt Enable Bit

This read/write bit enables the auto wakeup interrupt input to latch interrupt requests. Reset clears AWUIE.

1 = Auto wakeup enabled as interrupt input

0 = Auto wakeup not enabled as interrupt input

### NOTE

KBIE5–KBIE0 bits are not used in conjuction with the auto wakeup feature. To see a description of these bits, see 9.7.2 Keyboard Interrupt Enable Register.

#### **Configuration Register (CONFIG)**

## IRQPUD — IRQ Pin Pullup Control Bit

- 1 = Internal pullup is disconnected

- 0 = Internal pullup is connected between  $\overline{IRQ}$  pin and  $V_{DD}$

### IRQEN — IRQ Pin Function Selection Bit

- 1 = Interrupt request function active in pin

- 0 = Interrupt request function inactive in pin

## OSCOPT1 and OSCOPT0 — Selection Bits for Oscillator Option

- (0, 0) Internal oscillator

- (0, 1) External oscillator

- (1, 0) External RC oscillator

- (1, 1) External XTAL oscillator

## **RSTEN** — **RST** Pin Function Selection

- 1 = Reset function active in pin

- 0 =Reset function inactive in pin

#### NOTE

The RSTEN bit is cleared by a power-on reset (POR) only. Other resets will leave this bit unaffected.

Address: \$001F

|                 | Bit 7 | 6       | 5       | 4       | 3       | 2     | 1    | Bit 0 |

|-----------------|-------|---------|---------|---------|---------|-------|------|-------|

| Read:<br>Write: | COPRS | LVISTOP | LVIRSTD | LVIPWRD | LVI5OR3 | SSREC | STOP | COPD  |

| Reset:          | 0     | 0       | 0       | 0       | U       | 0     | 0    | 0     |

| POR:            | 0     | 0       | 0       | 0       | 0       | 0     | 0    | 0     |

|                 |       |         |         |         |         |       |      |       |

U = Unaffected

### Figure 5-2. Configuration Register 1 (CONFIG1)

### COPRS (Out of STOP Mode) — COP Reset Period Selection Bit

- 1 = COP reset short cycle = 8176 × BUSCLKX4

- $0 = COP reset long cycle = 262,128 \times BUSCLKX4$

## COPRS (In STOP Mode) — Auto Wakeup Period Selection Bit

- 1 = Auto wakeup short cycle =  $512 \times INTRCOSC$

- $0 = Auto wakeup long cycle = 16,384 \times INTRCOSC$

### LVISTOP — LVI Enable in Stop Mode Bit

When the LVIPWRD bit is clear, setting the LVISTOP bit enables the LVI to operate during stop mode. Reset clears LVISTOP.

1 = LVI enabled during stop mode

0 = LVI disabled during stop mode

### LVIRSTD — LVI Reset Disable Bit

LVIRSTD disables the reset signal from the LVI module.

1 = LVI module resets disabled

0 = LVI module resets enabled

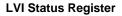

## 10.4 LVI Status Register

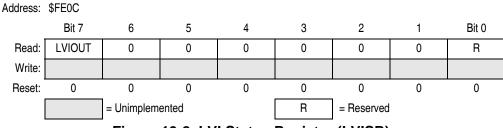

The LVI status register (LVISR) indicates if the  $V_{DD}$  voltage was detected below the  $V_{TRIPF}$  level while LVI resets have been disabled.

Figure 10-2. LVI Status Register (LVISR)

## LVIOUT — LVI Output Bit

This read-only flag becomes set when the  $V_{DD}$  voltage falls below the  $V_{TRIPF}$  trip voltage and is cleared when  $V_{DD}$  voltage rises above  $V_{TRIPR}$ . The difference in these threshold levels results in a hysteresis that prevents oscillation into and out of reset (see Table 10-1). Reset clears the LVIOUT bit.

| V <sub>DD</sub>                  | LVIOUT         |

|----------------------------------|----------------|

| $V_{DD} > V_{TRIPR}$             | 0              |

| $V_{DD} < V_{TRIPF}$             | 1              |

| $V_{TRIPF} < V_{DD} < V_{TRIPR}$ | Previous value |

Table 10-1. LVIOUT Bit Indication

## 10.5 LVI Interrupts

The LVI module does not generate interrupt requests.

## **10.6 Low-Power Modes**

The STOP and WAIT instructions put the MCU in low power-consumption standby modes.

## 10.6.1 Wait Mode

If enabled, the LVI module remains active in wait mode. If enabled to generate resets, the LVI module can generate a reset and bring the MCU out of wait mode.

## 10.6.2 Stop Mode

When the LVIPWRD bit in the configuration register is cleared and the LVISTOP bit in the configuration register is set, the LVI module remains active in stop mode. If enabled to generate resets, the LVI module can generate a reset and bring the MCU out of stop mode.

## 11.3.1.1 Internal Oscillator Trimming

The 8-bit trimming register, OSCTRIM, allows a clock period adjust of +127 and -128 steps. Increasing OSCTRIM value increases the clock period. Trimming allows the internal clock frequency to be set to 12.8 MHz  $\pm$  5%.

All devices are factory programmed with trim values in reserved FLASH memory locations \$FFC0 and \$FFC1. The trim value is not automatically loaded into the OSCTRIM register. User software must copy the trim value from \$FFC0 or \$FFC1 into OSCTRIM if needed. The factory trim value provides the accuracy required for communication using forced monitor mode. Some production programmers erase the factory trim values, so confirm with your programmer vendor that the trim values at \$FFC0 and \$FFC1 are preserved, or are re-trimmed. Trimming the device in the user application board will provide the most accurate trim value.

## 11.3.1.2 Internal to External Clock Switching

When external clock source (external OSC, RC, or XTAL) is desired, the user must perform the following steps:

- 1. For external crystal circuits only, OSCOPT[1:0] = 1:1: To help precharge an external crystal oscillator, set PTA4 (OSC2) as an output and drive high for several cycles. This may help the crystal circuit start more robustly.

- Set CONFIG2 bits OSCOPT[1:0] according to . The oscillator module control logic will then set OSC1 as an external clock input and, if the external crystal option is selected, OSC2 will also be set as the clock output.

- 3. Create a software delay to wait the stabilization time needed for the selected clock source (crystal, resonator, RC) as recommended by the component manufacturer. A good rule of thumb for crystal oscillators is to wait 4096 cycles of the crystal frequency, i.e., for a 4-MHz crystal, wait approximately 1 msec.

- 4. After the manufacturer's recommended delay has elapsed, the ECGON bit in the OSC status register (OSCSTAT) needs to be set by the user software.

- 5. After ECGON set is detected, the OSC module checks for oscillator activity by waiting two external clock rising edges.

- 6. The OSC module then switches to the external clock. Logic provides a glitch free transition.

- 7. The OSC module first sets the ECGST bit in the OSCSTAT register and then stops the internal oscillator.

### NOTE

Once transition to the external clock is done, the internal oscillator will only be reactivated with reset. No post-switch clock monitor feature is implemented (clock does not switch back to internal if external clock dies).

## 11.3.2 External Oscillator

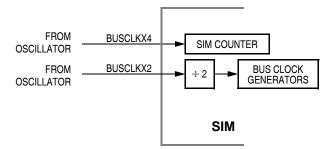

The external clock option is designed for use when a clock signal is available in the application to provide a clock source to the microcontroller. The OSC1 pin is enabled as an input by the oscillator module. The clock signal is used directly to create BUSCLKX4 and also divided by two to create BUSCLKX2.

In this configuration, the OSC2 pin cannot output BUSCLKX4.So the OSC2EN bit in the port A pullup enable register will be clear to enable PTA4 I/O functions on the pin

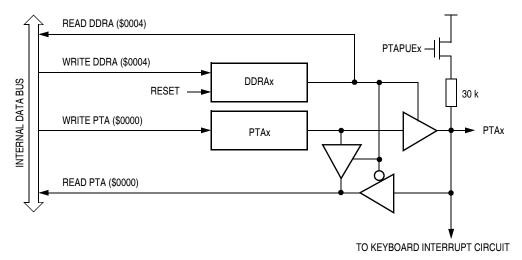

Figure 12-3 shows the port A I/O logic.

Figure 12-3. Port A I/O Circuit

**NOTE** Figure 12-3 does not apply to PTA2

When DDRAx is a 1, reading address \$0000 reads the PTAx data latch. When DDRAx is a 0, reading address \$0000 reads the voltage level on the pin. The data latch can always be written, regardless of the state of its data direction bit.

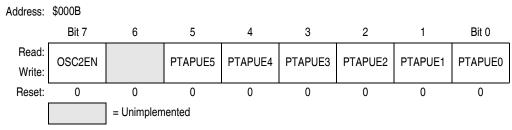

## 12.2.3 Port A Input Pullup Enable Register

The port A input pullup enable register (PTAPUE) contains a software configurable pullup device for each if the six port A pins. Each bit is individually configurable and requires the corresponding data direction register, DDRAx, to be configured as input. Each pullup device is automatically and dynamically disabled when its corresponding DDRAx bit is configured as output.

## **OSC2EN** — Enable PTA4 on OSC2 Pin

This read/write bit configures the OSC2 pin function when internal oscillator or RC oscillator option is selected. This bit has no effect for the XTAL or external oscillator options.

1 = OSC2 pin outputs the internal or RC oscillator clock (BUSCLKX4)

0 = OSC2 pin configured for PTA4 I/O, having all the interrupt and pullup functions

Figure 13-2. SIM Clock Signals

## 13.3.1 Bus Timing

In user mode, the internal bus frequency is the oscillator frequency (BUSCLKX4) divided by four.

## 13.3.2 Clock Start-Up from POR

When the power-on reset module generates a reset, the clocks to the CPU and peripherals are inactive and held in an inactive phase until after the 4096 BUSCLKX4 cycle POR time out has completed. The IBUS clocks start upon completion of the time out.

## 13.3.3 Clocks in Stop Mode and Wait Mode

Upon exit from stop mode by an interrupt or reset, the SIM allows BUSCLKX4 to clock the SIM counter. The CPU and peripheral clocks do not become active until after the stop delay time out. This time out is selectable as 4096 or 32 BUSCLKX4 cycles. See 13.7.2 Stop Mode.

In wait mode, the CPU clocks are inactive. The SIM also produces two sets of clocks for other modules. Refer to the wait mode subsection of each module to see if the module is active or inactive in wait mode. Some modules can be programmed to be active in wait mode.

## 13.4 Reset and System Initialization

The MCU has these reset sources:

- Power-on reset module (POR)

- External reset pin (RST)

- Computer operating properly module (COP)

- Low-voltage inhibit module (LVI)

- Illegal opcode

- Illegal address

All of these resets produce the vector \$FFFE\_FFF (\$FEFE\_FEFF in monitor mode) and assert the internal reset signal (IRST). IRST causes all registers to be returned to their default values and all modules to be returned to their reset states.

An internal reset clears the SIM counter (see 13.5 SIM Counter), but an external reset does not. Each of the resets sets a corresponding bit in the SIM reset status register (SRSR). See 13.8 SIM Registers.

#### System Integration Module (SIM)

The SIM counter is held in reset from the execution of the STOP instruction until the beginning of stop recovery. It is then used to time the recovery period. Figure 13-17 shows stop mode entry timing and Figure 13-18 shows the stop mode recovery time from interrupt or break.

**NOTE** To minimize stop current, all pins configured as inputs should be driven to

#### a logic 1 or logic 0. CPUSTOP ADDRESS BUS STOP ADDR STOP ADDR + 1 SAME SAME DATA BUS PREVIOUS DATA NEXT OPCODE SAME SAME R/W NOTE: Previous data can be operand data or the STOP opcode, depending on the last instruction. Figure 13-17. Stop Mode Entry Timing STOP RECOVERY PERIOD BUSCLKX4 INTERRUPT ADDRESS BUS STOP +1 STOP + 2 STOP + 2 SP SP – 1 SP – 2 SP – 3

Figure 13-18. Stop Mode Recovery from Interrupt

## 13.8 SIM Registers

The SIM has three memory mapped registers. Table 13-4 shows the mapping of these registers.

### Table 13-4. SIM Registers

| Address | Register | Access Mode |

|---------|----------|-------------|

| \$FE00  | BSR      | User        |

| \$FE01  | SRSR     | User        |

| \$FE03  | BFCR     | User        |

Timer Interface Module (TIM)

## 14.6 Wait Mode

The WAIT instruction puts the MCU in low power-consumption standby mode.

The TIM remains active after the execution of a WAIT instruction. In wait mode the TIM registers are not accessible by the CPU. Any enabled CPU interrupt request from the TIM can bring the MCU out of wait mode.

If TIM functions are not required during wait mode, reduce power consumption by stopping the TIM before executing the WAIT instruction.

## 14.7 TIM During Break Interrupts

A break interrupt stops the TIM counter.

The system integration module (SIM) controls whether status bits in other modules can be cleared during the break state. The BCFE bit in the break flag control register (BFCR) enables software to clear status bits during the break state. See 13.8.2 Break Flag Control Register.

To allow software to clear status bits during a break interrupt, write a 1 to the BCFE bit. If a status bit is cleared during the break state, it remains cleared when the MCU exits the break state.

To protect status bits during the break state, write a 0 to the BCFE bit. With BCFE at 0 (its default state), software can read and write I/O registers during the break state without affecting status bits. Some status bits have a two-step read/write clearing procedure. If software does the first step on such a bit before the break, the bit cannot change during the break state as long as BCFE is at 0. After the break, doing the second step clears the status bit.

## 14.8 Input/Output Signals

Port A shares three of its pins with the TIM. Two TIM channel I/O pins are PTA0/TCH0 and PTA1/TCH1 and an alternate clock source is PTA2/TCLK.

## 14.8.1 TIM Clock Pin (PTA2/TCLK)

PTA2/TCLK is an external clock input that can be the clock source for the TIM counter instead of the prescaled internal bus clock. Select the PTA2/TCLK input by writing 1s to the three prescaler select bits, PS[2–0]. (See 14.9.1 TIM Status and Control Register.) When the PTA2/TCLK pin is the TIM clock input, it is an input regardless of port pin initialization.

## 14.8.2 TIM Channel I/O Pins (PTA0/TCH0 and PTA1/TCH1)

Each channel I/O pin is programmable independently as an input capture pin or an output compare pin. PTA0/TCH0 can be configured as a buffered output compare or buffered PWM pin.

## 14.9 Input/Output Registers

The following I/O registers control and monitor operation of the TIM:

- TIM status and control register (TSC)

- TIM counter registers (TCNTH:TCNTL)

- TIM counter modulo registers (TMODH:TMODL)

- TIM channel status and control registers (TSC0 and TSC1)

- TIM channel registers (TCH0H:TCH0L and TCH1H:TCH1L)

#### Timer Interface Module (TIM)

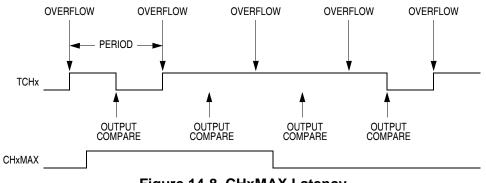

## CHxMAX — Channel x Maximum Duty Cycle Bit

When the TOVx bit is at a 1, setting the CHxMAX bit forces the duty cycle of buffered and unbuffered PWM signals to 100%. As Figure 14-8 shows, the CHxMAX bit takes effect in the cycle after it is set or cleared. The output stays at the 100% duty cycle level until the cycle after CHxMAX is cleared.

Figure 14-8. CHxMAX Latency

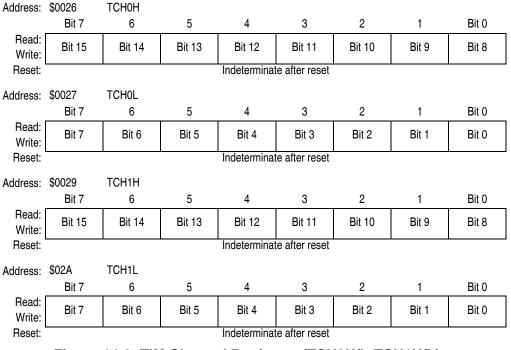

## 14.9.5 TIM Channel Registers

These read/write registers contain the captured TIM counter value of the input capture function or the output compare value of the output compare function. The state of the TIM channel registers after reset is unknown.

In input capture mode (MSxB:MSxA = 0:0), reading the high byte of the TIM channel x registers (TCHxH) inhibits input captures until the low byte (TCHxL) is read.

In output compare mode (MSxB:MSxA  $\neq$  0:0), writing to the high byte of the TIM channel x registers (TCHxH) inhibits output compares until the low byte (TCHxL) is written.

Figure 14-9. TIM Channel Registers (TCH0H/L:TCH1H/L)

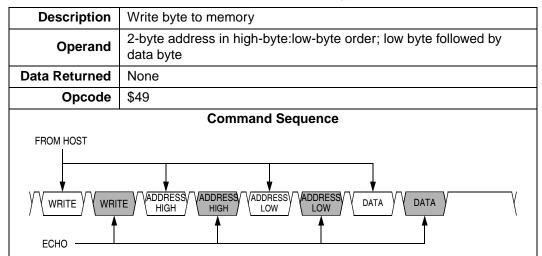

Development Support

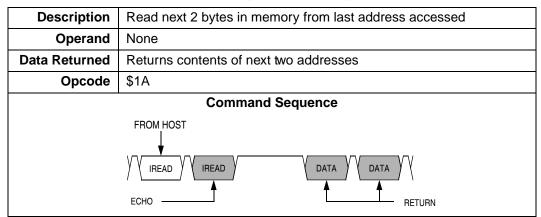

Table 15-5. IREAD (Indexed Read) Command

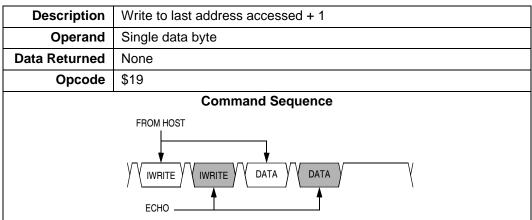

## Table 15-6. IWRITE (Indexed Write) Command

A sequence of IREAD or IWRITE commands can access a block of memory sequentially over the full 64-Kbyte memory map.

Development Support

## 15.3.2 Security

A security feature discourages unauthorized reading of FLASH locations while in monitor mode. The host can bypass the security feature at monitor mode entry by sending eight security bytes that match the bytes at locations \$FFF6–\$FFFD. Locations \$FFF6–\$FFFD contain user-defined data.

NOTE

Do not leave locations \$FFF6–\$FFFD blank. For security reasons, program locations \$FFF6–\$FFFD even if they are not used for vectors.

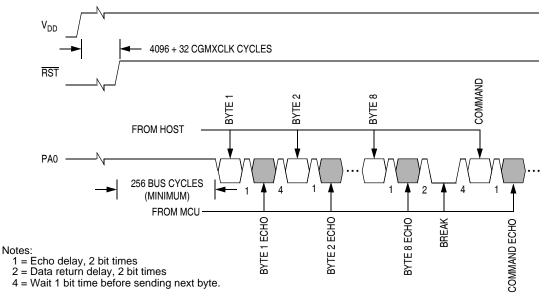

During monitor mode entry, the MCU waits after the power-on reset for the host to send the eight security bytes on pin PTA0. If the received bytes match those at locations \$FFF6-\$FFFD, the host bypasses the security feature and can read all FLASH locations and execute code from FLASH. Security remains bypassed until a power-on reset occurs. If the reset was not a power-on reset, security remains bypassed and security code entry is not required. See Figure 15-18.

Upon power-on reset, if the received bytes of the security code do not match the data at locations \$FFF6-\$FFFD, the host fails to bypass the security feature. The MCU remains in monitor mode, but reading a FLASH location returns an invalid value and trying to execute code from FLASH causes an illegal address reset. After receiving the eight security bytes from the host, the MCU transmits a break character, signifying that it is ready to receive a command.

## NOTE

The MCU does not transmit a break character until after the host sends the eight security bytes.

To determine whether the security code entered is correct, check to see if bit 6 of RAM address \$80 is set. If it is, then the correct security code has been entered and FLASH can be accessed.

If the security sequence fails, the device should be reset by a power-on reset and brought up in monitor mode to attempt another entry. After failing the security sequence, the FLASH module can also be mass erased by executing an erase routine that was downloaded into internal RAM. The mass erase operation clears the security code locations so that all eight security bytes become \$FF (blank).

Figure 15-18. Monitor Mode Entry Timing

**Electrical Specifications**

## **16.3 Functional Operating Range**

| Characteristic              | Symbol          | Value                                    | Unit | Temp.<br>Code |

|-----------------------------|-----------------|------------------------------------------|------|---------------|

| Operating temperature range | T <sub>A</sub>  | -40 to +125<br>-40 to +105<br>-40 to +85 | ۰C   | M<br>V<br>C   |

| Operating voltage range     | V <sub>DD</sub> | 2.7 to 5.5                               | V    | _             |

## **16.4 Thermal Characteristics**

| Characteristic                                                                                            | Symbol           | Value                                                                    | Unit |

|-----------------------------------------------------------------------------------------------------------|------------------|--------------------------------------------------------------------------|------|

| Thermal resistance<br>8-pin PDIP<br>8-pin SOIC<br>8-pin DFN<br>16-pin PDIP<br>16-pin SOIC<br>16-pin TSSOP | θ <sub>JA</sub>  | 105<br>142<br>173<br>76<br>90<br>133                                     | •C/W |

| I/O pin power dissipation                                                                                 | P <sub>I/O</sub> | User determined                                                          | W    |

| Power dissipation <sup>(1)</sup>                                                                          | P <sub>D</sub>   | $P_{D} = (I_{DD} \times V_{DD})$ $+ P_{I/O} = K/(T_{J} + 273 \bullet C)$ | W    |

| Constant <sup>(2)</sup>                                                                                   | к                | $P_{D} x (T_{A} + 273 \cdot C) + P_{D}^{2} x \theta_{JA}$                | W/•C |

| Average junction temperature                                                                              | TJ               | $T_A + (P_D \times \theta_{JA})$                                         | •C   |

| Maximum junction temperature                                                                              | T <sub>JM</sub>  | 150                                                                      | •C   |

1. Power dissipation is a function of temperature.

2. K constant unique to the device. K can be determined for a known  $T_A$  and measured  $P_D$ . With this value of K,  $P_D$  and  $T_J$  can be determined for any value of  $T_A$ .

**Electrical Specifications**

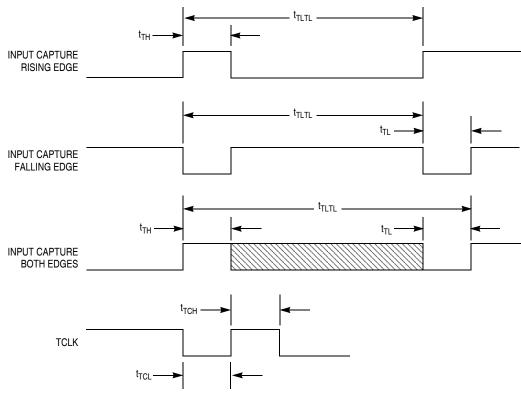

## **16.15 Timer Interface Module Characteristics**

| Characteristic                  | Symbol                              | Min                  | Max | Unit             |

|---------------------------------|-------------------------------------|----------------------|-----|------------------|

| Timer input capture pulse width | t <sub>TH,</sub> t <sub>TL</sub>    | 2                    | —   | t <sub>cyc</sub> |

| Timer input capture period      | t <sub>TLTL</sub>                   | Note <sup>(1)</sup>  | _   | t <sub>cyc</sub> |

| Timer input clock pulse width   | t <sub>TCL</sub> , t <sub>TCH</sub> | t <sub>cyc</sub> + 5 | _   | ns               |

1. The minimum period is the number of cycles it takes to execute the interrupt service routine plus 1  $t_{cyc}$ .

Figure 16-11. Timer Input Timing

|               |                                                                                                                                                       | MECHANICAL OUTLINES |         |      | INES    | DOCUMENT NO: 98ARL10557D |      |  |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------|------|---------|--------------------------|------|--|

| © FREESCALE S | FICESCALE<br>semiconcluctor<br>EMICONDUCTOR, INC. ALL RIGHTS RESERVED.                                                                                | DICTIONARY          |         |      |         | PAGE:                    | 1452 |  |

| DIRECTLY FROM | IONS ARE UNCONTROLLED EXCEPT WHEN ACCESSED<br>THE DOCUMENT CONTROL REPOSITORY. PRINTED<br>CONTROLLED EXCEPT WHEN STAMPED "CONTROLLED<br>COPY" IN RED. | DO NO               | T SCALE | THIS | DRAWING | REV:                     | A    |  |

NOTES:

- 1. ALL DIMENSIONS ARE IN MILLIMETERS.

- 2. INTERPRET DIMENSIONS AND TOLERANCES PER ASME Y14.5M-1994.

- 3. THE COMPLETE JEDEC DESIGNATOR FOR THIS PACKAGE IS: HP-VFDFP-N.

4. COPLANARITY APPLIES TO LEADS AND DIE ATTACH PAD.

| TITLE:THERMALLY ENHANCED DUAL                  | CASE NUMBER: 1452-01             |

|------------------------------------------------|----------------------------------|

| FLAT NO LEAD PACKAGE (DFN)                     | STANDARD: NON-JEDEC              |

| 8 TERMINAL, 0. 8 PITCH $(4 \times 4 \times 1)$ | PACKAGE CODE: 6165 SHEET: 4 OF 5 |

|                                                                                                                                                                                                   | MECHANICAL OUTLINES       | DOCUMENT NO: 98ASB42431B |     |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|--------------------------|-----|--|

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED.                                                                                                                                              | DICTIONARY                | PAGE:                    | 648 |  |

| ELECTRONIC VERSIONS ARE UNCONTROLLED EXCEPT WHEN ACCESSED<br>DIRECTLY FROM THE DOCUMENT CONTROL REPOSITORY, PRINTED<br>VERSIONS ARE UNCONTROLLED EXCEPT WHEN STAWPED "CONTROLLED<br>COPY" IN RED. | DO NOT SCALE THIS DRAWING | REV:                     | Т   |  |

## NOTES:

- 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

- 2. CONTROLLING DIMENSION: INCH.

- 3. DIMENSION TO CENTER OF LEADS WHEN FORMED PARALLEL.

- A DIMENSIONS DOES NOT INCLUDE MOLD FLASH.

- 5. ROUNDED CORNERS OPTIONAL.

- 6. 648-01 THRU -08 OBSOLETE, NEW STANDARD 648-09.

|            | MILLIMETERS                      |       | INCHES    |                     |     | MILLIMETERS         |        | INCHES |     |  |

|------------|----------------------------------|-------|-----------|---------------------|-----|---------------------|--------|--------|-----|--|

| DIM        | MIN                              | MAX   | MIN       | MAX                 | DIM | MIN                 | MAX    | MIN    | MAX |  |

| А          | 18.80                            | 19.55 | 0.740     | 0.770               |     |                     |        |        |     |  |

| В          | 6.35                             | 6.85  | 0.250     | 0,270               |     |                     |        |        |     |  |

| С          | 3.69                             | 4.44  | 0.145     | 0.175               |     |                     |        |        |     |  |

| D          | 0.39                             | 0.53  | 0.015     | 0.021               |     |                     |        |        |     |  |

| F          | 1.02                             | 1.77  | 0.040     | 0.070               |     |                     |        |        |     |  |

| G          | 2.54                             | BSC   | 0.100 BSC |                     |     |                     |        |        |     |  |

| Н          | 1.27                             | BSC   | 0.050 BSC |                     |     |                     |        |        |     |  |

| J          | 0.21                             | 0.38  | 0.008     | 0.015               |     |                     |        |        |     |  |

| K          | 2.80                             | 3.30  | 0.110     | 0.130               |     |                     |        |        |     |  |

| L          | 7.50                             | 7.74  | 0.295     | 0.305               |     |                     |        |        |     |  |

| М          | 0.                               | 10°   | 0.        | 10°                 |     |                     |        |        |     |  |

| S          | 0.51                             | 1.01  | 0.020     | 0.040               |     |                     |        |        |     |  |

| TITLE      | TITLE:                           |       |           |                     |     | CASE NUMBER: 648–08 |        |        |     |  |

| 16 LD PDIP |                                  |       |           | STANDARD: NON-JEDEC |     |                     |        |        |     |  |

|            | PACKAGE CODE: 0006 SHEET: 2 OF 4 |       |           |                     |     |                     | 2 OF 4 |        |     |  |