Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                |

| Core Processor             | HC08                                                                    |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 8MHz                                                                    |

| Connectivity               | -                                                                       |

| Peripherals                | LVD, POR, PWM                                                           |

| Number of I/O              | 13                                                                      |

| Program Memory Size        | 1.5KB (1.5K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 128 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                             |

| Data Converters            | -                                                                       |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 16-TSSOP (0.173", 4.40mm Width)                                         |

| Supplier Device Package    | 16-TSSOP                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc68hc908qy1cdt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Memory

#### **ERASE** — Erase Control Bit

This read/write bit configures the memory for erase operation. ERASE is interlocked with the PGM bit such that both bits cannot be equal to 1 or set to 1 at the same time.

- 1 = Erase operation selected

- 0 = Erase operation unselected

#### **PGM** — Program Control Bit

This read/write bit configures the memory for program operation. PGM is interlocked with the ERASE bit such that both bits cannot be equal to 1 or set to 1 at the same time.

- 1 = Program operation selected

- 0 = Program operation unselected

# 2.6.2 FLASH Page Erase Operation

Use the following procedure to erase a page of FLASH memory. A page consists of 64 consecutive bytes starting from addresses \$XX00, \$XX40, \$XX80, or \$XXC0. The 48-byte user interrupt vectors area also forms a page. Any FLASH memory page can be erased alone.

- 1. Set the ERASE bit and clear the MASS bit in the FLASH control register.

- 2. Read the FLASH block protect register.

- 3. Write any data to any FLASH location within the address range of the block to be erased.

- 4. Wait for a time,  $t_{NVS}$  (minimum 10  $\mu$ s).

- 5. Set the HVEN bit.

- 6. Wait for a time, t<sub>Erase</sub> (minimum 1 ms or 4 ms).

- 7. Clear the ERASE bit.

- 8. Wait for a time,  $t_{NVH}$  (minimum 5  $\mu$ s).

- 9. Clear the HVEN bit.

- 10. After time,  $t_{RCV}$  (typical 1  $\mu$ s), the memory can be accessed in read mode again.

#### NOTE

Programming and erasing of FLASH locations cannot be performed by code being executed from the FLASH memory. While these operations must be performed in the order as shown, but other unrelated operations may occur between the steps.

#### **CAUTION**

A page erase of the vector page will erase the internal oscillator trim values at \$FFC0 and \$FFC1.

In applications that require more than 1000 program/erase cycles, use the 4 ms page erase specification to get improved long-term reliability. Any application can use this 4 ms page erase specification. However, in applications where a FLASH location will be erased and reprogrammed less than 1000 times, and speed is important, use the 1 ms page erase specification to get a shorter cycle time.

# Chapter 3 Analog-to-Digital Converter (ADC)

# 3.1 Introduction

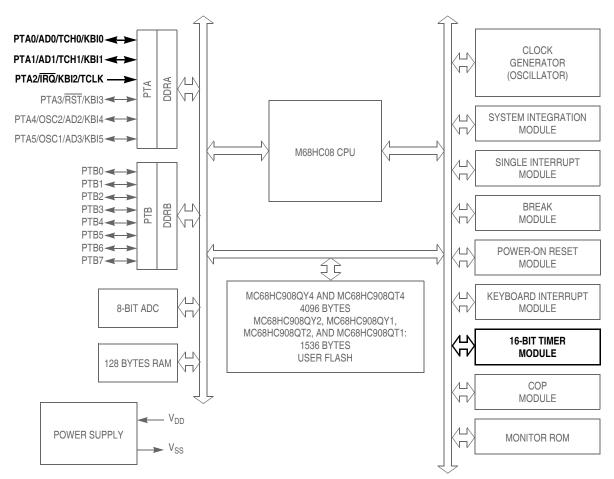

This section describes the analog-to-digital converter (ADC). The ADC is an 8-bit, 4-channel analog-to-digital converter. The ADC module is only available on the MC68HC908QY2, MC68HC908QT2, MC68HC908QY4, and MC68HC908QT4.

# 3.2 Features

Features of the ADC module include:

- · 4 channels with multiplexed input

- Linear successive approximation with monotonicity

- 8-bit resolution

- Single or continuous conversion

- Conversion complete flag or conversion complete interrupt

- Selectable ADC clock frequency

# 3.3 Functional Description

Four ADC channels are available for sampling external sources at pins PTA0, PTA1, PTA4, and PTA5. An analog multiplexer allows the single ADC converter to select one of the four ADC channels as an ADC voltage input (ADCVIN). ADCVIN is converted by the successive approximation register-based counters. The ADC resolution is eight bits. When the conversion is completed, ADC puts the result in the ADC data register and sets a flag or generates an interrupt.

Figure 3-2 shows a block diagram of the ADC.

# 3.3.1 ADC Port I/O Pins

PTA0, PTA1, PTA4, and PTA5 are general-purpose I/O pins that are shared with the ADC channels. The channel select bits (ADC status and control register (ADSCR), \$003C), define which ADC channel/port pin will be used as the input signal. The ADC overrides the port I/O logic by forcing that pin as input to the ADC. The remaining ADC channels/port pins are controlled by the port I/O logic and can be used as general-purpose I/O. Writes to the port register or data direction register (DDR) will not have any affect on the port pin that is selected by the ADC. Read of a port pin which is in use by the ADC will return a 0 if the corresponding DDR bit is at 0. If the DDR bit is at 1, the value in the port data latch is read.

#### **Configuration Register (CONFIG)**

# IRQPUD — IRQ Pin Pullup Control Bit

- 1 = Internal pullup is disconnected

- $0 = Internal pullup is connected between <math>\overline{IRQ}$  pin and  $V_{DD}$

# IRQEN — IRQ Pin Function Selection Bit

- 1 = Interrupt request function active in pin

- 0 = Interrupt request function inactive in pin

# OSCOPT1 and OSCOPT0 — Selection Bits for Oscillator Option

- (0, 0) Internal oscillator

- (0, 1) External oscillator

- (1, 0) External RC oscillator

- (1, 1) External XTAL oscillator

# **RSTEN** — RST Pin Function Selection

- 1 = Reset function active in pin

- 0 = Reset function inactive in pin

#### NOTE

The RSTEN bit is cleared by a power-on reset (POR) only. Other resets will leave this bit unaffected.

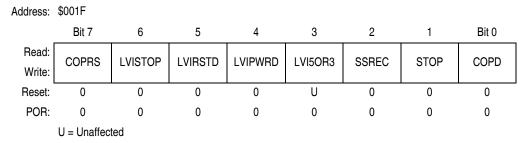

Figure 5-2. Configuration Register 1 (CONFIG1)

## COPRS (Out of STOP Mode) — COP Reset Period Selection Bit

- 1 = COP reset short cycle = 8176 × BUSCLKX4

- 0 = COP reset long cycle = 262,128 × BUSCLKX4

## COPRS (In STOP Mode) — Auto Wakeup Period Selection Bit

- 1 = Auto wakeup short cycle =  $512 \times INTRCOSC$

- 0 = Auto wakeup long cycle = 16,384 × INTRCOSC

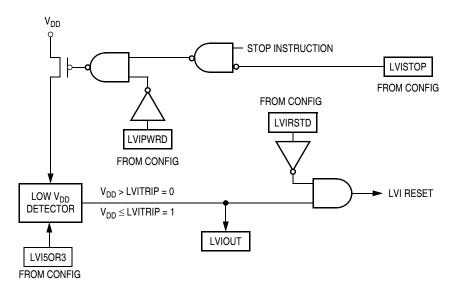

# LVISTOP — LVI Enable in Stop Mode Bit

When the LVIPWRD bit is clear, setting the LVISTOP bit enables the LVI to operate during stop mode. Reset clears LVISTOP.

- 1 = LVI enabled during stop mode

- 0 = LVI disabled during stop mode

#### LVIRSTD — LVI Reset Disable Bit

LVIRSTD disables the reset signal from the LVI module.

- 1 = LVI module resets disabled

- 0 = LVI module resets enabled

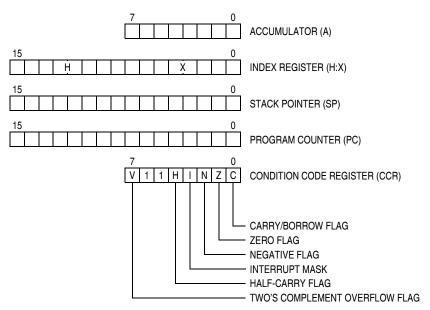

#### **Central Processor Unit (CPU)**

Figure 7-1. CPU Registers

## 7.3.1 Accumulator

The accumulator is a general-purpose 8-bit register. The CPU uses the accumulator to hold operands and the results of arithmetic/logic operations.

Figure 7-2. Accumulator (A)

# 7.3.2 Index Register

The 16-bit index register allows indexed addressing of a 64-Kbyte memory space. H is the upper byte of the index register, and X is the lower byte. H:X is the concatenated 16-bit index register.

In the indexed addressing modes, the CPU uses the contents of the index register to determine the conditional address of the operand.

The index register can serve also as a temporary data storage location.

Figure 7-3. Index Register (H:X)

MC68HC908QY/QT Family Data Sheet, Rev. 6

**Central Processor Unit (CPU)**

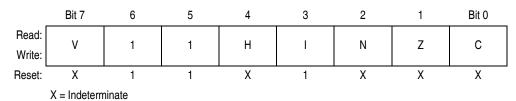

# 7.3.5 Condition Code Register

The 8-bit condition code register contains the interrupt mask and five flags that indicate the results of the instruction just executed. Bits 6 and 5 are set permanently to 1. The following paragraphs describe the functions of the condition code register.

Figure 7-6. Condition Code Register (CCR)

# V — Overflow Flag

The CPU sets the overflow flag when a two's complement overflow occurs. The signed branch instructions BGT, BGE, BLE, and BLT use the overflow flag.

- 1 = Overflow

- 0 = No overflow

# H — Half-Carry Flag

The CPU sets the half-carry flag when a carry occurs between accumulator bits 3 and 4 during an add-without-carry (ADD) or add-with-carry (ADC) operation. The half-carry flag is required for binary-coded decimal (BCD) arithmetic operations. The DAA instruction uses the states of the H and C flags to determine the appropriate correction factor.

- 1 = Carry between bits 3 and 4

- 0 = No carry between bits 3 and 4

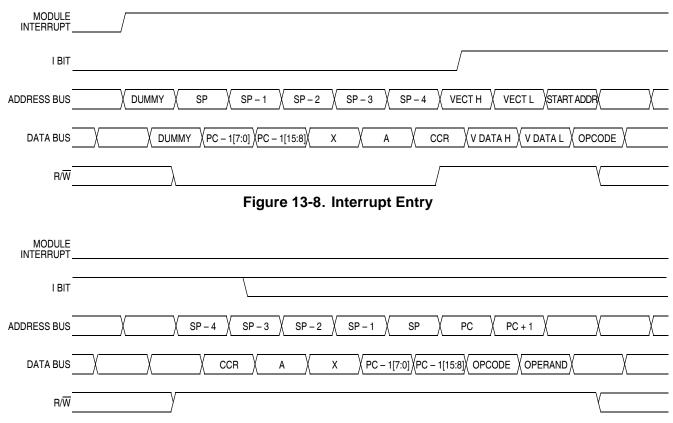

# I — Interrupt Mask

When the interrupt mask is set, all maskable CPU interrupts are disabled. CPU interrupts are enabled when the interrupt mask is cleared. When a CPU interrupt occurs, the interrupt mask is set automatically after the CPU registers are saved on the stack, but before the interrupt vector is fetched.

- 1 = Interrupts disabled

- 0 = Interrupts enabled

## **NOTE**

To maintain M6805 Family compatibility, the upper byte of the index register (H) is not stacked automatically. If the interrupt service routine modifies H, then the user must stack and unstack H using the PSHH and PULH instructions.

After the I bit is cleared, the highest-priority interrupt request is serviced first.

A return-from-interrupt (RTI) instruction pulls the CPU registers from the stack and restores the interrupt mask from the stack. After any reset, the interrupt mask is set and can be cleared only by the clear interrupt mask software instruction (CLI).

#### N — Negative Flag

The CPU sets the negative flag when an arithmetic operation, logic operation, or data manipulation produces a negative result, setting bit 7 of the result.

- 1 = Negative result

- 0 = Non-negative result

80

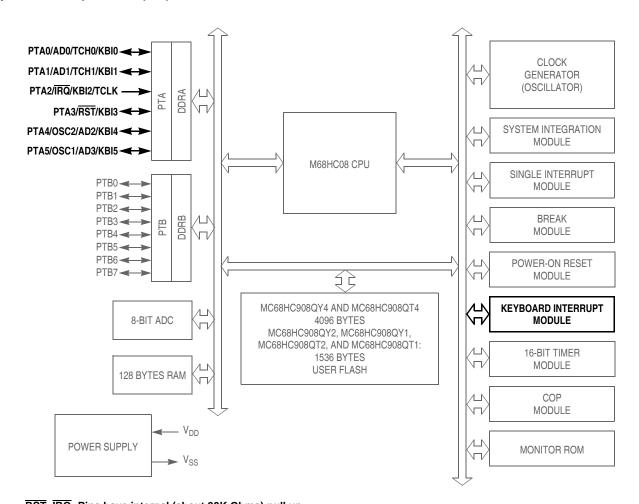

## **Keyboard Interrupt Module (KBI)**

RST, IRQ: Pins have internal (about 30K Ohms) pull up

PTA[0:5]: High current sink and source capability

PTA[0:5]: Pins have programmable keyboard interrupt and pull up

PTB[0:7]: Not available on 8-pin devices – MC68HC908QT1, MC68HC908QT2, and MC68HC908QT4 (see note in 12.1 Introduction)

ADC: Not available on the MC68HC908QY1 and MC68HC908QT1

Figure 9-1. Block Diagram Highlighting KBI Block and Pins

MC68HC908QY/QT Family Data Sheet, Rev. 6

# Chapter 10 Low-Voltage Inhibit (LVI)

# 10.1 Introduction

This section describes the low-voltage inhibit (LVI) module, which monitors the voltage on the  $V_{DD}$  pin and can force a reset when the  $V_{DD}$  voltage falls below the LVI trip falling voltage,  $V_{TRIPF}$ .

# 10.2 Features

Features of the LVI module include:

- Programmable LVI reset

- Programmable power consumption

- Selectable LVI trip voltage

- Programmable stop mode operation

# 10.3 Functional Description

Figure 10-1 shows the structure of the LVI module. LVISTOP, LVIPWRD, LVI5OR3, and LVIRSTD are user selectable options found in the configuration register (CONFIG1). See Chapter 5 Configuration Register (CONFIG).

Figure 10-1. LVI Module Block Diagram

The LVI is enabled out of reset. The LVI module contains a bandgap reference circuit and comparator. Clearing the LVI power disable bit, LVIPWRD, enables the LVI to monitor  $V_{DD}$  voltage. Clearing the LVI reset disable bit, LVIRSTD, enables the LVI module to generate a reset when  $V_{DD}$  falls below a voltage,

Oscillator Module (OSC)

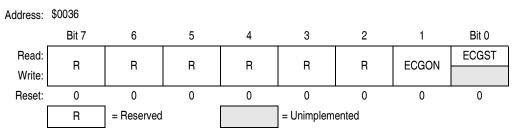

# 11.8.1 Oscillator Status Register

The oscillator status register (OSCSTAT) contains the bits for switching from internal to external clock sources.

Figure 11-4. Oscillator Status Register (OSCSTAT)

# **ECGON** — External Clock Generator On Bit

This read/write bit enables external clock generator, so that the switching process can be initiated. This bit is forced low during reset. This bit is ignored in monitor mode with the internal oscillator bypassed, PTM or CTM mode.

- 1 = External clock generator enabled

- 0 = External clock generator disabled

## **ECGST** — External Clock Status Bit

This read-only bit indicates whether or not an external clock source is engaged to drive the system clock.

- 1 = An external clock source engaged

- 0 = An external clock source disengaged

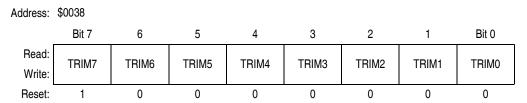

# 11.8.2 Oscillator Trim Register (OSCTRIM)

Figure 11-5. Oscillator Trim Register (OSCTRIM)

#### TRIM7-TRIM0 — Internal Oscillator Trim Factor Bits

These read/write bits change the size of the internal capacitor used by the internal oscillator. By measuring the period of the internal clock and adjusting this factor accordingly, the frequency of the internal clock can be fine tuned. Increasing (decreasing) this factor by one increases (decreases) the period by approximately 0.2% of the untrimmed period (the period for TRIM = \$80). The trimmed frequency is guaranteed not to vary by more than  $\pm 5\%$  over the full specified range of temperature and voltage. The reset value is \$80, which sets the frequency to 12.8 MHz (3.2 MHz bus speed)  $\pm 25\%$ .

Applications using the internal oscillator should copy the internal oscillator trim value at location \$FFC0 or \$FFC1 into this register to trim the clock source.

Input/Output Ports (PORTS)

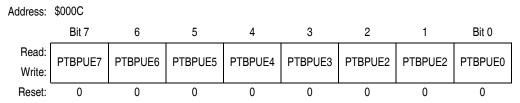

# 12.3.3 Port B Input Pullup Enable Register

The port B input pullup enable register (PTBPUE) contains a software configurable pullup device for each of the eight port B pins. Each bit is individually configurable and requires the corresponding data direction register, DDRBx, be configured as input. Each pullup device is automatically and dynamically disabled when its corresponding DDRBx bit is configured as output.

Figure 12-8. Port B Input Pullup Enable Register (PTBPUE)

# PTBPUE[7:0] — Port B Input Pullup Enable Bits

These read/write bits are software programmable to enable pullup devices on port B pins

- 1 = Corresponding port B pin configured to have internal pull if its DDRB bit is set to 0

- 0 = Pullup device is disconnected on the corresponding port B pin regardless of the state of its DDRB bit.

Table 12-3 summarizes the operation of the port B pins.

Table 12-3. Port B Pin Functions

| PTBPUE | DDRB | DRB PTB I/O Pin Accesses to DDRB |                                       | Accesses to PTB |           |                          |

|--------|------|----------------------------------|---------------------------------------|-----------------|-----------|--------------------------|

| Bit    | Bit  | Bit                              | Mode                                  | Read/Write      | Read      | Write                    |

| 1      | 0    | X <sup>(1)</sup>                 | Input, V <sub>DD</sub> <sup>(2)</sup> | DDRB7-DDRB0     | Pin       | PTB7-PTB0 <sup>(3)</sup> |

| 0      | 0    | Х                                | Input, Hi-Z <sup>(4)</sup>            | DDRB7-DDRB0     | Pin       | PTB7-PTB0 <sup>(3)</sup> |

| Х      | 1    | Х                                | Output                                | DDRB7-DDRB0     | PTB7-PTB0 | PTB7-PTB0                |

- 1. X = don't care

- 2. I/O pin pulled to  $V_{\mbox{\scriptsize DD}}$  by internal pullup.

- 3. Writing affects data register, but does not affect input.

- 4. Hi-Z = high impedance

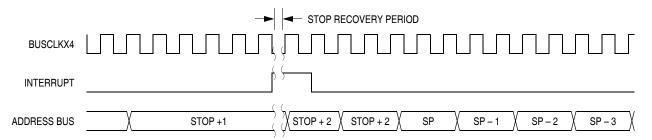

Figure 13-9. Interrupt Recovery

# 13.6.1.1 Hardware Interrupts

A hardware interrupt does not stop the current instruction. Processing of a hardware interrupt begins after completion of the current instruction. When the current instruction is complete, the SIM checks all pending hardware interrupts. If interrupts are not masked (I bit clear in the condition code register), and if the corresponding interrupt enable bit is set, the SIM proceeds with interrupt processing; otherwise, the next instruction is fetched and executed.

If more than one interrupt is pending at the end of an instruction execution, the highest priority interrupt is serviced first. Figure 13-10 demonstrates what happens when two interrupts are pending. If an interrupt is pending upon exit from the original interrupt service routine, the pending interrupt is serviced before the LDA instruction is executed.

The LDA opcode is prefetched by both the INT1 and INT2 return-from-interrupt (RTI) instructions. However, in the case of the INT1 RTI prefetch, this is a redundant operation.

#### NOTE

To maintain compatibility with the M6805 Family, the H register is not pushed on the stack during interrupt entry. If the interrupt service routine modifies the H register or uses the indexed addressing mode, software should save the H register and then restore it prior to exiting the routine.

A module that is active during wait mode can wake up the CPU with an interrupt if the interrupt is enabled. Stacking for the interrupt begins one cycle after the WAIT instruction during which the interrupt occurred. In wait mode, the CPU clocks are inactive. Refer to the wait mode subsection of each module to see if the module is active or inactive in wait mode. Some modules can be programmed to be active in wait mode.

Wait mode can also be exited by a reset (or break in emulation mode). A break interrupt during wait mode sets the SIM break stop/wait bit, SBSW, in the break status register (BSR). If the COP disable bit, COPD, in the configuration register is 0, then the computer operating properly module (COP) is enabled and remains active in wait mode.

Figure 13-15 and Figure 13-16 show the timing for wait recovery.

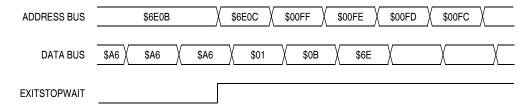

NOTE: EXITSTOPWAIT = RST pin OR CPU interrupt OR break interrupt

Figure 13-15. Wait Recovery from Interrupt

Figure 13-16. Wait Recovery from Internal Reset

# **13.7.2 Stop Mode**

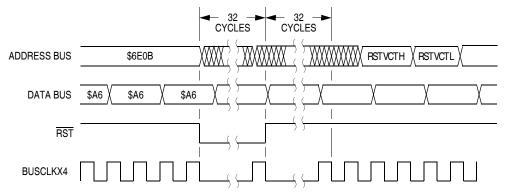

In stop mode, the SIM counter is reset and the system clocks are disabled. An interrupt request from a module can cause an exit from stop mode. Stacking for interrupts begins after the selected stop recovery time has elapsed. Reset or break also causes an exit from stop mode.

The SIM disables the oscillator signals (BUSCLKX2 and BUSCLKX4) in stop mode, stopping the CPU and peripherals. Stop recovery time is selectable using the SSREC bit in the configuration register 1 (CONFIG1). If SSREC is set, stop recovery is reduced from the normal delay of 4096 BUSCLKX4 cycles down to 32. This is ideal for the internal oscillator, RC oscillator, and external oscillator options which do not require long start-up times from stop mode.

#### NOTE

External crystal applications should use the full stop recovery time by clearing the SSREC bit.

MC68HC908QY/QT Family Data Sheet, Rev. 6

#### **System Integration Module (SIM)**

The SIM counter is held in reset from the execution of the STOP instruction until the beginning of stop recovery. It is then used to time the recovery period. Figure 13-17 shows stop mode entry timing and Figure 13-18 shows the stop mode recovery time from interrupt or break.

#### NOTE

To minimize stop current, all pins configured as inputs should be driven to a logic 1 or logic 0.

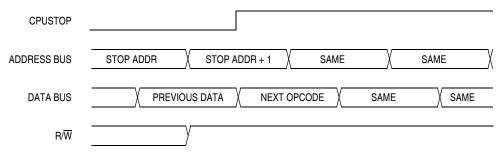

NOTE: Previous data can be operand data or the STOP opcode, depending on the last instruction.

Figure 13-17. Stop Mode Entry Timing

Figure 13-18. Stop Mode Recovery from Interrupt

# 13.8 SIM Registers

The SIM has three memory mapped registers. Table 13-4 shows the mapping of these registers.

Table 13-4. SIM Registers

| Address | Register | Access Mode |

|---------|----------|-------------|

| \$FE00  | BSR      | User        |

| \$FE01  | SRSR     | User        |

| \$FE03  | BFCR     | User        |

## **Timer Interface Module (TIM)**

RST, IRQ: Pins have internal (about 30K Ohms) pull up

PTA[0:5]: High current sink and source capability

PTA[0:5]: Pins have programmable keyboard interrupt and pull up

PTB[0:7]: Not available on 8-pin devices – MC68HC908QT1, MC68HC908QT2, and MC68HC908QT4 (see note in 12.1 Introduction)

ADC: Not available on the MC68HC908QY1 and MC68HC908QT1

Figure 14-1. Block Diagram Highlighting TIM Block and Pins

#### **Timer Interface Module (TIM)**

#### TRST — TIM Reset Bit

Setting this write-only bit resets the TIM counter and the TIM prescaler. Setting TRST has no effect on any other registers. Counting resumes from \$0000. TRST is cleared automatically after the TIM counter is reset and always reads as a 0. Reset clears the TRST bit.

- 1 = Prescaler and TIM counter cleared

- 0 = No effect

#### NOTE

Setting the TSTOP and TRST bits simultaneously stops the TIM counter at a value of \$0000.

# PS[2:0] — Prescaler Select Bits

These read/write bits select either the PTA2/TCLK pin or one of the seven prescaler outputs as the input to the TIM counter as Table 14-2 shows. Reset clears the PS[2:0] bits.

| PS2 | PS1 | PS0 | TIM Clock Source        |  |  |  |

|-----|-----|-----|-------------------------|--|--|--|

| 0   | 0   | 0   | Internal bus clock ÷ 1  |  |  |  |

| 0   | 0   | 1   | Internal bus clock ÷ 2  |  |  |  |

| 0   | 1   | 0   | Internal bus clock ÷ 4  |  |  |  |

| 0   | 1   | 1   | Internal bus clock ÷ 8  |  |  |  |

| 1   | 0   | 0   | Internal bus clock ÷ 16 |  |  |  |

| 1   | 0   | 1   | Internal bus clock ÷ 32 |  |  |  |

| 1   | 1   | 0   | Internal bus clock ÷ 64 |  |  |  |

| 1   | 1   | 1   | PTA2/TCLK               |  |  |  |

**Table 14-2. Prescaler Selection**

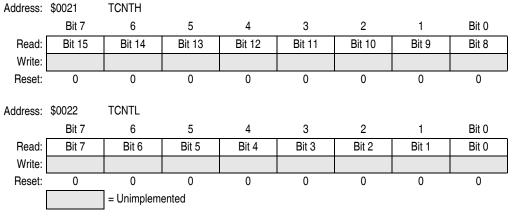

# 14.9.2 TIM Counter Registers

The two read-only TIM counter registers contain the high and low bytes of the value in the TIM counter. Reading the high byte (TCNTH) latches the contents of the low byte (TCNTL) into a buffer. Subsequent reads of TCNTH do not affect the latched TCNTL value until TCNTL is read. Reset clears the TIM counter registers. Setting the TIM reset bit (TRST) also clears the TIM counter registers.

#### NOTE

If you read TCNTH during a break interrupt, be sure to unlatch TCNTL by reading TCNTL before exiting the break interrupt. Otherwise, TCNTL retains the value latched during the break.

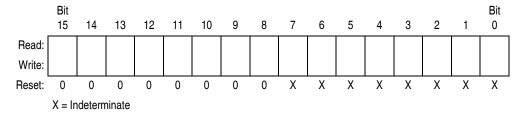

Figure 14-5. TIM Counter Registers (TCNTH:TCNTL)

MC68HC908QY/QT Family Data Sheet, Rev. 6

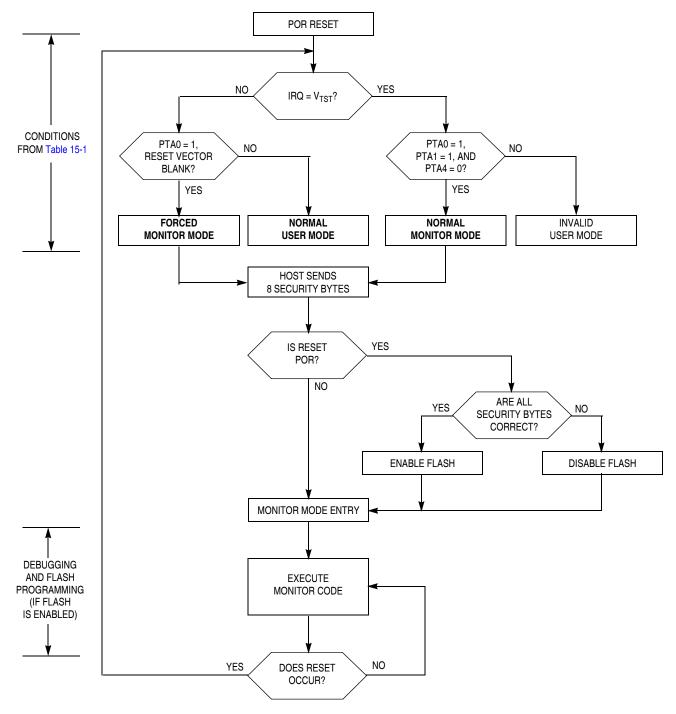

# 15.3.1 Functional Description

Figure 15-9 shows a simplified diagram of monitor mode entry.

The monitor module receives and executes commands from a host computer. Figure 15-10, Figure 15-11, and Figure 15-12 show example circuits used to enter monitor mode and communicate with a host computer via a standard RS-232 interface.

Figure 15-9. Simplified Monitor Mode Entry Flowchart

MC68HC908QY/QT Family Data Sheet, Rev. 6

#### **Development Support**

**Table 15-1. Monitor Mode Signal Requirements and Options**

| Mode IRQ                       |                         | RST        | Reset<br>Vector   | Serial<br>Communi-<br>cation | Mode<br>Selection |              | СОР      | Communication<br>Speed |                      |              | Comments                        |  |

|--------------------------------|-------------------------|------------|-------------------|------------------------------|-------------------|--------------|----------|------------------------|----------------------|--------------|---------------------------------|--|

|                                | (PTA2)                  | (PTA3)     | Vector            | PTA0                         | PTA0 PTA1 PTA4    |              |          | External Clock         | Bus<br>Frequency     | Baud<br>Rate |                                 |  |

| Normal<br>Monitor              | V <sub>TST</sub>        | $V_{DD}$   | Х                 | 1                            | 1                 | 0            | Disabled | 9.8304<br>MHz          | 2.4576<br>MHz        | 9600         | Provide external clock at OSC1. |  |

| Forced                         | V <sub>DD</sub>         | Х          | \$FFFF<br>(blank) | 1                            | Х                 | Х            | Disabled | 9.8304<br>MHz          | 2.4576<br>MHz        | 9600         | Provide external clock at OSC1. |  |

| Monitor                        | V <sub>SS</sub>         | Х          | \$FFFF<br>(blank) | 1                            | Х                 | Х            | Disabled | Х                      | 3.2 MHz<br>(Trimmed) | 9600         | Internal clock is active.       |  |

| User                           | Х                       | Х          | Not<br>\$FFFF     | Х                            | Х                 | Х            | Enabled  | Х                      | Х                    | Х            |                                 |  |

| MON08<br>Function<br>[Pin No.] | V <sub>TST</sub><br>[6] | RST<br>[4] | _                 | COM<br>[8]                   | MOD0<br>[12]      | MOD1<br>[10] | _        | OSC1<br>[13]           | _                    | _            |                                 |  |

- 1. PTA0 must have a pullup resistor to V<sub>DD</sub> in monitor mode.

- 2. Communication speed in the table is an example to obtain a baud rate of 9600. Baud rate using external oscillator is bus frequency / 256 and baud rate using internal oscillator is bus frequency / 335.

- 3. External clock is a 9.8304 MHz oscillator on OSC1.

- 4. X = don't care

- 5. MON08 pin refers to P&E Microcomputer Systems' MON08-Cyclone 2 by 8-pin connector.

| ۷D |

|----|

| ٧D |

| ST |

| Q  |

| AC |

| Α4 |

| Α1 |

| )  |

| )  |

|    |

The rising edge of the internal  $\overline{RST}$  signal latches the monitor mode. Once monitor mode is latched, the values on PTA1 and PTA4 pins can be changed.

Once out of reset, the MCU waits for the host to send eight security bytes (see 15.3.2 Security). After the security bytes, the MCU sends a break signal (10 consecutive logic 0s) to the host, indicating that it is ready to receive a command.

#### 15.3.1.1 Normal Monitor Mode

$\overline{RST}$  and OSC1 functions will be active on the PTA3 and PTA5 pins respectively as long as  $V_{TST}$  is applied to the  $\overline{IRQ}$  pin. If the  $\overline{IRQ}$  pin is lowered (no longer  $V_{TST}$ ) then the chip will still be operating in monitor mode, but the pin functions will be determined by the settings in the configuration registers (see Chapter 5 Configuration Register (CONFIG)) when  $V_{TST}$  was lowered. With  $V_{TST}$  lowered, the BIH and BIL instructions will read the  $\overline{IRQ}$  pin state only if IRQEN is set in the CONFIG2 register.

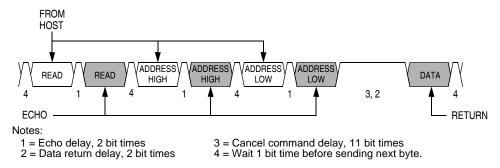

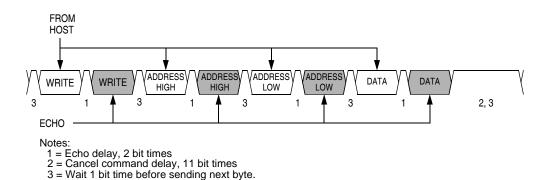

The monitor ROM firmware echoes each received byte back to the PTA0 pin for error checking. An 11-bit delay at the end of each command allows the host to send a break character to cancel the command. A delay of two bit times occurs before each echo and before READ, IREAD, or READSP data is returned. The data returned by a read command appears after the echo of the last byte of the command.

#### NOTE

Wait one bit time after each echo before sending the next byte.

Figure 15-15. Read Transaction

Figure 15-16. Write Transaction

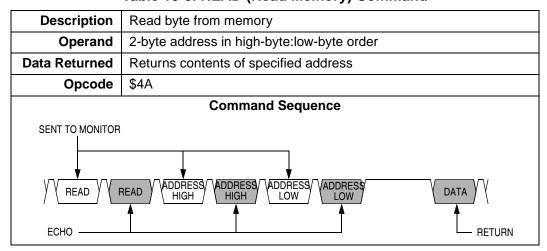

A brief description of each monitor mode command is given in Table 15-3 through Table 15-8.

Table 15-3. READ (Read Memory) Command

MC68HC908QY/QT Family Data Sheet, Rev. 6

# **Electrical Specifications**

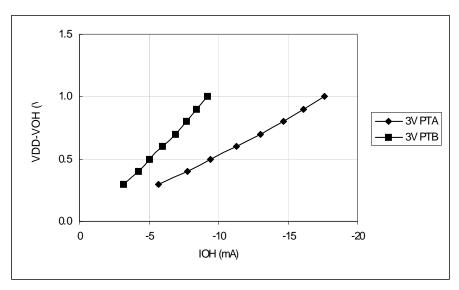

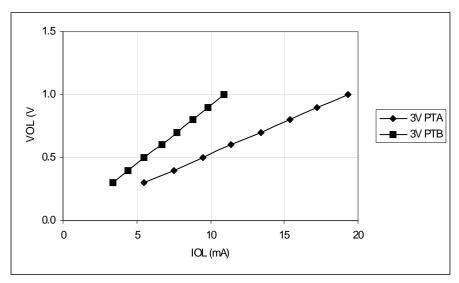

# **16.10 Typical 3.0-V Output Drive Characteristics**

Figure 16-5. Typical 3-Volt Output High Voltage versus Output High Current (25•C)

Figure 16-6. Typical 3-Volt Output Low Voltage versus Output Low Current (25•C)

# **16.16 Memory Characteristics**

| Characteristic                                | Symbol                           | Min        | Тур    | Max        | Unit   |

|-----------------------------------------------|----------------------------------|------------|--------|------------|--------|

| RAM data retention voltage                    | V <sub>RDR</sub>                 | 1.3        | _      | _          | V      |

| FLASH program bus clock frequency             | _                                | 1          | _      |            | MHz    |

| FLASH read bus clock frequency                | f <sub>Read</sub> <sup>(1)</sup> | 0          | _      | 8 M        | Hz     |

| FLASH page erase time <1 k cycles >1 k cycles | t <sub>Erase</sub>               | 0.9<br>3.6 | 1<br>4 | 1.1<br>5.5 | ms     |

| FLASH mass erase time                         | t <sub>MErase</sub>              | 4          | _      | _          | ms     |

| FLASH PGM/ERASE to HVEN setup time            | t <sub>NVS</sub>                 | 10         | _      | _          | μS     |

| FLASH high-voltage hold time                  | t <sub>NVH</sub>                 | 5          | _      | _          | μS     |

| FLASH high-voltage hold time (mass erase)     | t <sub>NVHL</sub>                | 100        | _      | _          | μS     |

| FLASH program hold time                       | t <sub>PGS</sub>                 | 5          | _      | _          | μS     |

| FLASH program time                            | t <sub>PROG</sub>                | 30         | _      | 40         | μS     |

| FLASH return to read time                     | t <sub>RCV</sub> <sup>(2)</sup>  | 1          | _      | _          | μS     |

| FLASH cumulative program HV period            | t <sub>HV</sub> <sup>(3)</sup>   | _          | _      | 4          | ms     |

| FLASH endurance <sup>(4)</sup>                | _                                | 10 k       | 100 k  | _          | Cycles |

| FLASH data retention time <sup>(5)</sup>      | _                                | 15         | 100    | _          | Years  |

- 1.  $f_{\mbox{\scriptsize Read}}$  is defined as the frequency range for which the FLASH memory can be read.

- 2. t<sub>RCV</sub> is defined as the time it needs before the FLASH can be read after turning off the high voltage charge pump, by clearing HVEN to 0.

- 3.  $t_{HV}$  is defined as the cumulative high voltage programming time to the same row before next erase.  $t_{HV}$  must satisfy this condition:  $t_{NVS} + t_{NVH} + t_{PGS} + (t_{PROG} \times 32) \le t_{HV}$  maximum.

- 4. Typical endurance was evaluated for this product family. For additional information on how Freescale defines *Typical Endurance*, please refer to Engineering Bulletin EB619.

- 5. Typical data retention values are based on intrinsic capability of the technology measured at high temperature and de-rated to 25•C using the Arrhenius equation. For additional information on how Freescale defines *Typical Data Retention*, please refer to Engineering Bulletin EB618.

# MECHANICAL OUTLINES DICTIONARY

DO NOT SCALE THIS DRAWING

DOCUMENT NO: 98ASB42567B 751G

PAGE:

REV: Ε

NOTES:

DIMENSIONS ARE IN MILLIMETERS.

DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

DATUMS A AND B TO BE DETERMINED AT THE PLANE WHERE THE BOTTOM OF THE LEADS EXIT THE PLASTIC BODY.

THIS DIMENSION DOES NOT INCLUDE MOLD FLASH, PROTRUSION OR GATE BURRS. MOLD FLASH, PROTRUSION OR GATE BURRS SHALL NOT EXCEED 0.15 MM PER SIDE. THIS DIMENSION IS DETERMINED AT THE PLANE WHERE THE BOTTOM OF THE LEADS EXIT THE PLASTIC BODY.

THIS DIMENSION DOES NOT INCLUDE INTER-LEAD FLASH OR PROTRUSIONS. INTER-LEAD FLASH AND PROTRUSIONS SHALL NOT EXCEED 0.25 MM PER SIDE. THIS DIMENSION IS DETERMINED AT THE PLANE WHERE THE BOTTOM OF THE LEADS EXIT THE PLASTIC BODY.

/6\ THIS DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL NOT CAUSE THE LEAD WIDTH TO EXCEED 0.62 mm.

TITLE:

16LD SOIC W/B, 1.27 PITCH, CASE OUTLINE

CASE NUMBER: 751G-05

STANDARD: JEDEC MS-013AA

PACKAGE CODE: 2003 SHEET: 2 OF 3