Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                |

| Core Processor             | HC08                                                                    |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 8MHz                                                                    |

| Connectivity               | -                                                                       |

| Peripherals                | LVD, POR, PWM                                                           |

| Number of I/O              | 13                                                                      |

| Program Memory Size        | 1.5KB (1.5K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 128 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                             |

| Data Converters            | A/D 4x8b                                                                |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 16-TSSOP (0.173", 4.40mm Width)                                         |

| Supplier Device Package    | 16-TSSOP                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc68hc908qy2cdt |

## **Revision History**

The following revision history table summarizes changes contained in this document. For your convenience, the page number designators have been linked to the appropriate location.

# **Revision History (Sheet 1 of 3)**

| Date               | Revision Description |                                                                                                                                                                        |     |  |  |

|--------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|--|

| September,<br>2002 | N/A                  | Initial release                                                                                                                                                        |     |  |  |

|                    |                      | 1.2 Features — Added 8-pin dual flat no lead (DFN) packages to features list.                                                                                          | 19  |  |  |

|                    |                      | Figure 1-2. MCU Pin Assignments — Figure updated to include DFN packages.                                                                                              | 21  |  |  |

|                    |                      | Figure 2-1. Memory Map — Clarified illegal address and unimplemented memory.                                                                                           | 27  |  |  |

|                    |                      | Figure 2-2. Control, Status, and Data Registers — Corrected bit definitions for Port A Data Register (PTA) and Data Direction Register A (DDRA).                       | 27  |  |  |

|                    |                      | Table 13-3. Interrupt Sources — Corrected vector addresses for keyboard interrupt and ADC conversion complete interrupt.                                               | 118 |  |  |

|                    |                      | Chapter 13 System Integration Module (SIM) — Removed reference to break status register as it is duplicated in break module.                                           | 113 |  |  |

|                    | 0.1                  | 11.3.1 Internal Oscillator and 11.3.1.1 Internal Oscillator Trimming — Clarified oscillator trim option ordering information and what to expect with untrimmed device. | 92  |  |  |

|                    |                      | Figure 11-5. Oscillator Trim Register (OSCTRIM) — Bit 1 designation corrected.                                                                                         | 98  |  |  |

| December,          |                      | Figure 15-13. Monitor Mode Circuit (Internal Clock, No High Voltage) — Diagram updated for clarity.                                                                    | 150 |  |  |

| 2002               |                      | Figure 12-1. I/O Port Register Summary — Corrected bit definitions for PTA7, DDRA7, and DDRA6.                                                                         | 99  |  |  |

|                    |                      | Figure 12-2. Port A Data Register (PTA) — Corrected bit definition for PTA7.                                                                                           | 100 |  |  |

|                    |                      | Figure 12-3. Data Direction Register A (DDRA) — Corrected bit definitions for DDRA7 and DDRA6.                                                                         | 101 |  |  |

|                    |                      | Figure 12-6. Port B Data Register (PTB) — Corrected bit definition for PTB1                                                                                            | 103 |  |  |

|                    |                      | Chapter 9 Keyboard Interrupt Module (KBI) — Section reworked after deletion of auto wakeup for clarity.                                                                | 83  |  |  |

|                    |                      | Chapter 4 Auto Wakeup Module (AWU) — New section added for clarity.                                                                                                    | 49  |  |  |

|                    |                      | Figure 10-1. LVI Module Block Diagram — Corrected LVI stop representation.                                                                                             | 87  |  |  |

|                    |                      | Chapter 16 Electrical Specifications — Extensive changes made to electrical specifications.                                                                            | 169 |  |  |

|                    |                      | 17.5 8-Pin Dual Flat No Lead (DFN) Package (Case #1452) — Added case outline drawing for DFN package.                                                                  | 177 |  |  |

|                    |                      | Chapter 17 Ordering Information and Mechanical Specifications — Added ordering information for DFN package.                                                            | 185 |  |  |

| January,<br>2003   | 0.2                  | 4.2 Features — Corrected third bulleted item.                                                                                                                          | 49  |  |  |

| T-1- | I    |      |      |      |

|------|------|------|------|------|

| ıan  | ie o | T L. | Onte | ents |

| 13.8    | SIM Registers                                  | 116 |

|---------|------------------------------------------------|-----|

| 13.8.1  | SIM Reset Status Register                      | 117 |

| 13.8.2  | Break Flag Control Register                    | 118 |

|         | Chapter 14                                     |     |

|         | Timer Interface Module (TIM)                   |     |

| 14.1    | Introduction                                   | 119 |

| 14.2    | Features                                       | 119 |

| 14.3    | Pin Name Conventions                           | 119 |

| 14.4    | Functional Description                         |     |

| 14.4.1  | TIM Counter Prescaler                          |     |

| 14.4.2  | Input Capture                                  | 122 |

| 14.4.3  | Output Compare                                 | 122 |

| 14.4.3. | 1 Unbuffered Output Compare                    | 122 |

| 14.4.3. | 2 Buffered Output Compare                      | 122 |

| 14.4.4  | Pulse Width Modulation (PWM)                   | 123 |

| 14.4.4. | 1 Unbuffered PWM Signal Generation             | 124 |

| 14.4.4. |                                                | 124 |

| 14.4.4. | 3 PWM Initialization                           | 125 |

| 14.5    | Interrupts                                     | 125 |

| 14.6    | Wait Mode                                      | 126 |

| 14.7    | TIM During Break Interrupts                    | 126 |

| 14.8    | Input/Output Signals                           |     |

| 14.8.1  | TIM Clock Pin (PTA2/TCLK)                      |     |

| 14.8.2  | TIM Channel I/O Pins (PTA0/TCH0 and PTA1/TCH1) |     |

| 14.9    | Input/Output Registers                         |     |

| 14.9.1  | TIM Status and Control Register                |     |

| 14.9.2  | TIM Counter Registers                          |     |

| 14.9.3  | TIM Counter Modulo Registers                   |     |

| 14.9.4  | TIM Channel Status and Control Registers       |     |

| 14.9.5  | TIM Channel Registers                          |     |

|         | Chantar 45                                     |     |

|         | Chapter 15 Development Support                 |     |

| 15.1    | Introduction                                   | 133 |

| 15.2    | Break Module (BRK)                             |     |

| 15.2.1  | Functional Description                         |     |

| 15.2.1. | ·                                              |     |

| 15.2.1. |                                                |     |

| 15.2.1. |                                                |     |

| 15.2.2  | Break Module Registers                         |     |

| 15.2.2. |                                                |     |

| 15.2.2. |                                                |     |

| 15.2.2. |                                                |     |

| 15.2.2. |                                                |     |

| 15.2.2. | 5 Break Flag Control Register                  | 138 |

| 15.2.3  | Low-Power Modes                                | 138 |

MC68HC908QY/QT Family Data Sheet, Rev. 6

## **General Description**

## 1.5 Pin Functions

Table 1-2 provides a description of the pin functions.

**Table 1-2. Pin Functions**

| Pin<br>Name             | Description                                                                                                      | Input/Output     |

|-------------------------|------------------------------------------------------------------------------------------------------------------|------------------|

| $V_{DD}$                | Power supply                                                                                                     | Power            |

| V <sub>SS</sub>         | Power supply ground                                                                                              | Power            |

|                         | PTA0 — General purpose I/O port                                                                                  | Input/Output     |

| PTA0                    | AD0 — A/D channel 0 input                                                                                        | Input            |

| PIAU                    | TCH0 — Timer Channel 0 I/O                                                                                       | Input/Output     |

|                         | KBI0 — Keyboard interrupt input 0                                                                                | Input            |

|                         | PTA1 — General purpose I/O port                                                                                  | Input/Output     |

| PTA1                    | AD1 — A/D channel 1 input                                                                                        | Input            |

| FIAI                    | TCH1 — Timer Channel 1 I/O                                                                                       | Input/Output     |

|                         | KBI1 — Keyboard interrupt input 1                                                                                | Input            |

|                         | PTA2 — General purpose input-only port                                                                           | Input            |

| PTA2                    | IRQ — External interrupt with programmable pullup and Schmitt trigger input                                      | Input            |

| FIAZ                    | KBI2 — Keyboard interrupt input 2                                                                                | Input            |

|                         | TCLK — Timer clock input                                                                                         | Input            |

|                         | PTA3 — General purpose I/O port                                                                                  | Input/Output     |

| PTA3                    | RST — Reset input, active low with internal pullup and Schmitt trigger                                           | Input            |

|                         | KBI3 — Keyboard interrupt input 3                                                                                | Input            |

|                         | PTA4 — General purpose I/O port                                                                                  | Input/Output     |

| PTA4                    | OSC2 —XTAL oscillator output (XTAL option only) RC or internal oscillator output (OSC2EN = 1 in PTAPUE register) | Output<br>Output |

|                         | AD2 — A/D channel 2 input                                                                                        | Input            |

|                         | KBI4 — Keyboard interrupt input 4                                                                                | Input            |

|                         | PTA5 — General purpose I/O port                                                                                  | Input/Output     |

| PTA5                    | OSC1 — XTAL, RC, or external oscillator input                                                                    | Input            |

| r IAO                   | AD3 — A/D channel 3 input                                                                                        | Input            |

|                         | KBI5 — Keyboard interrupt input 5                                                                                | Input            |

| PTB[0:7] <sup>(1)</sup> | 8 general-purpose I/O ports                                                                                      | Input/Output     |

|                         |                                                                                                                  |                  |

<sup>1.</sup> The PTB pins are not available on the 8-pin packages (see note in 12.1 Introduction).

MC68HC908QY/QT Family Data Sheet, Rev. 6

# **1.6 Pin Function Priority**

Table 1-3 is meant to resolve the priority if multiple functions are enabled on a single pin.

## NOTE

Upon reset all pins come up as input ports regardless of the priority table.

**Table 1-3. Function Priority in Shared Pins**

| Pin Name | Highest-to-Lowest Priority Sequence                                                             |

|----------|-------------------------------------------------------------------------------------------------|

| PTA0     | $AD0 \rightarrow TCH0 \rightarrow KBI0 \rightarrow PTA0$                                        |

| PTA1     | AD1 $\rightarrow$ TCH1 $\rightarrow$ KBI1 $\rightarrow$ PTA1                                    |

| PTA2     | $\overline{\text{IRQ}} \rightarrow \text{KBI2} \rightarrow \text{TCLK} \rightarrow \text{PTA2}$ |

| PTA3     | $\overline{RST} \to KBI3 \to PTA3$                                                              |

| PTA4     | $OSC2 \rightarrow AD2 \rightarrow KBI4 \rightarrow PTA4$                                        |

| PTA5     | $OSC1 \to AD3 \to KBI5 \to PTA5$                                                                |

#### Memory

- 8. Wait for time,  $t_{PROG}$  (minimum 30  $\mu$ s).

- 9. Repeat step 7 and 8 until all desired bytes within the row are programmed.

- 10. Clear the PGM bit<sup>(1)</sup>.

- 11. Wait for time,  $t_{NVH}$  (minimum 5  $\mu$ s).

- 12. Clear the HVEN bit.

- 13. After time,  $t_{RCV}$  (typical 1  $\mu$ s), the memory can be accessed in read mode again.

#### NOTE

The COP register at location \$FFFF should not be written between steps 5–12, when the HVEN bit is set. Since this register is located at a valid FLASH address, unpredictable behavior may occur if this location is written while HVEN is set.

This program sequence is repeated throughout the memory until all data is programmed.

#### NOTE

Programming and erasing of FLASH locations cannot be performed by code being executed from the FLASH memory. While these operations must be performed in the order shown, other unrelated operations may occur between the steps. Do not exceed  $t_{PROG}$  maximum, see 16.16 Memory Characteristics.

## 2.6.5 FLASH Protection

Due to the ability of the on-board charge pump to erase and program the FLASH memory in the target application, provision is made to protect blocks of memory from unintentional erase or program operations due to system malfunction. This protection is done by use of a FLASH block protect register (FLBPR). The FLBPR determines the range of the FLASH memory which is to be protected. The range of the protected area starts from a location defined by FLBPR and ends to the bottom of the FLASH memory (\$FFFF). When the memory is protected, the HVEN bit cannot be set in either ERASE or PROGRAM operations.

#### NOTE

In performing a program or erase operation, the FLASH block protect register must be read after setting the PGM or ERASE bit and before asserting the HVEN bit.

When the FLBPR is programmed with all 0 s, the entire memory is protected from being programmed and erased. When all the bits are erased (all 1's), the entire memory is accessible for program and erase.

When bits within the FLBPR are programmed, they lock a block of memory. The address ranges are shown in 2.6.6 FLASH Block Protect Register. Once the FLBPR is programmed with a value other than \$FF, any erase or program of the FLBPR or the protected block of FLASH memory is prohibited. Mass erase is disabled whenever any block is protected (FLBPR does not equal \$FF). The FLBPR itself can be erased or programmed only with an external voltage, V<sub>TST</sub>, present on the  $\overline{IRQ}$  pin. This voltage also allows entry from reset into the monitor mode.

MC68HC908QY/QT Family Data Sheet, Rev. 6

<sup>2.</sup> The time between each FLASH address change, or the time between the last FLASH address programmed to clearing PGM bit, must not exceed the maximum programming time, t<sub>PROG</sub> maximum.

#### **Configuration Register (CONFIG)**

## IRQPUD — IRQ Pin Pullup Control Bit

- 1 = Internal pullup is disconnected

- $0 = Internal pullup is connected between <math>\overline{IRQ}$  pin and  $V_{DD}$

### IRQEN — IRQ Pin Function Selection Bit

- 1 = Interrupt request function active in pin

- 0 = Interrupt request function inactive in pin

## OSCOPT1 and OSCOPT0 — Selection Bits for Oscillator Option

- (0, 0) Internal oscillator

- (0, 1) External oscillator

- (1, 0) External RC oscillator

- (1, 1) External XTAL oscillator

## **RSTEN** — RST Pin Function Selection

- 1 = Reset function active in pin

- 0 = Reset function inactive in pin

#### NOTE

The RSTEN bit is cleared by a power-on reset (POR) only. Other resets will leave this bit unaffected.

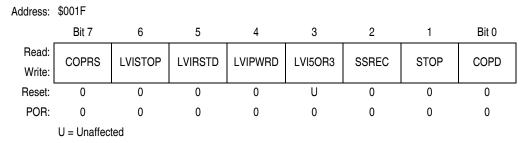

Figure 5-2. Configuration Register 1 (CONFIG1)

#### COPRS (Out of STOP Mode) — COP Reset Period Selection Bit

- 1 = COP reset short cycle = 8176 × BUSCLKX4

- 0 = COP reset long cycle = 262,128 × BUSCLKX4

#### COPRS (In STOP Mode) — Auto Wakeup Period Selection Bit

- 1 = Auto wakeup short cycle =  $512 \times INTRCOSC$

- 0 = Auto wakeup long cycle = 16,384 × INTRCOSC

## LVISTOP — LVI Enable in Stop Mode Bit

When the LVIPWRD bit is clear, setting the LVISTOP bit enables the LVI to operate during stop mode. Reset clears LVISTOP.

- 1 = LVI enabled during stop mode

- 0 = LVI disabled during stop mode

#### LVIRSTD — LVI Reset Disable Bit

LVIRSTD disables the reset signal from the LVI module.

- 1 = LVI module resets disabled

- 0 = LVI module resets enabled

#### LVIPWRD — LVI Power Disable Bit

LVIPWRD disables the LVI module.

- 1 = LVI module power disabled

- 0 = LVI module power enabled

#### LVI5OR3 — LVI 5-V or 3-V Operating Mode Bit

LVI5OR3 selects the voltage operating mode of the LVI module. The voltage mode selected for the LVI should match the operating  $V_{DD}$  for the LVI's voltage trip points for each of the modes.

- 1 = LVI operates in 5-V mode

- 0 = LVI operates in 3-V mode

#### NOTE

The LVI5OR3 bit is cleared by a power-on reset (POR) only. Other resets will leave this bit unaffected.

#### SSREC — Short Stop Recovery Bit

SSREC enables the CPU to exit stop mode with a delay of 32 BUSCLKX4 cycles instead of a 4096 BUSCLKX4 cycle delay.

- 1 = Stop mode recovery after 32 BUSCLKX4 cycles

- 0 = Stop mode recovery after 4096 BUSCLKX4 cycles

#### **NOTE**

Exiting stop mode by an LVI reset will result in the long stop recovery.

The system stabilization time for power-on reset and long stop recovery (both 4096 BUSCLKX4 cycles) gives a delay longer than the LVI enable time for these startup scenarios. There is no period where the MCU is not protected from a low-power condition. However, when using the short stop recovery configuration option, the 32 BUSCLKX4 delay must be greater than the LVI's turn on time to avoid a period in startup where the LVI is not protecting the MCU.

#### STOP — STOP Instruction Enable Bit

STOP enables the STOP instruction.

- 1 = STOP instruction enabled

- 0 = STOP instruction treated as illegal opcode

#### COPD — COP Disable Bit

COPD disables the COP module.

- 1 = COP module disabled

- 0 = COP module enabled

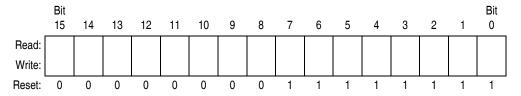

#### 7.3.3 Stack Pointer

The stack pointer is a 16-bit register that contains the address of the next location on the stack. During a reset, the stack pointer is preset to \$00FF. The reset stack pointer (RSP) instruction sets the least significant byte to \$FF and does not affect the most significant byte. The stack pointer decrements as data is pushed onto the stack and increments as data is pulled from the stack.

In the stack pointer 8-bit offset and 16-bit offset addressing modes, the stack pointer can function as an index register to access data on the stack. The CPU uses the contents of the stack pointer to determine the conditional address of the operand.

Figure 7-4. Stack Pointer (SP)

#### NOTE

The location of the stack is arbitrary and may be relocated anywhere in random-access memory (RAM). Moving the SP out of page 0 (\$0000 to \$00FF) frees direct address (page 0) space. For correct operation, the stack pointer must point only to RAM locations.

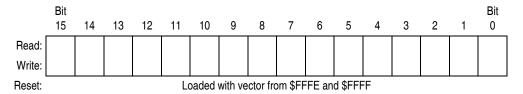

## 7.3.4 Program Counter

The program counter is a 16-bit register that contains the address of the next instruction or operand to be fetched.

Normally, the program counter automatically increments to the next sequential memory location every time an instruction or operand is fetched. Jump, branch, and interrupt operations load the program counter with an address other than that of the next sequential location.

During reset, the program counter is loaded with the reset vector address located at \$FFFE and \$FFFF. The vector address is the address of the first instruction to be executed after exiting the reset state.

Figure 7-5. Program Counter (PC)

MC68HC908QY/QT Family Data Sheet, Rev. 6 Freescale Semiconductor 63

#### **Keyboard Interrupt Module (KBI)**

To determine the logic level on a keyboard interrupt pin, use the data direction register to configure the pin as an input and then read the data register.

#### NOTE

Setting a keyboard interrupt enable bit (KBIEx) forces the corresponding keyboard interrupt pin to be an input, overriding the data direction register. However, the data direction register bit must be a 0 for software to read the pin.

## 9.3.2 Keyboard Initialization

When a keyboard interrupt pin is enabled, it takes time for the internal pullup to reach a logic 1. Therefore a false interrupt can occur as soon as the pin is enabled.

To prevent a false interrupt on keyboard initialization:

- 1. Mask keyboard interrupts by setting the IMASKK bit in the keyboard status and control register.

- 2. Enable the KBI pins by setting the appropriate KBIEx bits in the keyboard interrupt enable register.

- 3. Write to the ACKK bit in the keyboard status and control register to clear any false interrupts.

- 4. Clear the IMASKK bit.

An interrupt signal on an edge-triggered pin can be acknowledged immediately after enabling the pin. An interrupt signal on an edge- and level-triggered interrupt pin must be acknowledged after a delay that depends on the external load.

Another way to avoid a false interrupt:

- Configure the keyboard pins as outputs by setting the appropriate DDRA bits in the data direction register A.

- 2. Write 1s to the appropriate port A data register bits.

- 3. Enable the KBI pins by setting the appropriate KBIEx bits in the keyboard interrupt enable register.

## 9.4 Wait Mode

The keyboard module remains active in wait mode. Clearing the IMASKK bit in the keyboard status and control register enables keyboard interrupt requests to bring the MCU out of wait mode.

# 9.5 Stop Mode

The keyboard module remains active in stop mode. Clearing the IMASKK bit in the keyboard status and control register enables keyboard interrupt requests to bring the MCU out of stop mode.

# 9.6 Keyboard Module During Break Interrupts

The system integration module (SIM) controls whether the keyboard interrupt latch can be cleared during the break state. The BCFE bit in the break flag control register (BFCR) enables software to clear status bits during the break state.

To allow software to clear the keyboard interrupt latch during a break interrupt, write a 1 to the BCFE bit. If a latch is cleared during the break state, it remains cleared when the MCU exits the break state.

**Oscillator Module (OSC)**

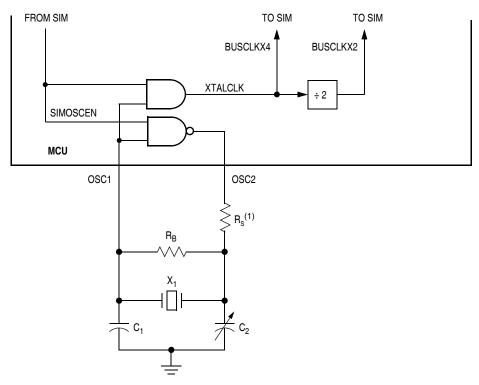

#### 11.3.3 XTAL Oscillator

The XTAL oscillator circuit is designed for use with an external crystal or ceramic resonator to provide an accurate clock source. In this configuration, the OSC2 pin is dedicated to the external crystal circuit. The OSC2EN bit in the port A pullup enable register has no effect when this clock mode is selected.

In its typical configuration, the XTAL oscillator is connected in a Pierce oscillator configuration, as shown in Figure 11-2. This figure shows only the logical representation of the internal components and may not represent actual circuitry. The oscillator configuration uses five components:

- Crystal, X<sub>1</sub>

- Fixed capacitor, C<sub>1</sub>

- Tuning capacitor, C<sub>2</sub> (can also be a fixed capacitor)

- Feedback resistor, R<sub>B</sub>

- Series resistor, R<sub>s</sub> (optional)

#### NOTE

The series resistor ( $R_{\rm S}$ ) is included in the diagram to follow strict Pierce oscillator guidelines and may not be required for all ranges of operation, especially with high frequency crystals. Refer to the crystal manufacturer's data for more information.

Note 1.

R<sub>S</sub> can be zero (shorted) when used with higher-frequency crystals. Refer to manufacturer's data. See Chapter 16 Electrical Specifications for component value recommendations.

Figure 11-2. XTAL Oscillator External Connections

Input/Output Ports (PORTS)

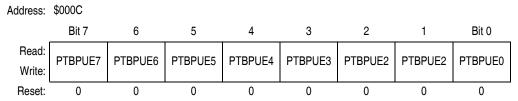

## 12.3.3 Port B Input Pullup Enable Register

The port B input pullup enable register (PTBPUE) contains a software configurable pullup device for each of the eight port B pins. Each bit is individually configurable and requires the corresponding data direction register, DDRBx, be configured as input. Each pullup device is automatically and dynamically disabled when its corresponding DDRBx bit is configured as output.

Figure 12-8. Port B Input Pullup Enable Register (PTBPUE)

#### PTBPUE[7:0] — Port B Input Pullup Enable Bits

These read/write bits are software programmable to enable pullup devices on port B pins

- 1 = Corresponding port B pin configured to have internal pull if its DDRB bit is set to 0

- 0 = Pullup device is disconnected on the corresponding port B pin regardless of the state of its DDRB bit.

Table 12-3 summarizes the operation of the port B pins.

Table 12-3. Port B Pin Functions

| PTBPUE | DDRB | РТВ              | I/O Pin                               | Accesses to DDRB | Access    | ses to PTB               |

|--------|------|------------------|---------------------------------------|------------------|-----------|--------------------------|

| Bit    | Bit  | Bit              | Mode                                  | Read/Write       | Read      | Write                    |

| 1      | 0    | X <sup>(1)</sup> | Input, V <sub>DD</sub> <sup>(2)</sup> | DDRB7-DDRB0      | Pin       | PTB7-PTB0 <sup>(3)</sup> |

| 0      | 0    | Х                | Input, Hi-Z <sup>(4)</sup>            | DDRB7-DDRB0      | Pin       | PTB7-PTB0 <sup>(3)</sup> |

| Х      | 1    | Х                | Output                                | DDRB7-DDRB0      | PTB7-PTB0 | PTB7-PTB0                |

- 1. X = don't care

- 2. I/O pin pulled to  $V_{\mbox{\scriptsize DD}}$  by internal pullup.

- 3. Writing affects data register, but does not affect input.

- 4. Hi-Z = high impedance

#### 13.6.2.1 Interrupt Status Register 1

Address: \$FE04 Bit 7 5 2 Bit 0 Read: 0 IF5 IF4 IF3 0 IF1 0 0 R R R R R R Write: R R 0 0 0 0 0 Reset: 0 0 0 R = Reserved

Figure 13-11. Interrupt Status Register 1 (INT1)

#### IF1 and IF3-IF5 — Interrupt Flags

These flags indicate the presence of interrupt requests from the sources shown in Table 13-3.

- 1 = Interrupt request present

- 0 = No interrupt request present

## Bit 0, 1, 3, and 7 — Always read 0

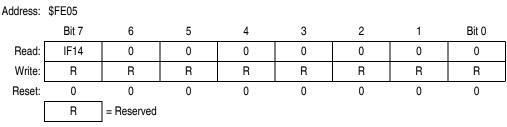

### 13.6.2.2 Interrupt Status Register 2

Figure 13-12. Interrupt Status Register 2 (INT2)

## IF14 — Interrupt Flags

This flag indicates the presence of interrupt requests from the sources shown in Table 13-3.

- 1 = Interrupt request present

- 0 = No interrupt request present

#### Bit 0-6 — Always read 0

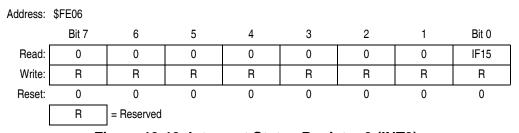

#### 13.6.2.3 Interrupt Status Register 3

Figure 13-13. Interrupt Status Register 3 (INT3)

#### IF15 — Interrupt Flags

These flags indicate the presence of interrupt requests from the sources shown in Table 13-3.

- 1 = Interrupt request present

- 0 = No interrupt request present

### Bit 1–7 — Always read 0

MC68HC908QY/QT Family Data Sheet, Rev. 6

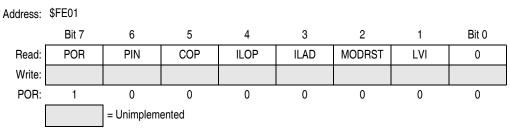

## 13.8.1 SIM Reset Status Register

The SRSR register contains flags that show the source of the last reset. The status register will automatically clear after reading SRSR. A power-on reset sets the POR bit and clears all other bits in the register. All other reset sources set the individual flag bits but do not clear the register. More than one reset source can be flagged at any time depending on the conditions at the time of the internal or external reset. For example, the POR and LVI bit can both be set if the power supply has a slow rise time.

Figure 13-19. SIM Reset Status Register (SRSR)

#### POR — Power-On Reset Bit

- 1 = Last reset caused by POR circuit

- 0 = Read of SRSR

#### PIN — External Reset Bit

- 1 = Last reset caused by external reset pin ( $\overline{RST}$ )

- 0 = POR or read of SRSR

## **COP** — Computer Operating Properly Reset Bit

- 1 = Last reset caused by COP counter

- 0 = POR or read of SRSR

#### ILOP — Illegal Opcode Reset Bit

- 1 = Last reset caused by an illegal opcode

- 0 = POR or read of SRSR

# ILAD — Illegal Address Reset Bit (illegal attempt to fetch an opcode from an unimplemented address)

- 1 = Last reset caused by an opcode fetch from an illegal address

- 0 = POR or read of SRSR

## **MODRST** — Monitor Mode Entry Module Reset Bit

- 1 = Last reset caused by monitor mode entry when vector locations \$FFFE and \$FFFF are \$FF after POR while  $\overline{IRQ} \neq V_{TST}$

- 0 = POR or read of SRSR

## LVI — Low Voltage Inhibit Reset Bit

- 1 = Last reset caused by LVI circuit

- 0 = POR or read of SRSR

#### **Timer Interface Module (TIM)**

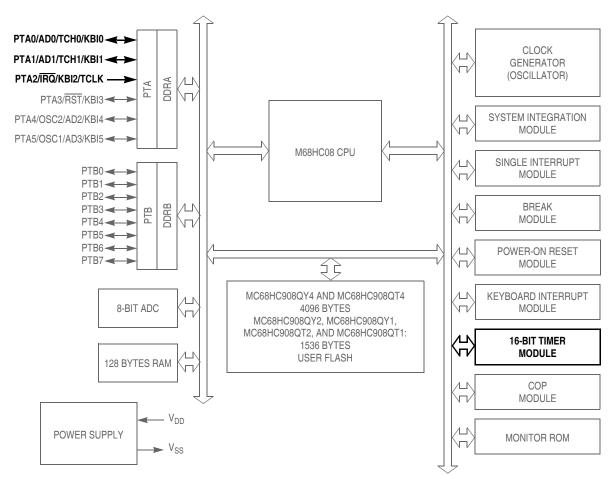

RST, IRQ: Pins have internal (about 30K Ohms) pull up

PTA[0:5]: High current sink and source capability

PTA[0:5]: Pins have programmable keyboard interrupt and pull up

PTB[0:7]: Not available on 8-pin devices – MC68HC908QT1, MC68HC908QT2, and MC68HC908QT4 (see note in 12.1 Introduction)

ADC: Not available on the MC68HC908QY1 and MC68HC908QT1

Figure 14-1. Block Diagram Highlighting TIM Block and Pins

**Timer Interface Module (TIM)**

## 14.6 Wait Mode

The WAIT instruction puts the MCU in low power-consumption standby mode.

The TIM remains active after the execution of a WAIT instruction. In wait mode the TIM registers are not accessible by the CPU. Any enabled CPU interrupt request from the TIM can bring the MCU out of wait mode.

If TIM functions are not required during wait mode, reduce power consumption by stopping the TIM before executing the WAIT instruction.

## 14.7 TIM During Break Interrupts

A break interrupt stops the TIM counter.

The system integration module (SIM) controls whether status bits in other modules can be cleared during the break state. The BCFE bit in the break flag control register (BFCR) enables software to clear status bits during the break state. See 13.8.2 Break Flag Control Register.

To allow software to clear status bits during a break interrupt, write a 1 to the BCFE bit. If a status bit is cleared during the break state, it remains cleared when the MCU exits the break state.

To protect status bits during the break state, write a 0 to the BCFE bit. With BCFE at 0 (its default state), software can read and write I/O registers during the break state without affecting status bits. Some status bits have a two-step read/write clearing procedure. If software does the first step on such a bit before the break, the bit cannot change during the break state as long as BCFE is at 0. After the break, doing the second step clears the status bit.

## 14.8 Input/Output Signals

Port A shares three of its pins with the TIM. Two TIM channel I/O pins are PTA0/TCH0 and PTA1/TCH1 and an alternate clock source is PTA2/TCLK.

## 14.8.1 TIM Clock Pin (PTA2/TCLK)

PTA2/TCLK is an external clock input that can be the clock source for the TIM counter instead of the prescaled internal bus clock. Select the PTA2/TCLK input by writing 1s to the three prescaler select bits, PS[2–0]. (See 14.9.1 TIM Status and Control Register.) When the PTA2/TCLK pin is the TIM clock input, it is an input regardless of port pin initialization.

## 14.8.2 TIM Channel I/O Pins (PTA0/TCH0 and PTA1/TCH1)

Each channel I/O pin is programmable independently as an input capture pin or an output compare pin. PTA0/TCH0 can be configured as a buffered output compare or buffered PWM pin.

# 14.9 Input/Output Registers

The following I/O registers control and monitor operation of the TIM:

- TIM status and control register (TSC)

- TIM counter registers (TCNTH:TCNTL)

- TIM counter modulo registers (TMODH:TMODL)

- TIM channel status and control registers (TSC0 and TSC1)

- TIM channel registers (TCH0H:TCH0L and TCH1H:TCH1L)

MC68HC908QY/QT Family Data Sheet, Rev. 6

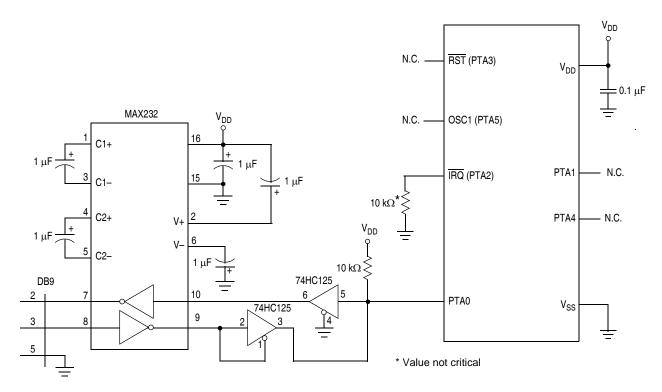

Figure 15-12. Monitor Mode Circuit (Internal Clock, No High Voltage)

Simple monitor commands can access any memory address. In monitor mode, the MCU can execute code downloaded into RAM by a host computer while most MCU pins retain normal operating mode functions. All communication between the host computer and the MCU is through the PTA0 pin. A level-shifting and multiplexing interface is required between PTA0 and the host computer. PTA0 is used in a wired-OR configuration and requires a pullup resistor.

The monitor code has been updated from previous versions of the monitor code to allow enabling the internal oscillator to generate the internal clock. This addition, which is enabled when  $\overline{IRQ}$  is held low out of reset, is intended to support serial communication/programming at 9600 baud in monitor mode by using the internal oscillator, and the internal oscillator user trim value OSCTRIM (FLASH location \$FFC0, if programmed) to generate the desired internal frequency (3.2 MHz). Since this feature is enabled only when  $\overline{IRQ}$  is held low out of reset, it cannot be used when the reset vector is programmed (i.e., the value is not \$FFFF) because entry into monitor mode in this case requires  $V_{TST}$  on  $\overline{IRQ}$ . The  $\overline{IRQ}$  pin must remain low during this monitor session in order to maintain communication.

Table 15-1 shows the pin conditions for entering monitor mode. As specified in the table, monitor mode may be entered after a power-on reset (POR) and will allow communication at 9600 baud provided one of the following sets of conditions is met:

- If \$FFFE and \$FFFF do not contain \$FF (programmed state):

- The external clock is 9.8304 MHz

- $\overline{IRQ} = V_{TST}$

- If \$FFFE and \$FFFF contain \$FF (erased state):

- The external clock is 9.8304 MHz

- $\overline{IRQ} = V_{DD}$  (this can be implemented through the internal  $\overline{IRQ}$  pullup)

- If \$FFFE and \$FFFF contain \$FF (erased state):

- $\overline{IRQ} = V_{SS}$  (internal oscillator is selected, no external clock required)

MC68HC908QY/QT Family Data Sheet, Rev. 6

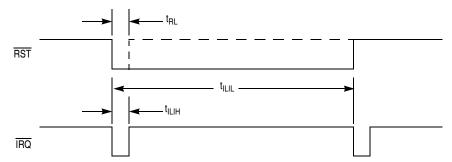

# 16.11 3-V Control Timing

| Characteristic <sup>(1)</sup>                  | Symbol                              | Min                 | Max | Unit             |

|------------------------------------------------|-------------------------------------|---------------------|-----|------------------|

| Internal operating frequency                   | f <sub>OP</sub> (f <sub>Bus</sub> ) | _                   | 4   | MHz              |

| Internal clock period (1/f <sub>OP</sub> )     | t <sub>cyc</sub>                    | 250                 | _   | ns               |

| RST input pulse width low                      | t <sub>RL</sub>                     | 200                 | _   | ns               |

| IRQ interrupt pulse width low (edge-triggered) | t <sub>ILIH</sub>                   | 200                 | _   | ns               |

| IRQ interrupt pulse period                     | t <sub>ILIL</sub>                   | Note <sup>(2)</sup> | _   | t <sub>cyc</sub> |

<sup>1.</sup>  $V_{DD}$  = 2.7 to 3.3 Vdc,  $V_{SS}$  = 0 Vdc,  $T_A$  =  $T_L$  to  $T_H$ ; timing shown with respect to 20%  $V_{DD}$  and 70%  $V_{DD}$ , unless otherwise noted.

<sup>2.</sup> The minimum period is the number of cycles it takes to execute the interrupt service routine plus 1  $t_{cyc}$ .

Figure 16-7. RST and IRQ Timing

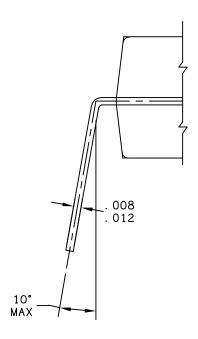

DETAIL "D"

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED. | MECHANICAL OUTLINE |              | PRINT VERSION NOT TO SCALE |             |

|------------------------------------------------------|--------------------|--------------|----------------------------|-------------|

| TITLE:                                               |                    | DOCUMENT NO  | : 98ASB42420B              | REV: N      |

| 8 LD PDIP                                            |                    | CASE NUMBER  | : 626–06                   | 19 MAY 2005 |

|                                                      |                    | STANDARD: NO | N-JEDEC                    |             |

Semiconductor

© FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED.

ELECTRONIC VERSIONS ARE UNCONTROLLED EXCEPT WHEN ACCESSED

DIRECTLY FROM THE DOCUMENT CONTROL REPOSITORY, PRINTED

VERSIONS ARE UNCONTROLLED EXCEPT WHEN STAMPED "CONTROLLED

COPY" IN RED.

## MECHANICAL OUTLINES DICTIONARY

DOCUMENT NO: 98ASH70107A

PAGE:

968

DO NOT SCALE THIS DRAWING

REV: Α

#### NOTES:

- 1. DIMENSIONS AND TOLERANCES PER ASME Y14.5-1994.

- 2. CONTROLLING DIMENSION: MILLIMETER.

/3\ DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS AND ARE MEASURED AT THE PARTING LINE. MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEDD 0.15mm PER SIDE.

4. TERMINAL NUMBERS ARE SHOWN FOR REFERENCE ONLY.

$\sqrt{5}$ \ THE LEAD WIDTH DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION SHALL BE 0.08mm TOTAL IN EXCESS OF THE LEAD WIDTH DIMENSION AT MAXIMUM MATERIAL CONDITION. DAMBAR CANNOT BE LOCATED ON THE LOWER RADIUS OR THE FOOT. MINIMUM SPACE BETWEEN PROTRUSIONS AND ADJACENT LEAD TO BE 0.46mm.

TITLE: CASE NUMBER: 968-02 8 LEAD MFP STANDARD: EIAJ PACKAGE CODE: 6003 SHEET: 3 OF 4