Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                |

| Core Processor             | HC08                                                                    |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 8MHz                                                                    |

| Connectivity               | -                                                                       |

| Peripherals                | LVD, POR, PWM                                                           |

| Number of I/O              | 13                                                                      |

| Program Memory Size        | 1.5KB (1.5K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 128 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                             |

| Data Converters            | A/D 4x8b                                                                |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 16-SOIC (0.295", 7.50mm Width)                                          |

| Supplier Device Package    | 16-SOIC                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc68hc908qy2cdw |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Chapter 7 Central Processor Unit (CPU)

| 7.1   | Introduction                            | 61        |

|-------|-----------------------------------------|-----------|

| 7.2   | Features                                | 61        |

| 7.3   | CPU Registers                           | 61        |

| 7.3.1 | Accumulator                             | 62        |

| 7.3.2 | Index Register                          |           |

| 7.3.3 | Stack Pointer                           |           |

| 7.3.4 | Program Counter                         |           |

| 7.3.5 | Condition Code Register                 |           |

| 7.4   | Arithmetic/Logic Unit (ALU)             |           |

| 7.5   | Low-Power Modes                         |           |

| 7.5.1 | Wait Mode                               |           |

| 7.5.2 | Stop Mode                               |           |

| 7.6   | CPU During Break Interrupts             |           |

| 7.7   | Instruction Set Summary                 |           |

| 7.8   | Opcode Map                              | 71        |

|       | Chapter 8                               |           |

|       | External Interrupt (IRQ)                |           |

| 8.1   | Introduction                            | 73        |

| 8.2   | Features                                | 73        |

| 8.3   | Functional Description                  | 73        |

| 8.3.1 | MODE = 1                                | 75        |

| 8.3.2 | MODE = 0                                | <b>75</b> |

| 8.4   | Interrupts                              | 76        |

| 8.5   | Low-Power Modes                         | <b>76</b> |

| 8.5.1 | Wait Mode                               | 76        |

| 8.5.2 | Stop Mode                               |           |

| 8.6   | IRQ Module During Break Interrupts      |           |

| 8.7   | I/O Signals                             |           |

| 8.7.1 | IRQ Input Pins (IRQ)                    |           |

| 8.8   | Registers                               | 77        |

|       | Chapter 9                               |           |

|       | Keyboard Interrupt Module (KBI)         |           |

| 9.1   | Introduction                            | 79        |

| 9.2   | Features                                | 79        |

| 9.3   | Functional Description                  |           |

| 9.3.1 | Keyboard Operation                      |           |

| 9.3.2 | Keyboard Initialization                 |           |

| 9.4   | Wait Mode                               | 82        |

| 9.5   | Stop Mode                               | 82        |

| 9.6   | Keyboard Module During Break Interrupts | 82        |

|       |                                         |           |

MC68HC908QY/QT Family Data Sheet, Rev. 6

### Memory

| Addr.                  | Register Name                              |                 | Bit 7        | 6           | 5     | 4     | 3              | 2        | 1                  | Bit 0 |

|------------------------|--------------------------------------------|-----------------|--------------|-------------|-------|-------|----------------|----------|--------------------|-------|

| \$0039<br>↓            | Unimplemented                              |                 |              |             |       |       |                |          |                    |       |

| \$003B                 |                                            |                 |              |             |       |       |                |          |                    |       |

|                        |                                            | Dand. [         | 0000         |             |       | 1     |                |          |                    |       |

| \$003C                 | ADC Status and Control<br>Register (ADSCR) | Read:<br>Write: | COCO<br>R    | AIEN        | ADCO  | CH4   | CH3            | CH2      | CH1                | CH0   |

| φυσου                  | See page 45.                               | Reset:          | 0            | 0           | 0     | 1     | 1              | 1        | 1                  | 1     |

| \$003D                 | Unimplemented                              | 110001.         |              |             |       |       | '              | '        | '                  | '     |

| ****                   |                                            | L               |              |             |       |       |                |          |                    |       |

|                        | ADC Data Register                          | Read:           | Bit 7        | Bit 6       | Bit 5 | Bit 4 | Bit 3          | Bit 2    | Bit 1              | Bit 0 |

| \$003E                 | (ADR)                                      | Write:          | DIL 7        | Dit 0       | Dit 3 |       |                | DIL Z    | DIL 1              | DIL 0 |

|                        | See page 47.                               | Reset:          |              |             |       |       | te after reset |          |                    |       |

|                        | ADC Input Clock Register                   | Read:           | ADIV2        | ADIV1       | ADIV0 | 0     | 0              | 0        | 0                  | 0     |

| \$003F                 | (ADICLK)<br>See page 47.                   | Write:          |              |             |       |       |                |          |                    | _     |

|                        |                                            | Reset:          | 0            | 0           | 0     | 0     | 0              | 0        | 0                  | 0     |

| \$FE00                 | Break Status Register (BSR)                | Read:<br>Write: | R            | R           | R     | R     | R              | R        | SBSW<br>See note 1 | R     |

| ψ. 200                 | See page 137.                              | Reset:          |              |             |       |       |                |          | 0                  |       |

|                        |                                            |                 | 1. Writing a | clears SBSV | N.    |       |                |          |                    |       |

|                        |                                            | -               |              |             |       |       |                |          |                    |       |

|                        | SIM Reset Status Register                  | Read:           | POR          | PIN         | COP   | ILOP  | ILAD           | MODRST   | LVI                | 0     |

| \$FE01                 | (SRSR)                                     | Write:          |              |             | _     | _     | _              |          | _                  | _     |

|                        | See page 117.                              | POR:            | 1            | 0           | 0     | 0     | 0              | 0        | 0                  | 0     |

| ¢EE00                  | Break Auxiliary                            | Read:           | 0            | 0           | 0     | 0     | 0              | 0        | 0                  | BDCOP |

| \$FE02                 | Register (BRKAR) See page 137.             | Write: Reset:   | 0            | 0           | 0     | 0     | 0              | 0        | 0                  | 0     |

|                        |                                            | Read:           | 0            | 0           |       | I     | 0              | U        |                    |       |

| \$FE03                 | Break Flag Control<br>Register (BFCR)      | Write:          | BCFE         | R           | R     | R     | R              | R        | R                  | R     |

| ,                      | See page 138.                              | Reset:          | 0            |             |       |       |                |          |                    |       |

|                        | Interrupt Status Register 1                | Read:           | 0            | IF5         | IF4   | IF3   | 0              | IF1      | 0                  | 0     |

| \$FE04                 | (INT1)                                     | Write:          | R            | R           | R     | R     | R              | R        | R                  | R     |

|                        | See page 77.                               | Reset:          | 0            | 0           | 0     | 0     | 0              | 0        | 0                  | 0     |

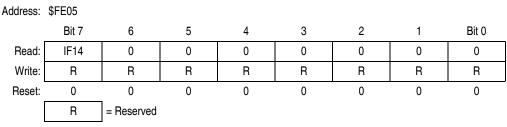

|                        | Interrupt Status Register 2                | Read:           | IF14         | 0           | 0     | 0     | 0              | 0        | 0                  | 0     |

| \$FE05                 | (INT2)                                     | Write:          | R            | R           | R     | R     | R              | R        | R                  | R     |

|                        | See page 77.                               | Reset:          | 0            | 0           | 0     | 0     | 0              | 0        | 0                  | 0     |

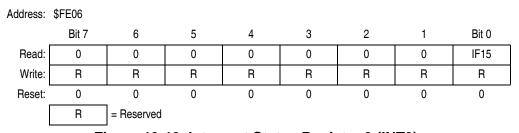

|                        | Interrupt Status Register 3                | Read:           | 0            | 0           | 0     | 0     | 0              | 0        | 0                  | IF15  |

| \$FE06                 | (INT3)<br>See page 77.                     | Write:          | R            | R           | R     | R     | R              | R        | R                  | R     |

| ФЕ <b>Г</b> О <b>7</b> |                                            | Reset:          | 0            | 0           | 0     | 0     | 0<br>R         | 0        | 0                  | 0     |

| \$FE07                 | Reserved                                   | Ĺ               | R            | R           | R     | R     | ň              | R        | R                  | R     |

|                        |                                            |                 |              | = Unimplem  | ented | R     | = Reserved     | U = Unaf | fected             |       |

Figure 2-2. Control, Status, and Data Registers (Sheet 4 of 5)

MC68HC908QY/QT Family Data Sheet, Rev. 6

### 2.6.7 Wait Mode

Putting the MCU into wait mode while the FLASH is in read mode does not affect the operation of the FLASH memory directly, but there will not be any memory activity since the CPU is inactive.

The WAIT instruction should not be executed while performing a program or erase operation on the FLASH, or the operation will discontinue and the FLASH will be on standby mode.

### 2.6.8 Stop Mode

Putting the MCU into stop mode while the FLASH is in read mode does not affect the operation of the FLASH memory directly, but there will not be any memory activity since the CPU is inactive.

The STOP instruction should not be executed while performing a program or erase operation on the FLASH, or the operation will discontinue and the FLASH will be on standby mode

### NOTE

Standby mode is the power-saving mode of the FLASH module in which all internal control signals to the FLASH are inactive and the current consumption of the FLASH is at a minimum.

### 3.5.2 Stop Mode

The ADC module is inactive after the execution of a STOP instruction. Any pending conversion is aborted. ADC conversions resume when the MCU exits stop mode. Allow one conversion cycle to stabilize the analog circuitry before using ADC data after exiting stop mode.

### 3.6 Input/Output Signals

The ADC module has four channels that are shared with I/O port A.

ADC voltage in (ADCVIN) is the input voltage signal from one of the four ADC channels to the ADC module.

### 3.7 Input/Output Registers

These I/O registers control and monitor ADC operation:

- ADC status and control register (ADSCR)

- ADC data register (ADR)

- ADC clock register (ADICLK)

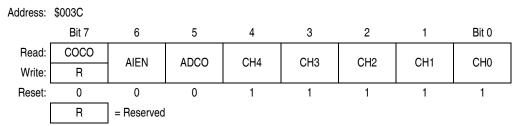

### 3.7.1 ADC Status and Control Register

The following paragraphs describe the function of the ADC status and control register (ADSCR). When a conversion is in process and the ADSCR is written, the current conversion data should be discarded to prevent an incorrect reading.

Figure 3-3. ADC Status and Control Register (ADSCR)

### **COCO** — Conversions Complete Bit

In non-interrupt mode (AIEN = 0), COCO is a read-only bit that is set at the end of each conversion. COCO will stay set until cleared by a read of the ADC data register. Reset clears this bit.

In interrupt mode (AIEN = 1), COCO is a read-only bit that is not set at the end of a conversion. It always reads as a 0.

- 1 = Conversion completed (AIEN = 0)

- 0 = Conversion not completed (AIEN = 0) or CPU interrupt enabled (AIEN = 1)

### NOTE

The write function of the COCO bit is reserved. When writing to the ADSCR register, always have a 0 in the COCO bit position.

MC68HC908QY/QT Family Data Sheet, Rev. 6

**Analog-to-Digital Converter (ADC)**

### **Auto Wakeup Module (AWU)**

### Bits 7-4 — Not used

These read-only bits always read as 0s.

### **KEYF** — Keyboard Flag Bit

This read-only bit is set when a keyboard interrupt is pending on port A or auto wakeup. Reset clears the KEYF bit.

- 1 = Keyboard/auto wakeup interrupt pending

- 0 = No keyboard/auto wakeup interrupt pending

### ACKK — Keyboard Acknowledge Bit

Writing a 1 to this write-only bit clears the keyboard/auto wakeup interrupt request on port A and auto wakeup logic. ACKK always reads as 0.Reset clears ACKK.

### **IMASKK**— Keyboard Interrupt Mask Bit

Writing a 1 to this read/write bit prevents the output of the keyboard interrupt mask from generating interrupt requests on port A or auto wakeup. Reset clears the IMASKK bit.

- 1 = Keyboard/auto wakeup interrupt requests masked

- 0 = Keyboard/auto wakeup interrupt requests not masked

### NOTE

MODEK is not used in conjuction with the auto wakeup feature. To see a description of this bit, see 9.7.1 Keyboard Status and Control Register.

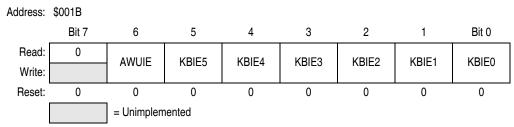

### 4.6.3 Keyboard Interrupt Enable Register

The keyboard interrupt enable register (KBIER) enables or disables the auto wakeup to operate as a keyboard/auto wakeup interrupt input.

Figure 4-4. Keyboard Interrupt Enable Register (KBIER)

### **AWUIE** — Auto Wakeup Interrupt Enable Bit

This read/write bit enables the auto wakeup interrupt input to latch interrupt requests. Reset clears AWUIE.

- 1 = Auto wakeup enabled as interrupt input

- 0 = Auto wakeup not enabled as interrupt input

### NOTE

KBIE5–KBIE0 bits are not used in conjuction with the auto wakeup feature. To see a description of these bits, see 9.7.2 Keyboard Interrupt Enable Register.

**Configuration Register (CONFIG)**

### **Central Processor Unit (CPU)**

# 7.7 Instruction Set Summary

Table 7-1 provides a summary of the M68HC08 instruction set.

Table 7-1. Instruction Set Summary (Sheet 1 of 6)

| Source                                                                                          | Operation                                            | Description                                              |           |   |   |          | t<br>R |   | Address<br>Mode                                                                              | Opcode                                           | Operand                                         | les                                  |

|-------------------------------------------------------------------------------------------------|------------------------------------------------------|----------------------------------------------------------|-----------|---|---|----------|--------|---|----------------------------------------------------------------------------------------------|--------------------------------------------------|-------------------------------------------------|--------------------------------------|

| Form                                                                                            | o polition                                           | 2000.1011011                                             | ٧         | Н | I | N        | Z      | С | Add                                                                                          | Opc                                              | Ope                                             | Cycles                               |

| ADC #opr<br>ADC opr<br>ADC opr<br>ADC opr,X<br>ADC opr,X<br>ADC, X<br>ADC opr,SP<br>ADC opr,SP  | Add with Carry                                       | $A \leftarrow (A) + (M) + (C)$                           | 1         | ‡ | ı | ‡        | ‡      | ‡ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2                                          | A9<br>B9<br>C9<br>D9<br>E9<br>F9<br>9EE9<br>9ED9 | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ee ff       | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5 |

| ADD #opr<br>ADD opr<br>ADD opr,X<br>ADD opr,X<br>ADD opr,X<br>ADD opr,SP<br>ADD opr,SP          | Add without Carry                                    | A ← (A) + (M)                                            | ‡         | ‡ | - | 1        | 1      | ‡ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2                                          | AB<br>BB<br>CB<br>DB<br>EB<br>FB<br>9EEB<br>9EDB |                                                 | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5 |

| AIS #opr                                                                                        | Add Immediate Value (Signed) to SP                   | SP ← (SP) + (16 <b>«</b> M)                              | -         | _ | _ | _        | _      | - | IMM                                                                                          | A7                                               | ii                                              | 2                                    |

| AIX #opr                                                                                        | Add Immediate Value (Signed) to H:X                  | H:X ← (H:X) + (16 ≪ M)                                   | -         | _ | _ | _        | -      | _ | IMM                                                                                          | AF                                               | ii                                              | 2                                    |

| AND #opr<br>AND opr<br>AND opr,<br>AND opr,X<br>AND opr,X<br>AND, X<br>AND opr,SP<br>AND opr,SP | Logical AND                                          | A ← (A) & (M)                                            | 0         | _ | _ | ‡        | ‡      | _ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2                                          | A4<br>B4<br>C4<br>D4<br>E4<br>F4<br>9EE4<br>9ED4 | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ff<br>ee ff | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5 |

| ASL opr<br>ASLA<br>ASLX<br>ASL opr,X<br>ASL ,X<br>ASL opr,SP                                    | Arithmetic Shift Left<br>(Same as LSL)               | C → 0 b0                                                 | 1         | _ | - | ‡        | 1      | ‡ | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1                                                        | 38<br>48<br>58<br>68<br>78<br>9E68               | dd<br>ff<br>ff                                  | 4<br>1<br>1<br>4<br>3<br>5           |

| ASR opr<br>ASRA<br>ASRX<br>ASR opr,X<br>ASR opr,X<br>ASR opr,SP                                 | Arithmetic Shift Right                               | b7 b0                                                    | ţ         | _ | - | <b>‡</b> | ţ      | ‡ | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1                                                        | 37<br>47<br>57<br>67<br>77<br>9E67               | dd<br>ff<br>ff                                  | 4<br>1<br>1<br>4<br>3<br>5           |

| BCC rel                                                                                         | Branch if Carry Bit Clear                            | $PC \leftarrow (PC) + 2 + rel ? (C) = 0$                 | _         | _ | _ | _        | -      | - | REL                                                                                          | 24                                               | rr                                              | 3                                    |

| BCLR n, opr                                                                                     | Clear Bit n in M                                     | Mn ← 0                                                   | _         | _ | _ | _        | _      | _ | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7) | 11<br>13<br>15<br>17<br>19<br>1B<br>1D<br>1F     | dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd    | 4<br>4<br>4<br>4<br>4<br>4<br>4      |

| BCS rel                                                                                         | Branch if Carry Bit Set (Same as BLO)                | PC ← (PC) + 2 + rel? (C) = 1                             | -         | - | - | _        | -      | - | REL                                                                                          | 25                                               | rr                                              | 3                                    |

| BEQ rel                                                                                         | Branch if Equal                                      | $PC \leftarrow (PC) + 2 + rel? (Z) = 1$                  | -         | - | _ | _        | _      | _ | REL                                                                                          | 27                                               | rr                                              | 3                                    |

| BGE opr                                                                                         | Branch if Greater Than or Equal To (Signed Operands) | $PC \leftarrow (PC) + 2 + rel? (N \oplus V) = 0$         | _         | - | _ | _        | _      | _ | REL                                                                                          | 90                                               | rr                                              | 3                                    |

| BGT opr                                                                                         | Branch if Greater Than (Signed Operands)             | $PC \leftarrow (PC) + 2 + rel?(Z) \mid (N \oplus V) = 0$ | _         | _ | - | _        | _      | _ | REL                                                                                          | 92                                               | rr                                              | 3                                    |

| BHCC rel                                                                                        | Branch if Half Carry Bit Clear                       | $PC \leftarrow (PC) + 2 + rel? (H) = 0$                  | _         | _ | _ | _        | _      | _ | REL                                                                                          | 28                                               | rr                                              | 3                                    |

| BHCS rel                                                                                        | Branch if Half Carry Bit Set                         | $PC \leftarrow (PC) + 2 + rel? (H) = 1$                  | <u> -</u> | _ | _ | _        | _      | _ | REL                                                                                          | 29                                               | rr                                              | 3                                    |

| BHI rel                                                                                         | Branch if Higher                                     | $PC \leftarrow (PC) + 2 + rel? (C)   (Z) = 0$            | -         | - | _ | _        | _      | _ | REL                                                                                          | 22                                               | rr                                              | 3                                    |

MC68HC908QY/QT Family Data Sheet, Rev. 6

# MC68HC908QY/QT Family Data Sheet, Rev. 6

8HC908QY/QT Family Da

Table 7-2. Opcode Map

|            | Bit Mani             | pulation            | Branch             |                    |                    | Read-Mod            | dify-Write          |                    |                    | Control            |                   | Register/Memory   |                   |                   |                   |                   |                   |                   |                  |

|------------|----------------------|---------------------|--------------------|--------------------|--------------------|---------------------|---------------------|--------------------|--------------------|--------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|

|            | DIR DIR REL          |                     | REL                | DIR                | INH                | INH IX1             |                     | SP1                | IX                 | INH                | INH               | IMM               | DIR               | EXT IX2           |                   | SP2 IX1           |                   | SP1               | IX               |

| MSB<br>LSB | 0                    | 1                   | 2                  | 3                  | 4                  | 5                   | 6                   | 9E6                | 7                  | 8                  | 9                 | Α                 | В                 | С                 | D                 | 9ED               | E                 | 9EE               | F                |

| 0          | -                    | BSET0<br>2 DIR      |                    |                    | 1<br>NEGA<br>1 INH |                     | 4<br>NEG<br>2 IX1   |                    | 3<br>NEG<br>1 IX   | 7<br>RTI<br>1 INH  |                   | SUB<br>2 IMM      |                   |                   | SUB<br>3 IX2      | 5<br>SUB<br>4 SP2 | 3<br>SUB<br>2 IX1 | 4<br>SUB<br>3 SP1 | SUB<br>1 IX      |

| 1          | 5<br>BRCLR0<br>3 DIR | 4<br>BCLR0<br>2 DIR | 3<br>BRN<br>2 REL  | 5<br>CBEQ<br>3 DIR | 3 IMM              | CBEQX<br>3 IMM      | 5<br>CBEQ<br>3 IX1+ | 6<br>CBEQ<br>4 SP1 |                    | 4<br>RTS<br>1 INH  | 3<br>BLT<br>2 REL |                   | 3<br>CMP<br>2 DIR | 4<br>CMP<br>3 EXT | 4<br>CMP<br>3 IX2 | 5<br>CMP<br>4 SP2 | 3<br>CMP<br>2 IX1 | 4<br>CMP<br>3 SP1 | 2<br>CMP<br>1 IX |

| 2          | -                    | BSET1<br>2 DIR      |                    |                    | 5<br>MUL<br>1 INH  | 7<br>DIV<br>1 INH   | 3<br>NSA<br>1 INH   |                    | 2<br>DAA<br>1 INH  |                    | 3<br>BGT<br>2 REL |                   | 3<br>SBC<br>2 DIR | 4<br>SBC<br>3 EXT | 4<br>SBC<br>3 IX2 | 5<br>SBC<br>4 SP2 |                   | 4<br>SBC<br>3 SP1 | SBC<br>1 IX      |

| 3          | -                    | 4<br>BCLR1<br>2 DIR |                    | COM<br>2 DIR       | 1<br>COMA<br>1 INH |                     | 4<br>COM<br>2 IX1   | 5<br>COM<br>3 SP1  |                    | 9<br>SWI<br>1 INH  |                   |                   |                   |                   |                   | 5<br>CPX<br>4 SP2 |                   | 4<br>CPX<br>3 SP1 | CPX<br>1 IX      |

| 4          | 5<br>BRSET2<br>3 DIR | 4<br>BSET2<br>2 DIR | 3<br>BCC<br>2 REL  | 4<br>LSR<br>2 DIR  | 1<br>LSRA<br>1 INH | 1<br>LSRX<br>1 INH  | 4<br>LSR<br>2 IX1   | 5<br>LSR<br>3 SP1  |                    | 2<br>TAP<br>1 INH  |                   | 2<br>AND<br>2 IMM |                   |                   |                   | 5<br>AND<br>4 SP2 |                   | 4<br>AND<br>3 SP1 | 2<br>AND<br>1 IX |

| 5          | 5<br>BRCLR2<br>3 DIR | 4<br>BCLR2<br>2 DIR | 3<br>BCS<br>2 REL  | 4<br>STHX<br>2 DIR | 3<br>LDHX<br>3 IMM | 4<br>LDHX<br>2 DIR  | CPHX<br>3 IMM       |                    | 4<br>CPHX<br>2 DIR | 1<br>TPA<br>1 INH  | 2<br>TSX<br>1 INH |                   |                   | 4<br>BIT<br>3 EXT |                   |                   | 3<br>BIT<br>2 IX1 | 4<br>BIT<br>3 SP1 | 2<br>BIT<br>1 IX |

| 6          | 5<br>BRSET3<br>3 DIR | BSET3<br>2 DIR      | 3<br>BNE<br>2 REL  | 4<br>ROR<br>2 DIR  | 1<br>RORA<br>1 INH | 1<br>RORX<br>1 INH  | 4<br>ROR<br>2 IX1   | 5<br>ROR<br>3 SP1  | 3<br>ROR<br>1 IX   | 2<br>PULA<br>1 INH |                   | 2<br>LDA<br>2 IMM | 3<br>LDA<br>2 DIR | 4<br>LDA<br>3 EXT | 4<br>LDA<br>3 IX2 | 5<br>LDA<br>4 SP2 | 3<br>LDA<br>2 IX1 | 4<br>LDA<br>3 SP1 | 2<br>LDA<br>1 IX |

| 7          | 5<br>BRCLR3<br>3 DIR | 4<br>BCLR3<br>2 DIR | 3<br>BEQ<br>2 REL  | 4<br>ASR<br>2 DIR  | 1<br>ASRA<br>1 INH | 1<br>ASRX<br>1 INH  | 4<br>ASR<br>2 IX1   | 5<br>ASR<br>3 SP1  | 3<br>ASR<br>1 IX   | 2<br>PSHA<br>1 INH | 1<br>TAX<br>1 INH | AIS<br>2 IMM      | 3<br>STA<br>2 DIR | 4<br>STA<br>3 EXT | 4<br>STA<br>3 IX2 | 5<br>STA<br>4 SP2 | 3<br>STA<br>2 IX1 | 4<br>STA<br>3 SP1 | 2<br>STA<br>1 IX |

| 8          | 5<br>BRSET4<br>3 DIR | BSET4<br>2 DIR      | 3<br>BHCC<br>2 REL | 4<br>LSL<br>2 DIR  | 1<br>LSLA<br>1 INH | 1<br>LSLX<br>1 INH  | 4<br>LSL<br>2 IX1   | 5<br>LSL<br>3 SP1  | 3<br>LSL<br>1 IX   | 2<br>PULX<br>1 INH | 1<br>CLC<br>1 INH | EOR<br>2 IMM      | 3<br>EOR<br>2 DIR | 4<br>EOR<br>3 EXT | 4<br>EOR<br>3 IX2 | 5<br>EOR<br>4 SP2 | 3<br>EOR<br>2 IX1 | 4<br>EOR<br>3 SP1 | EOR<br>1 IX      |

| 9          | 5<br>BRCLR4<br>3 DIR | 4<br>BCLR4<br>2 DIR |                    | 4<br>ROL<br>2 DIR  | 1<br>ROLA<br>1 INH | 1<br>ROLX<br>1 INH  | 4<br>ROL<br>2 IX1   | 5<br>ROL<br>3 SP1  | 3<br>ROL<br>1 IX   | 2<br>PSHX<br>1 INH | 1<br>SEC<br>1 INH |                   | 3<br>ADC<br>2 DIR |                   |                   | 5<br>ADC<br>4 SP2 |                   | 4<br>ADC<br>3 SP1 | 2<br>ADC<br>1 IX |

| A          | 5<br>BRSET5<br>3 DIR | 4<br>BSET5<br>2 DIR | 3<br>BPL<br>2 REL  | 4<br>DEC<br>2 DIR  | 1<br>DECA<br>1 INH | 1<br>DECX<br>1 INH  | 4<br>DEC<br>2 IX1   | 5<br>DEC<br>3 SP1  | 3<br>DEC<br>1 IX   | 2<br>PULH<br>1 INH | 2<br>CLI<br>1 INH | ORA<br>2 IMM      | 3<br>ORA<br>2 DIR | 4<br>ORA<br>3 EXT | 4<br>ORA<br>3 IX2 | 5<br>ORA<br>4 SP2 | 3<br>ORA<br>2 IX1 | 4<br>ORA<br>3 SP1 | 2<br>ORA<br>1 IX |

| В          | 5<br>BRCLR5<br>3 DIR | BCLR5<br>2 DIR      | 3<br>BMI<br>2 REL  | 5<br>DBNZ<br>3 DIR |                    | 3<br>DBNZX<br>2 INH | 5<br>DBNZ<br>3 IX1  | 6<br>DBNZ<br>4 SP1 | 4<br>DBNZ<br>2 IX  | 2<br>PSHH<br>1 INH | 2<br>SEI<br>1 INH | ADD<br>2 IMM      | 3<br>ADD<br>2 DIR | 4<br>ADD<br>3 EXT | 4<br>ADD<br>3 IX2 | 5<br>ADD<br>4 SP2 | 3<br>ADD<br>2 IX1 | 4<br>ADD<br>3 SP1 | 2<br>ADD<br>1 IX |

| С          | 5<br>BRSET6<br>3 DIR | 4<br>BSET6<br>2 DIR |                    | 4<br>INC<br>2 DIR  | 1<br>INCA<br>1 INH | 1<br>INCX<br>1 INH  | 4<br>INC<br>2 IX1   | 5<br>INC<br>3 SP1  | 3<br>INC<br>1 IX   | 1<br>CLRH<br>1 INH | 1<br>RSP<br>1 INH |                   | 2<br>JMP<br>2 DIR | 3<br>JMP<br>3 EXT |                   |                   | 3<br>JMP<br>2 IX1 |                   | 2<br>JMP<br>1 IX |

| D          | 5<br>BRCLR6<br>3 DIR | 4<br>BCLR6<br>2 DIR |                    | 3<br>TST<br>2 DIR  | 1<br>TSTA<br>1 INH |                     | 3<br>TST<br>2 IX1   | 4<br>TST<br>3 SP1  |                    |                    | 1<br>NOP<br>1 INH |                   | 4<br>JSR<br>2 DIR | 5<br>JSR<br>3 EXT |                   |                   | 5<br>JSR<br>2 IX1 |                   | JSR<br>1 IX      |

| E          |                      | 4<br>BSET7<br>2 DIR |                    |                    | 5<br>MOV<br>3 DD   | 4<br>MOV<br>2 DIX+  | 4<br>MOV<br>3 IMD   |                    | 4<br>MOV<br>2 IX+D | 1<br>STOP<br>1 INH | *                 |                   | 3<br>LDX<br>2 DIR |                   |                   | 5<br>LDX<br>4 SP2 |                   | 4<br>LDX<br>3 SP1 | 2<br>LDX<br>1 IX |

| F          | 5<br>BRCLR7<br>3 DIR | 4<br>BCLR7<br>2 DIR | 3<br>BIH<br>2 REL  | 3<br>CLR<br>2 DIR  | 1<br>CLRA<br>1 INH | 1<br>CLRX<br>1 INH  | 3<br>CLR<br>2 IX1   | 4<br>CLR<br>3 SP1  | 2<br>CLR<br>1 IX   | 1<br>WAIT<br>1 INH | 1<br>TXA<br>1 INH | 2<br>AIX<br>2 IMM | 3<br>STX<br>2 DIR | 4<br>STX<br>3 EXT | 4<br>STX<br>3 IX2 | 5<br>STX<br>4 SP2 | 3<br>STX<br>2 IX1 | 4<br>STX<br>3 SP1 | STX<br>1 IX      |

INH Inherent REL Relative

IMM Immediate IX Indexed, No Offset

DIR Direct IX1 Indexed, 8-Bit Offset

EXT Extended IX2 Indexed, 16-Bit Offset

IX+D Indexed-Direct IMD Immediate-Direct

IX+D Indexed-Direct DIX+ Direct-Indexed

\*Pre-byte for stack pointer indexed instructions

Indexed, 1-Byte Offset with Low Byte of Opcode in Hexadecimal Post Increment

|   | MSB | 0                    | High Byte of Opcode in Hexadecimal                             |

|---|-----|----------------------|----------------------------------------------------------------|

| ı | 0   | 5<br>BRSET0<br>3 DIR | Cycles<br>Opcode Mnemonic<br>Number of Bytes / Addressing Mode |

SP1 Stack Pointer, 8-Bit Offset SP2 Stack Pointer, 16-Bit Offset IX+ Indexed, No Offset with Post Increment IX1+ Indexed, 1-Byte Offset with Post Increment

### 8.7.1 IRQ Input Pins (IRQ)

The IRQ pin provides a maskable external interrupt source. The IRQ pin contains an internal pullup device.

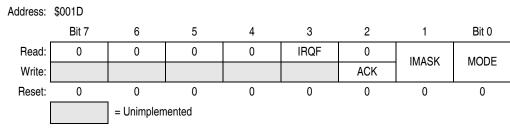

### 8.8 Registers

The IRQ status and control register (INTSCR) controls and monitors operation of the IRQ module. See Chapter 5 Configuration Register (CONFIG).

The INTSCR has the following functions:

- Shows the state of the IRQ flag

- Clears the IRQ latch

- Masks the IRQ interrupt request

- Controls triggering sensitivity of the IRQ interrupt pin

Figure 8-3. IRQ Status and Control Register (INTSCR)

### IRQF — IRQ Flag

This read-only status bit is set when the IRQ interrupt is pending.

- $1 = \overline{IRQ}$  interrupt pending

- $0 = \overline{IRQ}$  interrupt not pending

### ACK — IRQ Interrupt Request Acknowledge Bit

Writing a 1 to this write-only bit clears the IRQ latch. ACK always reads as 0.

### IMASK — IRQ Interrupt Mask Bit

Writing a 1 to this read/write bit disables the IRQ interrupt request.

- 1 = IRQ interrupt request disabled

- 0 = IRQ interrupt request enabled

### MODE — IRQ Edge/Level Select Bit

This read/write bit controls the triggering sensitivity of the  $\overline{IRQ}$  pin.

- $1 = \overline{IRQ}$  interrupt request on falling edges and low levels

- $0 = \overline{IRQ}$  interrupt request on falling edges only

External Interrupt (IRQ)

MC68HC908QY/QT Family Data Sheet, Rev. 6

To protect the latch during the break state, write a 0 to the BCFE bit. With BCFE at 0 (its default state), writing to the keyboard acknowledge bit (ACKK) in the keyboard status and control register during the break state has no effect.

### 9.7 Input/Output Registers

The following I/O registers control and monitor operation of the keyboard interrupt module:

- Keyboard interrupt status and control register (KBSCR)

- Keyboard interrupt enable register (KBIER)

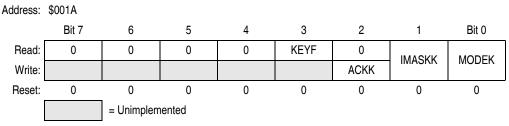

### 9.7.1 Keyboard Status and Control Register

The keyboard status and control register (KBSCR):

- Flags keyboard interrupt requests

- Acknowledges keyboard interrupt requests

- Masks keyboard interrupt requests

- Controls keyboard interrupt triggering sensitivity

Figure 9-3. Keyboard Status and Control Register (KBSCR)

### Bits 7-4 — Not used

These read-only bits always read as 0s.

### **KEYF** — Keyboard Flag Bit

This read-only bit is set when a keyboard interrupt is pending on port A or auto wakeup. Reset clears the KEYF bit.

- 1 = Keyboard interrupt pending

- 0 = No keyboard interrupt pending

### ACKK — Keyboard Acknowledge Bit

Writing a 1 to this write-only bit clears the keyboard interrupt request on port A and auto wakeup logic. ACKK always reads as 0. Reset clears ACKK.

### IMASKK— Keyboard Interrupt Mask Bit

Writing a 1 to this read/write bit prevents the output of the keyboard interrupt mask from generating interrupt requests on port A or auto wakeup. Reset clears the IMASKK bit.

- 1 = Keyboard interrupt requests masked

- 0 = Keyboard interrupt requests not masked

### **MODEK** — Keyboard Triggering Sensitivity Bit

This read/write bit controls the triggering sensitivity of the keyboard interrupt pins on port A and auto wakeup. Reset clears MODEK.

- 1 = Keyboard interrupt requests on falling edges and low levels

- 0 = Keyboard interrupt requests on falling edges only

MC68HC908QY/QT Family Data Sheet, Rev. 6

# **Chapter 12 Input/Output Ports (PORTS)**

### 12.1 Introduction

The MC68HC908QT1, MC68HC908QT2, and MC68HC908QT4 have five bidirectional input-output (I/O) pins and one input only pin. The MC68HC908QY1, MC68HC908QY2, and MC68HC908QY4 have thirteen bidirectional pins and one input only pin. All I/O pins are programmable as inputs or outputs.

### NOTE

Connect any unused I/O pins to an appropriate logic level, either  $V_{\rm DD}$  or  $V_{\rm SS}$ . Although the I/O ports do not require termination for proper operation, termination reduces excess current consumption and the possibility of electrostatic damage.

8-pin devices have non-bonded pins. These pins should be configured either as outputs driving low or high, or as inputs with internal pullups enabled. Configuring these non-bonded pins in this manner will prevent any excess current consumption caused by floating inputs.

### 12.2 Port A

Port A is a 6-bit special function port that shares all six of its pins with the keyboard interrupt (KBI) module (see Chapter 9 Keyboard Interrupt Module (KBI)). Each port A pin also has a software configurable pullup device if the corresponding port pin is configured as an input port.

### NOTE

PTA2 is input only.

When the  $\overline{IRQ}$  function is enabled in the configuration register 2 (CONFIG2), bit 2 of the port A data register (PTA) will always read a 0. In this case, the BIH and BIL instructions can be used to read the logic level on the PTA2 pin. When the  $\overline{IRQ}$  function is disabled, these instructions will behave as if the PTA2 pin is a logic 1. However, reading bit 2 of PTA will read the actual logic level on the pin.

**System Integration Module (SIM)**

### 13.4.1 External Pin Reset

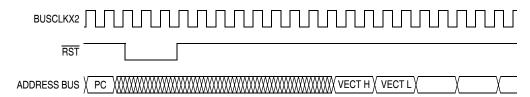

The  $\overline{RST}$  pin circuits include an internal pullup device. Pulling the asynchronous  $\overline{RST}$  pin low halts all processing. The PIN bit of the SIM reset status register (SRSR) is set as long as  $\overline{RST}$  is held low for at least the minimum  $t_{RL}$  time. Figure 13-3 shows the relative timing. The  $\overline{RST}$  pin function is only available if the RSTEN bit is set in the CONFIG2 register.

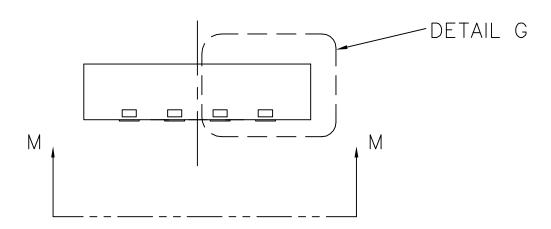

Figure 13-3. External Reset Timing

### 13.4.2 Active Resets from Internal Sources

The RST pin is initially setup as a general-purpose input after a POR. Setting the RSTEN bit in the CONFIG2 register enables the pin for the reset function. This section assumes the RSTEN bit is set when describing activity on the RST pin.

### NOTE

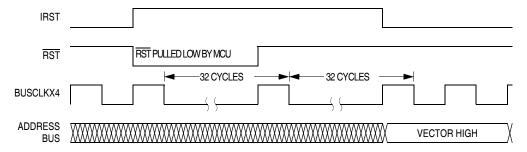

For POR and LVI resets, the SIM cycles through 4096 BUSCLKX4 cycles during which the SIM forces the  $\overline{RST}$  pin low. The internal reset signal then follows the sequence from the falling edge of  $\overline{RST}$  shown in Figure 13-4.

The COP reset is asynchronous to the bus clock.

The active reset feature allows the part to issue a reset to peripherals and other chips within a system built around the MCU.

All internal reset sources actively pull the  $\overline{RST}$  pin low for 32 BUSCLKX4 cycles to allow resetting of external peripherals. The internal reset signal IRST continues to be asserted for an additional 32 cycles (see Figure 13-4). An internal reset can be caused by an illegal address, illegal opcode, COP time out, LVI, or POR (see Figure 13-5).

Figure 13-4. Internal Reset Timing

MC68HC908QY/QT Family Data Sheet, Rev. 6

### 13.6.2.1 Interrupt Status Register 1

Address: \$FE04 Bit 7 5 2 Bit 0 Read: 0 IF5 IF4 IF3 0 IF1 0 0 R R R R R R Write: R R 0 0 0 0 0 Reset: 0 0 0 R = Reserved

Figure 13-11. Interrupt Status Register 1 (INT1)

### IF1 and IF3-IF5 — Interrupt Flags

These flags indicate the presence of interrupt requests from the sources shown in Table 13-3.

- 1 = Interrupt request present

- 0 = No interrupt request present

### Bit 0, 1, 3, and 7 — Always read 0

### 13.6.2.2 Interrupt Status Register 2

Figure 13-12. Interrupt Status Register 2 (INT2)

### IF14 — Interrupt Flags

This flag indicates the presence of interrupt requests from the sources shown in Table 13-3.

- 1 = Interrupt request present

- 0 = No interrupt request present

### Bit 0-6 — Always read 0

### 13.6.2.3 Interrupt Status Register 3

Figure 13-13. Interrupt Status Register 3 (INT3)

### IF15 — Interrupt Flags

These flags indicate the presence of interrupt requests from the sources shown in Table 13-3.

- 1 = Interrupt request present

- 0 = No interrupt request present

### Bit 1–7 — Always read 0

MC68HC908QY/QT Family Data Sheet, Rev. 6

### 14.4 Functional Description

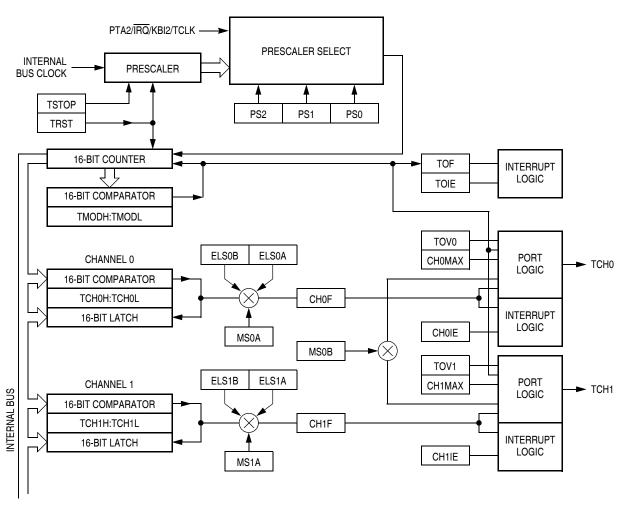

Figure 14-2 shows the structure of the TIM. The central component of the TIM is the 16-bit TIM counter that can operate as a free-running counter or a modulo up-counter. The TIM counter provides the timing reference for the input capture and output compare functions. The TIM counter modulo registers, TMODH:TMODL, control the modulo value of the TIM counter. Software can read the TIM counter value at any time without affecting the counting sequence.

The two TIM channels are programmable independently as input capture or output compare channels.

Figure 14-2. TIM Block Diagram

### Timer Interface Module (TIM)

### 14.4.4.1 Unbuffered PWM Signal Generation

Any output compare channel can generate unbuffered PWM pulses as described in 14.4.4 Pulse Width Modulation (PWM). The pulses are unbuffered because changing the pulse width requires writing the new pulse width value over the old value currently in the TIM channel registers.

An unsynchronized write to the TIM channel registers to change a pulse width value could cause incorrect operation for up to two PWM periods. For example, writing a new value before the counter reaches the old value but after the counter reaches the new value prevents any compare during that PWM period. Also, using a TIM overflow interrupt routine to write a new, smaller pulse width value may cause the compare to be missed. The TIM may pass the new value before it is written.

Use the following methods to synchronize unbuffered changes in the PWM pulse width on channel x:

- When changing to a shorter pulse width, enable channel x output compare interrupts and write the

new value in the output compare interrupt routine. The output compare interrupt occurs at the end

of the current pulse. The interrupt routine has until the end of the PWM period to write the new

value.

- When changing to a longer pulse width, enable TIM overflow interrupts and write the new value in the TIM overflow interrupt routine. The TIM overflow interrupt occurs at the end of the current PWM period. Writing a larger value in an output compare interrupt routine (at the end of the current pulse) could cause two output compares to occur in the same PWM period.

### NOTE

In PWM signal generation, do not program the PWM channel to toggle on output compare. Toggling on output compare prevents reliable 0% duty cycle generation and removes the ability of the channel to self-correct in the event of software error or noise. Toggling on output compare also can cause incorrect PWM signal generation when changing the PWM pulse width to a new, much larger value.

### 14.4.4.2 Buffered PWM Signal Generation

Channels 0 and 1 can be linked to form a buffered PWM channel whose output appears on the TCH0 pin. The TIM channel registers of the linked pair alternately control the pulse width of the output.

Setting the MS0B bit in TIM channel 0 status and control register (TSC0) links channel 0 and channel 1. The TIM channel 0 registers initially control the pulse width on the TCH0 pin. Writing to the TIM channel 1 registers enables the TIM channel 1 registers to synchronously control the pulse width at the beginning of the next PWM period. At each subsequent overflow, the TIM channel registers (0 or 1) that control the pulse width are the ones written to last. TSC0 controls and monitors the buffered PWM function, and TIM channel 1 status and control register (TSC1) is unused. While the MS0B bit is set, the channel 1 pin, TCH1, is available as a general-purpose I/O pin.

### NOTE

In buffered PWM signal generation, do not write new pulse width values to the currently active channel registers. User software should track the currently active channel to prevent writing a new value to the active channel. Writing to the active channel registers is the same as generating unbuffered PWM signals.

### **Electrical Specifications**

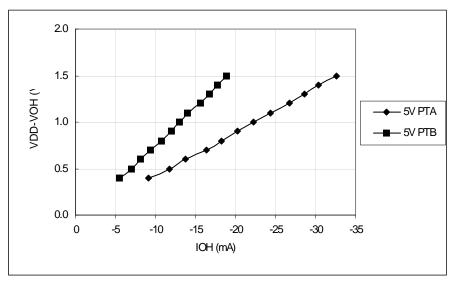

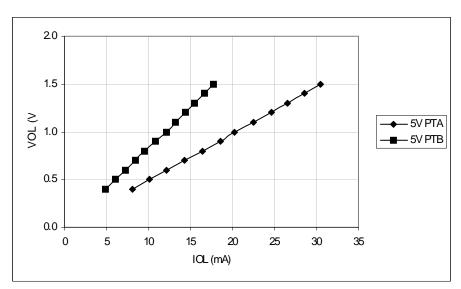

# 16.6 Typical 5-V Output Drive Characteristics

Figure 16-1. Typical 5-Volt Output High Voltage versus Output High Current (25•C)

Figure 16-2. Typical 5-Volt Output Low Voltage versus Output Low Current (25•C)

# 16.14 Analog-to-Digital Converter Characteristics

| Characteristic                                                 | Symbol            | Min                          | Max                          | Unit                     | Comments                                                          |

|----------------------------------------------------------------|-------------------|------------------------------|------------------------------|--------------------------|-------------------------------------------------------------------|

| Supply voltage                                                 | $V_{DDAD}$        | 2.7<br>(V <sub>DD</sub> min) | 5.5<br>(V <sub>DD</sub> max) | V                        | _                                                                 |

| Input voltages                                                 | V <sub>ADIN</sub> | V <sub>SS</sub>              | $V_{DD}$                     | V                        | _                                                                 |

| Resolution<br>(1 LSB)                                          | RES               | 10.5                         | 21.5                         | mV                       | _                                                                 |

| Absolute accuracy<br>(Total unadjusted error)                  | E <sub>TUE</sub>  | _                            | ± 1.5                        | LSB                      | Includes quantization                                             |

| ADC internal clock                                             | f <sub>ADIC</sub> | 0.5                          | 1.048                        | MHz                      | t <sub>ADIC</sub> = 1/f <sub>ADIC</sub> ,<br>tested only at 1 MHz |

| Conversion range                                               | V <sub>AIN</sub>  | V <sub>SS</sub>              | V <sub>DD</sub>              | V                        | _                                                                 |

| Power-up time                                                  | t <sub>ADPU</sub> | 16                           | _                            | t <sub>ADIC</sub> cycles | $t_{ADIC} = 1/f_{ADIC}$                                           |

| Conversion time                                                | t <sub>ADC</sub>  | 16                           | 17                           | t <sub>ADIC</sub> cycles | $t_{ADIC} = 1/f_{ADIC}$                                           |

| Sample time <sup>(1)</sup>                                     | t <sub>ADS</sub>  | 5                            | _                            | t <sub>ADIC</sub> cycles | $t_{ADIC} = 1/f_{ADIC}$                                           |

| Zero input reading <sup>(2)</sup>                              | Z <sub>ADI</sub>  | 00                           | 01                           | Hex                      | $V_{IN} = V_{SS}$                                                 |

| Full-scale reading <sup>(3)</sup>                              | F <sub>ADI</sub>  | FE                           | FF                           | Hex                      | $V_{IN} = V_{DD}$                                                 |

| Input capacitance                                              | C <sub>ADI</sub>  | _                            | 8                            | pF                       | Not tested                                                        |

| Input leakage <sup>(3)</sup>                                   | I <sub>IL</sub>   | _                            | ± 1                          | μΑ                       | _                                                                 |

| ADC supply current V <sub>DD</sub> = 3 V V <sub>DD</sub> = 5 V | I <sub>ADAD</sub> |                              | I = 0.45<br>I = 0.65         | mA<br>mA                 | Enabled<br>Enabled                                                |

<sup>1.</sup> Source impedances greater than 10  $k\Omega$  adversely affect internal RC charging time during input sampling.

<sup>2.</sup> Zero-input/full-scale reading requires sufficient decoupling measures for accurate conversions.

<sup>3.</sup> The external system error caused by input leakage current is approximately equal to the product of R source and input current.

© FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED.

ELECTRONIC VERSIONS ARE UNCONTROLLED EXCEPT WHEN ACCESSED

DIRECTLY FROM THE DOCUMENT CONTROL REPOSITORY. PRINTED VERSIONS

ARE UNCONTROLLED EXCEPT WHEN STAMPED "CONTROLLED COPY" IN RED.

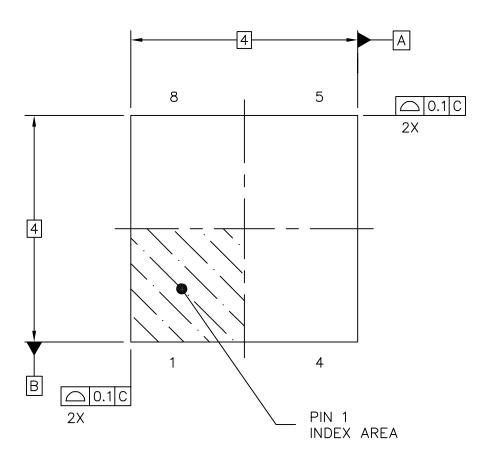

# MECHANICAL OUTLINES DICTIONARY

DO NOT SCALE THIS DRAWING

DOCUMENT NO: 98ARL10557D

PAGE: 1452

REV: A

TITLE: THERMALLY ENHANCED DUAL FLAT NO LEAD PACKAGE (DFN) 8 TERMINAL, 0.8 PITCH (4 X 4 X 1)

CASE NUMBER: 1452-01

STANDARD: NON-JEDEC

PACKAGE CODE: 6165 | SHEET: 1 OF 5