Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                |

| Core Processor             | HC08                                                                    |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 8MHz                                                                    |

| Connectivity               | -                                                                       |

| Peripherals                | LVD, POR, PWM                                                           |

| Number of I/O              | 13                                                                      |

| Program Memory Size        | 1.5KB (1.5K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 128 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                             |

| Data Converters            | A/D 4x8b                                                                |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                      |

| Mounting Type              | Through Hole                                                            |

| Package / Case             | 16-DIP (0.300", 7.62mm)                                                 |

| Supplier Device Package    | 16-PDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc68hc908qy2vpe |

**List of Chapters**

#### LVIPWRD — LVI Power Disable Bit

LVIPWRD disables the LVI module.

- 1 = LVI module power disabled

- 0 = LVI module power enabled

#### LVI5OR3 — LVI 5-V or 3-V Operating Mode Bit

LVI5OR3 selects the voltage operating mode of the LVI module. The voltage mode selected for the LVI should match the operating  $V_{DD}$  for the LVI's voltage trip points for each of the modes.

- 1 = LVI operates in 5-V mode

- 0 = LVI operates in 3-V mode

#### NOTE

The LVI5OR3 bit is cleared by a power-on reset (POR) only. Other resets will leave this bit unaffected.

#### SSREC — Short Stop Recovery Bit

SSREC enables the CPU to exit stop mode with a delay of 32 BUSCLKX4 cycles instead of a 4096 BUSCLKX4 cycle delay.

- 1 = Stop mode recovery after 32 BUSCLKX4 cycles

- 0 = Stop mode recovery after 4096 BUSCLKX4 cycles

#### **NOTE**

Exiting stop mode by an LVI reset will result in the long stop recovery.

The system stabilization time for power-on reset and long stop recovery (both 4096 BUSCLKX4 cycles) gives a delay longer than the LVI enable time for these startup scenarios. There is no period where the MCU is not protected from a low-power condition. However, when using the short stop recovery configuration option, the 32 BUSCLKX4 delay must be greater than the LVI's turn on time to avoid a period in startup where the LVI is not protecting the MCU.

#### STOP — STOP Instruction Enable Bit

STOP enables the STOP instruction.

- 1 = STOP instruction enabled

- 0 = STOP instruction treated as illegal opcode

#### COPD — COP Disable Bit

COPD disables the COP module.

- 1 = COP module disabled

- 0 = COP module enabled

# **Central Processor Unit (CPU)**

# Table 7-1. Instruction Set Summary (Sheet 3 of 6)

| Source                                                                                         | Operation                        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |   | Effect on CCR |   |          |          | Address<br>Mode                                     | Opcode                                           | Operand                                         | les                                  |

|------------------------------------------------------------------------------------------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|---|---------------|---|----------|----------|-----------------------------------------------------|--------------------------------------------------|-------------------------------------------------|--------------------------------------|

| Form                                                                                           | • poration                       | 2000 i piloti                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    | Н | I             | N | Z        | С        | Add<br>Mod                                          | Opc                                              | Ope                                             | Cycles                               |

| CLI                                                                                            | Clear Interrupt Mask             | I ← 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | _  | - | 0             | - | -        | -        | INH                                                 | 9A                                               |                                                 | 2                                    |

| CLR opr<br>CLRA<br>CLRX<br>CLRH<br>CLR opr,X<br>CLR ,X<br>CLR opr,SP                           | Clear                            | M ← \$00<br>A ← \$00<br>X ← \$00<br>H ← \$00<br>M ← \$00<br>M ← \$00                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |   | _             | 0 | 1        | _        | DIR<br>INH<br>INH<br>INH<br>IX1<br>IX<br>SP1        | 3F<br>4F<br>5F<br>8C<br>6F<br>7F<br>9E6F         | ff<br>ff                                        | 3<br>1<br>1<br>3<br>2<br>4           |

| CMP #opr<br>CMP opr<br>CMP opr,<br>CMP opr,X<br>CMP opr,X<br>CMP,X<br>CMP opr,SP<br>CMP opr,SP | Compare A with M                 | (A) – (M)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    | 1 |               | ‡ | 1        | <b>‡</b> | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | A1<br>B1<br>C1<br>D1<br>E1<br>F1<br>9EE1<br>9ED1 | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ff<br>ee ff | 2 3 4 4 3 2 4 5                      |

| COM opr<br>COMA<br>COMX<br>COM opr,X<br>COM ,X<br>COM opr,SP                                   | Complement (One's Complement)    | $\begin{array}{c} M \leftarrow (\overline{M}) = \$FF - (M) \\ A \leftarrow (\overline{A}) = \$FF - (M) \\ X \leftarrow (\overline{X}) = \$FF - (M) \\ M \leftarrow (\overline{M}) = \$FF - (M) \end{array}$                                                                                                                                                                                      |    | _ | _             | 1 | ‡        | 1        | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 33<br>43<br>53<br>63<br>73<br>9E63               | dd<br>ff<br>ff                                  | 4<br>1<br>1<br>4<br>3<br>5           |

| CPHX #opr<br>CPHX opr                                                                          | Compare H:X with M               | (H:X) – (M:M + 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ţ  | - | -             | 1 | 1        | 1        | IMM<br>DIR                                          | 65<br>75                                         | ii ii+1<br>dd                                   | 3<br>4                               |

| CPX #opr<br>CPX opr<br>CPX opr<br>CPX ,X<br>CPX opr,X<br>CPX opr,X<br>CPX opr,SP<br>CPX opr,SP | Compare X with M                 | (X) – (M)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ţ  | - | _             | ‡ | 1        | ‡        | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | A3<br>B3<br>C3<br>D3<br>E3<br>F3<br>9EE3<br>9ED3 |                                                 | 23443245                             |

| DAA                                                                                            | Decimal Adjust A                 | (A) <sub>10</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    | - | -             | ‡ | 1        | 1        | INH                                                 | 72                                               |                                                 | 2                                    |

| DBNZ opr,rel<br>DBNZA rel<br>DBNZX rel<br>DBNZ opr,X,rel<br>DBNZ X,rel<br>DBNZ opr,SP,rel      | Decrement and Branch if Not Zero | $\begin{array}{l} A \leftarrow (A) - 1 \text{ or } M \leftarrow (M) - 1 \text{ or } X \leftarrow (X) - 1 \\ PC \leftarrow (PC) + 3 + rel? \text{ (result)} \neq 0 \\ PC \leftarrow (PC) + 2 + rel? \text{ (result)} \neq 0 \\ PC \leftarrow (PC) + 2 + rel? \text{ (result)} \neq 0 \\ PC \leftarrow (PC) + 3 + rel? \text{ (result)} \neq 0 \\ PC \leftarrow (PC) + 2 + rel? \text{ (result)} \neq 0 \\ PC \leftarrow (PC) + 4 + rel? \text{ (result)} \neq 0 \\ PC \leftarrow (PC) + 4 + rel? \text{ (result)} \neq 0 \end{array}$ | _  | _ | _             | - | -        | _        | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 3B<br>4B<br>5B<br>6B<br>7B<br>9E6B               | dd rr<br>rr<br>rr<br>ff rr<br>rr<br>ff rr       | 533546                               |

| DEC opr<br>DECA<br>DECX<br>DEC opr,X<br>DEC ,X<br>DEC opr,SP                                   | Decrement                        | $\begin{array}{l} M \leftarrow (M) - 1 \\ A \leftarrow (A) - 1 \\ X \leftarrow (X) - 1 \\ M \leftarrow (M) - 1 \\ M \leftarrow (M) - 1 \\ M \leftarrow (M) - 1 \end{array}$                                                                                                                                                                                                                                                                                                                                                          | Į. | _ | _             | 1 | 1        | -        | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 3A<br>4A<br>5A<br>6A<br>7A<br>9E6A               | dd<br>ff<br>ff                                  | 4<br>1<br>1<br>4<br>3<br>5           |

| DIV                                                                                            | Divide                           | A ← (H:A)/(X)<br>H ← Remainder                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    | _ | _             | - | 1        | 1        | INH                                                 | 52                                               |                                                 | 7                                    |

| EOR #opr<br>EOR opr<br>EOR opr,X<br>EOR opr,X<br>EOR,X<br>EOR,X<br>EOR opr,SP<br>EOR opr,SP    | Exclusive OR M with A            | $A \leftarrow (A \oplus M)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0  | _ | _             | 1 | 1        | _        | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | A8<br>B8<br>C8<br>D8<br>E8<br>F8<br>9EE8<br>9ED8 | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ee ff       | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5 |

| INC opr<br>INCA<br>INCX<br>INC opr,X<br>INC ,X<br>INC opr,SP                                   | Increment                        | $ \begin{array}{c} M \leftarrow (M) + 1 \\ A \leftarrow (A) + 1 \\ X \leftarrow (X) + 1 \\ M \leftarrow (M) + 1 \\ M \leftarrow (M) + 1 \\ M \leftarrow (M) + 1 \end{array} $                                                                                                                                                                                                                                                                                                                                                        | 1  | _ | _             | ‡ | <b>†</b> | _        | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 3C<br>4C<br>5C<br>6C<br>7C<br>9E6C               | dd<br>ff<br>ff                                  | 4<br>1<br>1<br>4<br>3<br>5           |

# Chapter 8 External Interrupt (IRQ)

#### 8.1 Introduction

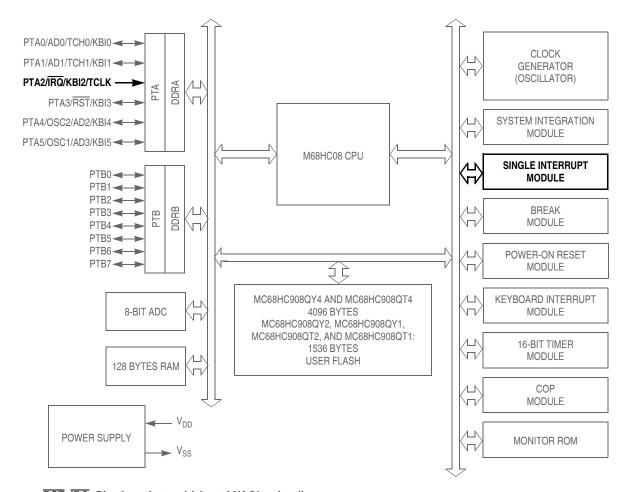

The IRQ pin (external interrupt), shared with PTA2 (general purpose input) and keyboard interrupt (KBI), provides a maskable interrupt input

#### 8.2 Features

Features of the IRQ module include the following:

- External interrupt pin, IRQ

- IRQ interrupt control bits

- Programmable edge-only or edge and level interrupt sensitivity

- Automatic interrupt acknowledge

- Selectable internal pullup resistor

# 8.3 Functional Description

IRQ pin functionality is enabled by setting configuration register 2 (CONFIG2) IRQEN bit accordingly. A zero disables the IRQ function and PTA2 will assume the other shared functionalities. A one enables the IRQ function.

A low level applied to the external interrupt request  $(\overline{IRQ})$  pin can latch a CPU interrupt request. Figure 8-2 shows the structure of the IRQ module.

Interrupt signals on the  $\overline{IRQ}$  pin are latched into the IRQ latch. The IRQ latch remains set until one of the following actions occurs:

- IRQ vector fetch An IRQ vector fetch automatically generates an interrupt acknowledge signal that clears the IRQ latch.

- Software clear Software can clear the IRQ latch by writing a 1 to the ACK bit in the interrupt status and control register (INTSCR).

- Reset A reset automatically clears the IRQ latch.

The external interrupt pin is falling-edge-triggered out of reset and is software-configurable to be either falling-edge or falling-edge and low-level triggered. The MODE bit in INTSCR controls the triggering sensitivity of the IRQ pin.

#### **External Interrupt (IRQ)**

#### RST, IRQ: Pins have internal (about 30K Ohms) pull up

PTA[0:5]: High current sink and source capability

PTA[0:5]: Pins have programmable keyboard interrupt and pull up

PTB[0:7]: Not available on 8-pin devices – MC68HC908QT1, MC68HC908QT2, and MC68HC908QT4 (see note in 12.1 Introduction)

ADC: Not available on the MC68HC908QY1 and MC68HC908QT1

Figure 8-1. Block Diagram Highlighting IRQ Block and Pins

When set, the IMASK bit in INTSCR masks the IRQ interrupt request. A latched interrupt request is not presented to the interrupt priority logic unless IMASK is clear.

#### **NOTE**

The interrupt mask (I) in the condition code register (CCR) masks all interrupt requests, including the IRQ interrupt request.

A falling edge on the  $\overline{IRQ}$  pin can latch an interrupt request into the IRQ latch. An IRQ vector fetch, software clear, or reset clears the IRQ latch.

**Oscillator Module (OSC)**

#### 11.4.2 Crystal Amplifier Output Pin (OSC2/PTA4/BUSCLKX4)

For the XTAL oscillator device, the OSC2 pin is the crystal oscillator inverting amplifier output.

For the external clock option, the OSC2 pin is dedicated to the PTA4 I/O function. The OSC2EN bit has no effect.

For the internal oscillator or RC oscillator options, the OSC2 pin can assume other functions according to Table 1-3. Function Priority in Shared Pins, or the output of the oscillator clock (BUSCLKX4).

Option

XTAL oscillator

External clock

Internal oscillator or RC oscillator

OSC2 Pin Function

Inverting OSC1

PTA4 I/O

Controlled by OSC2EN bit in PTAPUE register

OSC2EN = 0: PTA4 I/O

OSC2EN = 1: BUSCLKX4 output

**Table 11-1. OSC2 Pin Function**

### 11.4.3 Oscillator Enable Signal (SIMOSCEN)

The SIMOSCEN signal comes from the system integration module (SIM) and enables/disables either the XTAL oscillator circuit, the RC oscillator, or the internal oscillator.

#### 11.4.4 XTAL Oscillator Clock (XTALCLK)

XTALCLK is the XTAL oscillator output signal. It runs at the full speed of the crystal ( $f_{XCLK}$ ) and comes directly from the crystal oscillator circuit. Figure 11-2 shows only the logical relation of XTALCLK to OSC1 and OSC2 and may not represent the actual circuitry. The duty cycle of XTALCLK is unknown and may depend on the crystal and other external factors. Also, the frequency and amplitude of XTALCLK can be unstable at start up.

# 11.4.5 RC Oscillator Clock (RCCLK)

RCCLK is the RC oscillator output signal. Its frequency is directly proportional to the time constant of external R and internal C. Figure 11-3 shows only the logical relation of RCCLK to OSC1 and may not represent the actual circuitry.

## 11.4.6 Internal Oscillator Clock (INTCLK)

INTCLK is the internal oscillator output signal. Its nominal frequency is fixed to 12.8 MHz, but it can be also trimmed using the oscillator trimming feature of the OSCTRIM register (see 11.3.1.1 Internal Oscillator Trimming).

#### 11.4.7 Oscillator Out 2 (BUSCLKX4)

BUSCLKX4 is the same as the input clock (XTALCLK, RCCLK, or INTCLK). This signal is driven to the SIM module and is used to determine the COP cycles.

#### 11.4.8 Oscillator Out (BUSCLKX2)

The frequency of this signal is equal to half of the BUSCLKX4, this signal is driven to the SIM for generation of the bus clocks used by the CPU and other modules on the MCU. BUSCLKX2 will be divided

MC68HC908QY/QT Family Data Sheet, Rev. 6

again in the SIM and results in the internal bus frequency being one fourth of either the XTALCLK, RCCLK, or INTCLK frequency.

#### 11.5 Low Power Modes

The WAIT and STOP instructions put the MCU in low-power consumption standby modes.

#### 11.5.1 Wait Mode

The WAIT instruction has no effect on the oscillator logic. BUSCLKX2 and BUSCLKX4 continue to drive to the SIM module.

#### 11.5.2 Stop Mode

The STOP instruction disables either the XTALCLK, the RCCLK, or INTCLK output, hence BUSCLKX2 and BUSCLKX4.

# 11.6 Oscillator During Break Mode

The oscillator continues to drive BUSCLKX2 and BUSCLKX4 when the device enters the break state.

# 11.7 CONFIG2 Options

Two CONFIG2 register options affect the operation of the oscillator module: OSCOPT1 and OSCOPT0. All CONFIG2 register bits will have a default configuration. Refer to Chapter 5 Configuration Register (CONFIG) for more information on how the CONFIG2 register is used.

Table 11-2 shows how the OSCOPT bits are used to select the oscillator clock source.

OSCOPT1

OSCOPT0

Oscillator Modes

0

0

Internal oscillator

0

1

External oscillator

1

0

External RC

1

1

External crystal

Table 11-2. Oscillator Modes

# 11.8 Input/Output (I/O) Registers

The oscillator module contains these two registers:

- 1. Oscillator status register (OSCSTAT)

- 2. Oscillator trim register (OSCTRIM)

Freescale Semiconductor 95

MC68HC908QY/QT Family Data Sheet, Rev. 6

**System Integration Module (SIM)**

#### 13.6.3 Reset

All reset sources always have equal and highest priority and cannot be arbitrated.

#### 13.6.4 Break Interrupts

The break module can stop normal program flow at a software programmable break point by asserting its break interrupt output. (See Chapter 15 Development Support.) The SIM puts the CPU into the break state by forcing it to the SWI vector location. Refer to the break interrupt subsection of each module to see how each module is affected by the break state.

#### 13.6.5 Status Flag Protection in Break Mode

The SIM controls whether status flags contained in other modules can be cleared during break mode. The user can select whether flags are protected from being cleared by properly initializing the break clear flag enable bit (BCFE) in the break flag control register (BFCR).

Protecting flags in break mode ensures that set flags will not be cleared while in break mode. This protection allows registers to be freely read and written during break mode without losing status flag information.

Setting the BCFE bit enables the clearing mechanisms. Once cleared in break mode, a flag remains cleared even when break mode is exited. Status flags with a two-step clearing mechanism — for example, a read of one register followed by the read or write of another — are protected, even when the first step is accomplished prior to entering break mode. Upon leaving break mode, execution of the second step will clear the flag as normal.

#### 13.7 Low-Power Modes

Executing the WAIT or STOP instruction puts the MCU in a low power- consumption mode for standby situations. The SIM holds the CPU in a non-clocked state. The operation of each of these modes is described below. Both STOP and WAIT clear the interrupt mask (I) in the condition code register, allowing interrupts to occur.

#### 13.7.1 Wait Mode

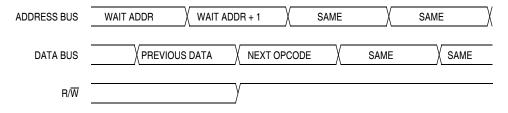

In wait mode, the CPU clocks are inactive while the peripheral clocks continue to run. Figure 13-14 shows the timing for wait mode entry.

NOTE: Previous data can be operand data or the WAIT opcode, depending on the last instruction.

Figure 13-14. Wait Mode Entry Timing

MC68HC908QY/QT Family Data Sheet, Rev. 6

# **Chapter 14 Timer Interface Module (TIM)**

#### 14.1 Introduction

This section describes the timer interface module (TIM). The TIM is a two-channel timer that provides a timing reference with input capture, output compare, and pulse-width-modulation functions. Figure 14-2 is a block diagram of the TIM.

#### 14.2 Features

Features of the TIM include the following:

- Two input capture/output compare channels

- Rising-edge, falling-edge, or any-edge input capture trigger

- Set, clear, or toggle output compare action

- Buffered and unbuffered pulse width modulation (PWM) signal generation

- Programmable TIM clock input

- 7-frequency internal bus clock prescaler selection

- External TIM clock input

- Free-running or modulo up-count operation

- Toggle any channel pin on overflow

- TIM counter stop and reset bits

#### 14.3 Pin Name Conventions

The TIM shares two input/output (I/O) pins with two port A I/O pins. The full names of the TIM I/O pins are listed in Table 14-1. The generic pin name appear in the text that follows.

**Table 14-1. Pin Name Conventions**

| TIM Generic Pin Names: | TCH0      | TCH1      | TCLK      |  |  |

|------------------------|-----------|-----------|-----------|--|--|

| Full TIM Pin Names:    | PTA0/TCH0 | PTA1/TCH1 | PTA2/TCLK |  |  |

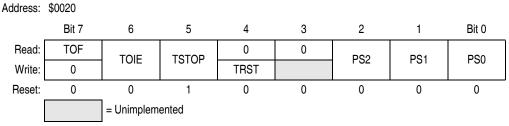

### 14.9.1 TIM Status and Control Register

The TIM status and control register (TSC) does the following:

- Enables TIM overflow interrupts

- Flags TIM overflows

- Stops the TIM counter

- Resets the TIM counter

- Prescales the TIM counter clock

Figure 14-4. TIM Status and Control Register (TSC)

#### **TOF** — **TIM** Overflow Flag Bit

This read/write flag is set when the TIM counter reaches the modulo value programmed in the TIM counter modulo registers. Clear TOF by reading the TIM status and control register when TOF is set and then writing a 0 to TOF. If another TIM overflow occurs before the clearing sequence is complete, then writing 0 to TOF has no effect. Therefore, a TOF interrupt request cannot be lost due to inadvertent clearing of TOF. Reset clears the TOF bit. Writing a 1 to TOF has no effect.

- 1 = TIM counter has reached modulo value

- 0 = TIM counter has not reached modulo value

#### **TOIE** — **TIM** Overflow Interrupt Enable Bit

This read/write bit enables TIM overflow interrupts when the TOF bit becomes set. Reset clears the TOIE bit.

- 1 = TIM overflow interrupts enabled

- 0 = TIM overflow interrupts disabled

#### TSTOP — TIM Stop Bit

This read/write bit stops the TIM counter. Counting resumes when TSTOP is cleared. Reset sets the TSTOP bit, stopping the TIM counter until software clears the TSTOP bit.

- 1 = TIM counter stopped

- 0 = TIM counter active

#### NOTE

Do not set the TSTOP bit before entering wait mode if the TIM is required to exit wait mode. When the TSTOP bit is set and the timer is configured for input capture operation, input captures are inhibited until the TSTOP bit is cleared.

When using TSTOP to stop the timer counter, see if any timer flags are set. If a timer flag is set, it must be cleared by clearing TSTOP, then clearing the flag, then setting TSTOP again.

When ELSxB:A = 00, this read/write bit selects the initial output level of the TCHx pin (see Table 14-3). Reset clears the MSxA bit.

- 1 = Initial output level low

- 0 = Initial output level high

#### NOTE

Before changing a channel function by writing to the MSxB or MSxA bit, set the TSTOP and TRST bits in the TIM status and control register (TSC).

Table 14-3. Mode, Edge, and Level Selection

| MSxB | MSxA | ELSxB | ELSxA | Mode            | Configuration                                     |

|------|------|-------|-------|-----------------|---------------------------------------------------|

| Х    | 0    | 0     | 0     | Output preset   | Pin under port control; initial output level high |

| Х    | 1    | 0     | 0     | Output preset   | Pin under port control; initial output level low  |

| 0    | 0    | 0     | 1     |                 | Capture on rising edge only                       |

| 0    | 0    | 1     | 0     | Input capture   | Capture on falling edge only                      |

| 0    | 0    | 1     | 1     |                 | Capture on rising or falling edge                 |

| 0    | 1    | 0     | 0     |                 | Software compare only                             |

| 0    | 1    | 0     | 1     | Output compare  | Toggle output on compare                          |

| 0    | 1    | 1     | 0     | or PWM          | Clear output on compare                           |

| 0    | 1    | 1     | 1     |                 | Set output on compare                             |

| 1    | Х    | 0     | 1     | Buffered output | Toggle output on compare                          |

| 1    | Х    | 1     | 0     | compare or      | Clear output on compare                           |

| 1    | Х    | 1     | 1     | buffered PWM    | Set output on compare                             |

#### ELSxB and ELSxA — Edge/Level Select Bits

When channel x is an input capture channel, these read/write bits control the active edge-sensing logic on channel x.

When channel x is an output compare channel, ELSxB and ELSxA control the channel x output behavior when an output compare occurs.

When ELSxB and ELSxA are both clear, channel x is not connected to an I/O port, and pin TCHx is available as a general-purpose I/O pin. Table 14-3 shows how ELSxB and ELSxA work. Reset clears the ELSxB and ELSxA bits.

#### NOTE

After initially enabling a TIM channel register for input capture operation and selecting the edge sensitivity, clear CHxF to ignore any erroneous edge detection flags.

#### TOVx — Toggle-On-Overflow Bit

When channel x is an output compare channel, this read/write bit controls the behavior of the channel x output when the TIM counter overflows. When channel x is an input capture channel, TOVx has no effect Reset clears the TOVx bit.

- 1 = Channel x pin toggles on TIM counter overflow.

- 0 = Channel x pin does not toggle on TIM counter overflow.

#### NOTE

When TOVx is set, a TIM counter overflow takes precedence over a channel x output compare if both occur at the same time.

MC68HC908QY/QT Family Data Sheet, Rev. 6

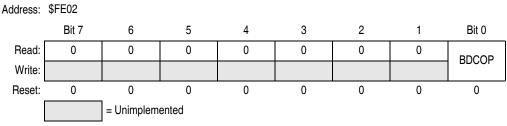

#### 15.2.2.3 Break Auxiliary Register

The break auxiliary register (BRKAR) contains a bit that enables software to disable the COP while the MCU is in a state of break interrupt with monitor mode.

Figure 15-6. Break Auxiliary Register (BRKAR)

#### BDCOP — Break Disable COP Bit

This read/write bit disables the COP during a break interrupt. Reset clears the BDCOP bit.

- 1 = COP disabled during break interrupt

- 0 = COP enabled during break interrupt

#### 15.2.2.4 Break Status Register

The break status register (BSR) contains a flag to indicate that a break caused an exit from wait mode. This register is only used in emulation mode.

Figure 15-7. Break Status Register (BSR)

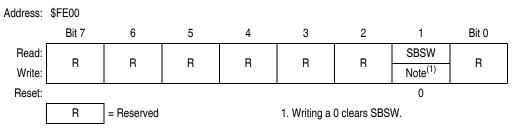

#### SBSW — SIM Break Stop/Wait

SBSW can be read within the break state SWI routine. The user can modify the return address on the stack by subtracting one from it.

- 1 = Wait mode was exited by break interrupt

- 0 = Wait mode was not exited by break interrupt

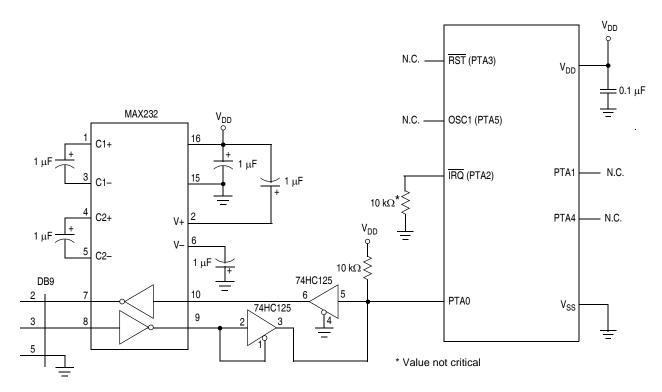

Figure 15-12. Monitor Mode Circuit (Internal Clock, No High Voltage)

Simple monitor commands can access any memory address. In monitor mode, the MCU can execute code downloaded into RAM by a host computer while most MCU pins retain normal operating mode functions. All communication between the host computer and the MCU is through the PTA0 pin. A level-shifting and multiplexing interface is required between PTA0 and the host computer. PTA0 is used in a wired-OR configuration and requires a pullup resistor.

The monitor code has been updated from previous versions of the monitor code to allow enabling the internal oscillator to generate the internal clock. This addition, which is enabled when  $\overline{IRQ}$  is held low out of reset, is intended to support serial communication/programming at 9600 baud in monitor mode by using the internal oscillator, and the internal oscillator user trim value OSCTRIM (FLASH location \$FFC0, if programmed) to generate the desired internal frequency (3.2 MHz). Since this feature is enabled only when  $\overline{IRQ}$  is held low out of reset, it cannot be used when the reset vector is programmed (i.e., the value is not \$FFFF) because entry into monitor mode in this case requires  $V_{TST}$  on  $\overline{IRQ}$ . The  $\overline{IRQ}$  pin must remain low during this monitor session in order to maintain communication.

Table 15-1 shows the pin conditions for entering monitor mode. As specified in the table, monitor mode may be entered after a power-on reset (POR) and will allow communication at 9600 baud provided one of the following sets of conditions is met:

- If \$FFFE and \$FFFF do not contain \$FF (programmed state):

- The external clock is 9.8304 MHz

- $\overline{IRQ} = V_{TST}$

- If \$FFFE and \$FFFF contain \$FF (erased state):

- The external clock is 9.8304 MHz

- $-\overline{IRQ} = V_{DD}$  (this can be implemented through the internal  $\overline{IRQ}$  pullup)

- If \$FFFE and \$FFFF contain \$FF (erased state):

- $\overline{IRQ} = V_{SS}$  (internal oscillator is selected, no external clock required)

MC68HC908QY/QT Family Data Sheet, Rev. 6

#### **Electrical Specifications**

# 16.12 3-V Oscillator Characteristics

| Characteristic                                                                                                                                                                            | Symbol              | Min         | Тур                | Max         | Unit |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-------------|--------------------|-------------|------|

| Internal oscillator frequency <sup>(1)</sup>                                                                                                                                              | f <sub>INTCLK</sub> | _           | 12.8               | _           | MHz  |

| Deviation from trimmed Internal oscillator <sup>(2)(3)</sup> 12.8 MHz, fixed voltage, fixed temp 12.8 MHz, V <sub>DD</sub> ± 10%, 0 to 70°C 12.8 MHz, V <sub>DD</sub> ± 10%, –40 to 125°C | ACC <sub>INT</sub>  | _<br>_<br>_ | ± 0.4<br>± 2<br>—  | <br><br>± 5 | %    |

| Crystal frequency, XTALCLK <sup>(1)</sup>                                                                                                                                                 | foscxclk            | 1           | _                  | 16          | MHz  |

| External RC oscillator frequency, RCCLK (1)                                                                                                                                               | f <sub>RCCLK</sub>  | 2           | _                  | 10          | MHz  |

| External clock reference frequency <sup>(1)</sup> (4)                                                                                                                                     | foscxclk            | dc          | _                  | 16          | MHz  |

| Crystal load capacitance <sup>(5)</sup>                                                                                                                                                   | CL                  | _           | 20                 | _           | pF   |

| Crystal fixed capacitance <sup>(3)</sup>                                                                                                                                                  | C <sub>1</sub>      | _           | 2 x C <sub>L</sub> | _           | _    |

| Crystal tuning capacitance <sup>(3)</sup>                                                                                                                                                 | C <sub>2</sub>      | _           | 2 x C <sub>L</sub> | _           | _    |

| Feedback bias resistor                                                                                                                                                                    | R <sub>B</sub>      | 0.5         | 1                  | 10          | МΩ   |

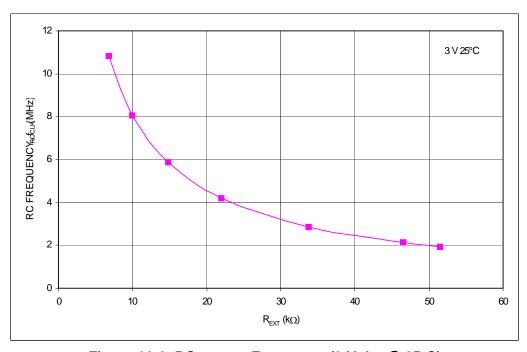

| RC oscillator external resistor                                                                                                                                                           | R <sub>EXT</sub>    |             | See Figure 16-     | -8          | _    |

| Crystal series damping resistor  f <sub>OSCXCLK</sub> = 1 MHz  f <sub>OSCXCLK</sub> = 4 MHz  f <sub>OSCXCLK</sub> = > 8 MHz                                                               | R <sub>S</sub>      | _<br>_<br>_ | 10<br>5<br>0       | _<br>_<br>_ | kΩ   |

- Bus frequency, f<sub>OP</sub>, is oscillator frequency divided by 4.

Deviation values assumes trimming @25•C and midpoint of voltage range.

Values are based on characterization results, not tested in production.

- 4. No more than 10% duty cycle deviation from 50%

- 5. Consult crystal vendor data sheet

Figure 16-8. RC versus Frequency (3 Volts @ 25•C)

MC68HC908QY/QT Family Data Sheet, Rev. 6

#### **Electrical Specifications**

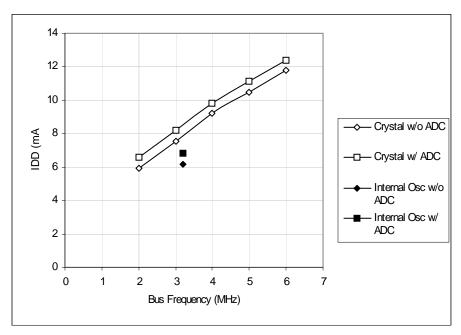

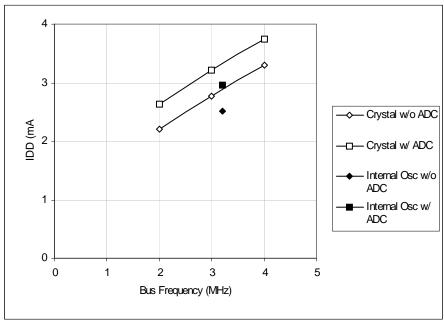

Figure 16-9. Typical 5-Volt Run Current versus Bus Frequency (25•C)

Figure 16-10. Typical 3-Volt Run Current versus Bus Frequency (25•C)

© FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED.

ELECTRONIC VERSIONS ARE UNCONTROLLED EXCEPT WHEN ACCESSED

DIRECTLY FROM THE DISCUMENT CONTROL REPOSITIORY, PRINTED

VERSIONS ARE UNCONTROLLED EXCEPT WHEN STAMPED "CONTROLLED

COPY" IN FED.

| MECHANICAL | DUTLINES |

|------------|----------|

| חורדוחו    | JARY     |

DO NOT SCALE THIS DRAWING

| DOCUMENT | N□: | 98ASH70107A |  |

|----------|-----|-------------|--|

| PAGE:    |     | 968         |  |

|          |     |             |  |

REV:

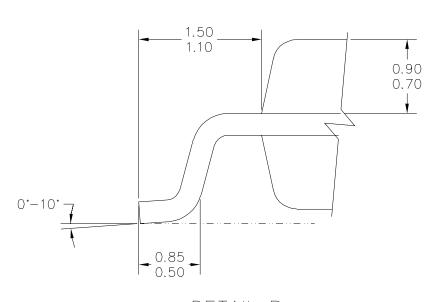

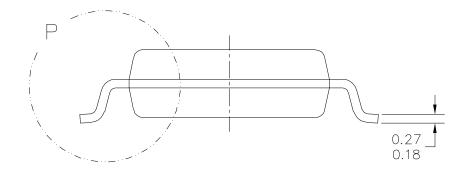

| TITLE:     | CASE NUMBER: 968-02              |  |  |  |  |  |

|------------|----------------------------------|--|--|--|--|--|

| 8 LEAD MFP | STANDARD: EIAJ                   |  |  |  |  |  |

|            | PACKAGE CODE: 6003 SHEET: 2 OF 4 |  |  |  |  |  |

Semiconductor

© FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED.

ELECTRONIC VERSIONS ARE UNCONTROLLED EXCEPT WHEN ACCESSED

DIRECTLY FROM THE DOCUMENT CONTROL REPOSITORY, PRINTED

VERSIONS ARE UNCONTROLLED EXCEPT WHEN STAMPED "CONTROLLED

COPY" IN RED.

#### MECHANICAL OUTLINES DICTIONARY

DOCUMENT NO: 98ASH70107A

PAGE:

968

DO NOT SCALE THIS DRAWING

REV: Α

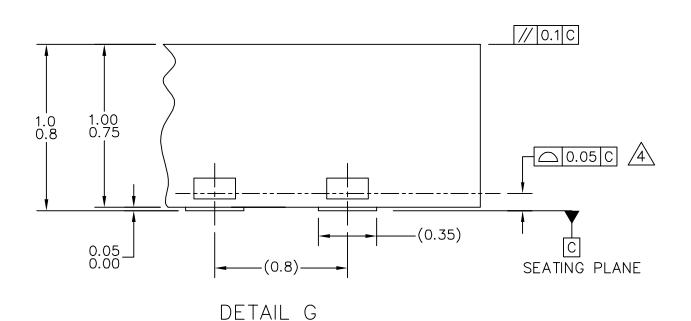

#### NOTES:

- 1. DIMENSIONS AND TOLERANCES PER ASME Y14.5-1994.

- 2. CONTROLLING DIMENSION: MILLIMETER.

/3\ DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS AND ARE MEASURED AT THE PARTING LINE. MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEDD 0.15mm PER SIDE.

4. TERMINAL NUMBERS ARE SHOWN FOR REFERENCE ONLY.

$\sqrt{5}$ \ THE LEAD WIDTH DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION SHALL BE 0.08mm TOTAL IN EXCESS OF THE LEAD WIDTH DIMENSION AT MAXIMUM MATERIAL CONDITION. DAMBAR CANNOT BE LOCATED ON THE LOWER RADIUS OR THE FOOT. MINIMUM SPACE BETWEEN PROTRUSIONS AND ADJACENT LEAD TO BE 0.46mm.

TITLE: CASE NUMBER: 968-02 8 LEAD MFP STANDARD: EIAJ PACKAGE CODE: 6003 SHEET: 3 OF 4

© FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED.

ELECTRONIC VERSIONS ARE UNCONTROLLED EXCEPT WHEN ACCESSED

DIRECTLY FROM THE DOCUMENT CONTROL REPOSITORY. PRINTED VERSIONS

ARE UNCONTROLLED EXCEPT WHEN STAMPED "CONTROLLED COPY" IN RED

# MECHANICAL OUTLINES DICTIONARY

DO NOT SCALE THIS DRAWING

DOCUMENT NO: 98ARL10557D

PAGE: 1452

REV: A

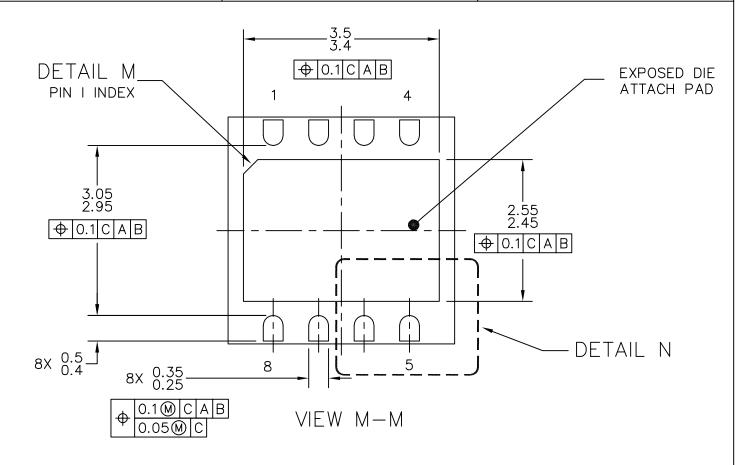

TITLE: THERMALLY ENHANCED DUAL FLAT NO LEAD PACKAGE (DFN) 8 TERMINAL, 0.8 PITCH (4 X 4 X 1)

CASE NUMBER: 1452-01

STANDARD: NON-JEDEC

PACKAGE CODE: 6165 | SHEET: 2 OF 5

\*\*Semiconductor\*

© FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED.

ELECTRONIC VERSIONS ARE UNCONTROLLED EXCEPT WHEN ACCESSED

DIRECTLY FROM THE DOCUMENT CONTROL REPOSITORY, PRINTED

VERSIONS ARE UNCONTROLLED EXCEPT WHEN STAMPED "CONTROLLED

COPY" IN RED.

# MECHANICAL OUTLINES DICTIONARY

DOCUMENT NO: 98ARL10557D

PAGE:

1452

DO NOT SCALE THIS DRAWING

REV:

#### NOTES:

- 1. ALL DIMENSIONS ARE IN MILLIMETERS.

- 2. INTERPRET DIMENSIONS AND TOLERANCES PER ASME Y14.5M-1994.

- 3. THE COMPLETE JEDEC DESIGNATOR FOR THIS PACKAGE IS: HP-VFDFP-N.

4.

COPLANARITY APPLIES TO LEADS AND DIE ATTACH PAD.

FLAT NO LEAD PACKAGE (DFN)

8 TERMINAL, 0.8 PITCH(4 X 4 X 1)

CASE NUMBER: 1452-01

STANDARD: NON-JEDEC

PACKAGE CODE: 6165

SHEET: 4 OF 5