Welcome to **E-XFL.COM**

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                              |

|----------------------------|--------------------------------------------------------------|

| Product Status             | Obsolete                                                     |

| Core Processor             | HC08                                                         |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 8MHz                                                         |

| Connectivity               | -                                                            |

| Peripherals                | LVD, POR, PWM                                                |

| Number of I/O              | 13                                                           |

| Program Memory Size        | 4KB (4K x 8)                                                 |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | -                                                            |

| RAM Size                   | 128 x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                  |

| Data Converters            | A/D 4x8b                                                     |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                           |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 16-TSSOP (0.173", 4.40mm Width)                              |

| Supplier Device Package    | 16-TSSOP                                                     |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc68hc908gy4mdt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Revision History**

The following revision history table summarizes changes contained in this document. For your convenience, the page number designators have been linked to the appropriate location.

# **Revision History (Sheet 1 of 3)**

| Date               | Revision<br>Level | Description                                                                                                                                                            |     |

|--------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| September,<br>2002 | N/A               | Initial release                                                                                                                                                        | N/A |

|                    |                   | 1.2 Features — Added 8-pin dual flat no lead (DFN) packages to features list.                                                                                          | 19  |

|                    |                   | Figure 1-2. MCU Pin Assignments — Figure updated to include DFN packages.                                                                                              | 21  |

|                    |                   | Figure 2-1. Memory Map — Clarified illegal address and unimplemented memory.                                                                                           | 27  |

|                    |                   | Figure 2-2. Control, Status, and Data Registers — Corrected bit definitions for Port A Data Register (PTA) and Data Direction Register A (DDRA).                       | 27  |

|                    |                   | Table 13-3. Interrupt Sources — Corrected vector addresses for keyboard interrupt and ADC conversion complete interrupt.                                               | 118 |

|                    |                   | Chapter 13 System Integration Module (SIM) — Removed reference to break status register as it is duplicated in break module.                                           | 113 |

|                    |                   | 11.3.1 Internal Oscillator and 11.3.1.1 Internal Oscillator Trimming — Clarified oscillator trim option ordering information and what to expect with untrimmed device. | 92  |

|                    |                   | Figure 11-5. Oscillator Trim Register (OSCTRIM) — Bit 1 designation corrected.                                                                                         | 98  |

| December,          |                   | Figure 15-13. Monitor Mode Circuit (Internal Clock, No High Voltage) — Diagram updated for clarity.                                                                    | 150 |

| 2002               | 0.1               | Figure 12-1. I/O Port Register Summary — Corrected bit definitions for PTA7, DDRA7, and DDRA6.                                                                         | 99  |

|                    |                   | Figure 12-2. Port A Data Register (PTA) — Corrected bit definition for PTA7.                                                                                           | 100 |

|                    |                   | Figure 12-3. Data Direction Register A (DDRA) — Corrected bit definitions for DDRA7 and DDRA6.                                                                         | 101 |

|                    |                   | Figure 12-6. Port B Data Register (PTB) — Corrected bit definition for PTB1                                                                                            | 103 |

|                    |                   | Chapter 9 Keyboard Interrupt Module (KBI) — Section reworked after deletion of auto wakeup for clarity.                                                                | 83  |

|                    |                   | Chapter 4 Auto Wakeup Module (AWU) — New section added for clarity.                                                                                                    | 49  |

|                    |                   | Figure 10-1. LVI Module Block Diagram — Corrected LVI stop representation.                                                                                             | 87  |

|                    |                   | Chapter 16 Electrical Specifications — Extensive changes made to electrical specifications.                                                                            | 169 |

|                    |                   | 17.5 8-Pin Dual Flat No Lead (DFN) Package (Case #1452) — Added case outline drawing for DFN package.                                                                  | 177 |

|                    |                   | Chapter 17 Ordering Information and Mechanical Specifications — Added ordering information for DFN package.                                                            | 185 |

| January,<br>2003   | 0.2               | 4.2 Features — Corrected third bulleted item.                                                                                                                          | 49  |

# **General Description**

# 1.5 Pin Functions

Table 1-2 provides a description of the pin functions.

**Table 1-2. Pin Functions**

| Pin<br>Name             | Description                                                                                                      | Input/Output     |

|-------------------------|------------------------------------------------------------------------------------------------------------------|------------------|

| $V_{DD}$                | Power supply                                                                                                     | Power            |

| $V_{SS}$                | Power supply ground                                                                                              | Power            |

|                         | PTA0 — General purpose I/O port                                                                                  | Input/Output     |

| PTA0                    | AD0 — A/D channel 0 input                                                                                        | Input            |

| PIAU                    | TCH0 — Timer Channel 0 I/O                                                                                       | Input/Output     |

|                         | KBI0 — Keyboard interrupt input 0                                                                                | Input            |

|                         | PTA1 — General purpose I/O port                                                                                  | Input/Output     |

| PTA1                    | AD1 — A/D channel 1 input                                                                                        | Input            |

| FIAI                    | TCH1 — Timer Channel 1 I/O                                                                                       | Input/Output     |

|                         | KBI1 — Keyboard interrupt input 1                                                                                | Input            |

|                         | PTA2 — General purpose input-only port                                                                           | Input            |

| PTA2                    | IRQ — External interrupt with programmable pullup and Schmitt trigger input                                      | Input            |

| FIAZ                    | KBI2 — Keyboard interrupt input 2                                                                                | Input            |

|                         | TCLK — Timer clock input                                                                                         | Input            |

|                         | PTA3 — General purpose I/O port                                                                                  | Input/Output     |

| PTA3                    | RST — Reset input, active low with internal pullup and Schmitt trigger                                           | Input            |

|                         | KBI3 — Keyboard interrupt input 3                                                                                | Input            |

|                         | PTA4 — General purpose I/O port                                                                                  | Input/Output     |

| PTA4                    | OSC2 —XTAL oscillator output (XTAL option only) RC or internal oscillator output (OSC2EN = 1 in PTAPUE register) | Output<br>Output |

|                         | AD2 — A/D channel 2 input                                                                                        | Input            |

|                         | KBI4 — Keyboard interrupt input 4                                                                                | Input            |

|                         | PTA5 — General purpose I/O port                                                                                  | Input/Output     |

| PTA5                    | OSC1 — XTAL, RC, or external oscillator input                                                                    | Input            |

| r IAO                   | AD3 — A/D channel 3 input                                                                                        | Input            |

|                         | KBI5 — Keyboard interrupt input 5                                                                                | Input            |

| PTB[0:7] <sup>(1)</sup> | 8 general-purpose I/O ports                                                                                      | Input/Output     |

|                         |                                                                                                                  |                  |

<sup>1.</sup> The PTB pins are not available on the 8-pin packages (see note in 12.1 Introduction).

# 2.4 Input/Output (I/O) Section

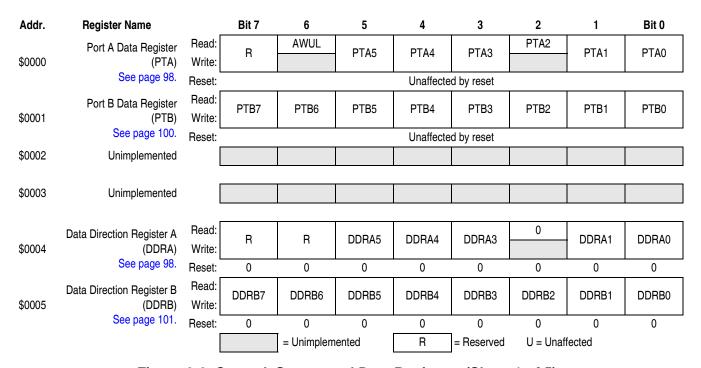

Addresses \$0000–\$003F, shown in Figure 2-2, contain most of the control, status, and data registers. Additional I/O registers have these addresses:

- \$FE00 Break status register, BSR

- \$FE01 Reset status register, SRSR

- \$FE02 Break auxiliary register, BRKAR

- \$FE03 Break flag control register, BFCR

- \$FE04 Interrupt status register 1, INT1

- \$FE05 Interrupt status register 2, INT2

- \$FE06 Interrupt status register 3, INT3

- \$FE07 Reserved

- \$FE08 FLASH control register, FLCR

- \$FE09 Break address register high, BRKH

- \$FE0A Break address register low, BRKL

- \$FE0B Break status and control register, BRKSCR

- \$FE0C LVI status register, LVISR

- \$FE0D Reserved

- \$FFBE FLASH block protect register, FLBPR

- \$FFC0 Internal OSC trim value (factory programmed, VDD = 5.0 V)

- \$FFC1 Internal OSC trim value (factory programmed, VDD = 3.0 V)

- \$FFFF COP control register, COPCTL

Figure 2-2. Control, Status, and Data Registers (Sheet 1 of 5)

MC68HC908QY/QT Family Data Sheet, Rev. 6

#### Memory

Table 2-1. Vector Addresses

| Vector Priority | Vector           | Address | Vector                                |

|-----------------|------------------|---------|---------------------------------------|

| Lowest          | owest IF15       |         | ADC conversion complete vector (high) |

| <b>A</b>        | 1113             | \$FFDF  | ADC conversion complete vector (low)  |

|                 | IF14             | \$FFE0  | Keyboard vector (high)                |

|                 | 11714            | \$FFE1  | Keyboard vector (low)                 |

|                 | IF13<br>↓<br>IF6 | _       | Not used                              |

|                 | ICE              | \$FFF2  | TIM overflow vector (high)            |

|                 | IF5              | \$FFF3  | TIM overflow vector (low)             |

|                 | IF4              | \$FFF4  | TIM Channel 1 vector (high)           |

|                 |                  | \$FFF5  | TIM Channel 1 vector (low)            |

|                 |                  | \$FFF6  | TIM Channel 0 vector (high)           |

|                 |                  | \$FFF7  | TIM Channel 0 vector (low)            |

|                 | IF2              | _       | Not used                              |

|                 | IF1              | \$FFFA  | IRQ vector (high)                     |

|                 | 151              | \$FFFB  | IRQ vector (low)                      |

|                 |                  | \$FFFC  | SWI vector (high)                     |

|                 | _                | \$FFFD  | SWI vector (low)                      |

| <b>Y</b>        |                  | \$FFFE  | Reset vector (high)                   |

| Highest         | _                | \$FFFF  | Reset vector (low)                    |

# 2.5 Random-Access Memory (RAM)

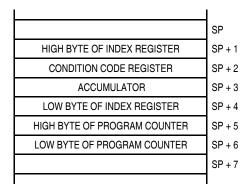

Addresses \$0080–\$00FF are RAM locations. The location of the stack RAM is programmable. The 16-bit stack pointer allows the stack to be anywhere in the 64-Kbyte memory space.

#### NOTE

For correct operation, the stack pointer must point only to RAM locations.

Before processing an interrupt, the central processor unit (CPU) uses five bytes of the stack to save the contents of the CPU registers.

#### NOTE

For M6805, M146805, and M68HC05 compatibility, the H register is not stacked.

During a subroutine call, the CPU uses two bytes of the stack to store the return address. The stack pointer decrements during pushes and increments during pulls.

## NOTE

Be careful when using nested subroutines. The CPU may overwrite data in the RAM during a subroutine or during the interrupt stacking operation.

MC68HC908QY/QT Family Data Sheet, Rev. 6

#### Memory

#### **ERASE** — Erase Control Bit

This read/write bit configures the memory for erase operation. ERASE is interlocked with the PGM bit such that both bits cannot be equal to 1 or set to 1 at the same time.

- 1 = Erase operation selected

- 0 = Erase operation unselected

## **PGM** — Program Control Bit

This read/write bit configures the memory for program operation. PGM is interlocked with the ERASE bit such that both bits cannot be equal to 1 or set to 1 at the same time.

- 1 = Program operation selected

- 0 = Program operation unselected

# 2.6.2 FLASH Page Erase Operation

Use the following procedure to erase a page of FLASH memory. A page consists of 64 consecutive bytes starting from addresses \$XX00, \$XX40, \$XX80, or \$XXC0. The 48-byte user interrupt vectors area also forms a page. Any FLASH memory page can be erased alone.

- 1. Set the ERASE bit and clear the MASS bit in the FLASH control register.

- 2. Read the FLASH block protect register.

- 3. Write any data to any FLASH location within the address range of the block to be erased.

- 4. Wait for a time,  $t_{NVS}$  (minimum 10  $\mu$ s).

- 5. Set the HVEN bit.

- 6. Wait for a time, t<sub>Erase</sub> (minimum 1 ms or 4 ms).

- 7. Clear the ERASE bit.

- 8. Wait for a time,  $t_{NVH}$  (minimum 5  $\mu$ s).

- 9. Clear the HVEN bit.

- 10. After time,  $t_{RCV}$  (typical 1  $\mu$ s), the memory can be accessed in read mode again.

#### NOTE

Programming and erasing of FLASH locations cannot be performed by code being executed from the FLASH memory. While these operations must be performed in the order as shown, but other unrelated operations may occur between the steps.

#### **CAUTION**

A page erase of the vector page will erase the internal oscillator trim values at \$FFC0 and \$FFC1.

In applications that require more than 1000 program/erase cycles, use the 4 ms page erase specification to get improved long-term reliability. Any application can use this 4 ms page erase specification. However, in applications where a FLASH location will be erased and reprogrammed less than 1000 times, and speed is important, use the 1 ms page erase specification to get a shorter cycle time.

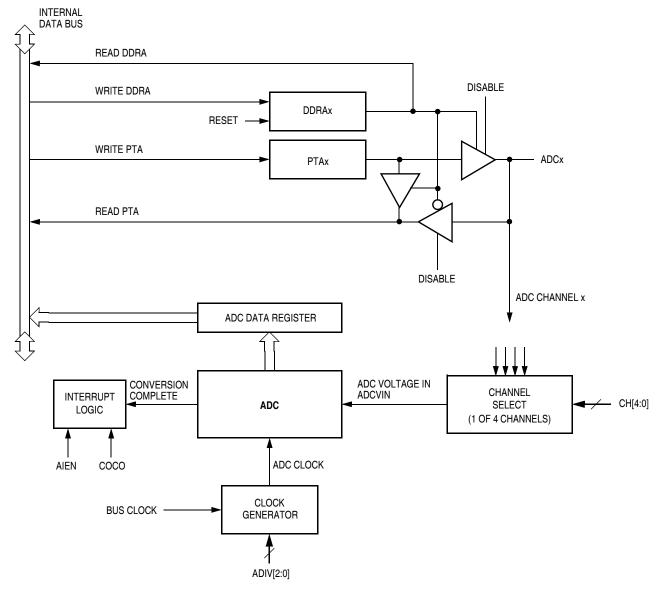

Figure 3-2. ADC Block Diagram

#### **Auto Wakeup Module (AWU)**

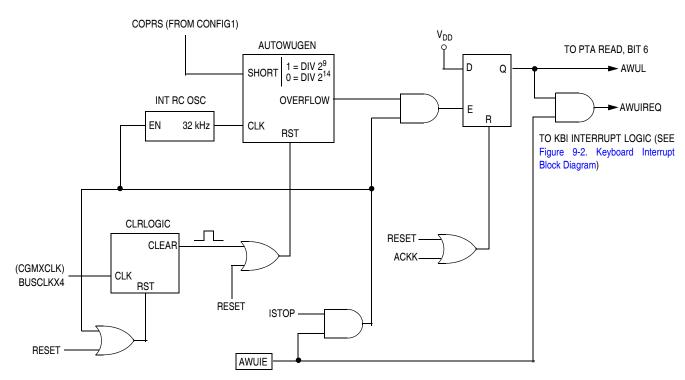

Figure 4-1. Auto Wakeup Interrupt Request Generation Logic

The auto wakeup RC oscillator is highly dependent on operating voltage and temperature. This feature is not recommended for use as a time-keeping function.

The wakeup request is latched to allow the interrupt source identification. The latched value, AWUL, can be read directly from the bit 6 position of PTA data register. This is a read-only bit which is occupying an empty bit position on PTA. No PTA associated registers, such as PTA6 data, PTA6 direction, and PTA6 pullup exist for this bit. The latch can be cleared by writing to the ACKK bit in the KBSCR register. Reset also clears the latch. AWUIE bit in KBI interrupt enable register (see Figure 4-1) has no effect on AWUL reading.

The AWU oscillator and counters are inactive in normal operating mode and become active only upon entering stop mode.

## 4.4 Wait Mode

The AWU module remains inactive in wait mode.

# 4.5 Stop Mode

When the AWU module is enabled (AWUIE = 1 in the keyboard interrupt enable register) it is activated automatically upon entering stop mode. Clearing the IMASKK bit in the keyboard status and control register enables keyboard interrupt requests to bring the MCU out of stop mode. The AWU counters start from '0' each time stop mode is entered.

**Computer Operating Properly (COP)**

# **Chapter 7 Central Processor Unit (CPU)**

# 7.1 Introduction

The M68HC08 CPU (central processor unit) is an enhanced and fully object-code-compatible version of the M68HC05 CPU. The *CPU08 Reference Manual* (document order number CPU08RM/AD) contains a description of the CPU instruction set, addressing modes, and architecture.

## 7.2 Features

Features of the CPU include:

- Object code fully upward-compatible with M68HC05 Family

- 16-bit stack pointer with stack manipulation instructions

- 16-bit index register with x-register manipulation instructions

- 8-MHz CPU internal bus frequency

- 64-Kbyte program/data memory space

- 16 addressing modes

- Memory-to-memory data moves without using accumulator

- Fast 8-bit by 8-bit multiply and 16-bit by 8-bit divide instructions

- Enhanced binary-coded decimal (BCD) data handling

- Modular architecture with expandable internal bus definition for extension of addressing range beyond 64 Kbytes

- Low-power stop and wait modes

# 7.3 CPU Registers

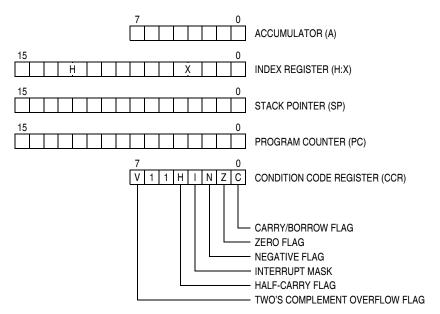

Figure 7-1 shows the five CPU registers. CPU registers are not part of the memory map.

#### **Central Processor Unit (CPU)**

Figure 7-1. CPU Registers

## 7.3.1 Accumulator

The accumulator is a general-purpose 8-bit register. The CPU uses the accumulator to hold operands and the results of arithmetic/logic operations.

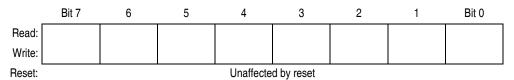

Figure 7-2. Accumulator (A)

# 7.3.2 Index Register

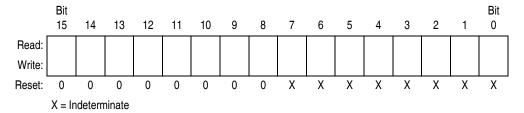

The 16-bit index register allows indexed addressing of a 64-Kbyte memory space. H is the upper byte of the index register, and X is the lower byte. H:X is the concatenated 16-bit index register.

In the indexed addressing modes, the CPU uses the contents of the index register to determine the conditional address of the operand.

The index register can serve also as a temporary data storage location.

Figure 7-3. Index Register (H:X)

MC68HC908QY/QT Family Data Sheet, Rev. 6

External Interrupt (IRQ)

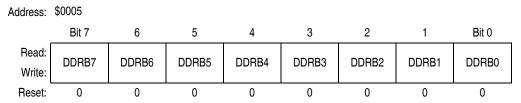

# 12.3.2 Data Direction Register B

Data direction register B (DDRB) determines whether each port B pin is an input or an output. Writing a 1 to a DDRB bit enables the output buffer for the corresponding port B pin; a 0 disables the output buffer.

Figure 12-6. Data Direction Register B (DDRB)

# DDRB[7:0] — Data Direction Register B Bits

These read/write bits control port B data direction. Reset clears DDRB[7:0], configuring all port B pins as inputs.

- 1 = Corresponding port B pin configured as output

- 0 = Corresponding port B pin configured as input

#### NOTE

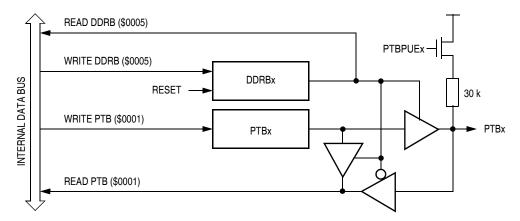

Avoid glitches on port B pins by writing to the port B data register before changing data direction register B bits from 0 to 1. Figure 12-7 shows the port B I/O logic.

Figure 12-7. Port B I/O Circuit

When DDRBx is a 1, reading address \$0001 reads the PTBx data latch. When DDRBx is a 0, reading address \$0001 reads the voltage level on the pin. The data latch can always be written, regardless of the state of its data direction bit. Table 12-2 summarizes the operation of the port B pins.

**Table 12-2. Port B Pin Functions**

| DDRB | PTB              | I/O Pin                    | Accesses to DDRB | Acc  | esses to PTB             |

|------|------------------|----------------------------|------------------|------|--------------------------|

| Bit  | Bit              | Mode                       | Read/Write       | Read | Write                    |

| 0    | X <sup>(1)</sup> | Input, Hi-Z <sup>(2)</sup> | DDRB7-DDRB0      | Pin  | PTB7-PTB0 <sup>(3)</sup> |

| 1    | X                | Output                     | DDRB7-DDRB0      | Pin  | PTB7-PTB0                |

- 1. X = don't care

- 2. Hi-Z = high impedance

- 3. Writing affects data register, but does not affect the input.

## MC68HC908QY/QT Family Data Sheet, Rev. 6

**System Integration Module (SIM)**

#### 13.4.1 External Pin Reset

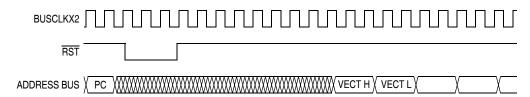

The  $\overline{RST}$  pin circuits include an internal pullup device. Pulling the asynchronous  $\overline{RST}$  pin low halts all processing. The PIN bit of the SIM reset status register (SRSR) is set as long as  $\overline{RST}$  is held low for at least the minimum  $t_{RL}$  time. Figure 13-3 shows the relative timing. The  $\overline{RST}$  pin function is only available if the RSTEN bit is set in the CONFIG2 register.

Figure 13-3. External Reset Timing

#### 13.4.2 Active Resets from Internal Sources

The RST pin is initially setup as a general-purpose input after a POR. Setting the RSTEN bit in the CONFIG2 register enables the pin for the reset function. This section assumes the RSTEN bit is set when describing activity on the RST pin.

#### NOTE

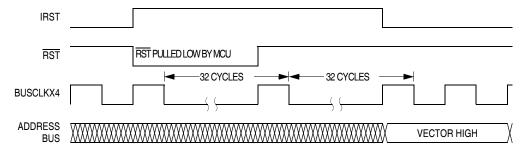

For POR and LVI resets, the SIM cycles through 4096 BUSCLKX4 cycles during which the SIM forces the  $\overline{RST}$  pin low. The internal reset signal then follows the sequence from the falling edge of  $\overline{RST}$  shown in Figure 13-4.

The COP reset is asynchronous to the bus clock.

The active reset feature allows the part to issue a reset to peripherals and other chips within a system built around the MCU.

All internal reset sources actively pull the  $\overline{RST}$  pin low for 32 BUSCLKX4 cycles to allow resetting of external peripherals. The internal reset signal IRST continues to be asserted for an additional 32 cycles (see Figure 13-4). An internal reset can be caused by an illegal address, illegal opcode, COP time out, LVI, or POR (see Figure 13-5).

Figure 13-4. Internal Reset Timing

MC68HC908QY/QT Family Data Sheet, Rev. 6

# **System Integration Module (SIM)**

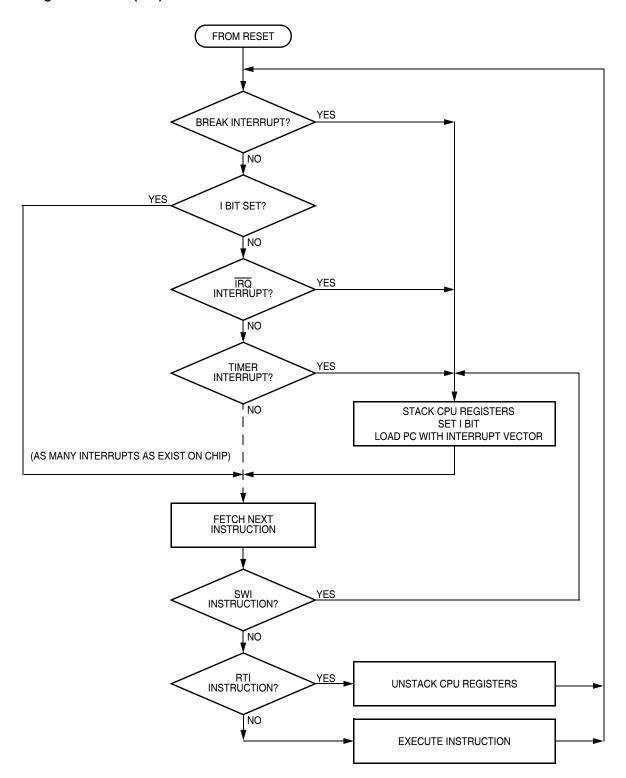

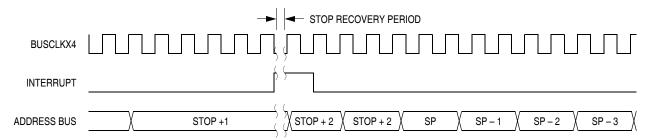

Figure 13-7. Interrupt Processing

#### **System Integration Module (SIM)**

The SIM counter is held in reset from the execution of the STOP instruction until the beginning of stop recovery. It is then used to time the recovery period. Figure 13-17 shows stop mode entry timing and Figure 13-18 shows the stop mode recovery time from interrupt or break.

#### NOTE

To minimize stop current, all pins configured as inputs should be driven to a logic 1 or logic 0.

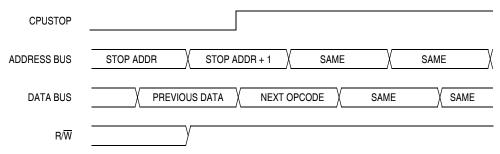

NOTE: Previous data can be operand data or the STOP opcode, depending on the last instruction.

Figure 13-17. Stop Mode Entry Timing

Figure 13-18. Stop Mode Recovery from Interrupt

# 13.8 SIM Registers

The SIM has three memory mapped registers. Table 13-4 shows the mapping of these registers.

Table 13-4. SIM Registers

| Address | Register | Access Mode |

|---------|----------|-------------|

| \$FE00  | BSR      | User        |

| \$FE01  | SRSR     | User        |

| \$FE03  | BFCR     | User        |

When ELSxB:A = 00, this read/write bit selects the initial output level of the TCHx pin (see Table 14-3). Reset clears the MSxA bit.

- 1 = Initial output level low

- 0 = Initial output level high

#### NOTE

Before changing a channel function by writing to the MSxB or MSxA bit, set the TSTOP and TRST bits in the TIM status and control register (TSC).

Table 14-3. Mode, Edge, and Level Selection

| MSxB | MSxA | ELSxB | ELSxA | Mode            | Configuration                                     |

|------|------|-------|-------|-----------------|---------------------------------------------------|

| Х    | 0    | 0     | 0     | Output preset   | Pin under port control; initial output level high |

| Х    | 1    | 0     | 0     | Output preset   | Pin under port control; initial output level low  |

| 0    | 0    | 0     | 1     |                 | Capture on rising edge only                       |

| 0    | 0    | 1     | 0     | Input capture   | Capture on falling edge only                      |

| 0    | 0    | 1     | 1     |                 | Capture on rising or falling edge                 |

| 0    | 1    | 0     | 0     |                 | Software compare only                             |

| 0    | 1    | 0     | 1     | Output compare  | Toggle output on compare                          |

| 0    | 1    | 1     | 0     | or PWM          | Clear output on compare                           |

| 0    | 1    | 1     | 1     |                 | Set output on compare                             |

| 1    | Х    | 0     | 1     | Buffered output | Toggle output on compare                          |

| 1    | Х    | 1     | 0     | compare or      | Clear output on compare                           |

| 1    | Х    | 1     | 1     | buffered PWM    | Set output on compare                             |

# ELSxB and ELSxA — Edge/Level Select Bits

When channel x is an input capture channel, these read/write bits control the active edge-sensing logic on channel x.

When channel x is an output compare channel, ELSxB and ELSxA control the channel x output behavior when an output compare occurs.

When ELSxB and ELSxA are both clear, channel x is not connected to an I/O port, and pin TCHx is available as a general-purpose I/O pin. Table 14-3 shows how ELSxB and ELSxA work. Reset clears the ELSxB and ELSxA bits.

#### NOTE

After initially enabling a TIM channel register for input capture operation and selecting the edge sensitivity, clear CHxF to ignore any erroneous edge detection flags.

#### TOVx — Toggle-On-Overflow Bit

When channel x is an output compare channel, this read/write bit controls the behavior of the channel x output when the TIM counter overflows. When channel x is an input capture channel, TOVx has no effect Reset clears the TOVx bit.

- 1 = Channel x pin toggles on TIM counter overflow.

- 0 = Channel x pin does not toggle on TIM counter overflow.

## NOTE

When TOVx is set, a TIM counter overflow takes precedence over a channel x output compare if both occur at the same time.

MC68HC908QY/QT Family Data Sheet, Rev. 6

Table 15-7. READSP (Read Stack Pointer) Command

| Description               | Reads stack pointer                                                          |  |  |  |

|---------------------------|------------------------------------------------------------------------------|--|--|--|

| Operand                   | None                                                                         |  |  |  |

| Data Returned             | Returns incremented stack pointer value (SP + 1) in high-byte:low-byte order |  |  |  |

| Opcode                    | \$0C                                                                         |  |  |  |

| Command Sequence          |                                                                              |  |  |  |

| FROM HOST                 |                                                                              |  |  |  |

| <b>↓</b>                  |                                                                              |  |  |  |

| READSP READSP SP HIGH LOW |                                                                              |  |  |  |

|                           | ECHO RETURN                                                                  |  |  |  |

Table 15-8. RUN (Run User Program) Command

| Description      | Executes PULH and RTI instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Operand          | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| Data Returned    | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| Opcode           | \$28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| Command Sequence |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|                  | FROM HOST    V RUN   RUN    ECHO   ECHO   PROPERTIES   PR |  |  |  |

The MCU executes the SWI and PSHH instructions when it enters monitor mode. The RUN command tells the MCU to execute the PULH and RTI instructions. Before sending the RUN command, the host can modify the stacked CPU registers to prepare to run the host program. The READSP command returns the incremented stack pointer value, SP + 1. The high and low bytes of the program counter are at addresses SP + 5 and SP + 6.

Figure 15-17. Stack Pointer at Monitor Mode Entry

MC68HC908QY/QT Family Data Sheet, Rev. 6

# 16.5 5-V DC Electrical Characteristics

| Characteristic <sup>(1)</sup>                                                                                                                                        | Symbol                              | Min                                                                  | Typ <sup>(2)</sup> | Max                   | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|----------------------------------------------------------------------|--------------------|-----------------------|------|

| Output high voltage  I <sub>Load</sub> = -2.0 mA, all I/O pins  I <sub>Load</sub> = -10.0 mA, all I/O pins  I <sub>Load</sub> = -15.0 mA, PTA0, PTA1, PTA3-PTA5 only | V <sub>OH</sub>                     | V <sub>DD</sub> -0.4<br>V <sub>DD</sub> -1.5<br>V <sub>DD</sub> -0.8 |                    | _<br>_<br>_           | V    |

| Maximum combined I <sub>OH</sub> (all I/O pins)                                                                                                                      | I <sub>OHT</sub>                    | _                                                                    | _                  | 50                    | mA   |

| Output low voltage  I <sub>Load</sub> = 1.6 mA, all I/O pins  I <sub>Load</sub> = 10.0 mA, all I/O pins  I <sub>Load</sub> = 15.0 mA, PTA0, PTA1, PTA3-PTA5 only     | V <sub>OL</sub>                     | _<br>_<br>_                                                          | _<br>_<br>_        | 0.4<br>1.5<br>0.8     | V    |

| Maximum combined I <sub>OL</sub> (all I/O pins)                                                                                                                      | I <sub>OLT</sub>                    | _                                                                    | _                  | 50                    | mA   |

| Input high voltage PTA0-PTA5, PTB0-PTB7                                                                                                                              | V <sub>IH</sub>                     | 0.7 x V <sub>DD</sub>                                                | _                  | V <sub>DD</sub>       | V    |

| Input low voltage PTA0-PTA5, PTB0-PTB7                                                                                                                               | V <sub>IL</sub>                     | V <sub>SS</sub>                                                      | _                  | 0.3 x V <sub>DD</sub> | V    |

| Input hysteresis                                                                                                                                                     | V <sub>HYS</sub>                    | 0.06 x V <sub>DD</sub>                                               | _                  | _                     | V    |

| DC injection current, all ports                                                                                                                                      | I <sub>INJ</sub>                    | -2                                                                   | _                  | +2                    | mA   |

| Total dc current injection (sum of all I/O)                                                                                                                          | I <sub>INJTOT</sub>                 | -25                                                                  | _                  | +25                   | mA   |

| Ports Hi-Z leakage current                                                                                                                                           | I <sub>IL</sub>                     | -1                                                                   | ±0.1               | +1                    | μА   |

| Capacitance Ports (as input) Ports (as input)                                                                                                                        | C <sub>IN</sub><br>C <sub>OUT</sub> |                                                                      |                    | 12<br>8               | pF   |

| POR rearm voltage <sup>(3)</sup>                                                                                                                                     | V <sub>POR</sub>                    | 0                                                                    | _                  | 100                   | mV   |

| POR rise time ramp rate <sup>(4)</sup>                                                                                                                               | R <sub>POR</sub>                    | 0.035                                                                | _                  | _                     | V/ms |

| Monitor mode entry voltage                                                                                                                                           | V <sub>TST</sub>                    | V <sub>DD</sub> + 2.5                                                | _                  | 9.1                   | V    |

| Pullup resistors <sup>(5)</sup><br>PTA0–PTA5, PTB0–PTB7                                                                                                              | R <sub>PU</sub>                     | 16                                                                   | 26                 | 36                    | kΩ   |

| Low-voltage inhibit reset, trip falling voltage                                                                                                                      | V <sub>TRIPF</sub>                  | 3.90                                                                 | 4.20               | 4.50                  | V    |

| Low-voltage inhibit reset, trip rising voltage                                                                                                                       | V <sub>TRIPR</sub>                  | 4.00                                                                 | 4.30               | 4.60                  | V    |

| Low-voltage inhibit reset/recover hysteresis                                                                                                                         | V <sub>HYS</sub>                    | _                                                                    | 100                | _                     | mV   |

- 1.  $V_{DD}$  = 4.5 to 5.5 Vdc,  $V_{SS}$  = 0 Vdc,  $T_A$  =  $T_L$  to  $T_H$ , unless otherwise noted. 2. Typical values reflect average measurements at midpoint of voltage range, 25•C only.

- 3. Maximum is highest voltage that POR is guaranteed.

- 4. If minimum V<sub>DD</sub> is not reached before the internal POR reset is released, the LVI will hold the part in reset until minimum  $V_{DD}$  is reached. 5.  $R_{PU}$  is measured at  $V_{DD}$  = 5.0 V.

# **16.16 Memory Characteristics**

| Characteristic                                | Symbol                           | Min        | Тур    | Max        | Unit   |

|-----------------------------------------------|----------------------------------|------------|--------|------------|--------|

| RAM data retention voltage                    | V <sub>RDR</sub>                 | 1.3        | _      | _          | V      |

| FLASH program bus clock frequency             | _                                | 1          | _      | _          | MHz    |

| FLASH read bus clock frequency                | f <sub>Read</sub> <sup>(1)</sup> | 0          | _      | 8 M        | Hz     |

| FLASH page erase time <1 k cycles >1 k cycles | t <sub>Erase</sub>               | 0.9<br>3.6 | 1<br>4 | 1.1<br>5.5 | ms     |

| FLASH mass erase time                         | t <sub>MErase</sub>              | 4          | _      | _          | ms     |

| FLASH PGM/ERASE to HVEN setup time            | t <sub>NVS</sub>                 | 10         | _      | _          | μS     |

| FLASH high-voltage hold time                  | t <sub>NVH</sub>                 | 5          | _      | _          | μS     |

| FLASH high-voltage hold time (mass erase)     | t <sub>NVHL</sub>                | 100        | _      | _          | μS     |

| FLASH program hold time                       | t <sub>PGS</sub>                 | 5          | _      | _          | μS     |

| FLASH program time                            | t <sub>PROG</sub>                | 30         | _      | 40         | μS     |

| FLASH return to read time                     | t <sub>RCV</sub> <sup>(2)</sup>  | 1          | _      | _          | μS     |

| FLASH cumulative program HV period            | t <sub>HV</sub> <sup>(3)</sup>   | _          | _      | 4          | ms     |

| FLASH endurance <sup>(4)</sup>                | _                                | 10 k       | 100 k  | _          | Cycles |

| FLASH data retention time <sup>(5)</sup>      | _                                | 15         | 100    | _          | Years  |

- 1.  $f_{\mbox{\scriptsize Read}}$  is defined as the frequency range for which the FLASH memory can be read.

- 2. t<sub>RCV</sub> is defined as the time it needs before the FLASH can be read after turning off the high voltage charge pump, by clearing HVEN to 0.

- 3.  $t_{HV}$  is defined as the cumulative high voltage programming time to the same row before next erase.  $t_{HV}$  must satisfy this condition:  $t_{NVS} + t_{NVH} + t_{PGS} + (t_{PROG} \times 32) \le t_{HV}$  maximum.

- 4. Typical endurance was evaluated for this product family. For additional information on how Freescale defines *Typical Endurance*, please refer to Engineering Bulletin EB619.

- 5. Typical data retention values are based on intrinsic capability of the technology measured at high temperature and de-rated to 25•C using the Arrhenius equation. For additional information on how Freescale defines *Typical Data Retention*, please refer to Engineering Bulletin EB618.

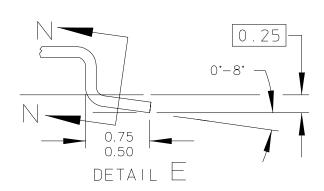

| MECHANICAL | DUTLINES |

|------------|----------|

| DICTION    | VARY     |

|--|

| DOCUMENT NO: |  | 98ASH70247A |  |

|--------------|--|-------------|--|

| PAGE:        |  | 948F        |  |

| REV:         |  | В           |  |

| $\overline{}$ | т | $\overline{}$ |   | _ |   |

|---------------|---|---------------|---|---|---|

|               | Ι |               | L | Ł | i |

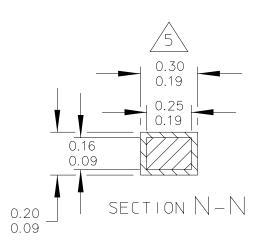

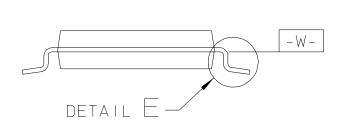

16 LD TSSOP, PITCH 0.65MM

CASE NUMBER: 948F-01

STANDARD: JEDEC

PACKAGE CDDE: 6117 SHEET: 2 DF 4