Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | HC08                                                                     |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 8MHz                                                                     |

| Connectivity               | -                                                                        |

| Peripherals                | LVD, POR, PWM                                                            |

| Number of I/O              | 13                                                                       |

| Program Memory Size        | 4KB (4K x 8)                                                             |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 128 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                              |

| Data Converters            | A/D 4x8b                                                                 |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 16-TSSOP (0.173", 4.40mm Width)                                          |

| Supplier Device Package    | 16-TSSOP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc68hc908qy4vdte |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Revision History**

The following revision history table summarizes changes contained in this document. For your convenience, the page number designators have been linked to the appropriate location.

# **Revision History (Sheet 1 of 3)**

| Date                  | Revision<br>Level                                                             | vel                                                                                                                                                                    |     |

|-----------------------|-------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| September,<br>2002    | N/A                                                                           |                                                                                                                                                                        |     |

|                       | 1.2 Features — Added 8-pin dual flat no lead (DFN) packages to features list. | 19                                                                                                                                                                     |     |

|                       |                                                                               | Figure 1-2. MCU Pin Assignments — Figure updated to include DFN packages.                                                                                              | 21  |

|                       |                                                                               | Figure 2-1. Memory Map — Clarified illegal address and unimplemented memory.                                                                                           | 27  |

|                       |                                                                               | Figure 2-2. Control, Status, and Data Registers — Corrected bit definitions for Port A Data Register (PTA) and Data Direction Register A (DDRA).                       | 27  |

|                       |                                                                               | Table 13-3. Interrupt Sources — Corrected vector addresses for keyboard interrupt and ADC conversion complete interrupt.                                               | 118 |

|                       |                                                                               | Chapter 13 System Integration Module (SIM) — Removed reference to break status register as it is duplicated in break module.                                           | 113 |

|                       |                                                                               | 11.3.1 Internal Oscillator and 11.3.1.1 Internal Oscillator Trimming — Clarified oscillator trim option ordering information and what to expect with untrimmed device. | 92  |

|                       |                                                                               | Figure 11-5. Oscillator Trim Register (OSCTRIM) — Bit 1 designation corrected.                                                                                         | 98  |

| December,<br>2002 0.1 |                                                                               | Figure 15-13. Monitor Mode Circuit (Internal Clock, No High Voltage) — Diagram updated for clarity.                                                                    |     |

|                       | 0.1                                                                           | Figure 12-1. I/O Port Register Summary — Corrected bit definitions for PTA7, DDRA7, and DDRA6.                                                                         | 99  |

|                       |                                                                               | Figure 12-2. Port A Data Register (PTA) — Corrected bit definition for PTA7.                                                                                           | 100 |

|                       |                                                                               | Figure 12-3. Data Direction Register A (DDRA) — Corrected bit definitions for DDRA7 and DDRA6.                                                                         | 101 |

|                       |                                                                               | Figure 12-6. Port B Data Register (PTB) — Corrected bit definition for PTB1                                                                                            | 103 |

|                       |                                                                               | Chapter 9 Keyboard Interrupt Module (KBI) — Section reworked after deletion of auto wakeup for clarity.                                                                | 83  |

|                       |                                                                               | Chapter 4 Auto Wakeup Module (AWU) — New section added for clarity.                                                                                                    | 49  |

|                       |                                                                               | Figure 10-1. LVI Module Block Diagram — Corrected LVI stop representation.                                                                                             | 87  |

|                       |                                                                               | Chapter 16 Electrical Specifications — Extensive changes made to electrical specifications.                                                                            | 169 |

|                       |                                                                               | 17.5 8-Pin Dual Flat No Lead (DFN) Package (Case #1452) — Added case outline drawing for DFN package.                                                                  | 177 |

|                       |                                                                               | Chapter 17 Ordering Information and Mechanical Specifications — Added ordering information for DFN package.                                                            | 185 |

| January,<br>2003      | 0.2                                                                           | 4.2 Features — Corrected third bulleted item.                                                                                                                          | 49  |

# Chapter 1 General Description

## **1.1 Introduction**

The MC68HC908QY4 is a member of the low-cost, high-performance M68HC08 Family of 8-bit microcontroller units (MCUs). The M68HC08 Family is a Complex Instruction Set Computer (CISC) with a Von Neumann architecture. All MCUs in the family use the enhanced M68HC08 central processor unit (CPU08) and are available with a variety of modules, memory sizes and types, and package types.

| Device       | FLASH<br>Memory Size | Analog-to-Digital<br>Converter | Pin<br>Count |

|--------------|----------------------|--------------------------------|--------------|

| MC68HC908QT1 | 1536 bytes           | —                              | 8 pins       |

| MC68HC908QT2 | 1536 bytes           | 4 ch, 8 bit                    | 8 pins       |

| MC68HC908QT4 | 4096 bytes           | 4 ch, 8 bit                    | 8 pins       |

| MC68HC908QY1 | 1536 bytes           | —                              | 16 pins      |

| MC68HC908QY2 | 1536 bytes           | 4 ch, 8 bit                    | 16 pins      |

| MC68HC908QY4 | 4096 bytes           | 4 ch, 8 bit                    | 16 pins      |

Table 1-1. Summary of Device Variations

### **1.2 Features**

Features include:

- High-performance M68HC08 CPU core

- Fully upward-compatible object code with M68HC05 Family

- 5-V and 3-V operating voltages (V<sub>DD</sub>)

- 8-MHz internal bus operation at 5 V, 4-MHz at 3 V

- Trimmable internal oscillator

- 3.2 MHz internal bus operation

- 8-bit trim capability allows 0.4% accuracy<sup>(1)</sup>

- ± 25% untrimmed

- Auto wakeup from STOP capability

- Configuration (CONFIG) register for MCU configuration options, including:

- Low-voltage inhibit (LVI) trip point

- In-system FLASH programming

- FLASH security<sup>(2)</sup>

<sup>1.</sup> The oscillator frequency is guaranteed to  $\pm 5\%$  over temperature and voltage range after trimming.

No security feature is absolutely secure. However, Freescale's strategy is to make reading or copying the FLASH difficult for unauthorized users.

| Vector Priority | Vector           | Address | Vector                                |

|-----------------|------------------|---------|---------------------------------------|

| Lowest          | IF15             | \$FFDE  | ADC conversion complete vector (high) |

| ▲               | 1113             | \$FFDF  | ADC conversion complete vector (low)  |

|                 | IF14             | \$FFE0  | Keyboard vector (high)                |

|                 | 1614             | \$FFE1  | Keyboard vector (low)                 |

|                 | IF13<br>↓<br>IF6 | _       | Not used                              |

|                 | IF5              | \$FFF2  | TIM overflow vector (high)            |

|                 | IFO              | \$FFF3  | TIM overflow vector (low)             |

|                 | IF4              | \$FFF4  | TIM Channel 1 vector (high)           |

|                 | 164              | \$FFF5  | TIM Channel 1 vector (low)            |

|                 | IF3              | \$FFF6  | TIM Channel 0 vector (high)           |

|                 |                  | \$FFF7  | TIM Channel 0 vector (low)            |

|                 | IF2              | —       | Not used                              |

|                 | IF1              | \$FFFA  | IRQ vector (high)                     |

|                 |                  | \$FFFB  | IRQ vector (low)                      |

|                 |                  | \$FFFC  | SWI vector (high)                     |

|                 |                  | \$FFFD  | SWI vector (low)                      |

| ♥               |                  | \$FFFE  | Reset vector (high)                   |

| Highest         |                  | \$FFFF  | Reset vector (low)                    |

Table 2-1. Vector Addresses

# 2.5 Random-Access Memory (RAM)

Addresses \$0080–\$00FF are RAM locations. The location of the stack RAM is programmable. The 16-bit stack pointer allows the stack to be anywhere in the 64-Kbyte memory space.

### NOTE

For correct operation, the stack pointer must point only to RAM locations.

Before processing an interrupt, the central processor unit (CPU) uses five bytes of the stack to save the contents of the CPU registers.

### NOTE

For M6805, M146805, and M68HC05 compatibility, the H register is not stacked.

During a subroutine call, the CPU uses two bytes of the stack to store the return address. The stack pointer decrements during pushes and increments during pulls.

### NOTE

Be careful when using nested subroutines. The CPU may overwrite data in the RAM during a subroutine or during the interrupt stacking operation.

# Chapter 4 Auto Wakeup Module (AWU)

### 4.1 Introduction

This section describes the auto wakeup module (AWU). The AWU generates a periodic interrupt during stop mode to wake the part up without requiring an external signal. Figure 4-1 is a block diagram of the AWU.

## 4.2 Features

Features of the auto wakeup module include:

- One internal interrupt with separate interrupt enable bit, sharing the same keyboard interrupt vector and keyboard interrupt mask bit

- Exit from low-power stop mode without external signals

- Selectable timeout periods

- Dedicated low-power internal oscillator separate from the main system clock sources

# 4.3 Functional Description

The function of the auto wakeup logic is to generate periodic wakeup requests to bring the microcontroller unit (MCU) out of stop mode. The wakeup requests are treated as regular keyboard interrupt requests, with the difference that instead of a pin, the interrupt signal is generated by an internal logic.

Writing the AWUIE bit in the keyboard interrupt enable register enables or disables the auto wakeup interrupt input (see Figure 4-1). A logic 1 applied to the AWUIREQ input with auto wakeup interrupt request enabled, latches an auto wakeup interrupt request.

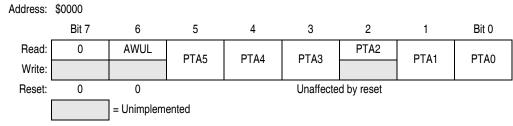

Auto wakeup latch, AWUL, can be read directly from the bit 6 position of port A data register (PTA). This is a read-only bit which is occupying an empty bit position on PTA. No PTA associated registers, such as PTA6 data direction or PTA6 pullup exist for this bit.

Entering stop mode will enable the auto wakeup generation logic. An internal RC oscillator (exclusive for the auto wakeup feature) drives the wakeup request generator. Once the overflow count is reached in the generator counter, a wakeup request, AWUIREQ, is latched and sent to the KBI logic. See Figure 4-1.

Wakeup interrupt requests will only be serviced if the associated interrupt enable bit, AWUIE, in KBIER is set. The AWU shares the keyboard interrupt vector.

The overflow count can be selected from two options defined by the COPRS bit in CONFIG1. This bit was "borrowed" from the computer operating properly (COP) using the fact that the COP feature is idle (no MCU clock available) in stop mode. The typical values of the periodic wakeup request are (at room temperature):

- COPRS = 0: 650 ms @ 5 V, 875 ms @ 3 V

- COPRS = 1: 16 ms @ 5 V, 22 ms @ 3 V

### 4.6 Input/Output Registers

The AWU shares registers with the keyboard interrupt (KBI) module and the port A I/O module. The following I/O registers control and monitor operation of the AWU:

- Port A data register (PTA)

- Keyboard interrupt status and control register (KBSCR)

- Keyboard interrupt enable register (KBIER)

### 4.6.1 Port A I/O Register

The port A data register (PTA) contains a data latch for the state of the AWU interrupt request, in addition to the data latches for port A.

Figure 4-2. Port A Data Register (PTA)

### AWUL — Auto Wakeup Latch

This is a read-only bit which has the value of the auto wakeup interrupt request latch. The wakeup request signal is generated internally. There is no PTA6 port or any of the associated bits such as PTA6 data direction or pullup bits.

1 = Auto wakeup interrupt request is pending

0 = Auto wakeup interrupt request is not pending

### NOTE

PTA5–PTA0 bits are not used in conjuction with the auto wakeup feature. To see a description of these bits, see 12.2.1 Port A Data Register.

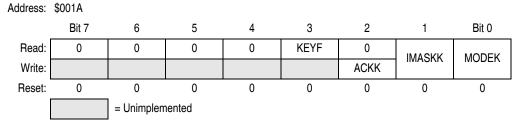

### 4.6.2 Keyboard Status and Control Register

The keyboard status and control register (KBSCR):

- Flags keyboard/auto wakeup interrupt requests

- Acknowledges keyboard/auto wakeup interrupt requests

- Masks keyboard/auto wakeup interrupt requests

### LVIPWRD — LVI Power Disable Bit

LVIPWRD disables the LVI module.

- 1 = LVI module power disabled

- 0 = LVI module power enabled

#### LVI5OR3 — LVI 5-V or 3-V Operating Mode Bit

LVI5OR3 selects the voltage operating mode of the LVI module. The voltage mode selected for the LVI should match the operating  $V_{DD}$  for the LVI's voltage trip points for each of the modes.

1 = LVI operates in 5-V mode

0 = LVI operates in 3-V mode

#### NOTE

The LVI5OR3 bit is cleared by a power-on reset (POR) only. Other resets will leave this bit unaffected.

#### SSREC — Short Stop Recovery Bit

SSREC enables the CPU to exit stop mode with a delay of 32 BUSCLKX4 cycles instead of a 4096 BUSCLKX4 cycle delay.

1 = Stop mode recovery after 32 BUSCLKX4 cycles

0 = Stop mode recovery after 4096 BUSCLKX4 cycles

### NOTE

#### Exiting stop mode by an LVI reset will result in the long stop recovery.

The system stabilization time for power-on reset and long stop recovery (both 4096 BUSCLKX4 cycles) gives a delay longer than the LVI enable time for these startup scenarios. There is no period where the MCU is not protected from a low-power condition. However, when using the short stop recovery configuration option, the 32 BUSCLKX4 delay must be greater than the LVI's turn on time to avoid a period in startup where the LVI is not protecting the MCU.

### **STOP** — **STOP** Instruction Enable Bit

STOP enables the STOP instruction.

- 1 = STOP instruction enabled

- 0 = STOP instruction treated as illegal opcode

### COPD — COP Disable Bit

COPD disables the COP module.

- 1 = COP module disabled

- 0 = COP module enabled

# Chapter 8 External Interrupt (IRQ)

### 8.1 Introduction

The IRQ pin (external interrupt), shared with PTA2 (general purpose input) and keyboard interrupt (KBI), provides a maskable interrupt input

### 8.2 Features

Features of the IRQ module include the following:

- External interrupt pin, IRQ

- IRQ interrupt control bits

- Programmable edge-only or edge and level interrupt sensitivity

- Automatic interrupt acknowledge

- Selectable internal pullup resistor

## 8.3 Functional Description

IRQ pin functionality is enabled by setting configuration register 2 (CONFIG2) IRQEN bit accordingly. A zero disables the IRQ function and PTA2 will assume the other shared functionalities. A one enables the IRQ function.

A low level applied to the external interrupt request (IRQ) pin can latch a CPU interrupt request. Figure 8-2 shows the structure of the IRQ module.

Interrupt signals on the IRQ pin are latched into the IRQ latch. The IRQ latch remains set until one of the following actions occurs:

- IRQ vector fetch An IRQ vector fetch automatically generates an interrupt acknowledge signal that clears the IRQ latch.

- Software clear Software can clear the IRQ latch by writing a 1 to the ACK bit in the interrupt status and control register (INTSCR).

- Reset A reset automatically clears the IRQ latch.

The external interrupt pin is falling-edge-triggered out of reset and is software-configurable to be either falling-edge or falling-edge and low-level triggered. The MODE bit in INTSCR controls the triggering sensitivity of the IRQ pin.

#### External Interrupt (IRQ)

#### RST, IRQ: Pins have internal (about 30K Ohms) pull up

PTA[0:5]: High current sink and source capability

PTA[0:5]: Pins have programmable keyboard interrupt and pull up

PTB[0:7]: Not available on 8-pin devices – MC68HC908QT1, MC68HC908QT2, and MC68HC908QT4 (see note in 12.1 Introduction)

ADC: Not available on the MC68HC908QY1 and MC68HC908QT1

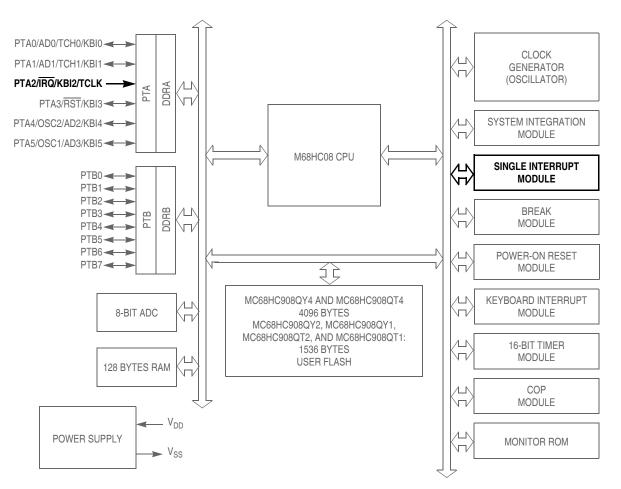

### Figure 8-1. Block Diagram Highlighting IRQ Block and Pins

When set, the IMASK bit in INTSCR masks the IRQ interrupt request. A latched interrupt request is not presented to the interrupt priority logic unless IMASK is clear.

### NOTE

The interrupt mask (I) in the condition code register (CCR) masks all interrupt requests, including the  $\overline{IRQ}$  interrupt request.

A falling edge on the IRQ pin can latch an interrupt request into the IRQ latch. An IRQ vector fetch, software clear, or reset clears the IRQ latch.

#### Keyboard Interrupt Module (KBI)

RST, IRQ: Pins have internal (about 30K Ohms) pull upPTA[0:5]: High current sink and source capabilityPTA[0:5]: Pins have programmable keyboard interrupt and pull upPTB[0:7]: Not available on 8-pin devices – MC68HC908QT1, MC68HC908QT2, and MC68HC908QT4 (see note in12.1 Introduction)

ADC: Not available on the MC68HC908QY1 and MC68HC908QT1

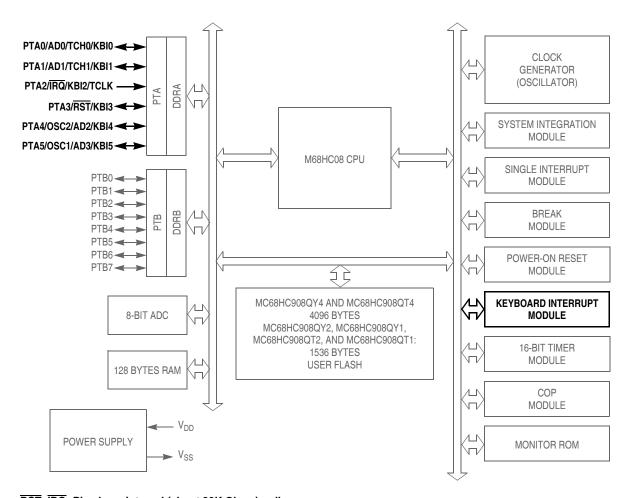

### Figure 9-1. Block Diagram Highlighting KBI Block and Pins

#### Input/Output Ports (PORTS)

#### PTAPUE[5:0] — Port A Input Pullup Enable Bits

These read/write bits are software programmable to enable pullup devices on port A pins.

- 1 = Corresponding port A pin configured to have internal pull if its DDRA bit is set to 0

- 0 = Pullup device is disconnected on the corresponding port A pin regardless of the state of its DDRA bit

Table 12-1 summarizes the operation of the port A pins.

| PTAPUE | DDRA | ΡΤΑ              | I/O Pin                               | Accesses to DDRA | Access    | ses to PTA               |

|--------|------|------------------|---------------------------------------|------------------|-----------|--------------------------|

| Bit    | Bit  | Bit              | Mode                                  | Read/Write       | Read      | Write                    |

| 1      | 0    | X <sup>(1)</sup> | Input, V <sub>DD</sub> <sup>(2)</sup> | DDRA5-DDRA0      | Pin       | PTA5–PTA0 <sup>(3)</sup> |

| 0      | 0    | Х                | Input, Hi-Z <sup>(4)</sup>            | DDRA5-DDRA0      | Pin       | PTA5-PTA0 <sup>(3)</sup> |

| Х      | 1    | Х                | Output                                | DDRA5-DDRA0      | PTA5-PTA0 | PTA5-PTA0 <sup>(5)</sup> |

#### Table 12-1. Port A Pin Functions

1. X = don't care

2. I/O pin pulled to  $V_{DD}$  by internal pullup.

3. Writing affects data register, but does not affect input.

4. Hi-Z = high impedance

5. Output does not apply to PTA2

## 12.3 Port B

Port B is an 8-bit general purpose I/O port. Port B is only available on the MC68HC908QY1, MC68HC908QY2, and MC68HC908QY4.

### 12.3.1 Port B Data Register

The port B data register (PTB) contains a data latch for each of the eight port B pins.

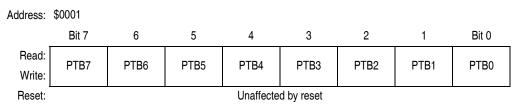

### Figure 12-5. Port B Data Register (PTB)

### PTB[7:0] — Port B Data Bits

These read/write bits are software programmable. Data direction of each port B pin is under the control of the corresponding bit in data direction register B. Reset has no effect on port B data.

#### Timer Interface Module (TIM)

### 14.4.4.1 Unbuffered PWM Signal Generation

Any output compare channel can generate unbuffered PWM pulses as described in 14.4.4 Pulse Width Modulation (PWM). The pulses are unbuffered because changing the pulse width requires writing the new pulse width value over the old value currently in the TIM channel registers.

An unsynchronized write to the TIM channel registers to change a pulse width value could cause incorrect operation for up to two PWM periods. For example, writing a new value before the counter reaches the old value but after the counter reaches the new value prevents any compare during that PWM period. Also, using a TIM overflow interrupt routine to write a new, smaller pulse width value may cause the compare to be missed. The TIM may pass the new value before it is written.

Use the following methods to synchronize unbuffered changes in the PWM pulse width on channel x:

- When changing to a shorter pulse width, enable channel x output compare interrupts and write the new value in the output compare interrupt routine. The output compare interrupt occurs at the end of the current pulse. The interrupt routine has until the end of the PWM period to write the new value.

- When changing to a longer pulse width, enable TIM overflow interrupts and write the new value in the TIM overflow interrupt routine. The TIM overflow interrupt occurs at the end of the current PWM period. Writing a larger value in an output compare interrupt routine (at the end of the current pulse) could cause two output compares to occur in the same PWM period.

#### NOTE

In PWM signal generation, do not program the PWM channel to toggle on output compare. Toggling on output compare prevents reliable 0% duty cycle generation and removes the ability of the channel to self-correct in the event of software error or noise. Toggling on output compare also can cause incorrect PWM signal generation when changing the PWM pulse width to a new, much larger value.

#### 14.4.4.2 Buffered PWM Signal Generation

Channels 0 and 1 can be linked to form a buffered PWM channel whose output appears on the TCH0 pin. The TIM channel registers of the linked pair alternately control the pulse width of the output.

Setting the MS0B bit in TIM channel 0 status and control register (TSC0) links channel 0 and channel 1. The TIM channel 0 registers initially control the pulse width on the TCH0 pin. Writing to the TIM channel 1 registers enables the TIM channel 1 registers to synchronously control the pulse width at the beginning of the next PWM period. At each subsequent overflow, the TIM channel registers (0 or 1) that control the pulse width are the ones written to last. TSC0 controls and monitors the buffered PWM function, and TIM channel 1 status and control register (TSC1) is unused. While the MS0B bit is set, the channel 1 pin, TCH1, is available as a general-purpose I/O pin.

#### NOTE

In buffered PWM signal generation, do not write new pulse width values to the currently active channel registers. User software should track the currently active channel to prevent writing a new value to the active channel. Writing to the active channel registers is the same as generating unbuffered PWM signals.

# Chapter 15 Development Support

### **15.1 Introduction**

This section describes the break module, the monitor read-only memory (MON), and the monitor mode entry methods.

# 15.2 Break Module (BRK)

The break module can generate a break interrupt that stops normal program flow at a defined address to enter a background program.

Features include:

- Accessible input/output (I/O) registers during the break Interrupt

- Central processor unit (CPU) generated break interrupts

- Software-generated break interrupts

- Computer operating properly (COP) disabling during break interrupts

### 15.2.1 Functional Description

When the internal address bus matches the value written in the break address registers, the break module issues a breakpoint signal (BKPT) to the system integration module (SIM). The SIM then causes the CPU to load the instruction register with a software interrupt instruction (SWI). The program counter vectors to \$FFFC and \$FFFD (\$FEFC and \$FEFD in monitor mode).

The following events can cause a break interrupt to occur:

- A CPU generated address (the address in the program counter) matches the contents of the break address registers.

- Software writes a 1 to the BRKA bit in the break status and control register.

When a CPU generated address matches the contents of the break address registers, the break interrupt is generated. A return-from-interrupt instruction (RTI) in the break routine ends the break interrupt and returns the microcontroller unit (MCU) to normal operation.

Figure 15-2 shows the structure of the break module.

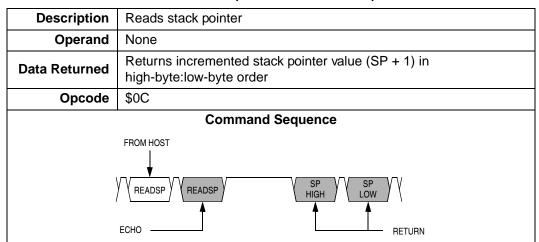

### Table 15-7. READSP (Read Stack Pointer) Command

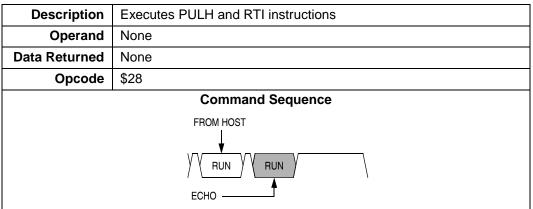

The MCU executes the SWI and PSHH instructions when it enters monitor mode. The RUN command tells the MCU to execute the PULH and RTI instructions. Before sending the RUN command, the host can modify the stacked CPU registers to prepare to run the host program. The READSP command returns the incremented stack pointer value, SP + 1. The high and low bytes of the program counter are at addresses SP + 5 and SP + 6.

|                              | J      |

|------------------------------|--------|

|                              | SP     |

| HIGH BYTE OF INDEX REGISTER  | SP + 1 |

| CONDITION CODE REGISTER      | SP + 2 |

| ACCUMULATOR                  | SP + 3 |

| LOW BYTE OF INDEX REGISTER   | SP + 4 |

| HIGH BYTE OF PROGRAM COUNTER | SP + 5 |

| LOW BYTE OF PROGRAM COUNTER  | SP + 6 |

|                              | SP + 7 |

|                              | 1      |

Figure 15-17. Stack Pointer at Monitor Mode Entry

# 16.7 5-V Control Timing

| Characteristic <sup>(1)</sup>                  | Symbol                              | Min                 | Max | Unit             |

|------------------------------------------------|-------------------------------------|---------------------|-----|------------------|

| Internal operating frequency                   | f <sub>OP</sub> (f <sub>Bus</sub> ) | —                   | 8   | MHz              |

| Internal clock period (1/f <sub>OP</sub> )     | t <sub>cyc</sub>                    | 125                 | _   | ns               |

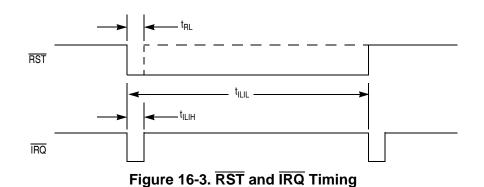

| RST input pulse width low                      | t <sub>RL</sub>                     | 100                 | _   | ns               |

| IRQ interrupt pulse width low (edge-triggered) | t <sub>ILIH</sub>                   | 100                 | _   | ns               |

| IRQ interrupt pulse period                     | t <sub>ILIL</sub>                   | Note <sup>(2)</sup> |     | t <sub>cyc</sub> |

1. V<sub>DD</sub> = 4.5 to 5.5 Vdc, V<sub>SS</sub> = 0 Vdc, T<sub>A</sub> = T<sub>L</sub> to T<sub>H</sub>; timing shown with respect to 20% V<sub>DD</sub> and 70% V<sub>SS</sub>, unless otherwise noted.

2. The minimum period is the number of cycles it takes to execute the interrupt service routine plus 1  $t_{cyc}$ .

**Electrical Specifications**

# 16.8 5-V Oscillator Characteristics

| Characteristic                                                                                                                                                                               | Symbol             | Min | Тур                | Max  | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|--------------------|------|------|

| Internal oscillator frequency <sup>(1)</sup>                                                                                                                                                 | <b>f</b> INTCLK    | —   | 12.8               | _    | MHz  |

| Deviation from trimmed Internal oscillator $^{(2)(3)}$<br>12.8 MHz, fixed voltage, fixed temp<br>12.8 MHz, V <sub>DD</sub> ± 10%, 0 to 70°C<br>12.8 MHz, V <sub>DD</sub> ± 10%, -40 to 125°C | ACC <sub>INT</sub> |     | ±0.4<br>±2<br>—    | <br> | %    |

| Crystal frequency, XTALCLK <sup>(1)</sup>                                                                                                                                                    | foscxclk           | 1   | —                  | 24   | MHz  |

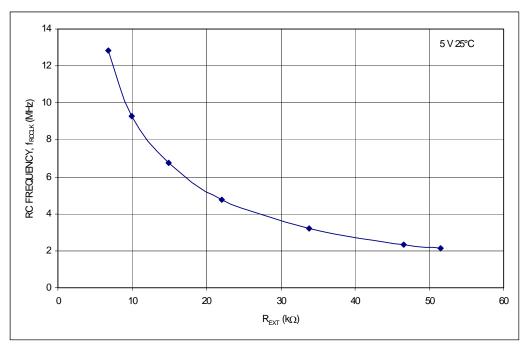

| External RC oscillator frequency, RCCLK <sup>(1)</sup>                                                                                                                                       | f <sub>RCCLK</sub> | 2   | —                  | 12   | MHz  |

| External clock reference frequency <sup>(1) (4)</sup>                                                                                                                                        | foscxclk           | dc  | —                  | 32   | MHz  |

| Crystal load capacitance <sup>(5)</sup>                                                                                                                                                      | CL                 | —   | 20                 |      | pF   |

| Crystal fixed capacitance <sup>(3)</sup>                                                                                                                                                     | C <sub>1</sub>     | —   | 2 x C <sub>L</sub> | _    | —    |

| Crystal tuning capacitance <sup>(3)</sup>                                                                                                                                                    | C <sub>2</sub>     | —   | 2 x C <sub>L</sub> | _    | —    |

| Feedback bias resistor                                                                                                                                                                       | R <sub>B</sub>     | 0.5 | 1                  | 10   | MΩ   |

| RC oscillator external resistor                                                                                                                                                              | R <sub>EXT</sub>   | S   | See Figure 16-     | 4    | —    |

| Crystal series damping resistor<br>$f_{OSCXCLK} = 1 MHz$<br>$f_{OSCXCLK} = 4 MHz$<br>$f_{OSCXCLK} = > 8 MHz$                                                                                 | R <sub>S</sub>     |     | 20<br>10<br>0      | <br> | kΩ   |

Bus frequency, f<sub>OP</sub>, is oscillator frequency divided by 4.

Deviation values assumes trimming @25•C and midpoint of voltage range.

Values are based on characterization results, not tested in production.

No more than 10% duty cycle deviation from 50%.

5. Consult crystal vendor data sheet.

Figure 16-4. RC versus Frequency (5 Volts @ 25•C)

## 16.14 Analog-to-Digital Converter Characteristics

| Characteristic                                         | Symbol            | Min                          | Мах                          | Unit                     | Comments                                         |

|--------------------------------------------------------|-------------------|------------------------------|------------------------------|--------------------------|--------------------------------------------------|

| Supply voltage                                         | V <sub>DDAD</sub> | 2.7<br>(V <sub>DD</sub> min) | 5.5<br>(V <sub>DD</sub> max) | V                        | —                                                |

| Input voltages                                         | V <sub>ADIN</sub> | V <sub>SS</sub>              | V <sub>DD</sub>              | V                        | —                                                |

| Resolution<br>(1 LSB)                                  | RES               | 10.5                         | 21.5                         | mV                       | —                                                |

| Absolute accuracy<br>(Total unadjusted error)          | E <sub>TUE</sub>  | _                            | ± 1.5                        | LSB                      | Includes quantization                            |

| ADC internal clock                                     | f <sub>ADIC</sub> | 0.5                          | 1.048                        | MHz                      | $t_{ADIC} = 1/f_{ADIC},$<br>tested only at 1 MHz |

| Conversion range                                       | V <sub>AIN</sub>  | V <sub>SS</sub>              | V <sub>DD</sub>              | V                        | —                                                |

| Power-up time                                          | t <sub>ADPU</sub> | 16                           | —                            | t <sub>ADIC</sub> cycles | $t_{ADIC} = 1/f_{ADIC}$                          |

| Conversion time                                        | t <sub>ADC</sub>  | 16                           | 17                           | t <sub>ADIC</sub> cycles | $t_{ADIC} = 1/f_{ADIC}$                          |

| Sample time <sup>(1)</sup>                             | t <sub>ADS</sub>  | 5                            | —                            | t <sub>ADIC</sub> cycles | $t_{ADIC} = 1/f_{ADIC}$                          |

| Zero input reading <sup>(2)</sup>                      | Z <sub>ADI</sub>  | 00                           | 01                           | Hex                      | $V_{IN} = V_{SS}$                                |

| Full-scale reading <sup>(3)</sup>                      | F <sub>ADI</sub>  | FE                           | FF                           | Hex                      | $V_{IN} = V_{DD}$                                |

| Input capacitance                                      | C <sub>ADI</sub>  | _                            | 8                            | pF                       | Not tested                                       |

| Input leakage <sup>(3)</sup>                           | I <sub>IL</sub>   | —                            | ± 1                          | μΑ                       | —                                                |

| ADC supply current<br>$V_{DD} = 3 V$<br>$V_{DD} = 5 V$ | I <sub>ADAD</sub> |                              | l = 0.45<br>l = 0.65         | mA<br>mA                 | Enabled<br>Enabled                               |

1. Source impedances greater than 10 kΩ adversely affect internal RC charging time during input sampling.

2. Zero-input/full-scale reading requires sufficient decoupling measures for accurate conversions.

3. The external system error caused by input leakage current is approximately equal to the product of R source and input current.

### **16.16 Memory Characteristics**

| Characteristic                                      | Symbol                           | Min        | Тур    | Max        | Unit   |

|-----------------------------------------------------|----------------------------------|------------|--------|------------|--------|

| RAM data retention voltage                          | V <sub>RDR</sub>                 | 1.3        | _      | _          | V      |

| FLASH program bus clock frequency                   | _                                | 1          | _      |            | MHz    |

| FLASH read bus clock frequency                      | f <sub>Read</sub> <sup>(1)</sup> | 0          | —      | 8 M        | Hz     |

| FLASH page erase time<br><1 k cycles<br>>1 k cycles | t <sub>Erase</sub>               | 0.9<br>3.6 | 1<br>4 | 1.1<br>5.5 | ms     |

| FLASH mass erase time                               | t <sub>MErase</sub>              | 4          | _      | _          | ms     |

| FLASH PGM/ERASE to HVEN setup time                  | t <sub>NVS</sub>                 | 10         | —      | _          | μs     |

| FLASH high-voltage hold time                        | t <sub>NVH</sub>                 | 5          | —      | _          | μs     |

| FLASH high-voltage hold time (mass erase)           | t <sub>NVHL</sub>                | 100        | —      | _          | μs     |

| FLASH program hold time                             | t <sub>PGS</sub>                 | 5          | —      | _          | μs     |

| FLASH program time                                  | t <sub>PROG</sub>                | 30         | _      | 40         | μs     |

| FLASH return to read time                           | t <sub>RCV</sub> <sup>(2)</sup>  | 1          | _      | _          | μS     |

| FLASH cumulative program HV period                  | t <sub>HV</sub> <sup>(3)</sup>   | _          | —      | 4          | ms     |

| FLASH endurance <sup>(4)</sup>                      | _                                | 10 k       | 100 k  | _          | Cycles |

| FLASH data retention time <sup>(5)</sup>            | _                                | 15         | 100    | _          | Years  |

1.  $f_{Read}$  is defined as the frequency range for which the FLASH memory can be read.

2. t<sub>RCV</sub> is defined as the time it needs before the FLASH can be read after turning off the high voltage charge pump, by clearing HVEN to 0.

3.  $t_{HV}$  is defined as the cumulative high voltage programming time to the same row before next erase.

$t_{HV}$  must satisfy this condition:  $t_{NVS}$  +  $t_{NVH}$  +  $t_{PGS}$  +  $(t_{PROG} \ x \ 32) \ \leq t_{HV}$  maximum.

4. Typical endurance was evaluated for this product family. For additional information on how Freescale defines *Typical Endurance*, please refer to Engineering Bulletin EB619.

5. Typical data retention values are based on intrinsic capability of the technology measured at high temperature and de-rated to 25•C using the Arrhenius equation. For additional information on how Freescale defines *Typical Data Retention*, please refer to Engineering Bulletin EB618.

# Chapter 17 Ordering Information and Mechanical Specifications

## **17.1 Introduction**

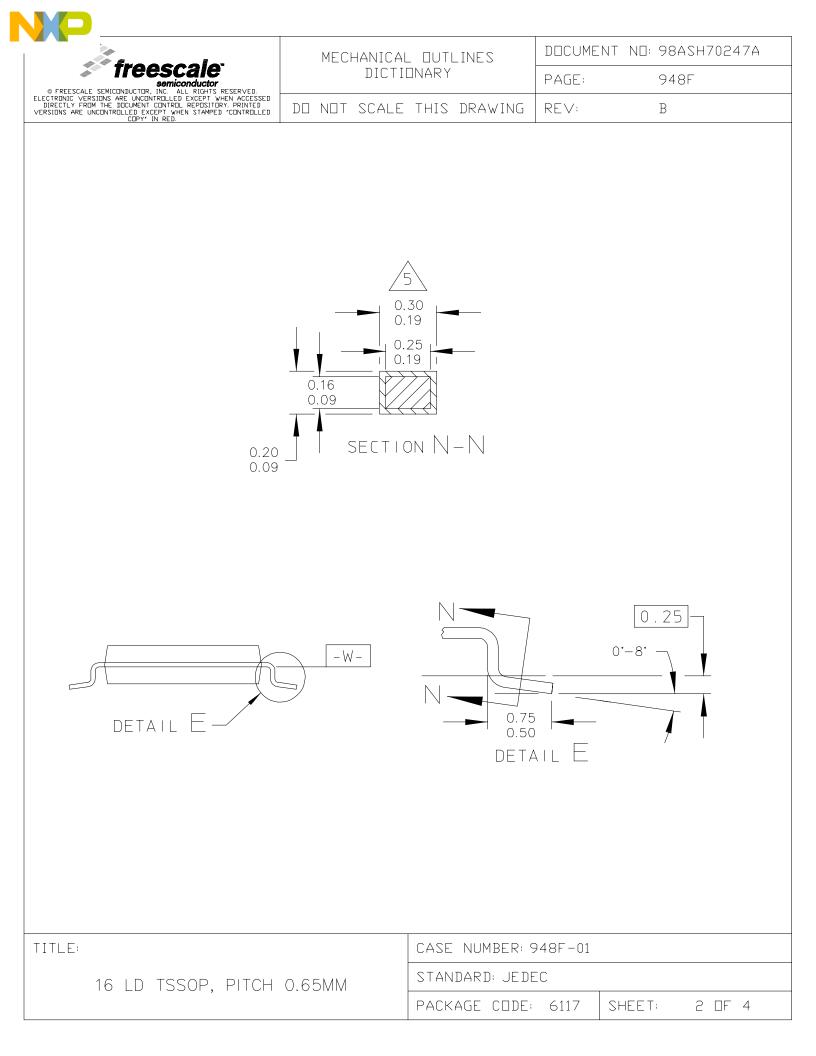

This section contains order numbers for the MC68HC908QY1, MC68HC908QY2, MC68HC908QY4, MC68HC908QT1, MC68HC908QT2, and MC69HC908QT4. Dimensions are given for:

- 8-pin plastic dual in-line package (PDIP)

- 8-pin small outline integrated circuit (SOIC) package

- 8-pin dual flat no lead (DFN) package

- 16-pin PDIP

- 16-pin SOIC

- 16-pin thin shrink small outline package (TSSOP)

## 17.2 MC Order Numbers

| MC Order Number | ADC | FLASH Memory | Package     |

|-----------------|-----|--------------|-------------|

| MC908QY1        | —   | 1536 bytes   | 16-pins     |

| MC908QY2        | Yes | 1536 bytes   | PDIP, SOIC, |

| MC908QY4        | Yes | 4096 bytes   | and TSSOP   |

| MC908QT1        | —   | 1536 bytes   | 8-pins      |

| MC908QT2        | Yes | 1536 bytes   | PDIP, SOIC, |

| MC908QT4        | Yes | 4096 bytes   | and DFN     |

Table 17-1. MC Order Numbers

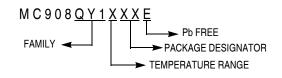

Temperature and package designators:

$$C = -40 \bullet C$$

to  $+85 \bullet C$

$V = -40 \cdot C \text{ to } +105 \cdot C$

$M = -40 \cdot C \text{ to } + 125 \cdot C$

P = Plastic dual in-line package (PDIP)

DW = Small outline integrated circuit package (SOIC)

DT = Thin shrink small outline package (TSSOP)

FQ = Dual flat no lead (DFN)

Figure 17-1. Device Numbering System

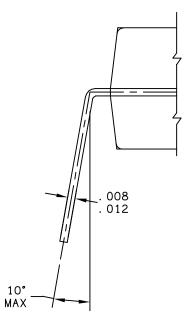

### 17.3 Package Dimensions

Refer to the following pages for detailed package dimensions.

DETAIL "D"

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED. |    | UTLINE     | PRINT VERSION NO | DT TO SCALE |

|------------------------------------------------------|----|------------|------------------|-------------|

| TITLE:                                               | DO | CUMENT NO  | ): 98ASB42420B   | REV: N      |

| 8 LD PDIP                                            | CA | SE NUMBER  | 8: 626–06        | 19 MAY 2005 |

|                                                      | ST | ANDARD: NO | N-JEDEC          |             |