Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                                                                                                     |                    |              |                                                                        |

|-------------------------------------------------------------------------------------------------------------|--------------------|--------------|------------------------------------------------------------------------|

|                                                                                                             | Obsolete           |              |                                                                        |

| Product Status                                                                                              |                    |              |                                                                        |

| Core Processor                                                                                              | HC08               |              |                                                                        |

| Core Size                                                                                                   | 8-Bit              |              |                                                                        |

| Speed                                                                                                       | 8MHz               |              |                                                                        |

| Connectivity                                                                                                | -                  |              |                                                                        |

| Peripherals                                                                                                 | LVD, POR, PWM      |              |                                                                        |

| Number of I/O                                                                                               | 13                 |              |                                                                        |

| Program Memory Size                                                                                         | 1.5KB (1.5K x 8)   |              |                                                                        |

| Program Memory Type                                                                                         | FLASH              |              |                                                                        |

| EEPROM Size                                                                                                 | -                  |              |                                                                        |

| RAM Size                                                                                                    | 128 x 8            |              |                                                                        |

| Voltage - Supply (Vcc/Vdd)                                                                                  | 2.7V ~ 5.5V        |              |                                                                        |

| Data Converters                                                                                             | A/D 6x10b          |              |                                                                        |

| Oscillator Type                                                                                             | Internal           |              |                                                                        |

| Operating Temperature                                                                                       | -40°C ~ 105°C (TA) |              |                                                                        |

| Mounting Type Surface Mount  Package / Case 16-SOIC (0.295", 7.50mm Width)  Supplier Device Package 16-SOIC |                    |              |                                                                        |

|                                                                                                             |                    | Purchase URL | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc908qy2avdwer |

6.7.2

6.8

#### **Table of Contents** 3.6 Input/Output Signals ...... 3.7 3.7.1 3.7.2 3.7.3 Chapter 4 **Auto Wakeup Module (AWU)** 4.1 4.2 4.3 4.4 4.5 4.6 4.6.1 Keyboard Status and Control Register......51 4.6.2 4.6.3 Keyboard Interrupt Enable Register..... 52 **Chapter 5** Configuration Register (CONFIG) 5.1 5.2 Chapter 6 **Computer Operating Properly (COP)** 6.1 6.2 6.3 6.3.1 6.3.2 6.3.3 6.3.4 6.3.5 6.3.6 6.3.7 6.4 6.5 6.6 6.7 6.7.1

## Chapter 12 Input/Output Ports (PORTS)

| 12.1    | Introduction                          | . 97 |

|---------|---------------------------------------|------|

| 12.2    | Port A                                | 97   |

| 12.2.1  | Port A Data Register                  |      |

| 12.2.2  | Data Direction Register A             |      |

| 12.2.3  | Port A Input Pullup Enable Register   | . 99 |

| 12.3    | Port B.                               | 100  |

| 12.3.1  | Port B Data Register                  |      |

| 12.3.2  | Data Direction Register B             |      |

| 12.3.3  | Port B Input Pullup Enable Register   | 102  |

|         | Chapter 13                            |      |

|         | System Integration Module (SIM)       |      |

| 13.1    | Introduction                          | 103  |

| 13.2    | RST and IRQ Pins Initialization       |      |

| 13.3    | SIM Bus Clock Control and Generation  |      |

| 13.3.1  | Bus Timing                            |      |

| 13.3.2  | Clock Start-Up from POR.              |      |

| 13.3.3  | Clocks in Stop Mode and Wait Mode     |      |

| 13.4    | Reset and System Initialization       |      |

| 13.4.1  | External Pin Reset                    |      |

| 13.4.2  | Active Resets from Internal Sources   | 106  |

| 13.4.2. |                                       |      |

| 13.4.2. |                                       |      |

| 13.4.2. | <b>3</b> 1                            |      |

| 13.4.2. |                                       |      |

| 13.4.2. |                                       |      |

|         | SIM Counter                           |      |

| 13.5.1  | SIM Counter During Power-On Reset     |      |

| 13.5.2  | SIM Counter During Stop Mode Recovery |      |

| 13.5.3  | SIM Counter and Reset States          |      |

| 13.6    | Exception Control.                    |      |

| 13.6.1  | Interrupts                            |      |

| 13.6.1. | · · · · · · · · · · · · · · · · · · · |      |

| 13.6.1. | 2 SWI Instruction                     |      |

| 13.6.2. | ·                                     |      |

| 13.6.2. |                                       |      |

| 13.6.2. |                                       |      |

| 13.6.3  | Reset                                 |      |

| 13.6.4  | Break Interrupts                      |      |

| 13.6.5  | Status Flag Protection in Break Mode  |      |

|         | Low-Power Modes                       |      |

| 13.7.1  | Wait Mode                             |      |

| 13.7.2  | Stop Mode                             |      |

MC68HC908QY/QT Family Data Sheet, Rev. 6

| 15.3               | Monitor Module (MON)                               | 138 |  |  |  |  |

|--------------------|----------------------------------------------------|-----|--|--|--|--|

| 15.3.1             | Functional Description                             | 139 |  |  |  |  |

| 15.3.1             | .1 Normal Monitor Mode                             | 142 |  |  |  |  |

|                    | 15.3.1.2 Forced Monitor Mode                       |     |  |  |  |  |

|                    | 15.3.1.3 Monitor Vectors                           |     |  |  |  |  |

| 15.3.1             |                                                    |     |  |  |  |  |

| 15.3.1             |                                                    |     |  |  |  |  |

| 15.3.1.<br>15.3.1. |                                                    |     |  |  |  |  |

| 15.3.1             |                                                    |     |  |  |  |  |

| 13.3.2             | Security                                           | 140 |  |  |  |  |

|                    | Chapter 16                                         |     |  |  |  |  |

|                    | Electrical Specifications                          |     |  |  |  |  |

| 16.1               | Introduction                                       | 149 |  |  |  |  |

| 16.2               | Absolute Maximum Ratings                           | 149 |  |  |  |  |

| 16.3               | Functional Operating Range                         | 150 |  |  |  |  |

| 16.4               | Thermal Characteristics                            | 150 |  |  |  |  |

| 16.5               | 5-V DC Electrical Characteristics                  | 151 |  |  |  |  |

| 16.6               | Typical 5-V Output Drive Characteristics           | 152 |  |  |  |  |

| 16.7               | 5-V Control Timing                                 | 153 |  |  |  |  |

| 16.8               | · · · · · · · · · · · · · · · · · · ·              |     |  |  |  |  |

| 16.9               | 3-V DC Electrical Characteristics                  | 155 |  |  |  |  |

| 16.10              | Typical 3.0-V Output Drive Characteristics         | 156 |  |  |  |  |

| 16.11              | 3-V Control Timing                                 | 157 |  |  |  |  |

| 16.12              | 3-V Oscillator Characteristics                     | 158 |  |  |  |  |

| 16.13              | Supply Current Characteristics                     | 159 |  |  |  |  |

| 16.14              | Analog-to-Digital Converter Characteristics        | 161 |  |  |  |  |

| 16.15              | Timer Interface Module Characteristics             | 162 |  |  |  |  |

| 16.16              | Memory Characteristics                             | 163 |  |  |  |  |

|                    | ·                                                  |     |  |  |  |  |

|                    | Chapter 17                                         |     |  |  |  |  |

| 47.4               | Ordering Information and Mechanical Specifications | 405 |  |  |  |  |

| 17.1               | Introduction                                       |     |  |  |  |  |

| 17.2               | MC Order Numbers                                   |     |  |  |  |  |

| 17.3               | Package Dimensions                                 | 165 |  |  |  |  |

**General Description**

Memory

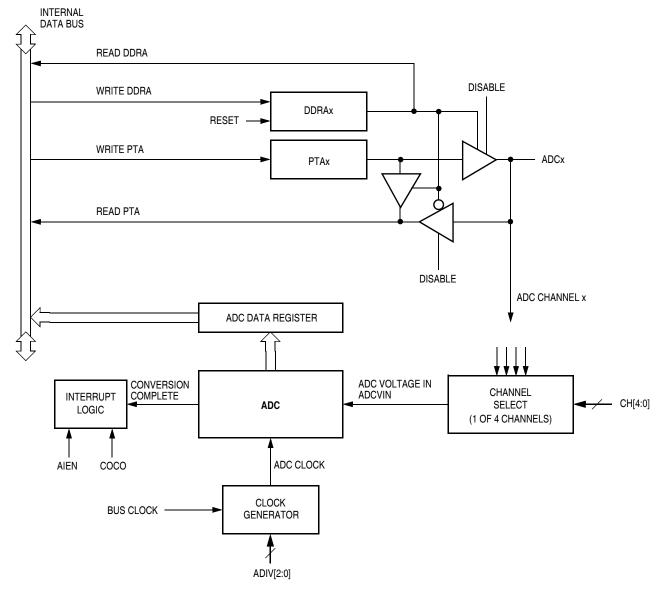

Figure 3-2. ADC Block Diagram

## Analog-to-Digital Converter (ADC)

## AIEN — ADC Interrupt Enable Bit

When this bit is set, an interrupt is generated at the end of an ADC conversion. The interrupt signal is cleared when ADR is read or ADSCR is written. Reset clears the AIEN bit.

- 1 = ADC interrupt enabled

- 0 = ADC interrupt disabled

## ADCO — ADC Continuous Conversion Bit

When set, the ADC will convert samples continuously and update ADR at the end of each conversion. Only one conversion is allowed when this bit is cleared. Reset clears the ADCO bit.

- 1 = Continuous ADC conversion

- 0 = One ADC conversion

## CH[4:0] — ADC Channel Select Bits

CH4, CH3, CH2, CH1, and CH0 form a 5-bit field which is used to select one of the four ADC channels. The five select bits are detailed in Table 3-1. Care should be taken when using a port pin as both an analog and a digital input simultaneously to prevent switching noise from corrupting the analog signal. The ADC subsystem is turned off when the channel select bits are all set to 1. This feature allows for reduced power consumption for the MCU when the ADC is not used. Reset sets all of these bits to 1.

#### NOTE

Recovery from the disabled state requires one conversion cycle to stabilize.

| CH4          | СНЗ          | CH2      | CH1          | СН0          | ADC<br>Channel | Input Select                    |  |

|--------------|--------------|----------|--------------|--------------|----------------|---------------------------------|--|

| 0            | 0            | 0        | 0            | 0            | ADC0           | PTA0                            |  |

| 0            | 0            | 0        | 0            | 1            | ADC1           | PTA1                            |  |

| 0            | 0            | 0        | 1            | 0            | ADC2           | PTA4                            |  |

| 0            | 0            | 0        | 1            | 1            | ADC3           | PTA5                            |  |

| 0            | 0            | 1        | 0            | 0            | _              |                                 |  |

| $\downarrow$ | $\downarrow$ | <b>\</b> | $\downarrow$ | $\downarrow$ | _              | Unused <sup>(1)</sup>           |  |

| 1            | 1            | 0        | 1            | 0            | _              |                                 |  |

| 1            | 1            | 0        | 1            | 1            | _              | Reserved                        |  |

| 1            | 1            | 1        | 0            | 0            | _              | Unused                          |  |

| 1            | 1            | 1        | 0            | 1            | _              | V <sub>DDA</sub> <sup>(2)</sup> |  |

| 1            | 1            | 1        | 1            | 0            | _              | V <sub>SSA</sub> <sup>(2)</sup> |  |

| 1            | 1            | 1        | 1            | 1            | _              | ADC power off                   |  |

Table 3-1. MUX Channel Select

If any unused channels are selected, the resulting ADC conversion will be unknown.

The voltage levels supplied from internal reference nodes, as specified in the table, are used to verify the operation of the ADC converter both in production test and for user applications.

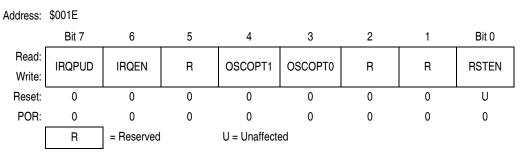

# **Chapter 5 Configuration Register (CONFIG)**

## 5.1 Introduction

This section describes the configuration registers (CONFIG1 and CONFIG2). The configuration registers enable or disable the following options:

- Stop mode recovery time (32 x BUSCLKX4 cycles or 4096 x BUSCLKX4 cycles)

- STOP instruction

- Computer operating properly module (COP)

- COP reset period (COPRS): 8176 × BUSCLKX4 or 262,128 × BUSCLKX4

- Low-voltage inhibit (LVI) enable and trip voltage selection

- OSC option selection

- IRQ pin

- RST pin

- Auto wakeup timeout period

## 5.2 Functional Description

The configuration registers are used in the initialization of various options. The configuration registers can be written once after each reset. Most of the configuration register bits are cleared during reset. Since the various options affect the operation of the microcontroller unit (MCU) it is recommended that this register be written immediately after reset. The configuration registers are located at \$001E and \$001F, and may be read at anytime.

## **NOTE**

The CONFIG registers are one-time writable by the user after each reset. Upon a reset, the CONFIG registers default to predetermined settings as shown in Figure 5-1 and Figure 5-2.

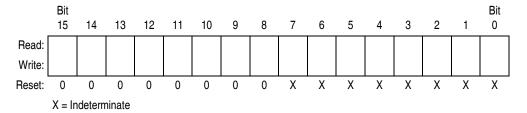

Figure 5-1. Configuration Register 2 (CONFIG2)

## **Computer Operating Properly (COP)**

The COP counter is a free-running 6-bit counter preceded by the 12-bit system integration module (SIM) counter. If not cleared by software, the COP counter overflows and generates an asynchronous reset after 262,128 or 8176 BUSCLKX4 cycles; depending on the state of the COP rate select bit, COPRS, in configuration register 1. With a 262,128 BUSCLKX4 cycle overflow option, the internal 12.8-MHz oscillator gives a COP timeout period of 20.48 ms. Writing any value to location \$FFFF before an overflow occurs prevents a COP reset by clearing the COP counter and stages 12–5 of the SIM counter.

#### NOTE

Service the COP immediately after reset and before entering or after exiting stop mode to guarantee the maximum time before the first COP counter overflow.

A COP reset pulls the  $\overline{RST}$  pin low (if the RSTEN bit is set in the CONFIG1 register) for  $32 \times BUSCLKX4$  cycles and sets the COP bit in the reset status register (RSR). See 13.8.1 SIM Reset Status Register.

#### NOTE

Place COP clearing instructions in the main program and not in an interrupt subroutine. Such an interrupt subroutine could keep the COP from generating a reset even while the main program is not working properly.

## 6.3 I/O Signals

The following paragraphs describe the signals shown in Figure 6-1.

## 6.3.1 BUSCLKX4

BUSCLKX4 is the oscillator output signal. BUSCLKX4 frequency is equal to the internal oscillator frequency, the crystal frequency, or the RC-oscillator frequency.

## 6.3.2 STOP Instruction

The STOP instruction clears the SIM counter.

## 6.3.3 COPCTL Write

Writing any value to the COP control register (COPCTL) (see 6.4 COP Control Register) clears the COP counter and clears stages 12–5 of the SIM counter. Reading the COP control register returns the low byte of the reset vector.

## 6.3.4 Power-On Reset

The power-on reset (POR) circuit in the SIM clears the SIM counter  $4096 \times BUSCLKX4$  cycles after power up.

## 6.3.5 Internal Reset

An internal reset clears the SIM counter and the COP counter.

## 6.3.6 COPD (COP Disable)

The COPD signal reflects the state of the COP disable bit (COPD) in the configuration register 1 (CONFIG1). See Chapter 5 Configuration Register (CONFIG).

MC68HC908QY/QT Family Data Sheet, Rev. 6

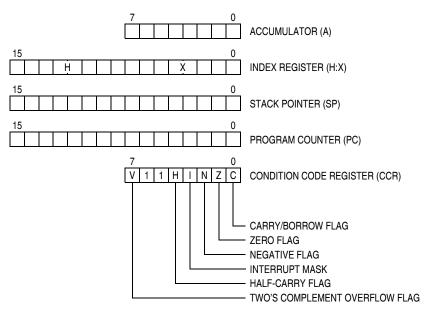

## **Central Processor Unit (CPU)**

Figure 7-1. CPU Registers

## 7.3.1 Accumulator

The accumulator is a general-purpose 8-bit register. The CPU uses the accumulator to hold operands and the results of arithmetic/logic operations.

Figure 7-2. Accumulator (A)

## 7.3.2 Index Register

The 16-bit index register allows indexed addressing of a 64-Kbyte memory space. H is the upper byte of the index register, and X is the lower byte. H:X is the concatenated 16-bit index register.

In the indexed addressing modes, the CPU uses the contents of the index register to determine the conditional address of the operand.

The index register can serve also as a temporary data storage location.

Figure 7-3. Index Register (H:X)

MC68HC908QY/QT Family Data Sheet, Rev. 6

# **Chapter 11 Oscillator Module (OSC)**

## 11.1 Introduction

The oscillator module is used to provide a stable clock source for the microcontroller system and bus. The oscillator module generates two output clocks, BUSCLKX2 and BUSCLKX4. The BUSCLKX4 clock is used by the system integration module (SIM) and the computer operating properly module (COP). The BUSCLKX2 clock is divided by two in the SIM to be used as the bus clock for the microcontroller. Therefore the bus frequency will be one fourth of the BUSCLKX4 frequency.

## 11.2 Features

The oscillator has these four clock source options available:

- 1. Internal oscillator: An internally generated, fixed frequency clock, trimmable to ±5%. This is the default option out of reset.

- 2. External oscillator: An external clock that can be driven directly into OSC1.

- 3. External RC: A built-in oscillator module (RC oscillator) that requires an external R connection only. The capacitor is internal to the chip.

- 4. External crystal: A built-in oscillator module (XTAL oscillator) that requires an external crystal or ceramic-resonator.

## 11.3 Functional Description

The oscillator contains these major subsystems:

- Internal oscillator circuit

- Internal or external clock switch control

- External clock circuit

- External crystal circuit

- External RC clock circuit

again in the SIM and results in the internal bus frequency being one fourth of either the XTALCLK, RCCLK, or INTCLK frequency.

## 11.5 Low Power Modes

The WAIT and STOP instructions put the MCU in low-power consumption standby modes.

## 11.5.1 Wait Mode

The WAIT instruction has no effect on the oscillator logic. BUSCLKX2 and BUSCLKX4 continue to drive to the SIM module.

## 11.5.2 Stop Mode

The STOP instruction disables either the XTALCLK, the RCCLK, or INTCLK output, hence BUSCLKX2 and BUSCLKX4.

## 11.6 Oscillator During Break Mode

The oscillator continues to drive BUSCLKX2 and BUSCLKX4 when the device enters the break state.

## 11.7 CONFIG2 Options

Two CONFIG2 register options affect the operation of the oscillator module: OSCOPT1 and OSCOPT0. All CONFIG2 register bits will have a default configuration. Refer to Chapter 5 Configuration Register (CONFIG) for more information on how the CONFIG2 register is used.

Table 11-2 shows how the OSCOPT bits are used to select the oscillator clock source.

OSCOPT1

OSCOPT0

Oscillator Modes

0

0

Internal oscillator

0

1

External oscillator

1

0

External RC

1

1

External crystal

Table 11-2. Oscillator Modes

## 11.8 Input/Output (I/O) Registers

The oscillator module contains these two registers:

- 1. Oscillator status register (OSCSTAT)

- 2. Oscillator trim register (OSCTRIM)

Freescale Semiconductor 95

MC68HC908QY/QT Family Data Sheet, Rev. 6

## **System Integration Module (SIM)**

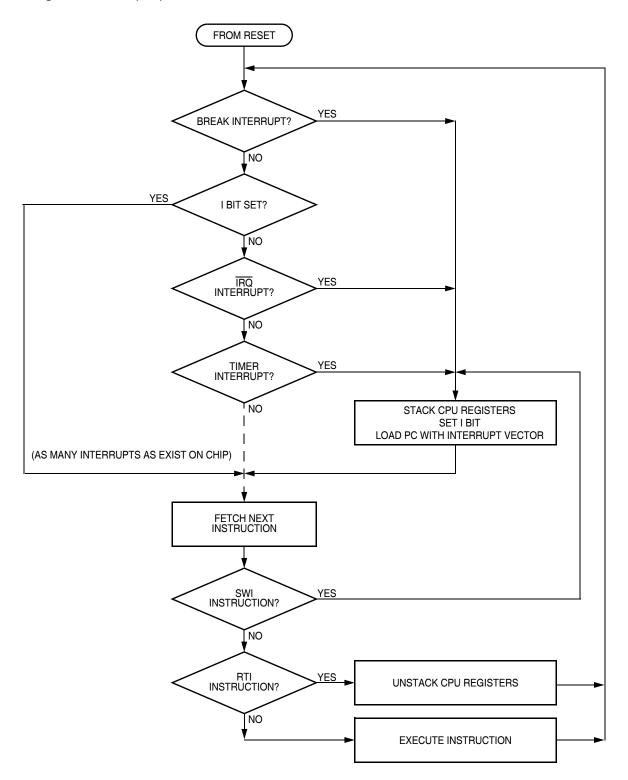

Figure 13-7. Interrupt Processing

**System Integration Module (SIM)**

## 13.6.3 Reset

All reset sources always have equal and highest priority and cannot be arbitrated.

## 13.6.4 Break Interrupts

The break module can stop normal program flow at a software programmable break point by asserting its break interrupt output. (See Chapter 15 Development Support.) The SIM puts the CPU into the break state by forcing it to the SWI vector location. Refer to the break interrupt subsection of each module to see how each module is affected by the break state.

## 13.6.5 Status Flag Protection in Break Mode

The SIM controls whether status flags contained in other modules can be cleared during break mode. The user can select whether flags are protected from being cleared by properly initializing the break clear flag enable bit (BCFE) in the break flag control register (BFCR).

Protecting flags in break mode ensures that set flags will not be cleared while in break mode. This protection allows registers to be freely read and written during break mode without losing status flag information.

Setting the BCFE bit enables the clearing mechanisms. Once cleared in break mode, a flag remains cleared even when break mode is exited. Status flags with a two-step clearing mechanism — for example, a read of one register followed by the read or write of another — are protected, even when the first step is accomplished prior to entering break mode. Upon leaving break mode, execution of the second step will clear the flag as normal.

## 13.7 Low-Power Modes

Executing the WAIT or STOP instruction puts the MCU in a low power- consumption mode for standby situations. The SIM holds the CPU in a non-clocked state. The operation of each of these modes is described below. Both STOP and WAIT clear the interrupt mask (I) in the condition code register, allowing interrupts to occur.

## 13.7.1 Wait Mode

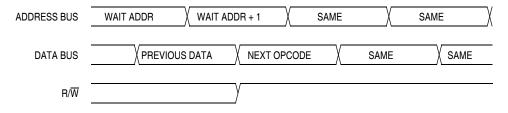

In wait mode, the CPU clocks are inactive while the peripheral clocks continue to run. Figure 13-14 shows the timing for wait mode entry.

NOTE: Previous data can be operand data or the WAIT opcode, depending on the last instruction.

Figure 13-14. Wait Mode Entry Timing

MC68HC908QY/QT Family Data Sheet, Rev. 6

#### Timer Interface Module (TIM)

## 14.4.4.1 Unbuffered PWM Signal Generation

Any output compare channel can generate unbuffered PWM pulses as described in 14.4.4 Pulse Width Modulation (PWM). The pulses are unbuffered because changing the pulse width requires writing the new pulse width value over the old value currently in the TIM channel registers.

An unsynchronized write to the TIM channel registers to change a pulse width value could cause incorrect operation for up to two PWM periods. For example, writing a new value before the counter reaches the old value but after the counter reaches the new value prevents any compare during that PWM period. Also, using a TIM overflow interrupt routine to write a new, smaller pulse width value may cause the compare to be missed. The TIM may pass the new value before it is written.

Use the following methods to synchronize unbuffered changes in the PWM pulse width on channel x:

- When changing to a shorter pulse width, enable channel x output compare interrupts and write the

new value in the output compare interrupt routine. The output compare interrupt occurs at the end

of the current pulse. The interrupt routine has until the end of the PWM period to write the new

value.

- When changing to a longer pulse width, enable TIM overflow interrupts and write the new value in the TIM overflow interrupt routine. The TIM overflow interrupt occurs at the end of the current PWM period. Writing a larger value in an output compare interrupt routine (at the end of the current pulse) could cause two output compares to occur in the same PWM period.

#### NOTE

In PWM signal generation, do not program the PWM channel to toggle on output compare. Toggling on output compare prevents reliable 0% duty cycle generation and removes the ability of the channel to self-correct in the event of software error or noise. Toggling on output compare also can cause incorrect PWM signal generation when changing the PWM pulse width to a new, much larger value.

## 14.4.4.2 Buffered PWM Signal Generation

Channels 0 and 1 can be linked to form a buffered PWM channel whose output appears on the TCH0 pin. The TIM channel registers of the linked pair alternately control the pulse width of the output.

Setting the MS0B bit in TIM channel 0 status and control register (TSC0) links channel 0 and channel 1. The TIM channel 0 registers initially control the pulse width on the TCH0 pin. Writing to the TIM channel 1 registers enables the TIM channel 1 registers to synchronously control the pulse width at the beginning of the next PWM period. At each subsequent overflow, the TIM channel registers (0 or 1) that control the pulse width are the ones written to last. TSC0 controls and monitors the buffered PWM function, and TIM channel 1 status and control register (TSC1) is unused. While the MS0B bit is set, the channel 1 pin, TCH1, is available as a general-purpose I/O pin.

#### NOTE

In buffered PWM signal generation, do not write new pulse width values to the currently active channel registers. User software should track the currently active channel to prevent writing a new value to the active channel. Writing to the active channel registers is the same as generating unbuffered PWM signals.

## **Electrical Specifications**

## 16.8 5-V Oscillator Characteristics

| Characteristic                                                                                                                                                                            | Symbol             | Min         | Тур                | Max           | Unit |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------|--------------------|---------------|------|

| Internal oscillator frequency <sup>(1)</sup>                                                                                                                                              | fINTCLK            | _           | 12.8               | _             | MHz  |

| Deviation from trimmed Internal oscillator <sup>(2)(3)</sup> 12.8 MHz, fixed voltage, fixed temp 12.8 MHz, V <sub>DD</sub> ± 10%, 0 to 70°C 12.8 MHz, V <sub>DD</sub> ± 10%, –40 to 125°C | ACC <sub>INT</sub> | _<br>_<br>_ | ± 0.4<br>± 2<br>—  | —<br>—<br>± 5 | %    |

| Crystal frequency, XTALCLK <sup>(1)</sup>                                                                                                                                                 | foscxclk           | 1           | _                  | 24            | MHz  |

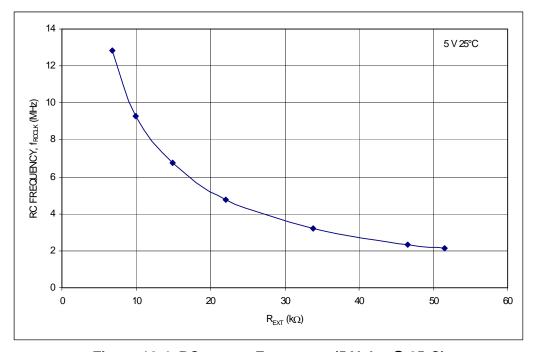

| External RC oscillator frequency, RCCLK <sup>(1)</sup>                                                                                                                                    | f <sub>RCCLK</sub> | 2           | _                  | 12            | MHz  |

| External clock reference frequency <sup>(1)</sup> (4)                                                                                                                                     | foscxclk           | dc          | _                  | 32            | MHz  |

| Crystal load capacitance <sup>(5)</sup>                                                                                                                                                   | CL                 | _           | 20                 | _             | pF   |

| Crystal fixed capacitance <sup>(3)</sup>                                                                                                                                                  | C <sub>1</sub>     | _           | 2 x C <sub>L</sub> | _             | _    |

| Crystal tuning capacitance <sup>(3)</sup>                                                                                                                                                 | C <sub>2</sub>     | _           | 2 x C <sub>L</sub> | _             | _    |

| Feedback bias resistor                                                                                                                                                                    | R <sub>B</sub>     | 0.5         | 1                  | 10            | MΩ   |

| RC oscillator external resistor                                                                                                                                                           | R <sub>EXT</sub>   | Ş           | See Figure 16-     | 4             | _    |

| Crystal series damping resistor $f_{OSCXCLK} = 1 \text{ MHz}$ $f_{OSCXCLK} = 4 \text{ MHz}$ $f_{OSCXCLK} = 8 \text{ MHz}$                                                                 | R <sub>S</sub>     | _<br>_<br>_ | 20<br>10<br>0      | _<br>_<br>_   | kΩ   |

- Bus frequency, f<sub>OP</sub>, is oscillator frequency divided by 4.

Deviation values assumes trimming @25•C and midpoint of voltage range.

Values are based on characterization results, not tested in production.

No more than 10% duty cycle deviation from 50%.

- 5. Consult crystal vendor data sheet.

Figure 16-4. RC versus Frequency (5 Volts @ 25•C)

MC68HC908QY/QT Family Data Sheet, Rev. 6

© FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED.

ELECTRONIC VERSIONS ARE UNCONTROLLED EXCEPT WHEN ACCESSED

DIRECTLY FROM THE DOCUMENT CONTROL REPOSITORY, PRINTED VERSIONS

ARE UNCONTROLLED EXCEPT WHEN STAMPED "CONTROLLED COPY" IN RED

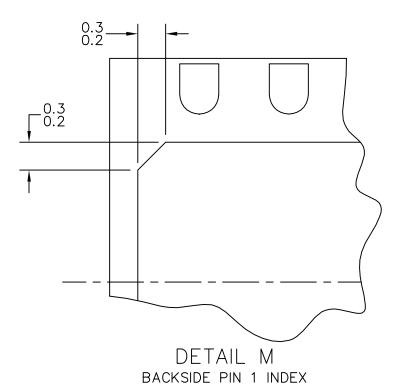

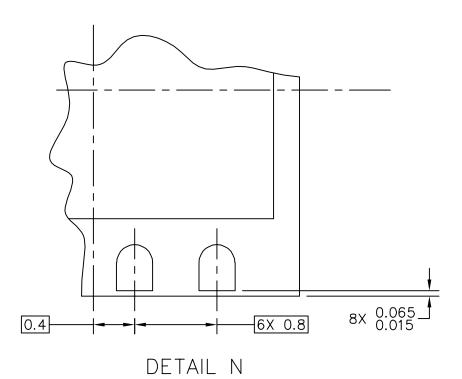

## MECHANICAL OUTLINES DICTIONARY

DO NOT SCALE THIS DRAWING

DOCUMENT NO: 98ARL10557D

PAGE: 1452

REV: A

TITLE: THERMALLY ENHANCED DUAL FLAT NO LEAD PACKAGE (DFN) 8 TERMINAL, 0.8 PITCH (4 X 4 X 1)

CASE NUMBER: 1452-01

STANDARD: NON-JEDEC

PACKAGE CODE: 6165 | SHEET: 3 OF 5

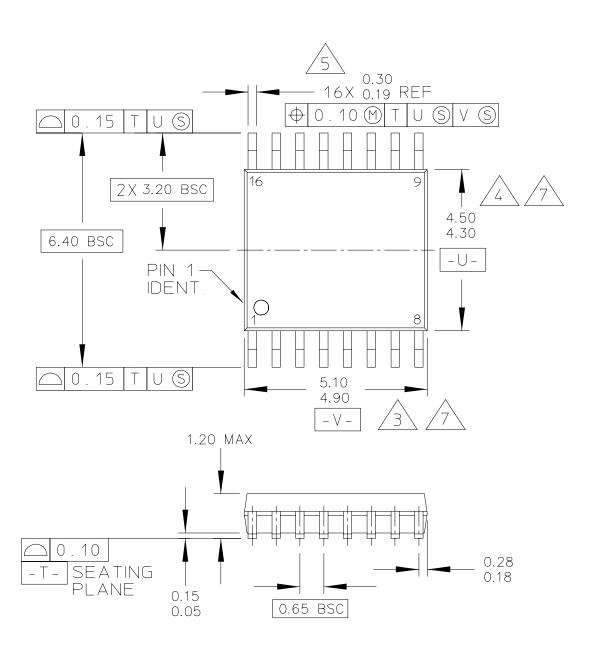

## MECHANICAL OUTLINES DICTIONARY

DO NOT SCALE THIS DRAWING

DOCUMENT NO: 98ASB42567B 751G

PAGE:

REV: Ε

NOTES:

DIMENSIONS ARE IN MILLIMETERS.

DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

DATUMS A AND B TO BE DETERMINED AT THE PLANE WHERE THE BOTTOM OF THE LEADS EXIT THE PLASTIC BODY.

THIS DIMENSION DOES NOT INCLUDE MOLD FLASH, PROTRUSION OR GATE BURRS. MOLD FLASH, PROTRUSION OR GATE BURRS SHALL NOT EXCEED 0.15 MM PER SIDE. THIS DIMENSION IS DETERMINED AT THE PLANE WHERE THE BOTTOM OF THE LEADS EXIT THE PLASTIC BODY.

THIS DIMENSION DOES NOT INCLUDE INTER-LEAD FLASH OR PROTRUSIONS. INTER-LEAD FLASH AND PROTRUSIONS SHALL NOT EXCEED 0.25 MM PER SIDE. THIS DIMENSION IS DETERMINED AT THE PLANE WHERE THE BOTTOM OF THE LEADS EXIT THE PLASTIC BODY.

/6\ THIS DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL NOT CAUSE THE LEAD WIDTH TO EXCEED 0.62 mm.

TITLE:

16LD SOIC W/B, 1.27 PITCH, CASE OUTLINE

CASE NUMBER: 751G-05

STANDARD: JEDEC MS-013AA

PACKAGE CODE: 2003 SHEET: 2 OF 3

FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED.

ELECTRONIC VERSIONS ARE UNCONTROLLED EXCEPT WHEN ACCESSED DIRECTLY FROM THE DOCUMENT CONTROL REPOSITORY. PRINTED VERSIONS ARE UNCONTROLLED EXCEPT WHEN STAMPED 'CONTROLLED COPY' IN RED.

## MECHANICAL DUTLINES DICTIONARY

DO NOT SCALE THIS DRAWING

| DOCUMENT | N□: | 98ASH70247A |

|----------|-----|-------------|

| PAGE:    |     | 948F        |

В

REV:

| TITLE:                    | CASE NUMBER: 948F-01             |  |  |

|---------------------------|----------------------------------|--|--|

| 16 LD TSSOP, PITCH 0.65MM | STANDARD: JEDEC                  |  |  |

|                           | PACKAGE CODE: 6117 SHEET: 1 OF 4 |  |  |

Semiconductor

© FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED.

ECONOMIC VERSIONS ARE UNCONTROLLED EXCEPT WHEN ACCESSED

DIRECTLY FROM THE DIOCUMENT CONTROLL REPOSITIORY. PRINTED

DIRECTLY FROM THE DIOCUMENT CONTROLL REPOSITIORY. PRINTED

| MECHANICAL DUTLINES       | DOCUMENT NO: 98ASH70247A |

|---------------------------|--------------------------|

| DICTIONARY                | PAGE: 948F               |

| DO NOT SCALE THIS DRAWING | REV: B                   |

## NOTES:

- 1. CONTROLLING DIMENSION: MILLIMETER

- 2. DIMENSIONS AND TOLERANCES PER ANSI Y14.5M-1982.

DIMENSION DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS. MOLD FLASH OR GATE BURRS SHALL NOT EXCEED 0.15 PER SIDE.

DIMENSION DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION.

INTERLEAD FLASH OR PROTRUSION SHALL NOT EXCEED 0.25 PER SIDE.

DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.08 TOTAL IN EXCESS OF THE DIMENSION AT MAXIMUM MATERIAL CONDITION.

6. TERMINAL NUMBERS ARE SHOWN FOR REFERENCE ONLY.

DIMENSIONS ARE TO BE DETERMINED AT DATUM PLANE [-W-]

| TITLE:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | CASE NUMBER: 948F-01             |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|--|--|--|

| 16 LD TSSOP, PITCH 0.65MM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | STANDARD: JEDEC                  |  |  |  |

| The Late of the second | PACKAGE CODE: 6117 SHEET: 3 OF 4 |  |  |  |