Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                               |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | HC08                                                                   |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 8MHz                                                                   |

| Connectivity               | -                                                                      |

| Peripherals                | LVD, POR, PWM                                                          |

| Number of I/O              | 5                                                                      |

| Program Memory Size        | 1.5KB (1.5K x 8)                                                       |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 128 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                            |

| Data Converters            | -                                                                      |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 8-SOIC (0.209", 5.30mm Width)                                          |

| Supplier Device Package    | 8-SO                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mchc908qt1cdwe |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

MC68HC908QY4 MC68HC908QT4 MC68HC908QY2 MC68HC908QT2 MC68HC908QY1 MC68HC908QT1

**Data Sheet**

To provide the most up-to-date information, the revision of our documents on the World Wide Web will be the most current. Your printed copy may be an earlier revision. To verify you have the latest information available, refer to:

http://freescale.com/

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. This product incorporates SuperFlash® technology licensed from SST.

© Freescale Semiconductor, Inc., 2005–2010. All rights reserved.

MC68HC908QY/QT Family Data Sheet, Rev. 6

List of Chapters

# **1.6 Pin Function Priority**

Table 1-3 is meant to resolve the priority if multiple functions are enabled on a single pin.

NOTE

Upon reset all pins come up as input ports regardless of the priority table.

| Pin Name | Highest-to-Lowest Priority Sequence                                                             |

|----------|-------------------------------------------------------------------------------------------------|

| PTA0     | $AD0 \rightarrow TCH0 \rightarrow KBI0 \rightarrow PTA0$                                        |

| PTA1     | $AD1 \rightarrow TCH1 \rightarrow KBI1 \rightarrow PTA1$                                        |

| PTA2     | $\overline{\text{IRQ}} \rightarrow \text{KBI2} \rightarrow \text{TCLK} \rightarrow \text{PTA2}$ |

| PTA3     | $\overline{\text{RST}} \rightarrow \text{KBI3} \rightarrow \text{PTA3}$                         |

| PTA4     | $OSC2 \rightarrow AD2 \rightarrow KBI4 \rightarrow PTA4$                                        |

| PTA5     | $OSC1 \rightarrow AD3 \rightarrow KBI5 \rightarrow PTA5$                                        |

# Table 1-3. Function Priority in Shared Pins

FLASH Memory (FLASH)

# 2.6 FLASH Memory (FLASH)

This subsection describes the operation of the embedded FLASH memory. The FLASH memory can be read, programmed, and erased from a single external supply. The program and erase operations are enabled through the use of an internal charge pump.

The FLASH memory consists of an array of 4096 or 1536 bytes with an additional 48 bytes for user vectors. The minimum size of FLASH memory that can be erased is 64 bytes; and the maximum size of FLASH memory that can be programmed in a program cycle is 32 bytes (a row). Program and erase operations are facilitated through control bits in the FLASH control register (FLCR). Details for these operations appear later in this section. The address ranges for the user memory and vectors are:

- \$EE00 \$FDFF; user memory, 4096 bytes: MC68HC908QY4 and MC68HC908QT4

- \$F800 \$FDFF; user memory, 1536 bytes: MC68HC908QY2, MC68HC908QT2, MC68HC908QY1 and MC68HC908QT1

- \$FFD0 \$FFFF; user interrupt vectors, 48 bytes.

### NOTE

An erased bit reads as a 1 and a programmed bit reads as a 0. A security feature prevents viewing of the FLASH contents.<sup>(1)</sup>

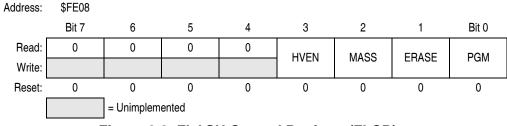

# 2.6.1 FLASH Control Register

The FLASH control register (FLCR) controls FLASH program and erase operations.

Figure 2-3. FLASH Control Register (FLCR)

### HVEN — High Voltage Enable Bit

This read/write bit enables high voltage from the charge pump to the memory for either program or erase operation. It can only be set if either PGM =1 or ERASE =1 and the proper sequence for program or erase is followed.

- 1 = High voltage enabled to array and charge pump on

- 0 = High voltage disabled to array and charge pump off

# MASS — Mass Erase Control Bit

This read/write bit configures the memory for mass erase operation.

- 1 = Mass erase operation selected

- 0 = Mass erase operation unselected

<sup>1.</sup> No security feature is absolutely secure. However, Freescale's strategy is to make reading or copying the FLASH difficult for unauthorized users.

Memory

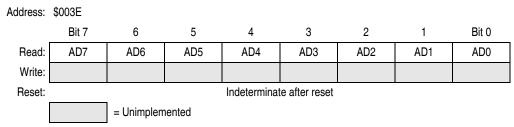

# 3.7.2 ADC Data Register

One 8-bit result register is provided. This register is updated each time an ADC conversion completes.

Figure 3-4. ADC Data Register (ADR)

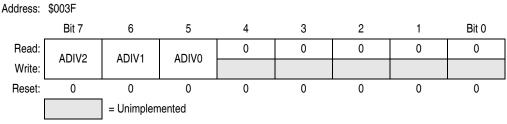

# 3.7.3 ADC Input Clock Register

This register selects the clock frequency for the ADC.

Figure 3-5. ADC Input Clock Register (ADICLK)

# ADIV2–ADIV0 — ADC Clock Prescaler Bits

ADIV2, ADIV1, and ADIV0 form a 3-bit field which selects the divide ratio used by the ADC to generate the internal ADC clock. Table 3-2 shows the available clock configurations. The ADC clock frequency should be set between  $f_{ADIC(MIN)}$  and  $f_{ADIC(MAX)}$ . The analog input level should remain stable for the entire conversion time (maximum = 17 ADC clock cycles).

| ADIV2 | ADIV1 | ADIV0 | ADC Clock Rate |  |  |

|-------|-------|-------|----------------|--|--|

| 0     | 0     | 0     | Bus clock ÷ 1  |  |  |

| 0     | 0     | 1     | Bus clock ÷ 2  |  |  |

| 0     | 1     | 0     | Bus clock ÷ 4  |  |  |

| 0     | 1     | 1     | Bus clock ÷ 8  |  |  |

| 1     | Х     | Х     | Bus clock ÷ 16 |  |  |

Table 3-2. ADC Clock Divide Ratio

X = don't care

# 6.3.7 COPRS (COP Rate Select)

The COPRS signal reflects the state of the COP rate select bit (COPRS) in the configuration register 1 (CONFIG1). See Chapter 5 Configuration Register (CONFIG).

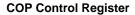

# 6.4 COP Control Register

The COP control register (COPCTL) is located at address \$FFFF and overlaps the reset vector. Writing any value to \$FFFF clears the COP counter and starts a new timeout period. Reading location \$FFFF returns the low byte of the reset vector.

Figure 6-2. COP Control Register (COPCTL)

# 6.5 Interrupts

The COP does not generate CPU interrupt requests.

# 6.6 Monitor Mode

The COP is disabled in monitor mode when  $V_{TST}$  is present on the IRQ pin.

# 6.7 Low-Power Modes

The WAIT and STOP instructions put the MCU in low power-consumption standby modes.

# 6.7.1 Wait Mode

The COP continues to operate during wait mode. To prevent a COP reset during wait mode, periodically clear the COP counter.

# 6.7.2 Stop Mode

Stop mode turns off the BUSCLKX4 input to the COP and clears the SIM counter. Service the COP immediately before entering or after exiting stop mode to ensure a full COP timeout period after entering or exiting stop mode.

# 6.8 COP Module During Break Mode

The COP is disabled during a break interrupt with monitor mode when BDCOP bit is set in break auxiliary register (BRKAR).

**Central Processor Unit (CPU)**

# 7.7 Instruction Set Summary

Table 7-1 provides a summary of the M68HC08 instruction set.

| Source                                                                                           | Operation                                            | Description                                                         |   |     | Effect<br>on CCR |           |           |   | Address<br>Mode                                                                                          | Opcode                                           | Operand                                            | les                                  |

|--------------------------------------------------------------------------------------------------|------------------------------------------------------|---------------------------------------------------------------------|---|-----|------------------|-----------|-----------|---|----------------------------------------------------------------------------------------------------------|--------------------------------------------------|----------------------------------------------------|--------------------------------------|

| Form                                                                                             |                                                      |                                                                     |   |     | I                | Ν         | z         | С | Add<br>Mod                                                                                               | Opc                                              | Ope                                                | Cycles                               |

| ADC #opr<br>ADC opr<br>ADC opr<br>ADC opr,X<br>ADC opr,X<br>ADC opr,SP<br>ADC opr,SP             | Add with Carry                                       | A ← (A) + (M) + (C)                                                 | ţ | ţ   | _                | ţ         | ţ         | ţ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2                                                      | A9<br>B9<br>C9<br>D9<br>E9<br>F9<br>9EE9<br>9ED9 | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ee ff          | 2<br>3<br>4<br>3<br>2<br>4<br>5      |

| ADD #opr<br>ADD opr<br>ADD opr<br>ADD opr,X<br>ADD opr,X<br>ADD ,X<br>ADD ,X<br>ADD opr,SP       | Add without Carry                                    | A ← (A) + (M)                                                       | t | ţ   | _                | t         | ţ         | ţ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2                                                      | AB<br>BB<br>CB<br>DB<br>EB<br>FB<br>9EEB<br>9EDB | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ee ff          | 2<br>3<br>4<br>3<br>2<br>4<br>5      |

| AIS #opr                                                                                         | Add Immediate Value (Signed) to SP                   | $SP \leftarrow (SP) + (16 \ \ensuremath{M})$                        | - | -   | -                | —         | -         | - | IMM                                                                                                      | A7                                               | ii                                                 | 2                                    |

| AIX #opr                                                                                         | Add Immediate Value (Signed) to H:X                  | $H:X \leftarrow (H:X) + (16 \ \ M)$                                 | - | -   | -                | —         | —         | - | IMM                                                                                                      | AF                                               | ii                                                 | 2                                    |

| AND #opr<br>AND opr<br>AND opr,X<br>AND opr,X<br>AND opr,X<br>AND ,X<br>AND opr,SP<br>AND opr,SP | Logical AND                                          | A ← (A) & (M)                                                       | 0 | _   | _                | ţ         | ţ         | _ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2                                                      | A4<br>B4<br>C4<br>D4<br>E4<br>F4<br>9EE4<br>9ED4 | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ff<br>ee ff    | 2<br>3<br>4<br>3<br>2<br>4<br>5      |

| ASL opr<br>ASLA<br>ASLX<br>ASL opr,X<br>ASL ,X<br>ASL opr,SP                                     | Arithmetic Shift Left<br>(Same as LSL)               | C ←                                                                 | ţ | _   | _                | ţ         | ţ         | ţ | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1                                                                    | 38<br>48<br>58<br>68<br>78<br>9E68               | dd<br>ff<br>ff                                     | 4<br>1<br>4<br>3<br>5                |

| ASR opr<br>ASRA<br>ASRX<br>ASR opr,X<br>ASR opr,X<br>ASR opr,SP                                  | Arithmetic Shift Right                               |                                                                     | t | _   | -                | ţ         | ţ         | ţ | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1                                                                    | 37<br>47<br>57<br>67<br>77<br>9E67               | dd<br>ff<br>ff                                     | 4<br>1<br>4<br>3<br>5                |

| BCC rel                                                                                          | Branch if Carry Bit Clear                            | $PC \leftarrow (PC) + 2 + rel ? (C) = 0$                            | - | -   | -                | -         | -         | - | REL                                                                                                      | 24                                               | rr                                                 | 3                                    |

| BCLR n, opr                                                                                      | Clear Bit n in M                                     | Mn ← 0                                                              | _ | -   | -                | -         | -         | - | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7) | 11<br>13<br>15<br>17<br>19<br>1B<br>1D<br>1F     | dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd | 4<br>4<br>4<br>4<br>4<br>4<br>4<br>4 |

| BCS rel                                                                                          | Branch if Carry Bit Set (Same as BLO)                | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (C) = 1$                   | - | -   | -                | -         | -         | - | REL                                                                                                      | 25                                               | rr                                                 | 3                                    |

| BEQ rel                                                                                          | Branch if Equal                                      | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (Z) = 1$                   | - | [-] | _                | <u> -</u> | -         | - | REL                                                                                                      | 27                                               | rr                                                 | 3                                    |

| BGE opr                                                                                          | Branch if Greater Than or Equal To (Signed Operands) | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (N \oplus V) = 0$          | - | -   | -                | -         | -         | - | REL                                                                                                      | 90                                               | rr                                                 | 3                                    |

| BGT opr                                                                                          | Branch if Greater Than (Signed<br>Operands)          | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (Z) \mid (N \oplus V) = 0$ | - | -   | -                | -         | -         | - | REL                                                                                                      | 92                                               | rr                                                 | 3                                    |

| BHCC rel                                                                                         | Branch if Half Carry Bit Clear                       | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (H) = 0$                   | - | -   | _                | <u> -</u> | <u> -</u> | - | REL                                                                                                      | 28                                               | rr                                                 | 3                                    |

| BHCS rel                                                                                         | Branch if Half Carry Bit Set                         | $PC \leftarrow (PC) + 2 + rel? (H) = 1$                             | - | -   | -                | -         | -         | - | REL                                                                                                      | 29                                               | rr                                                 | 3                                    |

| BHI rel                                                                                          | Branch if Higher                                     | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (C) \mid (Z) = 0$          | - | [-  | -                | -         | -         | - | REL                                                                                                      | 22                                               | rr                                                 | 3                                    |

# Table 7-1. Instruction Set Summary (Sheet 1 of 6)

# 11.3.1.1 Internal Oscillator Trimming

The 8-bit trimming register, OSCTRIM, allows a clock period adjust of +127 and -128 steps. Increasing OSCTRIM value increases the clock period. Trimming allows the internal clock frequency to be set to 12.8 MHz  $\pm$  5%.

All devices are factory programmed with trim values in reserved FLASH memory locations \$FFC0 and \$FFC1. The trim value is not automatically loaded into the OSCTRIM register. User software must copy the trim value from \$FFC0 or \$FFC1 into OSCTRIM if needed. The factory trim value provides the accuracy required for communication using forced monitor mode. Some production programmers erase the factory trim values, so confirm with your programmer vendor that the trim values at \$FFC0 and \$FFC1 are preserved, or are re-trimmed. Trimming the device in the user application board will provide the most accurate trim value.

# 11.3.1.2 Internal to External Clock Switching

When external clock source (external OSC, RC, or XTAL) is desired, the user must perform the following steps:

- 1. For external crystal circuits only, OSCOPT[1:0] = 1:1: To help precharge an external crystal oscillator, set PTA4 (OSC2) as an output and drive high for several cycles. This may help the crystal circuit start more robustly.

- Set CONFIG2 bits OSCOPT[1:0] according to . The oscillator module control logic will then set OSC1 as an external clock input and, if the external crystal option is selected, OSC2 will also be set as the clock output.

- 3. Create a software delay to wait the stabilization time needed for the selected clock source (crystal, resonator, RC) as recommended by the component manufacturer. A good rule of thumb for crystal oscillators is to wait 4096 cycles of the crystal frequency, i.e., for a 4-MHz crystal, wait approximately 1 msec.

- 4. After the manufacturer's recommended delay has elapsed, the ECGON bit in the OSC status register (OSCSTAT) needs to be set by the user software.

- 5. After ECGON set is detected, the OSC module checks for oscillator activity by waiting two external clock rising edges.

- 6. The OSC module then switches to the external clock. Logic provides a glitch free transition.

- 7. The OSC module first sets the ECGST bit in the OSCSTAT register and then stops the internal oscillator.

### NOTE

Once transition to the external clock is done, the internal oscillator will only be reactivated with reset. No post-switch clock monitor feature is implemented (clock does not switch back to internal if external clock dies).

# 11.3.2 External Oscillator

The external clock option is designed for use when a clock signal is available in the application to provide a clock source to the microcontroller. The OSC1 pin is enabled as an input by the oscillator module. The clock signal is used directly to create BUSCLKX4 and also divided by two to create BUSCLKX2.

In this configuration, the OSC2 pin cannot output BUSCLKX4.So the OSC2EN bit in the port A pullup enable register will be clear to enable PTA4 I/O functions on the pin

| Reset Recovery Type | Actual Number of Cycles |

|---------------------|-------------------------|

| POR/LVI             | 4163 (4096 + 64 + 3)    |

| All others          | 67 (64 + 3)             |

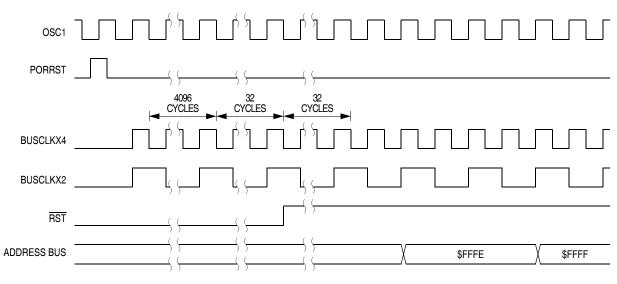

# 13.4.2.1 Power-On Reset

When power is first applied to the MCU, the power-on reset module (POR) generates a pulse to indicate that power on has occurred. The SIM counter counts out 4096 BUSCLKX4 cycles. Sixty-four BUSCLKX4 cycles later, the CPU and memories are released from reset to allow the reset vector sequence to occur.

At power on, the following events occur:

- A POR pulse is generated.

- The internal reset signal is asserted.

- The SIM enables the oscillator to drive BUSCLKX4.

- Internal clocks to the CPU and modules are held inactive for 4096 BUSCLKX4 cycles to allow stabilization of the oscillator.

- The POR bit of the SIM reset status register (SRSR) is set

## See Figure 13-6.

Figure 13-6. POR Recovery

MC68HC908QY/QT Family Data Sheet, Rev. 6

#### System Integration Module (SIM)

# 13.4.2.2 Computer Operating Properly (COP) Reset

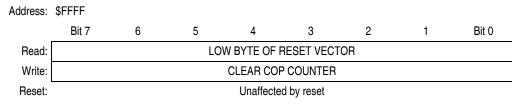

An input to the SIM is reserved for the COP reset signal. The overflow of the COP counter causes an internal reset and sets the COP bit in the SIM reset status register (SRSR). The SIM actively pulls down the RST pin for all internal reset sources.

To prevent a COP module time out, write any value to location \$FFFF. Writing to location \$FFFF clears the COP counter and stages 12–5 of the SIM counter. The SIM counter output, which occurs at least every 4080 BUSCLKX4 cycles, drives the COP counter. The COP should be serviced as soon as possible out of reset to guarantee the maximum amount of time before the first time out.

The COP module is disabled during a break interrupt with monitor mode when BDCOP bit is set in break auxiliary register (BRKAR).

# 13.4.2.3 Illegal Opcode Reset

The SIM decodes signals from the CPU to detect illegal instructions. An illegal instruction sets the ILOP bit in the SIM reset status register (SRSR) and causes a reset.

If the stop enable bit, STOP, in the mask option register is 0, the SIM treats the STOP instruction as an illegal opcode and causes an illegal opcode reset. The SIM actively pulls down the RST pin for all internal reset sources.

## 13.4.2.4 Illegal Address Reset

An opcode fetch from an unmapped address generates an illegal address reset. The SIM verifies that the CPU is fetching an opcode prior to asserting the ILAD bit in the SIM reset status register (SRSR) and resetting the MCU. A data fetch from an unmapped address does not generate a reset. The SIM actively pulls down the RST pin for all internal reset sources. See Figure 2-1. Memory Map for memory ranges.

# 13.4.2.5 Low-Voltage Inhibit (LVI) Reset

The LVI asserts its output to the SIM when the V<sub>DD</sub> voltage falls to the LVI trip voltage V<sub>TRIPF</sub>. The LVI bit in the SIM reset status register (SRSR) is set, and the external reset pin (RST) is held low while the SIM counter counts out 4096 BUSCLKX4 cycles after V<sub>DD</sub> rises above V<sub>TRIPR</sub>. Sixty-four BUSCLKX4 cycles later, the CPU and memories are released from reset to allow the reset vector sequence to occur. The SIM actively pulls down the (RST) pin for all internal reset sources.

# 13.5 SIM Counter

The SIM counter is used by the power-on reset module (POR) and in stop mode recovery to allow the oscillator time to stabilize before enabling the internal bus (IBUS) clocks. The SIM counter also serves as a prescaler for the computer operating properly module (COP). The SIM counter uses 12 stages for counting, followed by a 13th stage that triggers a reset of SIM counters and supplies the clock for the COP module. The SIM counter is clocked by the falling edge of BUSCLKX4.

# 13.5.1 SIM Counter During Power-On Reset

The power-on reset module (POR) detects power applied to the MCU. At power-on, the POR circuit asserts the signal PORRST. Once the SIM is initialized, it enables the oscillator to drive the bus clock state machine.

System Integration Module (SIM)

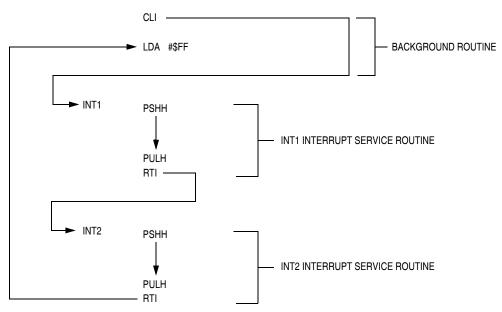

Figure 13-10. Interrupt Recognition Example

# 13.6.1.2 SWI Instruction

The SWI instruction is a non-maskable instruction that causes an interrupt regardless of the state of the interrupt mask (I bit) in the condition code register.

## NOTE

A software interrupt pushes PC onto the stack. A software interrupt does **not** push PC - 1, as a hardware interrupt does.

# 13.6.2 Interrupt Status Registers

The flags in the interrupt status registers identify maskable interrupt sources. Table 13-3 summarizes the interrupt sources and the interrupt status register flags that they set. The interrupt status registers can be useful for debugging.

| Priority | Source                            | Flag | Mask <sup>(1)</sup> | INT<br>Register<br>Flag | Vector<br>Address |

|----------|-----------------------------------|------|---------------------|-------------------------|-------------------|

| Highest  | Reset                             | _    | —                   |                         | \$FFFE-\$FFFF     |

| ▲        | SWI instruction                   | _    | —                   |                         | \$FFFC\$FFFD      |

|          | IRQ pin                           | IRQF | IMASK               | IF1                     | \$FFFA-\$FFFB     |

|          | Timer channel 0 interrupt         | CH0F | CH0IE               | IF3                     | \$FFF6-\$FFF7     |

|          | Timer channel 1 interrupt         | CH1F | CH1IE               | IF4                     | \$FFF4-\$FFF5     |

|          | Timer overflow interrupt          | TOF  | TOIE                | IF5                     | \$FFF2-\$FFF3     |

| ↓        | Keyboard interrupt                | KEYF | IMASKK              | IF14                    | \$FFE0-\$FFE1     |

| Lowest   | ADC conversion complete interrupt | COCO | AIEN                | IF15                    | \$FFDE-\$FFDF     |

Table 13-3. Interrupt Sources

1. The I bit in the condition code register is a global mask for all interrupt sources except the SWI instruction.

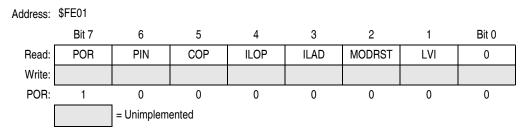

# 13.8.1 SIM Reset Status Register

The SRSR register contains flags that show the source of the last reset. The status register will automatically clear after reading SRSR. A power-on reset sets the POR bit and clears all other bits in the register. All other reset sources set the individual flag bits but do not clear the register. More than one reset source can be flagged at any time depending on the conditions at the time of the internal or external reset. For example, the POR and LVI bit can both be set if the power supply has a slow rise time.

## Figure 13-19. SIM Reset Status Register (SRSR)

### POR — Power-On Reset Bit

- 1 = Last reset caused by POR circuit

- 0 = Read of SRSR

### PIN — External Reset Bit

- 1 = Last reset caused by external reset pin ( $\overline{RST}$ )

- 0 = POR or read of SRSR

### COP — Computer Operating Properly Reset Bit

- 1 = Last reset caused by COP counter

- 0 = POR or read of SRSR

### ILOP — Illegal Opcode Reset Bit

- 1 = Last reset caused by an illegal opcode

- 0 = POR or read of SRSR

# ILAD — Illegal Address Reset Bit (illegal attempt to fetch an opcode from an unimplemented address)

- 1 = Last reset caused by an opcode fetch from an illegal address

- 0 = POR or read of SRSR

### MODRST — Monitor Mode Entry Module Reset Bit

- 1 = Last reset caused by monitor mode entry when vector locations \$FFFE and \$FFFF are \$FF after POR while  $\overline{IRQ} \neq V_{TST}$

- 0 = POR or read of SRSR

### LVI — Low Voltage Inhibit Reset Bit

- 1 = Last reset caused by LVI circuit

- 0 = POR or read of SRSR

# 14.9.3 TIM Counter Modulo Registers

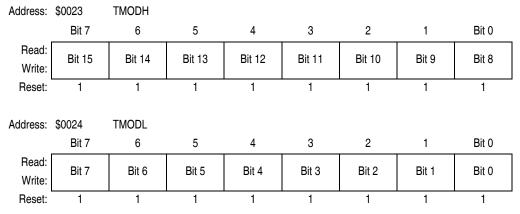

The read/write TIM modulo registers contain the modulo value for the TIM counter. When the TIM counter reaches the modulo value, the overflow flag (TOF) becomes set, and the TIM counter resumes counting from \$0000 at the next timer clock. Writing to the high byte (TMODH) inhibits the TOF bit and overflow interrupts until the low byte (TMODL) is written. Reset sets the TIM counter modulo registers.

Reset the TIM counter before writing to the TIM counter modulo registers.

# 14.9.4 TIM Channel Status and Control Registers

Each of the TIM channel status and control registers does the following:

- Flags input captures and output compares

- Enables input capture and output compare interrupts

- Selects input capture, output compare, or PWM operation

- Selects high, low, or toggling output on output compare

- Selects rising edge, falling edge, or any edge as the active input capture trigger

- Selects output toggling on TIM overflow

- Selects 0% and 100% PWM duty cycle

- Selects buffered or unbuffered output compare/PWM operation

# Chapter 15 Development Support

# **15.1 Introduction**

This section describes the break module, the monitor read-only memory (MON), and the monitor mode entry methods.

# 15.2 Break Module (BRK)

The break module can generate a break interrupt that stops normal program flow at a defined address to enter a background program.

Features include:

- Accessible input/output (I/O) registers during the break Interrupt

- Central processor unit (CPU) generated break interrupts

- Software-generated break interrupts

- Computer operating properly (COP) disabling during break interrupts

# 15.2.1 Functional Description

When the internal address bus matches the value written in the break address registers, the break module issues a breakpoint signal (BKPT) to the system integration module (SIM). The SIM then causes the CPU to load the instruction register with a software interrupt instruction (SWI). The program counter vectors to \$FFFC and \$FFFD (\$FEFC and \$FEFD in monitor mode).

The following events can cause a break interrupt to occur:

- A CPU generated address (the address in the program counter) matches the contents of the break address registers.

- Software writes a 1 to the BRKA bit in the break status and control register.

When a CPU generated address matches the contents of the break address registers, the break interrupt is generated. A return-from-interrupt instruction (RTI) in the break routine ends the break interrupt and returns the microcontroller unit (MCU) to normal operation.

Figure 15-2 shows the structure of the break module.

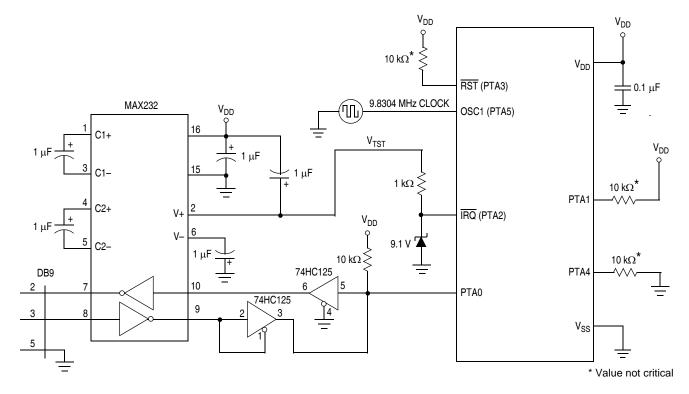

Figure 15-10. Monitor Mode Circuit (External Clock, with High Voltage)

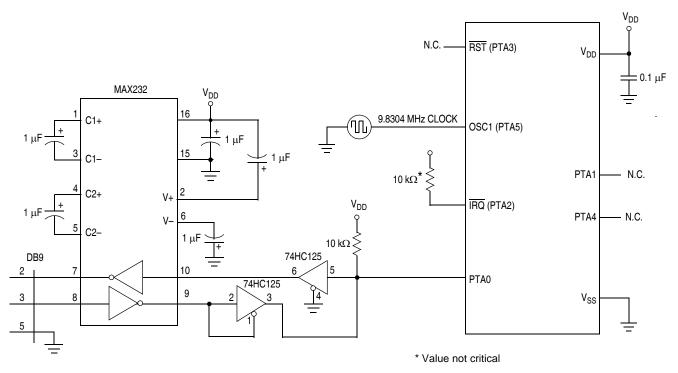

Figure 15-11. Monitor Mode Circuit (External Clock, No High Voltage)

MC68HC908QY/QT Family Data Sheet, Rev. 6

**Electrical Specifications**

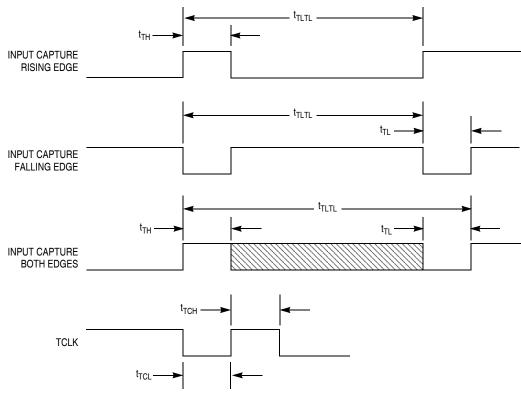

# **16.15 Timer Interface Module Characteristics**

| Characteristic                  | Symbol                              | Min                  | Max | Unit             |

|---------------------------------|-------------------------------------|----------------------|-----|------------------|

| Timer input capture pulse width | t <sub>TH,</sub> t <sub>TL</sub>    | 2                    | —   | t <sub>cyc</sub> |

| Timer input capture period      | t <sub>TLTL</sub>                   | Note <sup>(1)</sup>  | _   | t <sub>cyc</sub> |

| Timer input clock pulse width   | t <sub>TCL</sub> , t <sub>TCH</sub> | t <sub>cyc</sub> + 5 | _   | ns               |

1. The minimum period is the number of cycles it takes to execute the interrupt service routine plus 1  $t_{cyc}$ .

Figure 16-11. Timer Input Timing

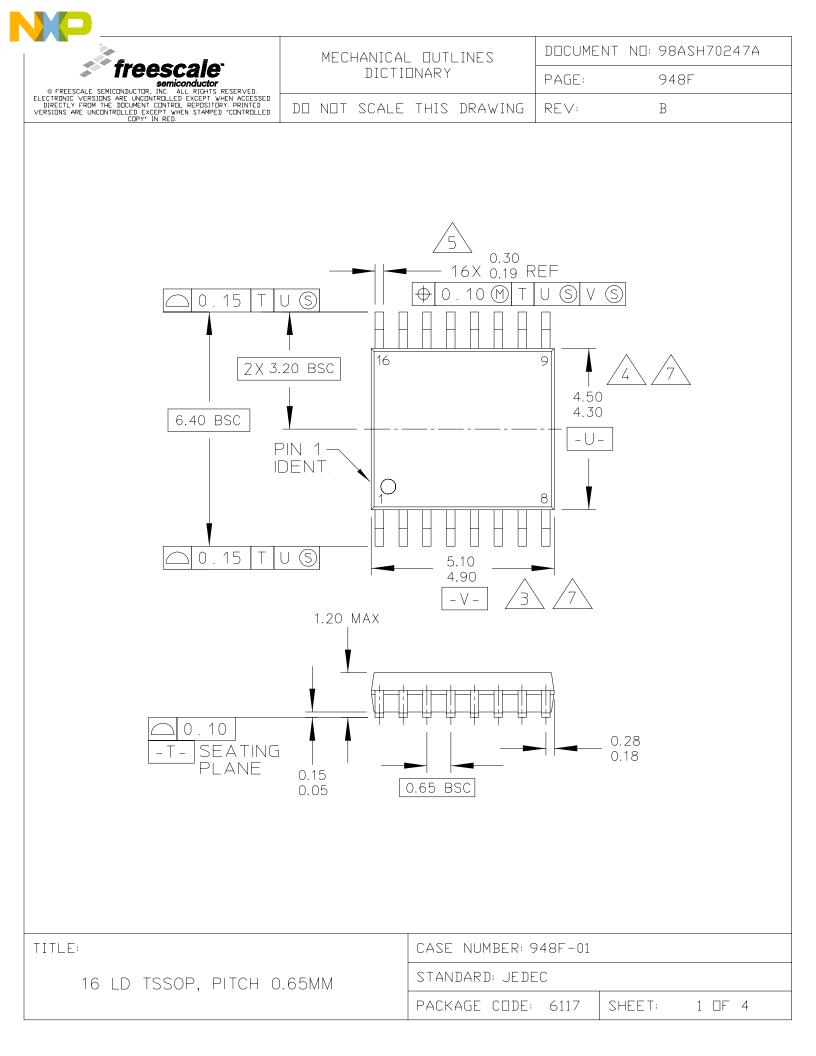

|                                                                                                                                                                                                   | MECHANICAL OUTLINES       | DOCUMENT | NO: 98ASB42431B |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|----------|-----------------|

| Freescale Semiconductor Freescale seMiconductor, INC. ALL RIGHTS RESERVED.                                                                                                                        | DICTIONARY                | PAGE:    | 648             |

| ELECTRONIC VERSIONS ARE UNCONTROLLED EXCEPT WHEN ACCESSED<br>DIRECTLY FROM THE DOCUMENT CONTROL REPOSITORY, PRINTED<br>VERSIONS ARE UNCONTROLLED EXCEPT WHEN STAWPED "CONTROLLED<br>COPY" IN RED. | DO NOT SCALE THIS DRAWING | REV:     | Т               |

# NOTES:

- 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

- 2. CONTROLLING DIMENSION: INCH.

- 3. DIMENSION TO CENTER OF LEADS WHEN FORMED PARALLEL.

- A DIMENSIONS DOES NOT INCLUDE MOLD FLASH.

- 5. ROUNDED CORNERS OPTIONAL.

- 6. 648-01 THRU -08 OBSOLETE, NEW STANDARD 648-09.

|                                | MILLIN                     | IETERS | INC   | HES   |      | MILLIMETERS |          | 11     | NCHES  |

|--------------------------------|----------------------------|--------|-------|-------|------|-------------|----------|--------|--------|

| DIM                            | MIN                        | MAX    | MIN   | MAX   | DIM  | MIN         | MAX      | MIN    | MAX    |

| А                              | 18.80                      | 19.55  | 0.740 | 0.770 |      |             |          |        |        |

| В                              | 6.35                       | 6.85   | 0.250 | 0,270 |      |             |          |        |        |

| С                              | 3.69                       | 4.44   | 0.145 | 0.175 |      |             |          |        |        |

| D                              | 0.39                       | 0.53   | 0.015 | 0.021 |      |             |          |        |        |

| F                              | 1.02                       | 1.77   | 0.040 | 0.070 |      |             |          |        |        |

| G                              | 2.54                       | BSC    | 0.100 | BSC   |      |             |          |        |        |

| Н                              | 1.27                       | BSC    | 0.050 | ) BSC |      |             |          |        |        |

| J                              | 0.21                       | 0.38   | 0.008 | 0.015 |      |             |          |        |        |

| K                              | 2.80                       | 3.30   | 0.110 | 0.130 |      |             |          |        |        |

| L                              | 7.50                       | 7.74   | 0.295 | 0.305 |      |             |          |        |        |

| М                              | 0.                         | 10°    | 0.    | 10°   |      |             |          |        |        |

| S                              | 0.51                       | 1.01   | 0.020 | 0.040 |      |             |          |        |        |

| TITLE                          | TITLE: CASE NUMBER: 648–08 |        |       |       |      |             |          |        |        |

| 16 LD PDIP STANDARD: NON-JEDEC |                            |        |       |       |      |             |          |        |        |

|                                |                            |        |       |       | PACK | AGE CODE:   | : 0006 S | SHEET: | 2 OF 4 |

#### How to Reach Us:

Home Page: www.freescale.com

E-mail: support@freescale.com

#### USA/Europe or Locations Not Listed:

Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 +1-800-521-6274 or +1-480-768-2130 support@freescale.com

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street Tai Po Industrial Estate Tai Po, N.T., Hong Kong +800 2666 8080 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 1-800-441-2447 or 303-675-2140 Fax: 303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc. 2005–2010. All rights reserved.

MC68HC908QY4 Rev. 6, 03/2010