Welcome to **E-XFL.COM**

## What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                        |  |

|----------------------------|------------------------------------------------------------------------|--|

| Product Status             | Obsolete                                                               |  |

| Core Processor             | HC08                                                                   |  |

| Core Size                  | 8-Bit                                                                  |  |

| Speed                      | 8MHz                                                                   |  |

| Connectivity               | -                                                                      |  |

| Peripherals                | LVD, POR, PWM                                                          |  |

| Number of I/O              | 5                                                                      |  |

| Program Memory Size        | 1.5KB (1.5K x 8)                                                       |  |

| Program Memory Type        | FLASH                                                                  |  |

| EEPROM Size                | -                                                                      |  |

| RAM Size                   | 128 x 8                                                                |  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                            |  |

| Data Converters            | -                                                                      |  |

| Oscillator Type            | Internal                                                               |  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                     |  |

| Mounting Type              | kage / Case 8-SOIC (0.209", 5.30mm Width)                              |  |

| Package / Case             |                                                                        |  |

| Supplier Device Package    |                                                                        |  |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mchc908qt1mdwe |  |

6.7.2

6.8

#### **Table of Contents** 3.6 3.7 3.7.1 3.7.2 3.7.3 Chapter 4 **Auto Wakeup Module (AWU)** 4.1 4.2 4.3 4.4 4.5 4.6 4.6.1 Keyboard Status and Control Register......51 4.6.2 4.6.3 Keyboard Interrupt Enable Register..... 52 **Chapter 5** Configuration Register (CONFIG) 5.1 5.2 Chapter 6 **Computer Operating Properly (COP)** 6.1 6.2 6.3 6.3.1 6.3.2 6.3.3 6.3.4 6.3.5 6.3.6 6.3.7 6.4 6.5 6.6 6.7 6.7.1

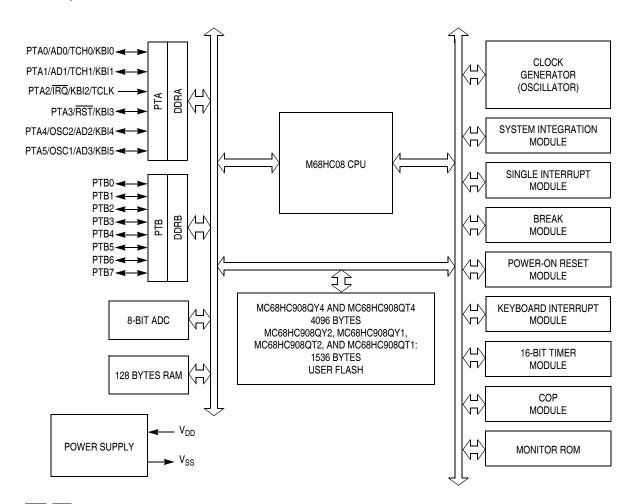

## **General Description**

RST, IRQ: Pins have internal (about 30K Ohms) pull up

PTA[0:5]: High current sink and source capability

PTA[0:5]: Pins have programmable keyboard interrupt and pull up

PTB[0:7]: Not available on 8-pin devices – MC68HC908QT1, MC68HC908QT2, and MC68HC908QT4 (see note in 12.1 Introduction)

ADC: Not available on the MC68HC908QY1 and MC68HC908QT1

Figure 1-1. Block Diagram

MC68HC908QY/QT Family Data Sheet, Rev. 6

**General Description**

# 4.6 Input/Output Registers

The AWU shares registers with the keyboard interrupt (KBI) module and the port A I/O module. The following I/O registers control and monitor operation of the AWU:

- Port A data register (PTA)

- Keyboard interrupt status and control register (KBSCR)

- Keyboard interrupt enable register (KBIER)

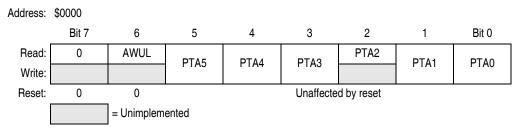

# 4.6.1 Port A I/O Register

The port A data register (PTA) contains a data latch for the state of the AWU interrupt request, in addition to the data latches for port A.

Figure 4-2. Port A Data Register (PTA)

## AWUL — Auto Wakeup Latch

This is a read-only bit which has the value of the auto wakeup interrupt request latch. The wakeup request signal is generated internally. There is no PTA6 port or any of the associated bits such as PTA6 data direction or pullup bits.

- 1 = Auto wakeup interrupt request is pending

- 0 = Auto wakeup interrupt request is not pending

## NOTE

PTA5–PTA0 bits are not used in conjuction with the auto wakeup feature. To see a description of these bits, see 12.2.1 Port A Data Register.

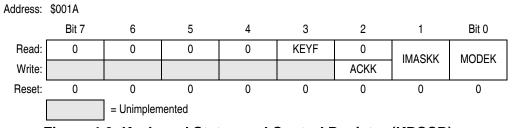

# 4.6.2 Keyboard Status and Control Register

The keyboard status and control register (KBSCR):

- Flags keyboard/auto wakeup interrupt requests

- Acknowledges keyboard/auto wakeup interrupt requests

- Masks keyboard/auto wakeup interrupt requests

Figure 4-3. Keyboard Status and Control Register (KBSCR)

MC68HC908QY/QT Family Data Sheet, Rev. 6

# **Chapter 5 Configuration Register (CONFIG)**

## 5.1 Introduction

This section describes the configuration registers (CONFIG1 and CONFIG2). The configuration registers enable or disable the following options:

- Stop mode recovery time (32 x BUSCLKX4 cycles or 4096 x BUSCLKX4 cycles)

- STOP instruction

- Computer operating properly module (COP)

- COP reset period (COPRS): 8176 × BUSCLKX4 or 262,128 × BUSCLKX4

- Low-voltage inhibit (LVI) enable and trip voltage selection

- OSC option selection

- IRQ pin

- RST pin

- Auto wakeup timeout period

# 5.2 Functional Description

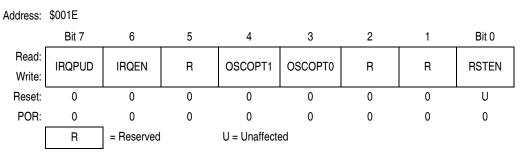

The configuration registers are used in the initialization of various options. The configuration registers can be written once after each reset. Most of the configuration register bits are cleared during reset. Since the various options affect the operation of the microcontroller unit (MCU) it is recommended that this register be written immediately after reset. The configuration registers are located at \$001E and \$001F, and may be read at anytime.

## **NOTE**

The CONFIG registers are one-time writable by the user after each reset. Upon a reset, the CONFIG registers default to predetermined settings as shown in Figure 5-1 and Figure 5-2.

Figure 5-1. Configuration Register 2 (CONFIG2)

# **Chapter 6 Computer Operating Properly (COP)**

# 6.1 Introduction

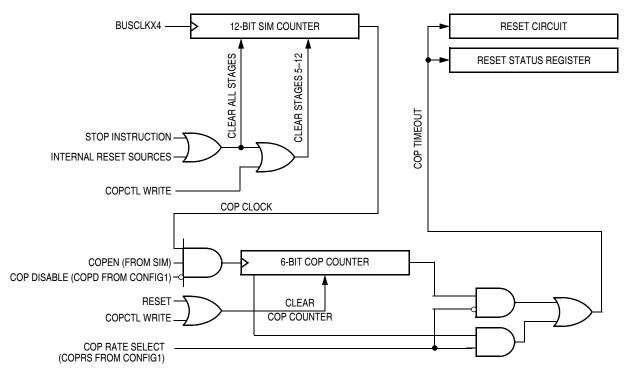

The computer operating properly (COP) module contains a free-running counter that generates a reset if allowed to overflow. The COP module helps software recover from runaway code. Prevent a COP reset by clearing the COP counter periodically. The COP module can be disabled through the COPD bit in the configuration 1 (CONFIG1) register.

# **6.2 Functional Description**

Figure 6-1. COP Block Diagram

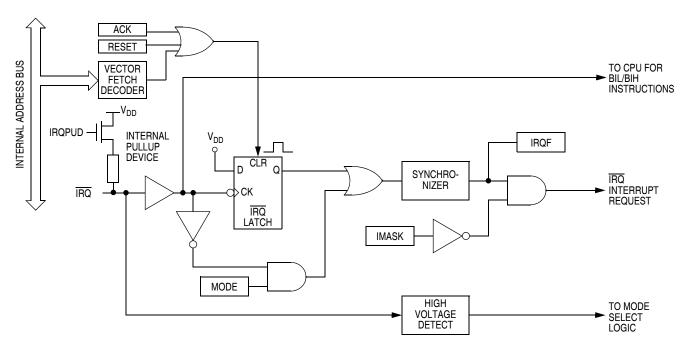

Figure 8-2. IRQ Module Block Diagram

#### 8.3.1 MODE = 1

If the MODE bit is set, the  $\overline{IRQ}$  pin is both falling edge sensitive and low level sensitive. With MODE set, both of the following actions must occur to clear the  $\overline{IRQ}$  interrupt request:

- Return of the IRQ pin to a high level. As long as the IRQ pin is low, the IRQ request remains active.

- IRQ vector fetch or software clear. An IRQ vector fetch generates an interrupt acknowledge signal to clear the IRQ latch. Software generates the interrupt acknowledge signal by writing a 1 to ACK in INTSCR. The ACK bit is useful in applications that poll the IRQ pin and require software to clear the IRQ latch. Writing to ACK prior to leaving an interrupt service routine can also prevent spurious interrupts due to noise. Setting ACK does not affect subsequent transitions on the IRQ pin. A falling edge that occurs after writing to ACK latches another interrupt request. If the IRQ mask bit, IMASK, is clear, the CPU loads the program counter with the IRQ vector address.

The IRQ vector fetch or software clear and the return of the  $\overline{\text{IRQ}}$  pin to a high level may occur in any order. The interrupt request remains pending as long as the  $\overline{\text{IRQ}}$  pin is low. A reset will clear the IRQ latch and the MODE control bit, thereby clearing the interrupt even if the pin stays low.

Use the BIH or BIL instruction to read the logic level on the IRQ pin.

#### 8.3.2 MODE = 0

If the MODE bit is clear, the  $\overline{IRQ}$  pin is falling edge sensitive only. With MODE clear, an IRQ vector fetch or software clear immediately clears the IRQ latch.

The IRQF bit in INTSCR can be read to check for pending interrupts. The IRQF bit is not affected by IMASK, which makes it useful in applications where polling is preferred.

#### NOTE

When using the level-sensitive interrupt trigger, avoid false IRQ interrupts by masking interrupt requests in the interrupt routine.

MC68HC908QY/QT Family Data Sheet, Rev. 6

External Interrupt (IRQ)

MC68HC908QY/QT Family Data Sheet, Rev. 6

Low-Voltage Inhibit (LVI)

# **Chapter 11 Oscillator Module (OSC)**

## 11.1 Introduction

The oscillator module is used to provide a stable clock source for the microcontroller system and bus. The oscillator module generates two output clocks, BUSCLKX2 and BUSCLKX4. The BUSCLKX4 clock is used by the system integration module (SIM) and the computer operating properly module (COP). The BUSCLKX2 clock is divided by two in the SIM to be used as the bus clock for the microcontroller. Therefore the bus frequency will be one fourth of the BUSCLKX4 frequency.

## 11.2 Features

The oscillator has these four clock source options available:

- 1. Internal oscillator: An internally generated, fixed frequency clock, trimmable to ±5%. This is the default option out of reset.

- 2. External oscillator: An external clock that can be driven directly into OSC1.

- 3. External RC: A built-in oscillator module (RC oscillator) that requires an external R connection only. The capacitor is internal to the chip.

- 4. External crystal: A built-in oscillator module (XTAL oscillator) that requires an external crystal or ceramic-resonator.

# 11.3 Functional Description

The oscillator contains these major subsystems:

- Internal oscillator circuit

- Internal or external clock switch control

- External clock circuit

- External crystal circuit

- External RC clock circuit

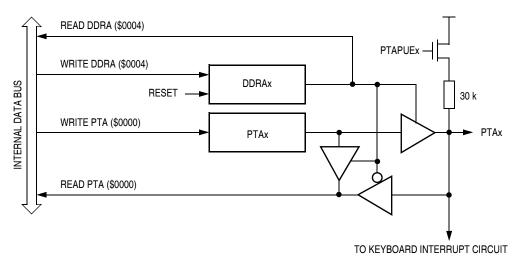

Figure 12-3 shows the port A I/O logic.

Figure 12-3. Port A I/O Circuit

#### NOTE

Figure 12-3 does not apply to PTA2

When DDRAx is a 1, reading address \$0000 reads the PTAx data latch. When DDRAx is a 0, reading address \$0000 reads the voltage level on the pin. The data latch can always be written, regardless of the state of its data direction bit.

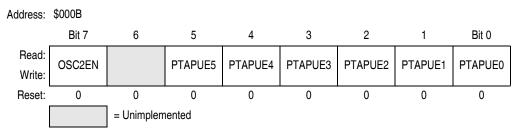

# 12.2.3 Port A Input Pullup Enable Register

The port A input pullup enable register (PTAPUE) contains a software configurable pullup device for each if the six port A pins. Each bit is individually configurable and requires the corresponding data direction register, DDRAx, to be configured as input. Each pullup device is automatically and dynamically disabled when its corresponding DDRAx bit is configured as output.

Figure 12-4. Port A Input Pullup Enable Register (PTAPUE)

## OSC2EN — Enable PTA4 on OSC2 Pin

This read/write bit configures the OSC2 pin function when internal oscillator or RC oscillator option is selected. This bit has no effect for the XTAL or external oscillator options.

- 1 = OSC2 pin outputs the internal or RC oscillator clock (BUSCLKX4)

- 0 = OSC2 pin configured for PTA4 I/O, having all the interrupt and pullup functions

MC68HC908QY/QT Family Data Sheet, Rev. 6

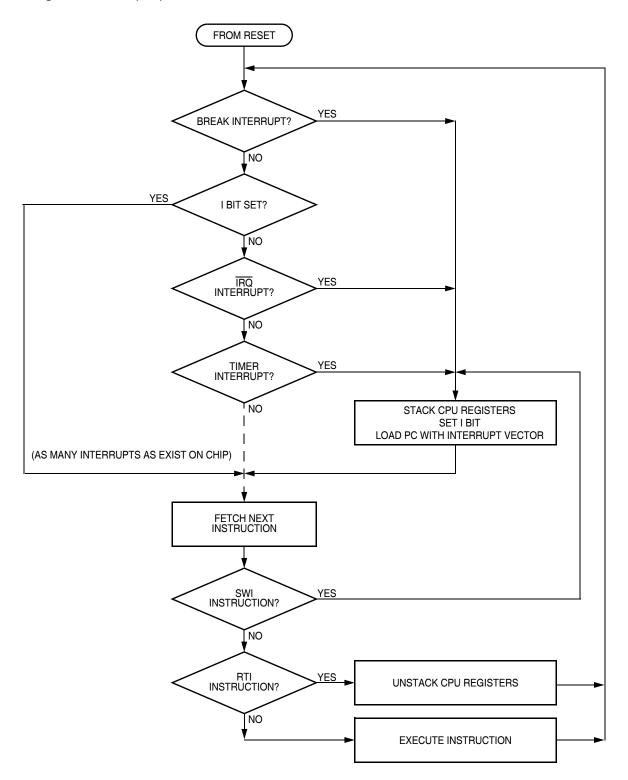

# **Chapter 13 System Integration Module (SIM)**

# 13.1 Introduction

This section describes the system integration module (SIM), which supports up to 24 external and/or internal interrupts. Together with the central processor unit (CPU), the SIM controls all microcontroller unit (MCU) activities. A block diagram of the SIM is shown in Figure 13-1. The SIM is a system state controller that coordinates CPU and exception timing.

# The SIM is responsible for:

- Bus clock generation and control for CPU and peripherals

- Stop/wait/reset/break entry and recovery

- Internal clock control

- Master reset control, including power-on reset (POR) and computer operating properly (COP) timeout

- Interrupt control:

- Acknowledge timing

- Arbitration control timing

- Vector address generation

- CPU enable/disable timing

**Table 13-1. Signal Name Conventions**

| Signal Name | Description                                                                                                                                           |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| BUSCLKX4    | Buffered clock from the internal, RC or XTAL oscillator circuit.                                                                                      |

| BUSCLKX2    | The BUSCLKX4 frequency divided by two. This signal is again divided by two in the SIM to generate the internal bus clocks (bus clock = BUSCLKX4 ÷ 4). |

| Address bus | Internal address bus                                                                                                                                  |

| Data bus    | Internal data bus                                                                                                                                     |

| PORRST      | Signal from the power-on reset module to the SIM                                                                                                      |

| IRST        | Internal reset signal                                                                                                                                 |

| R/W         | Read/write signal                                                                                                                                     |

Figure 13-5. Sources of Internal Reset

**Table 13-2. Reset Recovery Timing**

| Reset Recovery Type | Actual Number of Cycles |

|---------------------|-------------------------|

| POR/LVI             | 4163 (4096 + 64 + 3)    |

| All others          | 67 (64 + 3)             |

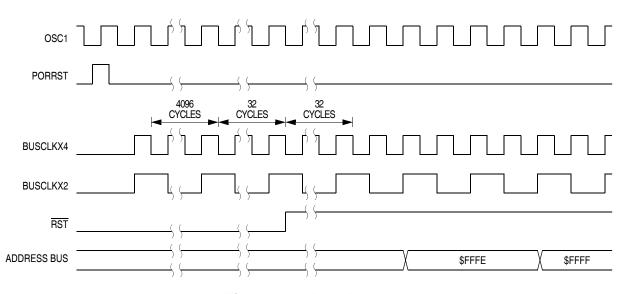

#### 13.4.2.1 Power-On Reset

When power is first applied to the MCU, the power-on reset module (POR) generates a pulse to indicate that power on has occurred. The SIM counter counts out 4096 BUSCLKX4 cycles. Sixty-four BUSCLKX4 cycles later, the CPU and memories are released from reset to allow the reset vector sequence to occur.

At power on, the following events occur:

- A POR pulse is generated.

- The internal reset signal is asserted.

- The SIM enables the oscillator to drive BUSCLKX4.

- Internal clocks to the CPU and modules are held inactive for 4096 BUSCLKX4 cycles to allow stabilization of the oscillator.

- The POR bit of the SIM reset status register (SRSR) is set

See Figure 13-6.

Figure 13-6. POR Recovery

MC68HC908QY/QT Family Data Sheet, Rev. 6

## **System Integration Module (SIM)**

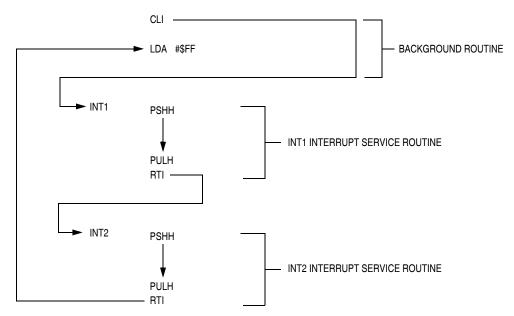

Figure 13-7. Interrupt Processing

## **System Integration Module (SIM)**

Figure 13-10. Interrupt Recognition Example

## 13.6.1.2 SWI Instruction

The SWI instruction is a non-maskable instruction that causes an interrupt regardless of the state of the interrupt mask (I bit) in the condition code register.

#### NOTE

A software interrupt pushes PC onto the stack. A software interrupt does **not** push PC – 1, as a hardware interrupt does.

# 13.6.2 Interrupt Status Registers

The flags in the interrupt status registers identify maskable interrupt sources. Table 13-3 summarizes the interrupt sources and the interrupt status register flags that they set. The interrupt status registers can be useful for debugging.

| Priority | Source                            | Flag | Mask <sup>(1)</sup> | INT<br>Register<br>Flag | Vector<br>Address |

|----------|-----------------------------------|------|---------------------|-------------------------|-------------------|

| Highest  | Reset                             | _    | _                   | _                       | \$FFFE-\$FFFF     |

| <b>A</b> | SWI instruction                   | _    | _                   | _                       | \$FFFC-\$FFFD     |

|          | IRQ pin                           | IRQF | IMASK               | IF1                     | \$FFFA-\$FFFB     |

|          | Timer channel 0 interrupt         | CH0F | CH0IE               | IF3                     | \$FFF6-\$FFF7     |

|          | Timer channel 1 interrupt         | CH1F | CH1IE               | IF4                     | \$FFF4-\$FFF5     |

|          | Timer overflow interrupt          | TOF  | TOIE                | IF5                     | \$FFF2-\$FFF3     |

|          | Keyboard interrupt                | KEYF | IMASKK              | IF14                    | \$FFE0-\$FFE1     |

| Lowest   | ADC conversion complete interrupt | coco | AIEN                | IF15                    | \$FFDE-\$FFDF     |

**Table 13-3. Interrupt Sources**

MC68HC908QY/QT Family Data Sheet, Rev. 6

The I bit in the condition code register is a global mask for all interrupt sources except the SWI instruction.

**System Integration Module (SIM)**

#### 13.6.3 Reset

All reset sources always have equal and highest priority and cannot be arbitrated.

# 13.6.4 Break Interrupts

The break module can stop normal program flow at a software programmable break point by asserting its break interrupt output. (See Chapter 15 Development Support.) The SIM puts the CPU into the break state by forcing it to the SWI vector location. Refer to the break interrupt subsection of each module to see how each module is affected by the break state.

# 13.6.5 Status Flag Protection in Break Mode

The SIM controls whether status flags contained in other modules can be cleared during break mode. The user can select whether flags are protected from being cleared by properly initializing the break clear flag enable bit (BCFE) in the break flag control register (BFCR).

Protecting flags in break mode ensures that set flags will not be cleared while in break mode. This protection allows registers to be freely read and written during break mode without losing status flag information.

Setting the BCFE bit enables the clearing mechanisms. Once cleared in break mode, a flag remains cleared even when break mode is exited. Status flags with a two-step clearing mechanism — for example, a read of one register followed by the read or write of another — are protected, even when the first step is accomplished prior to entering break mode. Upon leaving break mode, execution of the second step will clear the flag as normal.

## 13.7 Low-Power Modes

Executing the WAIT or STOP instruction puts the MCU in a low power- consumption mode for standby situations. The SIM holds the CPU in a non-clocked state. The operation of each of these modes is described below. Both STOP and WAIT clear the interrupt mask (I) in the condition code register, allowing interrupts to occur.

#### 13.7.1 Wait Mode

In wait mode, the CPU clocks are inactive while the peripheral clocks continue to run. Figure 13-14 shows the timing for wait mode entry.

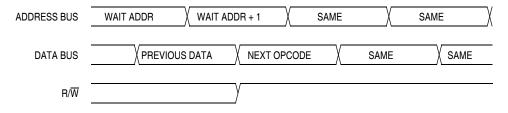

NOTE: Previous data can be operand data or the WAIT opcode, depending on the last instruction.

Figure 13-14. Wait Mode Entry Timing

MC68HC908QY/QT Family Data Sheet, Rev. 6

# 15.3.1 Functional Description

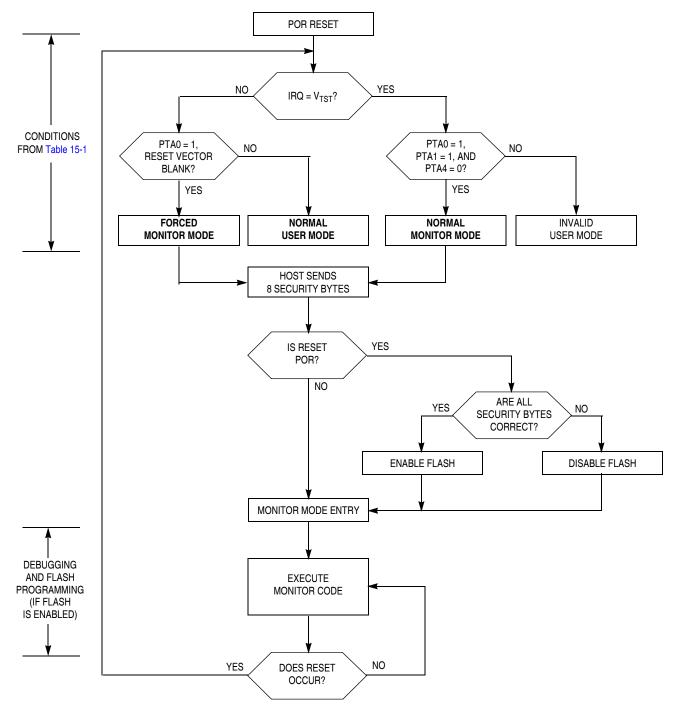

Figure 15-9 shows a simplified diagram of monitor mode entry.

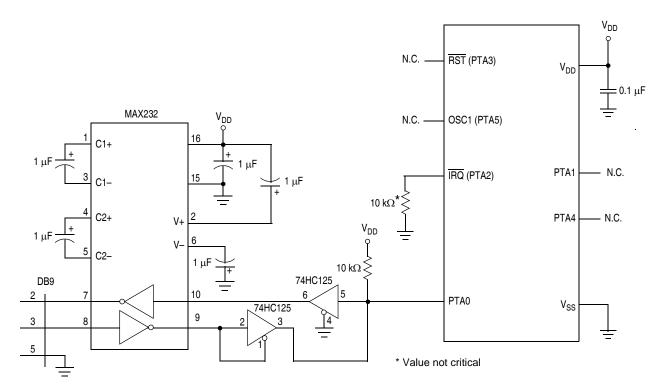

The monitor module receives and executes commands from a host computer. Figure 15-10, Figure 15-11, and Figure 15-12 show example circuits used to enter monitor mode and communicate with a host computer via a standard RS-232 interface.

Figure 15-9. Simplified Monitor Mode Entry Flowchart

MC68HC908QY/QT Family Data Sheet, Rev. 6

Figure 15-12. Monitor Mode Circuit (Internal Clock, No High Voltage)

Simple monitor commands can access any memory address. In monitor mode, the MCU can execute code downloaded into RAM by a host computer while most MCU pins retain normal operating mode functions. All communication between the host computer and the MCU is through the PTA0 pin. A level-shifting and multiplexing interface is required between PTA0 and the host computer. PTA0 is used in a wired-OR configuration and requires a pullup resistor.

The monitor code has been updated from previous versions of the monitor code to allow enabling the internal oscillator to generate the internal clock. This addition, which is enabled when  $\overline{IRQ}$  is held low out of reset, is intended to support serial communication/programming at 9600 baud in monitor mode by using the internal oscillator, and the internal oscillator user trim value OSCTRIM (FLASH location \$FFC0, if programmed) to generate the desired internal frequency (3.2 MHz). Since this feature is enabled only when  $\overline{IRQ}$  is held low out of reset, it cannot be used when the reset vector is programmed (i.e., the value is not \$FFFF) because entry into monitor mode in this case requires  $V_{TST}$  on  $\overline{IRQ}$ . The  $\overline{IRQ}$  pin must remain low during this monitor session in order to maintain communication.

Table 15-1 shows the pin conditions for entering monitor mode. As specified in the table, monitor mode may be entered after a power-on reset (POR) and will allow communication at 9600 baud provided one of the following sets of conditions is met:

- If \$FFFE and \$FFFF do not contain \$FF (programmed state):

- The external clock is 9.8304 MHz

- $\overline{IRQ} = V_{TST}$

- If \$FFFE and \$FFFF contain \$FF (erased state):

- The external clock is 9.8304 MHz

- $-\overline{IRQ} = V_{DD}$  (this can be implemented through the internal  $\overline{IRQ}$  pullup)

- If \$FFFE and \$FFFF contain \$FF (erased state):

- $\overline{IRQ} = V_{SS}$  (internal oscillator is selected, no external clock required)

MC68HC908QY/QT Family Data Sheet, Rev. 6

# **16.16 Memory Characteristics**

| Characteristic                                | Symbol                           | Min        | Тур    | Max        | Unit   |

|-----------------------------------------------|----------------------------------|------------|--------|------------|--------|

| RAM data retention voltage                    | V <sub>RDR</sub>                 | 1.3        | _      | _          | V      |

| FLASH program bus clock frequency             | _                                | 1          | _      |            | MHz    |

| FLASH read bus clock frequency                | f <sub>Read</sub> <sup>(1)</sup> | 0          | _      | 8 M        | Hz     |

| FLASH page erase time <1 k cycles >1 k cycles | t <sub>Erase</sub>               | 0.9<br>3.6 | 1<br>4 | 1.1<br>5.5 | ms     |

| FLASH mass erase time                         | t <sub>MErase</sub>              | 4          | _      | _          | ms     |

| FLASH PGM/ERASE to HVEN setup time            | t <sub>NVS</sub>                 | 10         | _      | _          | μS     |

| FLASH high-voltage hold time                  | t <sub>NVH</sub>                 | 5          | _      | _          | μS     |

| FLASH high-voltage hold time (mass erase)     | t <sub>NVHL</sub>                | 100        | _      | _          | μS     |

| FLASH program hold time                       | t <sub>PGS</sub>                 | 5          | _      | _          | μS     |

| FLASH program time                            | t <sub>PROG</sub>                | 30         | _      | 40         | μS     |

| FLASH return to read time                     | t <sub>RCV</sub> <sup>(2)</sup>  | 1          | _      | _          | μS     |

| FLASH cumulative program HV period            | t <sub>HV</sub> <sup>(3)</sup>   | _          | _      | 4          | ms     |

| FLASH endurance <sup>(4)</sup>                | _                                | 10 k       | 100 k  | _          | Cycles |

| FLASH data retention time <sup>(5)</sup>      |                                  | 15         | 100    | _          | Years  |

- 1.  $f_{\mbox{\scriptsize Read}}$  is defined as the frequency range for which the FLASH memory can be read.

- 2. t<sub>RCV</sub> is defined as the time it needs before the FLASH can be read after turning off the high voltage charge pump, by clearing HVEN to 0.

- 3.  $t_{HV}$  is defined as the cumulative high voltage programming time to the same row before next erase.  $t_{HV}$  must satisfy this condition:  $t_{NVS} + t_{NVH} + t_{PGS} + (t_{PROG} \times 32) \le t_{HV}$  maximum.

- 4. Typical endurance was evaluated for this product family. For additional information on how Freescale defines *Typical Endurance*, please refer to Engineering Bulletin EB619.

- 5. Typical data retention values are based on intrinsic capability of the technology measured at high temperature and de-rated to 25•C using the Arrhenius equation. For additional information on how Freescale defines *Typical Data Retention*, please refer to Engineering Bulletin EB618.

© FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED.

ELECTRONIC VERSIONS ARE UNCONTROLLED EXCEPT WHEN ACCESSED

DIRECTLY FROM THE DISCUMENT CONTROL REPOSITIORY, PRINTED

VERSIONS ARE UNCONTROLLED EXCEPT WHEN STAMPED "CONTROLLED

COPY" IN FED.

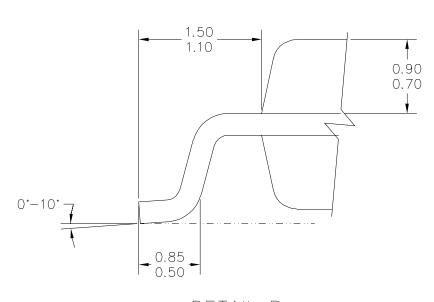

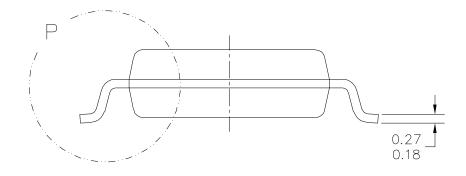

| MECHANICAL | DUTLINES |

|------------|----------|

| חורדוחו    | JARY     |

DO NOT SCALE THIS DRAWING

| DOCUMENT | N□: | 98ASH70107A |  |

|----------|-----|-------------|--|

| PAGE:    |     | 968         |  |

|          |     |             |  |

REV:

| TITLE:     | CASE NUMBER: 968-02              |  |  |  |

|------------|----------------------------------|--|--|--|

| 8 LEAD MFP | STANDARD: EIAJ                   |  |  |  |

|            | PACKAGE CODE: 6003 SHEET: 2 OF 4 |  |  |  |