#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                      |

|----------------------------|-------------------------------------------------------------|

| Core Processor             | -                                                           |

| Core Size                  | - ·                                                         |

| Speed                      | -                                                           |

| Connectivity               | - ·                                                         |

| Peripherals                | -                                                           |

| Number of I/O              | -                                                           |

| Program Memory Size        | - ·                                                         |

| Program Memory Type        | -                                                           |

| EEPROM Size                | -                                                           |

| RAM Size                   | - ·                                                         |

| Voltage - Supply (Vcc/Vdd) | -                                                           |

| Data Converters            | - ·                                                         |

| Oscillator Type            | -                                                           |

| Operating Temperature      | -                                                           |

| Mounting Type              |                                                             |

| Package / Case             | -                                                           |

| Supplier Device Package    |                                                             |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mchc908qt2cdwe |

|                            |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Revision History (Sheet 2 of 3)**

\_\_\_\_\_

| Date             | Revision<br>Level                                         | Description                                                                                                                                                                               | Page<br>Number(s)                                                                                                                                                                                                    |    |

|------------------|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|                  |                                                           | Reformatted to meet latest M68HC08 documentation standards                                                                                                                                | N/A                                                                                                                                                                                                                  |    |

|                  |                                                           | Figure 1-1. Block Diagram — Diagram redrawn to include keyboard interrupt module and TCLK pin designator.                                                                                 | 20                                                                                                                                                                                                                   |    |

|                  |                                                           | Figure 1-2. MCU Pin Assignments — Added TCLK pin designator.                                                                                                                              | 21                                                                                                                                                                                                                   |    |

|                  |                                                           | Table 1-2. Pin Functions — Added TCLK pin description.                                                                                                                                    | 22                                                                                                                                                                                                                   |    |

|                  |                                                           | Table 1-3. Function Priority in Shared Pins — Revised table for clarity and to add TCLK.                                                                                                  | 23                                                                                                                                                                                                                   |    |

| August,          |                                                           | Figure 2-1. Memory Map — Corrected names for the IRQ status and control register (INTSCR) bits 3–0.                                                                                       | 26                                                                                                                                                                                                                   |    |

| 2003             | 1.0                                                       | 3.7.3 ADC Input Clock Register — Clarified bit description for the ADC clock prescaler bits.                                                                                              | 47                                                                                                                                                                                                                   |    |

|                  |                                                           | 4.3 Functional Description — Updated periodic wakeup request values.                                                                                                                      | 51                                                                                                                                                                                                                   |    |

|                  |                                                           | Figure 6-1. COP Block Diagram — Reworked for clarity                                                                                                                                      | 59                                                                                                                                                                                                                   |    |

|                  |                                                           | Chapter 8 External Interrupt (IRQ) — Corrected bit names for MODE, IRQF, ACK, and IMASK                                                                                                   | 77–79                                                                                                                                                                                                                |    |

|                  |                                                           | Chapter 14 Timer Interface Module (TIM) — Added TCLK function.                                                                                                                            | 131–139                                                                                                                                                                                                              |    |

|                  | 15.3 Monitor Module (MON) — Updated with additional data. | 147                                                                                                                                                                                       |                                                                                                                                                                                                                      |    |

|                  |                                                           | Chapter 16 Electrical Specifications — Updated with additional data.                                                                                                                      | 169–173                                                                                                                                                                                                              |    |

|                  |                                                           |                                                                                                                                                                                           | Figure 2-2. Control, Status, and Data Registers — Deleted unimplemented areas from \$FFB0–\$FFBD and \$FFC2–\$FFCF as they are actually available. Also corrected \$FFBF designation from unimplemented to reserved. | 27 |

|                  |                                                           | Figure 6-1. COP Block Diagram — Reworked for clarity                                                                                                                                      | 59                                                                                                                                                                                                                   |    |

|                  |                                                           | 6.3.2 STOP Instruction — Added subsection                                                                                                                                                 | 60                                                                                                                                                                                                                   |    |

|                  |                                                           | 13.4.2 Active Resets from Internal Sources — Reworked notes for clarity.                                                                                                                  | 111                                                                                                                                                                                                                  |    |

| October,<br>2003 | 2.0                                                       | Table 13-2. Reset Recovery Timing — Replaced previous table with new information.                                                                                                         | 112                                                                                                                                                                                                                  |    |

|                  |                                                           | Chapter 14 Timer Interface Module (TIM) — Updated with additional data.                                                                                                                   | 131                                                                                                                                                                                                                  |    |

|                  |                                                           | Figure 15-3. Break I/O Register Summary — Corrected bit designators for the BRKAR register                                                                                                | 143                                                                                                                                                                                                                  |    |

|                  |                                                           | 15.3 Monitor Module (MON) — Clarified seventh bullet.                                                                                                                                     | 147                                                                                                                                                                                                                  |    |

|                  |                                                           | Table 17-1. MC Order Numbers — Corrected temperature and package designators.                                                                                                             | 175                                                                                                                                                                                                                  |    |

| January,         | 3.0                                                       | Figure 2-2. Control, Status, and Data Registers — Corrected reset state for the FLASH Block Protect Register at address location \$FFBE and the Internal Oscillator Trim Value at \$FFC0. | 32                                                                                                                                                                                                                   |    |

| 2004             |                                                           | Figure 2-5. FLASH Block Protect Register (FLBPR) — Restated reset state for clarity.                                                                                                      | 38                                                                                                                                                                                                                   |    |

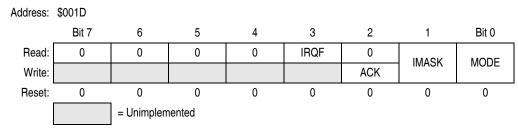

#### **General Description**

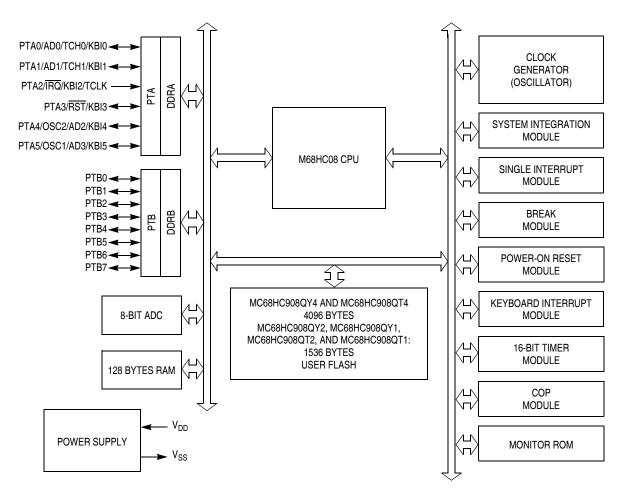

RST, IRQ: Pins have internal (about 30K Ohms) pull up

PTA[0:5]: High current sink and source capability

PTA[0:5]: Pins have programmable keyboard interrupt and pull up

PTB[0:7]: Not available on 8-pin devices – MC68HC908QT1, MC68HC908QT2, and MC68HC908QT4 (see note in 12.1 Introduction)

ADC: Not available on the MC68HC908QY1 and MC68HC908QT1

### Figure 1-1. Block Diagram

## **1.6 Pin Function Priority**

Table 1-3 is meant to resolve the priority if multiple functions are enabled on a single pin.

NOTE

Upon reset all pins come up as input ports regardless of the priority table.

| Pin Name | Highest-to-Lowest Priority Sequence                                                             |

|----------|-------------------------------------------------------------------------------------------------|

| PTA0     | $AD0 \rightarrow TCH0 \rightarrow KBI0 \rightarrow PTA0$                                        |

| PTA1     | $AD1 \rightarrow TCH1 \rightarrow KBI1 \rightarrow PTA1$                                        |

| PTA2     | $\overline{\text{IRQ}} \rightarrow \text{KBI2} \rightarrow \text{TCLK} \rightarrow \text{PTA2}$ |

| PTA3     | $\overline{\text{RST}} \rightarrow \text{KBI3} \rightarrow \text{PTA3}$                         |

| PTA4     | $OSC2 \rightarrow AD2 \rightarrow KBI4 \rightarrow PTA4$                                        |

| PTA5     | $OSC1 \rightarrow AD3 \rightarrow KBI5 \rightarrow PTA5$                                        |

### Table 1-3. Function Priority in Shared Pins

### 2.6.7 Wait Mode

Putting the MCU into wait mode while the FLASH is in read mode does not affect the operation of the FLASH memory directly, but there will not be any memory activity since the CPU is inactive.

The WAIT instruction should not be executed while performing a program or erase operation on the FLASH, or the operation will discontinue and the FLASH will be on standby mode.

### 2.6.8 Stop Mode

Putting the MCU into stop mode while the FLASH is in read mode does not affect the operation of the FLASH memory directly, but there will not be any memory activity since the CPU is inactive.

The STOP instruction should not be executed while performing a program or erase operation on the FLASH, or the operation will discontinue and the FLASH will be on standby mode

#### NOTE

Standby mode is the power-saving mode of the FLASH module in which all internal control signals to the FLASH are inactive and the current consumption of the FLASH is at a minimum.

### 3.5.2 Stop Mode

The ADC module is inactive after the execution of a STOP instruction. Any pending conversion is aborted. ADC conversions resume when the MCU exits stop mode. Allow one conversion cycle to stabilize the analog circuitry before using ADC data after exiting stop mode.

## 3.6 Input/Output Signals

The ADC module has four channels that are shared with I/O port A.

ADC voltage in (ADCVIN) is the input voltage signal from one of the four ADC channels to the ADC module.

## 3.7 Input/Output Registers

These I/O registers control and monitor ADC operation:

- ADC status and control register (ADSCR)

- ADC data register (ADR)

- ADC clock register (ADICLK)

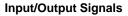

### 3.7.1 ADC Status and Control Register

The following paragraphs describe the function of the ADC status and control register (ADSCR). When a conversion is in process and the ADSCR is written, the current conversion data should be discarded to prevent an incorrect reading.

Figure 3-3. ADC Status and Control Register (ADSCR)

### COCO — Conversions Complete Bit

In non-interrupt mode (AIEN = 0), COCO is a read-only bit that is set at the end of each conversion. COCO will stay set until cleared by a read of the ADC data register. Reset clears this bit.

In interrupt mode (AIEN = 1), COCO is a read-only bit that is not set at the end of a conversion. It always reads as a 0.

1 = Conversion completed (AIEN = 0)

0 = Conversion not completed (AIEN = 0) or CPU interrupt enabled (AIEN = 1)

#### NOTE

The write function of the COCO bit is reserved. When writing to the ADSCR register, always have a 0 in the COCO bit position.

MC68HC908QY/QT Family Data Sheet, Rev. 6

#### **Configuration Register (CONFIG)**

#### IRQPUD — IRQ Pin Pullup Control Bit

- 1 = Internal pullup is disconnected

- 0 = Internal pullup is connected between  $\overline{IRQ}$  pin and  $V_{DD}$

#### IRQEN — IRQ Pin Function Selection Bit

- 1 = Interrupt request function active in pin

- 0 = Interrupt request function inactive in pin

#### OSCOPT1 and OSCOPT0 — Selection Bits for Oscillator Option

- (0, 0) Internal oscillator

- (0, 1) External oscillator

- (1, 0) External RC oscillator

- (1, 1) External XTAL oscillator

### **RSTEN** — **RST** Pin Function Selection

- 1 = Reset function active in pin

- 0 =Reset function inactive in pin

#### NOTE

The RSTEN bit is cleared by a power-on reset (POR) only. Other resets will leave this bit unaffected.

Address: \$001F

|                 | Bit 7 | 6       | 5       | 4       | 3       | 2     | 1    | Bit 0 |

|-----------------|-------|---------|---------|---------|---------|-------|------|-------|

| Read:<br>Write: | COPRS | LVISTOP | LVIRSTD | LVIPWRD | LVI5OR3 | SSREC | STOP | COPD  |

| Reset:          | 0     | 0       | 0       | 0       | U       | 0     | 0    | 0     |

| POR:            | 0     | 0       | 0       | 0       | 0       | 0     | 0    | 0     |

|                 |       |         |         |         |         |       |      |       |

U = Unaffected

#### Figure 5-2. Configuration Register 1 (CONFIG1)

#### COPRS (Out of STOP Mode) — COP Reset Period Selection Bit

- 1 = COP reset short cycle = 8176 × BUSCLKX4

- $0 = COP reset long cycle = 262,128 \times BUSCLKX4$

#### COPRS (In STOP Mode) — Auto Wakeup Period Selection Bit

- 1 = Auto wakeup short cycle =  $512 \times INTRCOSC$

- 0 = Auto wakeup long cycle =  $16,384 \times$  INTRCOSC

#### LVISTOP — LVI Enable in Stop Mode Bit

When the LVIPWRD bit is clear, setting the LVISTOP bit enables the LVI to operate during stop mode. Reset clears LVISTOP.

1 = LVI enabled during stop mode

0 = LVI disabled during stop mode

#### LVIRSTD — LVI Reset Disable Bit

LVIRSTD disables the reset signal from the LVI module.

1 = LVI module resets disabled

0 = LVI module resets enabled

### 6.3.7 COPRS (COP Rate Select)

The COPRS signal reflects the state of the COP rate select bit (COPRS) in the configuration register 1 (CONFIG1). See Chapter 5 Configuration Register (CONFIG).

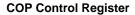

## 6.4 COP Control Register

The COP control register (COPCTL) is located at address \$FFFF and overlaps the reset vector. Writing any value to \$FFFF clears the COP counter and starts a new timeout period. Reading location \$FFFF returns the low byte of the reset vector.

Figure 6-2. COP Control Register (COPCTL)

## 6.5 Interrupts

The COP does not generate CPU interrupt requests.

## 6.6 Monitor Mode

The COP is disabled in monitor mode when  $V_{TST}$  is present on the IRQ pin.

## 6.7 Low-Power Modes

The WAIT and STOP instructions put the MCU in low power-consumption standby modes.

### 6.7.1 Wait Mode

The COP continues to operate during wait mode. To prevent a COP reset during wait mode, periodically clear the COP counter.

### 6.7.2 Stop Mode

Stop mode turns off the BUSCLKX4 input to the COP and clears the SIM counter. Service the COP immediately before entering or after exiting stop mode to ensure a full COP timeout period after entering or exiting stop mode.

## 6.8 COP Module During Break Mode

The COP is disabled during a break interrupt with monitor mode when BDCOP bit is set in break auxiliary register (BRKAR).

### 8.7.1 IRQ Input Pins (IRQ)

The IRQ pin provides a maskable external interrupt source. The IRQ pin contains an internal pullup device.

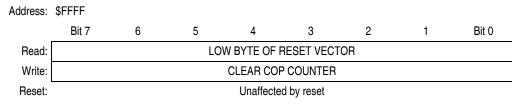

## 8.8 Registers

The IRQ status and control register (INTSCR) controls and monitors operation of the IRQ module. See Chapter 5 Configuration Register (CONFIG).

The INTSCR has the following functions:

- Shows the state of the IRQ flag

- Clears the IRQ latch

- Masks the IRQ interrupt request

- Controls triggering sensitivity of the IRQ interrupt pin

Figure 8-3. IRQ Status and Control Register (INTSCR)

#### IRQF — IRQ Flag

This read-only status bit is set when the IRQ interrupt is pending.

$1 = \overline{IRQ}$  interrupt pending

$0 = \overline{IRQ}$  interrupt not pending

#### ACK — IRQ Interrupt Request Acknowledge Bit

Writing a 1 to this write-only bit clears the IRQ latch. ACK always reads as 0.

#### IMASK — IRQ Interrupt Mask Bit

Writing a 1 to this read/write bit disables the IRQ interrupt request.

1 = IRQ interrupt request disabled

0 = IRQ interrupt request enabled

#### MODE — IRQ Edge/Level Select Bit

This read/write bit controls the triggering sensitivity of the IRQ pin.

$1 = \overline{IRQ}$  interrupt request on falling edges and low levels

$0 = \overline{IRQ}$  interrupt request on falling edges only

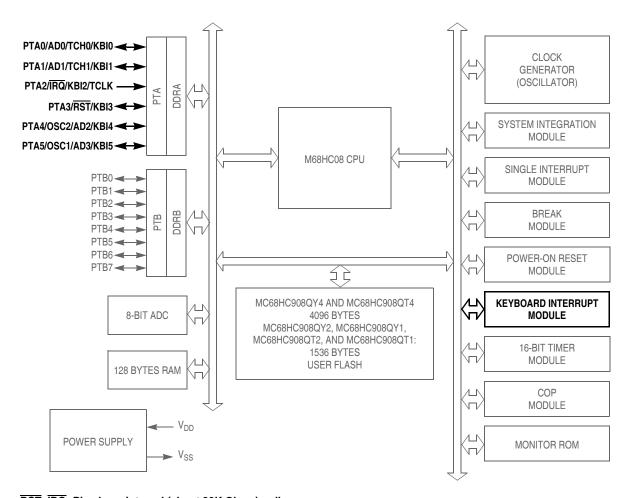

#### Keyboard Interrupt Module (KBI)

RST, IRQ: Pins have internal (about 30K Ohms) pull upPTA[0:5]: High current sink and source capabilityPTA[0:5]: Pins have programmable keyboard interrupt and pull upPTB[0:7]: Not available on 8-pin devices – MC68HC908QT1, MC68HC908QT2, and MC68HC908QT4 (see note in12.1 Introduction)

ADC: Not available on the MC68HC908QY1 and MC68HC908QT1

### Figure 9-1. Block Diagram Highlighting KBI Block and Pins

again in the SIM and results in the internal bus frequency being one fourth of either the XTALCLK, RCCLK, or INTCLK frequency.

## **11.5 Low Power Modes**

The WAIT and STOP instructions put the MCU in low-power consumption standby modes.

### 11.5.1 Wait Mode

The WAIT instruction has no effect on the oscillator logic. BUSCLKX2 and BUSCLKX4 continue to drive to the SIM module.

### 11.5.2 Stop Mode

The STOP instruction disables either the XTALCLK, the RCCLK, or INTCLK output, hence BUSCLKX2 and BUSCLKX4.

## 11.6 Oscillator During Break Mode

The oscillator continues to drive BUSCLKX2 and BUSCLKX4 when the device enters the break state.

## 11.7 CONFIG2 Options

Two CONFIG2 register options affect the operation of the oscillator module: OSCOPT1 and OSCOPT0. All CONFIG2 register bits will have a default configuration. Refer to Chapter 5 Configuration Register (CONFIG) for more information on how the CONFIG2 register is used.

Table 11-2 shows how the OSCOPT bits are used to select the oscillator clock source.

Table 11-2. Oscillator Modes

| OSCOPT1 | OSCOPT0 | Oscillator Modes    |

|---------|---------|---------------------|

| 0       | 0       | Internal oscillator |

| 0       | 1       | External oscillator |

| 1       | 0       | External RC         |

| 1       | 1       | External crystal    |

## 11.8 Input/Output (I/O) Registers

The oscillator module contains these two registers:

- 1. Oscillator status register (OSCSTAT)

- 2. Oscillator trim register (OSCTRIM)

#### Input/Output Ports (PORTS)

#### PTAPUE[5:0] — Port A Input Pullup Enable Bits

These read/write bits are software programmable to enable pullup devices on port A pins.

- 1 = Corresponding port A pin configured to have internal pull if its DDRA bit is set to 0

- 0 = Pullup device is disconnected on the corresponding port A pin regardless of the state of its DDRA bit

Table 12-1 summarizes the operation of the port A pins.

| PTAPUE | DDRA | ΡΤΑ              | I/O Pin                               | Accesses to DDRA | Access    | ses to PTA               |

|--------|------|------------------|---------------------------------------|------------------|-----------|--------------------------|

| Bit    | Bit  | Bit              | Mode                                  | Read/Write       | Read      | Write                    |

| 1      | 0    | X <sup>(1)</sup> | Input, V <sub>DD</sub> <sup>(2)</sup> | DDRA5-DDRA0      | Pin       | PTA5–PTA0 <sup>(3)</sup> |

| 0      | 0    | Х                | Input, Hi-Z <sup>(4)</sup>            | DDRA5-DDRA0      | Pin       | PTA5-PTA0 <sup>(3)</sup> |

| Х      | 1    | Х                | Output                                | DDRA5-DDRA0      | PTA5-PTA0 | PTA5-PTA0 <sup>(5)</sup> |

#### Table 12-1. Port A Pin Functions

1. X = don't care

2. I/O pin pulled to  $V_{DD}$  by internal pullup.

3. Writing affects data register, but does not affect input.

4. Hi-Z = high impedance

5. Output does not apply to PTA2

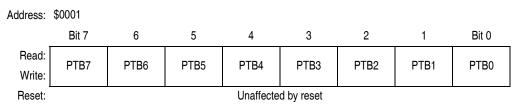

## 12.3 Port B

Port B is an 8-bit general purpose I/O port. Port B is only available on the MC68HC908QY1, MC68HC908QY2, and MC68HC908QY4.

### 12.3.1 Port B Data Register

The port B data register (PTB) contains a data latch for each of the eight port B pins.

### Figure 12-5. Port B Data Register (PTB)

### PTB[7:0] — Port B Data Bits

These read/write bits are software programmable. Data direction of each port B pin is under the control of the corresponding bit in data direction register B. Reset has no effect on port B data.

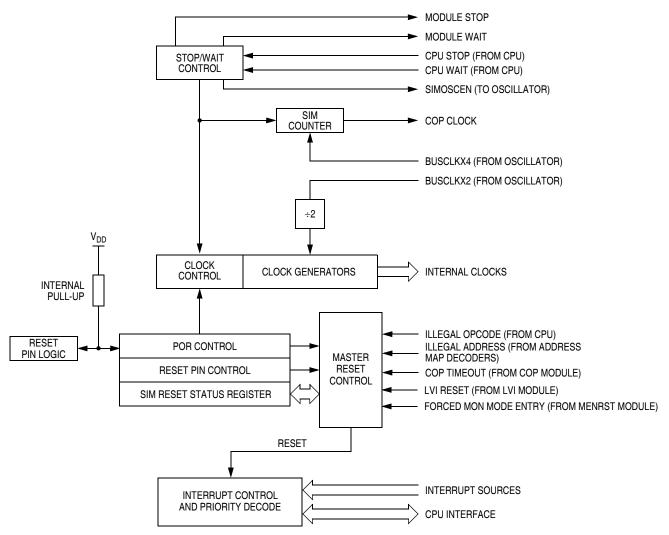

#### System Integration Module (SIM)

Figure 13-1. SIM Block Diagram

## 13.2 RST and IRQ Pins Initialization

RST and IRQ pins come out of reset as PTA3 and PTA2 respectively. RST and IRQ functions can be activated by programing CONFIG2 accordingly. Refer to Chapter 5 Configuration Register (CONFIG).

## **13.3 SIM Bus Clock Control and Generation**

The bus clock generator provides system clock signals for the CPU and peripherals on the MCU. The system clocks are generated from an incoming clock, BUSCLKX2, as shown in Figure 13-2.

### 13.5.2 SIM Counter During Stop Mode Recovery

The SIM counter also is used for stop mode recovery. The STOP instruction clears the SIM counter. After an interrupt, break, or reset, the SIM senses the state of the short stop recovery bit, SSREC, in the configuration register 1 (CONFIG1). If the SSREC bit is a 1, then the stop recovery is reduced from the normal delay of 4096 BUSCLKX4 cycles down to 32 BUSCLKX4 cycles. This is ideal for applications using canned oscillators that do not require long start-up times from stop mode. External crystal applications should use the full stop recovery time, that is, with SSREC cleared in the configuration register 1 (CONFIG1).

### 13.5.3 SIM Counter and Reset States

External reset has no effect on the SIM counter (see 13.7.2 Stop Mode for details.) The SIM counter is free-running after all reset states. See 13.4.2 Active Resets from Internal Sources for counter control and internal reset recovery sequences.

## **13.6 Exception Control**

Normal sequential program execution can be changed in three different ways:

- 1. Interrupts

- a. Maskable hardware CPU interrupts

- b. Non-maskable software interrupt instruction (SWI)

- 2. Reset

- 3. Break interrupts

#### 13.6.1 Interrupts

An interrupt temporarily changes the sequence of program execution to respond to a particular event. Figure 13-7 flow charts the handling of system interrupts.

Interrupts are latched, and arbitration is performed in the SIM at the start of interrupt processing. The arbitration result is a constant that the CPU uses to determine which vector to fetch. Once an interrupt is latched by the SIM, no other interrupt can take precedence, regardless of priority, until the latched interrupt is serviced (or the I bit is cleared).

At the beginning of an interrupt, the CPU saves the CPU register contents on the stack and sets the interrupt mask (I bit) to prevent additional interrupts. At the end of an interrupt, the RTI instruction recovers the CPU register contents from the stack so that normal processing can resume. Figure 13-8 shows interrupt entry timing. Figure 13-9 shows interrupt recovery timing.

#### System Integration Module (SIM)

The SIM counter is held in reset from the execution of the STOP instruction until the beginning of stop recovery. It is then used to time the recovery period. Figure 13-17 shows stop mode entry timing and Figure 13-18 shows the stop mode recovery time from interrupt or break.

**NOTE** To minimize stop current, all pins configured as inputs should be driven to

#### a logic 1 or logic 0. CPUSTOP ADDRESS BUS STOP ADDR STOP ADDR + 1 SAME SAME DATA BUS PREVIOUS DATA NEXT OPCODE SAME SAME R/W NOTE: Previous data can be operand data or the STOP opcode, depending on the last instruction. Figure 13-17. Stop Mode Entry Timing STOP RECOVERY PERIOD BUSCLKX4 INTERRUPT ADDRESS BUS STOP +1 STOP + 2 STOP + 2 SP SP – 1 SP – 2 SP – 3

Figure 13-18. Stop Mode Recovery from Interrupt

## 13.8 SIM Registers

The SIM has three memory mapped registers. Table 13-4 shows the mapping of these registers.

#### Table 13-4. SIM Registers

| Address | Register | Access Mode |

|---------|----------|-------------|

| \$FE00  | BSR      | User        |

| \$FE01  | SRSR     | User        |

| \$FE03  | BFCR     | User        |

# Chapter 16 Electrical Specifications

## **16.1 Introduction**

This section contains electrical and timing specifications.

## 16.2 Absolute Maximum Ratings

Maximum ratings are the extreme limits to which the microcontroller unit (MCU) can be exposed without permanently damaging it.

NOTE

This device is not guaranteed to operate properly at the maximum ratings. Refer to 16.5 5-V DC Electrical Characteristics and 16.9 3-V DC Electrical Characteristics for guaranteed operating conditions.

| Characteristic <sup>(1)</sup>                                                                          | Symbol                               | Value                          | Unit |

|--------------------------------------------------------------------------------------------------------|--------------------------------------|--------------------------------|------|

| Supply voltage                                                                                         | V <sub>DD</sub>                      | -0.3 to +6.0                   | V    |

| Input voltage                                                                                          | V <sub>IN</sub>                      | $V_{SS}$ –0.3 to $V_{DD}$ +0.3 | V    |

| Mode entry voltage, IRQ pin                                                                            | V <sub>TST</sub>                     | V <sub>SS</sub> –0.3 to +9.1   | V    |

| Maximum current per pin excluding PTA0–PTA5, $\mathrm{V}_{\mathrm{DD}}$ and $\mathrm{V}_{\mathrm{SS}}$ | I                                    | ±15                            | mA   |

| Maximum current for pins PTA0–PTA5                                                                     | I <sub>PTA0</sub> _I <sub>PTA5</sub> | ±25                            | mA   |

| Storage temperature                                                                                    | T <sub>STG</sub>                     | -55 to +150                    | °C   |

| Maximum current out of V <sub>SS</sub>                                                                 | I <sub>MVSS</sub>                    | 100                            | mA   |

| Maximum current into V <sub>DD</sub>                                                                   | I <sub>MVDD</sub>                    | 100                            | mA   |

1. Voltages references to  $V_{SS}$ .

### NOTE

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum-rated voltages to this high-impedance circuit. For proper operation, it is recommended that  $V_{IN}$  and  $V_{OUT}$  be constrained to the range  $V_{SS} \leq (V_{IN} \text{ or } V_{OUT}) \leq V_{DD}$ . Reliability of operation is enhanced if unused inputs are connected to an appropriate logic voltage level (for example, either  $V_{SS}$  or  $V_{DD}$ .)

MC68HC908QY/QT Family Data Sheet, Rev. 6

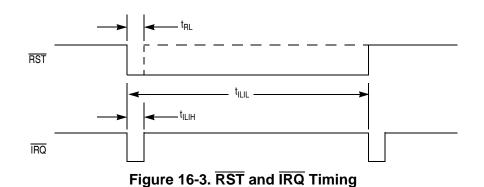

## 16.7 5-V Control Timing

| Characteristic <sup>(1)</sup>                  | Symbol                              | Min                 | Max | Unit             |

|------------------------------------------------|-------------------------------------|---------------------|-----|------------------|

| Internal operating frequency                   | f <sub>OP</sub> (f <sub>Bus</sub> ) | —                   | 8   | MHz              |

| Internal clock period (1/f <sub>OP</sub> )     | t <sub>cyc</sub>                    | 125                 | _   | ns               |

| RST input pulse width low                      | t <sub>RL</sub>                     | 100                 | _   | ns               |

| IRQ interrupt pulse width low (edge-triggered) | t <sub>ILIH</sub>                   | 100                 | _   | ns               |

| IRQ interrupt pulse period                     | t <sub>ILIL</sub>                   | Note <sup>(2)</sup> |     | t <sub>cyc</sub> |

1. V<sub>DD</sub> = 4.5 to 5.5 Vdc, V<sub>SS</sub> = 0 Vdc, T<sub>A</sub> = T<sub>L</sub> to T<sub>H</sub>; timing shown with respect to 20% V<sub>DD</sub> and 70% V<sub>SS</sub>, unless otherwise noted.

2. The minimum period is the number of cycles it takes to execute the interrupt service routine plus 1  $t_{cyc}$ .

## **16.16 Memory Characteristics**

| Characteristic                                      | Symbol                           | Min        | Тур    | Max        | Unit   |

|-----------------------------------------------------|----------------------------------|------------|--------|------------|--------|

| RAM data retention voltage                          | V <sub>RDR</sub>                 | 1.3        | _      | _          | V      |

| FLASH program bus clock frequency                   | _                                | 1          | _      |            | MHz    |

| FLASH read bus clock frequency                      | f <sub>Read</sub> <sup>(1)</sup> | 0          | —      | 8 M        | Hz     |

| FLASH page erase time<br><1 k cycles<br>>1 k cycles | t <sub>Erase</sub>               | 0.9<br>3.6 | 1<br>4 | 1.1<br>5.5 | ms     |

| FLASH mass erase time                               | t <sub>MErase</sub>              | 4          | _      | _          | ms     |

| FLASH PGM/ERASE to HVEN setup time                  | t <sub>NVS</sub>                 | 10         | —      | _          | μs     |

| FLASH high-voltage hold time                        | t <sub>NVH</sub>                 | 5          | —      | _          | μs     |

| FLASH high-voltage hold time (mass erase)           | t <sub>NVHL</sub>                | 100        | —      | _          | μs     |

| FLASH program hold time                             | t <sub>PGS</sub>                 | 5          | —      | _          | μs     |

| FLASH program time                                  | t <sub>PROG</sub>                | 30         | _      | 40         | μs     |

| FLASH return to read time                           | t <sub>RCV</sub> <sup>(2)</sup>  | 1          | _      | _          | μS     |

| FLASH cumulative program HV period                  | t <sub>HV</sub> <sup>(3)</sup>   | _          | —      | 4          | ms     |

| FLASH endurance <sup>(4)</sup>                      | _                                | 10 k       | 100 k  | _          | Cycles |

| FLASH data retention time <sup>(5)</sup>            | _                                | 15         | 100    | _          | Years  |

1.  $f_{Read}$  is defined as the frequency range for which the FLASH memory can be read.

2. t<sub>RCV</sub> is defined as the time it needs before the FLASH can be read after turning off the high voltage charge pump, by clearing HVEN to 0.

3.  $t_{HV}$  is defined as the cumulative high voltage programming time to the same row before next erase.

$t_{HV}$  must satisfy this condition:  $t_{NVS}$  +  $t_{NVH}$  +  $t_{PGS}$  +  $(t_{PROG} \ x \ 32) \ \leq t_{HV}$  maximum.

4. Typical endurance was evaluated for this product family. For additional information on how Freescale defines *Typical Endurance*, please refer to Engineering Bulletin EB619.

5. Typical data retention values are based on intrinsic capability of the technology measured at high temperature and de-rated to 25•C using the Arrhenius equation. For additional information on how Freescale defines *Typical Data Retention*, please refer to Engineering Bulletin EB618.

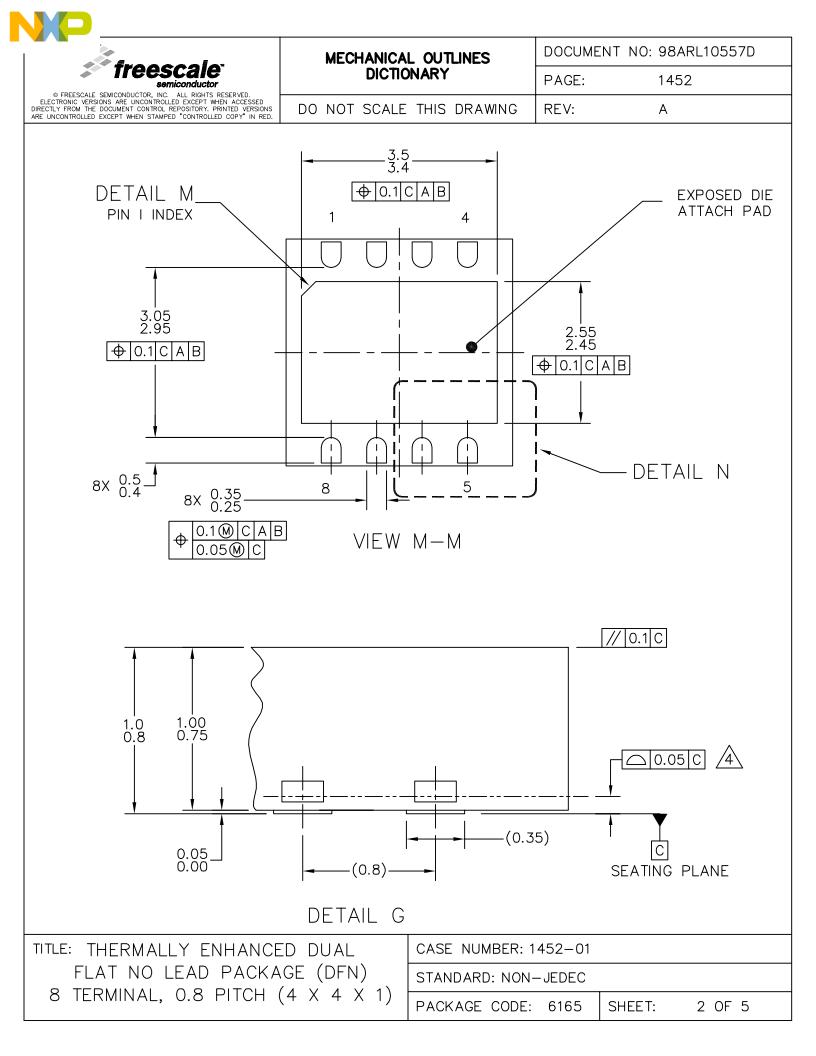

| NP                                                                                                                                                                                                |                           |                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|--------------------------|

|                                                                                                                                                                                                   | MECHANICAL OUTLINES       | DOCUMENT NO: 98ASH70107A |

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED.                                                                                                                                              | DICTIONARY                | PAGE: 968                |

| ELECTRONIC VERSIONS ARE UNCONTROLLED EXCEPT WHEN ACCESSED<br>DIRECTLY FROM THE DOCUMENT CONTROL REPOSITORY. PRINTED<br>VERSIONS ARE UNCONTROLLED EXCEPT WHEN STAMPED "CONTROLLED<br>COPY" IN RED. | DO NOT SCALE THIS DRAWING | REV: A                   |

NOTES:

1. DIMENSIONS AND TOLERANCES PER ASME Y14.5-1994.

2. CONTROLLING DIMENSION: MILLIMETER.

3. DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS AND ARE MEASURED AT THE PARTING LINE. MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEDD 0.15mm PER SIDE.

4. TERMINAL NUMBERS ARE SHOWN FOR REFERENCE ONLY.

5. THE LEAD WIDTH DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION SHALL BE 0.08mm TOTAL IN EXCESS OF THE LEAD WIDTH DIMENSION AT MAXIMUM MATERIAL CONDITION. DAMBAR CANNOT BE LOCATED ON THE LOWER RADIUS OR THE FOOT. MINIMUM SPACE BETWEEN PROTRUSIONS AND ADJACENT LEAD TO BE 0.46mm.

| 8 LEAD MFP |  | CASE NUMBER: 968-02 |               |  |  |

|------------|--|---------------------|---------------|--|--|

|            |  | STANDARD: EIAJ      |               |  |  |

|            |  | PACKAGE CODE: 6003  | SHEET: 3 OF 4 |  |  |

| NP                                                                                                                                                                                                |                                   |                          |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|--------------------------|--|

| • FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED.                                                                                                                                              | MECHANICAL OUTLINES<br>DICTIONARY | DOCUMENT NO: 98ASB42567B |  |

|                                                                                                                                                                                                   |                                   | PAGE: 751G               |  |

| ELECTRONIC VERSIONS ARE UNCONTROLLED EXCEPT WHEN ACCESSED<br>DIRECTLY FROM THE DOCUMENT CONTROL REPOSITORY. PRINTED<br>VERSIONS ARE UNCONTROLLED EXCEPT WHEN STAMPED "CONTROLLED<br>COPY" IN RED. | DO NOT SCALE THIS DRAWING         | REV: E                   |  |

#### NOTES:

- 1. DIMENSIONS ARE IN MILLIMETERS.

- 2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

- 3. DATUMS A AND B TO BE DETERMINED AT THE PLANE WHERE THE BOTTOM OF THE LEADS EXIT THE PLASTIC BODY.

- 4. THIS DIMENSION DOES NOT INCLUDE MOLD FLASH, PROTRUSION OR GATE BURRS. MOLD FLASH, PROTRUSION OR GATE BURRS SHALL NOT EXCEED 0.15 MM PER SIDE. THIS DIMENSION IS DETERMINED AT THE PLANE WHERE THE BOTTOM OF THE LEADS EXIT THE PLASTIC BODY.

- 5. THIS DIMENSION DOES NOT INCLUDE INTER-LEAD FLASH OR PROTRUSIONS. INTER-LEAD FLASH AND PROTRUSIONS SHALL NOT EXCEED 0.25 MM PER SIDE. THIS DIMENSION IS DETERMINED AT THE PLANE WHERE THE BOTTOM OF THE LEADS EXIT THE PLASTIC BODY.

- 6. THIS DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL NOT CAUSE THE LEAD WIDTH TO EXCEED 0.62 mm.

| TITLE:<br>16LD SOIC W/B, 1.27 PITCH,<br>CASE OUTLINE | CASE NUMBER: 751G-05             |  |

|------------------------------------------------------|----------------------------------|--|

|                                                      | STANDARD: JEDEC MS-013AA         |  |

|                                                      | PACKAGE CODE: 2003 SHEET: 2 OF 3 |  |