Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                      |

|----------------------------|-------------------------------------------------------------|

| Core Processor             | HC08                                                        |

| Core Size                  | 8-Bit                                                       |

| Speed                      | 8MHz                                                        |

| Connectivity               | -                                                           |

| Peripherals                | LVD, POR, PWM                                               |

| Number of I/O              | 6                                                           |

| Program Memory Size        | 1.5KB (1.5K x 8)                                            |

| Program Memory Type        | FLASH                                                       |

| EEPROM Size                | -                                                           |

| RAM Size                   | 128 x 8                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                 |

| Data Converters            | A/D 4x8b                                                    |

| Oscillator Type            | Internal                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                          |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 8-SOIC (0.209", 5.30mm Width)                               |

| Supplier Device Package    | 8-SO                                                        |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mchc908qt2mdwe |

|                            |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

**Revision History**

# **Revision History (Sheet 3 of 3)**

| Date              | Revision<br>Level | Description                                                                                                                                     | Page<br>Number(s)                    |

|-------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

|                   |                   | Reformatted to meet current documentation standards                                                                                             | Throughout                           |

|                   |                   | 6.3.1 BUSCLKX4 — Clarified description of BUSCLKX4                                                                                              | 58                                   |

|                   |                   | Chapter 7 Central Processor Unit (CPU) — In 7.7 Instruction Set Summary:<br>Reworked definitions for STOP instruction<br>Added WAIT instruction | 70<br>71                             |

| November,<br>2004 | 4.0               | 13.8.1 SIM Reset Status Register — Clarified SRSR flag setting                                                                                  | 117                                  |

| 2001              |                   | 14.9.1 TIM Status and Control Register — Added information to TSTOP note                                                                        | 127                                  |

|                   |                   | 16.8 5-V Oscillator Characteristics — Added values for deviation from trimmed inernal oscillator                                                | 155                                  |

|                   |                   | 16.12 3-V Oscillator Characteristics — Added values for deviation from trimmed inernal oscillator                                               | 158                                  |

|                   |                   | Figure 5-2. Configuration Register 1 (CONFIG1) — Clarified bit definitions for COPRS.                                                           | 54                                   |

| July,             | 5.0               | Chapter 8 External Interrupt (IRQ) — Reworked for clarification.                                                                                | 73                                   |

| 2005              |                   | 11.3.4 RC Oscillator — Improved RC oscillator wording.                                                                                          | 93                                   |

|                   |                   | 12.1 Introduction — Added note pertaining to non-bonded port pins.                                                                              | 97                                   |

|                   |                   | 17.3 Package Dimensions — Updated package information.                                                                                          | 165                                  |

| March,<br>2010    | 6.0               | Clarify internal oscillator trim register information.                                                                                          | 26, 27, 31,<br>34, 35, 38,<br>91, 96 |

# Chapter 12 Input/Output Ports (PORTS)

| 12.1   | Introduction                          | 97 |

|--------|---------------------------------------|----|

|        | Port A                                |    |

| 12.2.1 | Port A Data Register                  | 98 |

| 12.2.2 |                                       | 98 |

| 12.2.3 | Port A Input Pullup Enable Register   | 99 |

|        | Port B 1                              | 00 |

| 12.3.1 |                                       |    |

| 12.3.2 |                                       |    |

| 12.3.3 | Port B Input Pullup Enable Register 1 | 02 |

# Chapter 13 System Integration Module (SIM)

| 13.1 Intr        | oduction                                | 103 |

|------------------|-----------------------------------------|-----|

| 13.2 RS          | T and IRQ Pins Initialization           | 104 |

| 13.3 SIN         | A Bus Clock Control and Generation      | 104 |

| 13.3.1           | Bus Timing                              |     |

| 13.3.2           | Clock Start-Up from POR                 | 105 |

| 13.3.3           | Clocks in Stop Mode and Wait Mode       | 105 |

| 13.4 Res         | set and System Initialization           | 105 |

| 13.4.1           | External Pin Reset                      |     |

| 13.4.2           | Active Resets from Internal Sources     | 106 |

| 13.4.2.1         | Power-On Reset.                         |     |

| 13.4.2.2         | Computer Operating Properly (COP) Reset |     |

| 13.4.2.3         | Illegal Opcode Reset                    |     |

| 13.4.2.4         | Illegal Address Reset                   |     |

| 13.4.2.5         | Low-Voltage Inhibit (LVI) Reset         |     |

|                  | A Counter                               |     |

| 13.5.1           | SIM Counter During Power-On Reset       |     |

| 13.5.2           | SIM Counter During Stop Mode Recovery   |     |

| 13.5.3           | SIM Counter and Reset States            |     |

|                  | ception Control.                        |     |

| 13.6.1           | Interrupts                              |     |

| 13.6.1.1         | Hardware Interrupts                     |     |

| 13.6.1.2         | SWI Instruction                         |     |

| 13.6.2           | Interrupt Status Registers              |     |

| 13.6.2.1         | Interrupt Status Register 1             |     |

| 13.6.2.2         | Interrupt Status Register 2             |     |

| 13.6.2.3         | Interrupt Status Register 3             |     |

| 13.6.3<br>13.6.4 | Reset                                   |     |

| 13.6.5           | Break Interrupts                        |     |

|                  | Status Flag Protection in Break Mode    |     |

|                  | w-Power Modes                           |     |

| 13.7.1           | Wait Mode                               |     |

| 13.7.2           | Stop Mode                               | 115 |

#### General Description

- On-chip in-application programmable FLASH memory (with internal program/erase voltage generation)

- MC68HC908QY4 and MC68HC908QT4 4096 bytes

- MC68HC908QY2, MC68HC908QY1, MC68HC908QT2, and MC68HC908QT1 1536 bytes

- 128 bytes of on-chip random-access memory (RAM)

- 2-channel, 16-bit timer interface module (TIM)

- 4-channel, 8-bit analog-to-digital converter (ADC) on MC68HC908QY2, MC68HC908QY4, MC68HC908QT2, and MC68HC908QT4

- 5 or 13 bidirectional input/output (I/O) lines and one input only:

- Six shared with keyboard interrupt function and ADC

- Two shared with timer channels

- One shared with external interrupt (IRQ)

- Eight extra I/O lines on 16-pin package only

- High current sink/source capability on all port pins

- Selectable pullups on all ports, selectable on an individual bit basis

- Three-state ability on all port pins

- 6-bit keyboard interrupt with wakeup feature (KBI)

- Low-voltage inhibit (LVI) module features:

- Software selectable trip point in CONFIG register

- System protection features:

- Computer operating properly (COP) watchdog

- Low-voltage detection with reset

- Illegal opcode detection with reset

- Illegal address detection with reset

- External asynchronous interrupt pin with internal pullup (IRQ) shared with general-purpose input pin

- Master asynchronous reset pin (RST) shared with general-purpose input/output (I/O) pin

- Power-on reset

- Internal pullups on IRQ and RST to reduce external components

- Memory mapped I/O registers

- Power saving stop and wait modes

- MC68HC908QY4, MC68HC908QY2, and MC68HC908QY1 are available in these packages:

- 16-pin plastic dual in-line package (PDIP)

- 16-pin small outline integrated circuit (SOIC) package

- 16-pin thin shrink small outline package (TSSOP)

- MC68HC908QT4, MC68HC908QT2, and MC68HC908QT1 are available in these packages:

- 8-pin PDIP

- 8-pin SOIC

- 8-pin dual flat no lead (DFN) package

**General Description**

# **1.5 Pin Functions**

Table 1-2 provides a description of the pin functions.

| Pin<br>Name             | Description                                                                                                         | Input/Output     |

|-------------------------|---------------------------------------------------------------------------------------------------------------------|------------------|

| $V_{DD}$                | Power supply                                                                                                        | Power            |

| V <sub>SS</sub>         | Power supply ground                                                                                                 | Power            |

|                         | PTA0 — General purpose I/O port                                                                                     | Input/Output     |

| DTAO                    | AD0 — A/D channel 0 input                                                                                           | Input            |

| PTA0                    | TCH0 — Timer Channel 0 I/O                                                                                          | Input/Output     |

|                         | KBI0 — Keyboard interrupt input 0                                                                                   | Input            |

|                         | PTA1 — General purpose I/O port                                                                                     | Input/Output     |

| PTA1                    | AD1 — A/D channel 1 input                                                                                           | Input            |

| FIAT                    | TCH1 — Timer Channel 1 I/O                                                                                          | Input/Output     |

|                         | KBI1 — Keyboard interrupt input 1                                                                                   | Input            |

|                         | PTA2 — General purpose input-only port                                                                              | Input            |

| PTA2                    | IRQ — External interrupt with programmable pullup and Schmitt trigger input                                         | Input            |

| ΠΑΖ                     | KBI2 — Keyboard interrupt input 2                                                                                   | Input            |

|                         | TCLK — Timer clock input                                                                                            | Input            |

|                         | PTA3 — General purpose I/O port                                                                                     | Input/Output     |

| PTA3                    | RST — Reset input, active low with internal pullup and Schmitt trigger                                              | Input            |

|                         | KBI3 — Keyboard interrupt input 3                                                                                   | Input            |

|                         | PTA4 — General purpose I/O port                                                                                     | Input/Output     |

| PTA4                    | OSC2 —XTAL oscillator output (XTAL option only)<br>RC or internal oscillator output (OSC2EN = 1 in PTAPUE register) | Output<br>Output |

|                         | AD2 — A/D channel 2 input                                                                                           | Input            |

|                         | KBI4 — Keyboard interrupt input 4                                                                                   | Input            |

|                         | PTA5 — General purpose I/O port                                                                                     | Input/Output     |

| PTA5                    | OSC1 — XTAL, RC, or external oscillator input                                                                       | Input            |

| L 149                   | AD3 — A/D channel 3 input                                                                                           | Input            |

|                         | KBI5 — Keyboard interrupt input 5                                                                                   | Input            |

| PTB[0:7] <sup>(1)</sup> | 8 general-purpose I/O ports                                                                                         | Input/Output     |

### Table 1-2. Pin Functions

1. The PTB pins are not available on the 8-pin packages (see note in 12.1 Introduction).

#### Keyboard Interrupt Module (KBI)

To determine the logic level on a keyboard interrupt pin, use the data direction register to configure the pin as an input and then read the data register.

#### NOTE

Setting a keyboard interrupt enable bit (KBIEx) forces the corresponding keyboard interrupt pin to be an input, overriding the data direction register. However, the data direction register bit must be a 0 for software to read the pin.

#### 9.3.2 Keyboard Initialization

When a keyboard interrupt pin is enabled, it takes time for the internal pullup to reach a logic 1. Therefore a false interrupt can occur as soon as the pin is enabled.

To prevent a false interrupt on keyboard initialization:

- 1. Mask keyboard interrupts by setting the IMASKK bit in the keyboard status and control register.

- 2. Enable the KBI pins by setting the appropriate KBIEx bits in the keyboard interrupt enable register.

- 3. Write to the ACKK bit in the keyboard status and control register to clear any false interrupts.

- 4. Clear the IMASKK bit.

An interrupt signal on an edge-triggered pin can be acknowledged immediately after enabling the pin. An interrupt signal on an edge- and level-triggered interrupt pin must be acknowledged after a delay that depends on the external load.

Another way to avoid a false interrupt:

- 1. Configure the keyboard pins as outputs by setting the appropriate DDRA bits in the data direction register A.

- 2. Write 1s to the appropriate port A data register bits.

- 3. Enable the KBI pins by setting the appropriate KBIEx bits in the keyboard interrupt enable register.

# 9.4 Wait Mode

The keyboard module remains active in wait mode. Clearing the IMASKK bit in the keyboard status and control register enables keyboard interrupt requests to bring the MCU out of wait mode.

# 9.5 Stop Mode

The keyboard module remains active in stop mode. Clearing the IMASKK bit in the keyboard status and control register enables keyboard interrupt requests to bring the MCU out of stop mode.

# 9.6 Keyboard Module During Break Interrupts

The system integration module (SIM) controls whether the keyboard interrupt latch can be cleared during the break state. The BCFE bit in the break flag control register (BFCR) enables software to clear status bits during the break state.

To allow software to clear the keyboard interrupt latch during a break interrupt, write a 1 to the BCFE bit. If a latch is cleared during the break state, it remains cleared when the MCU exits the break state.

#### Low-Voltage Inhibit (LVI)

$V_{TRIPF}$ . Setting the LVI enable in stop mode bit, LVISTOP, enables the LVI to operate in stop mode. Setting the LVI 5-V or 3-V trip point bit, LVI5OR3, enables the trip point voltage,  $V_{TRIPF}$ , to be configured for 5-V operation. Clearing the LVI5OR3 bit enables the trip point voltage,  $V_{TRIPF}$ , to be configured for 3-V operation. The actual trip thresholds are specified in 16.5 5-V DC Electrical Characteristics and 16.9 3-V DC Electrical Characteristics.

#### NOTE

After a power-on reset, the LVI's default mode of operation is 3 volts. If a 5-V system is used, the user must set the LVI5OR3 bit to raise the trip point to 5-V operation.

If the user requires 5-V mode and sets the LVI5OR3 bit after power-on reset while the V<sub>DD</sub> supply is not above the V<sub>TRIPR</sub> for 5-V mode, the microcontroller unit (MCU) will immediately go into reset. The next time the LVI releases the reset, the supply will be above the V<sub>TRIPR</sub> for 5-V mode.

Once an LVI reset occurs, the MCU remains in reset until  $V_{DD}$  rises above a voltage,  $V_{TRIPR}$ , which causes the MCU to exit reset. See Chapter 13 System Integration Module (SIM) for the reset recovery sequence.

The output of the comparator controls the state of the LVIOUT flag in the LVI status register (LVISR) and can be used for polling LVI operation when the LVI reset is disabled.

# 10.3.1 Polled LVI Operation

In applications that can operate at  $V_{DD}$  levels below the  $V_{TRIPF}$  level, software can monitor  $V_{DD}$  by polling the LVIOUT bit. In the configuration register, the LVIPWRD bit must be cleared to enable the LVI module, and the LVIRSTD bit must be at set to disable LVI resets.

### 10.3.2 Forced Reset Operation

In applications that require  $V_{DD}$  to remain above the  $V_{TRIPF}$  level, enabling LVI resets allows the LVI module to reset the MCU when  $V_{DD}$  falls below the  $V_{TRIPF}$  level. In the configuration register, the LVIPWRD and LVIRSTD bits must be cleared to enable the LVI module and to enable LVI resets.

### 10.3.3 Voltage Hysteresis Protection

Once the LVI has triggered (by having  $V_{DD}$  fall below  $V_{TRIPF}$ ), the LVI will maintain a reset condition until  $V_{DD}$  rises above the rising trip point voltage,  $V_{TRIPR}$ . This prevents a condition in which the MCU is continually entering and exiting reset if  $V_{DD}$  is approximately equal to  $V_{TRIPF}$ .  $V_{TRIPR}$  is greater than  $V_{TRIPF}$  by the hysteresis voltage,  $V_{HYS}$ .

### 10.3.4 LVI Trip Selection

The LVI5OR3 bit in the configuration register selects whether the LVI is configured for 5-V or 3-V protection.

#### NOTE

The microcontroller is guaranteed to operate at a minimum supply voltage. The trip point ( $V_{TRIPF}$  [5 V] or  $V_{TRIPF}$  [3 V]) may be lower than this. See 16.5 5-V DC Electrical Characteristics and 16.9 3-V DC Electrical Characteristics for the actual trip point voltages.

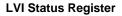

# 10.4 LVI Status Register

The LVI status register (LVISR) indicates if the  $V_{DD}$  voltage was detected below the  $V_{TRIPF}$  level while LVI resets have been disabled.

Figure 10-2. LVI Status Register (LVISR)

### LVIOUT — LVI Output Bit

This read-only flag becomes set when the  $V_{DD}$  voltage falls below the  $V_{TRIPF}$  trip voltage and is cleared when  $V_{DD}$  voltage rises above  $V_{TRIPR}$ . The difference in these threshold levels results in a hysteresis that prevents oscillation into and out of reset (see Table 10-1). Reset clears the LVIOUT bit.

| V <sub>DD</sub>                  | LVIOUT         |

|----------------------------------|----------------|

| $V_{DD} > V_{TRIPR}$             | 0              |

| $V_{DD} < V_{TRIPF}$             | 1              |

| $V_{TRIPF} < V_{DD} < V_{TRIPR}$ | Previous value |

Table 10-1. LVIOUT Bit Indication

# 10.5 LVI Interrupts

The LVI module does not generate interrupt requests.

# **10.6 Low-Power Modes**

The STOP and WAIT instructions put the MCU in low power-consumption standby modes.

### 10.6.1 Wait Mode

If enabled, the LVI module remains active in wait mode. If enabled to generate resets, the LVI module can generate a reset and bring the MCU out of wait mode.

### 10.6.2 Stop Mode

When the LVIPWRD bit in the configuration register is cleared and the LVISTOP bit in the configuration register is set, the LVI module remains active in stop mode. If enabled to generate resets, the LVI module can generate a reset and bring the MCU out of stop mode.

Oscillator Module (OSC)

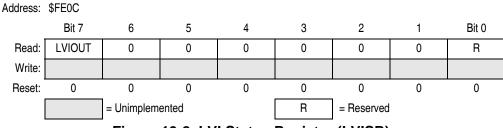

# 11.3.3 XTAL Oscillator

The XTAL oscillator circuit is designed for use with an external crystal or ceramic resonator to provide an accurate clock source. In this configuration, the OSC2 pin is dedicated to the external crystal circuit. The OSC2EN bit in the port A pullup enable register has no effect when this clock mode is selected.

In its typical configuration, the XTAL oscillator is connected in a Pierce oscillator configuration, as shown in Figure 11-2. This figure shows only the logical representation of the internal components and may not represent actual circuitry. The oscillator configuration uses five components:

- Crystal, X<sub>1</sub>

- Fixed capacitor, C<sub>1</sub>

- Tuning capacitor, C<sub>2</sub> (can also be a fixed capacitor)

- Feedback resistor, R<sub>B</sub>

- Series resistor, R<sub>s</sub> (optional)

#### NOTE

The series resistor ( $R_s$ ) is included in the diagram to follow strict Pierce oscillator guidelines and may not be required for all ranges of operation, especially with high frequency crystals. Refer to the crystal manufacturer's data for more information.

Note 1.

$R_s$  can be zero (shorted) when used with higher-frequency crystals. Refer to manufacturer's data. See Chapter 16 Electrical Specifications for component value recommendations.

MC68HC908QY/QT Family Data Sheet, Rev. 6

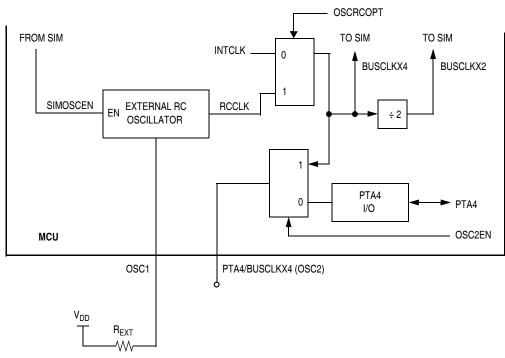

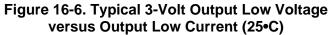

# 11.3.4 RC Oscillator

The RC oscillator circuit is designed for use with an external resistor ( $R_{EXT}$ ) to provide a clock source with a tolerance within 25% of the expected frequency. See Figure 11-3.

The capacitor (C) for the RC oscillator is internal to the MCU. The R<sub>EXT</sub> value must have a tolerance of 1% or less to minimize its effect on the frequency.

In this configuration, the OSC2 pin can be left in the reset state as PTA4. Or, the OSC2EN bit in the port A pullup enable register can be set to enable the OSC2 output function on the pin. Enabling the OSC2 output slightly increases the external RC oscillator frequency, f<sub>RCCLK</sub>.

See Chapter 16 Electrical Specifications for component value requirements.

#### Figure 11-3. RC Oscillator External Connections

# **11.4 Oscillator Module Signals**

The following paragraphs describe the signals that are inputs to and outputs from the oscillator module.

### 11.4.1 Crystal Amplifier Input Pin (OSC1)

The OSC1 pin is either an input to the crystal oscillator amplifier, an input to the RC oscillator circuit, or an external clock source.

For the internal oscillator configuration, the OSC1 pin can assume other functions according to Table 1-3. Function Priority in Shared Pins.

Timer Interface Module (TIM)

# 14.4.1 TIM Counter Prescaler

The TIM clock source is one of the seven prescaler outputs or the TIM clock pin, TCLK. The prescaler generates seven clock rates from the internal bus clock. The prescaler select bits, PS[2:0], in the TIM status and control register (TSC) select the TIM clock source.

# 14.4.2 Input Capture

With the input capture function, the TIM can capture the time at which an external event occurs. When an active edge occurs on the pin of an input capture channel, the TIM latches the contents of the TIM counter into the TIM channel registers, TCHxH:TCHxL. The polarity of the active edge is programmable. Input captures can generate TIM central processor unit (CPU) interrupt requests.

# 14.4.3 Output Compare

With the output compare function, the TIM can generate a periodic pulse with a programmable polarity, duration, and frequency. When the counter reaches the value in the registers of an output compare channel, the TIM can set, clear, or toggle the channel pin. Output compares can generate TIM CPU interrupt requests.

### 14.4.3.1 Unbuffered Output Compare

Any output compare channel can generate unbuffered output compare pulses as described in 14.4.3 Output Compare. The pulses are unbuffered because changing the output compare value requires writing the new value over the old value currently in the TIM channel registers.

An unsynchronized write to the TIM channel registers to change an output compare value could cause incorrect operation for up to two counter overflow periods. For example, writing a new value before the counter reaches the old value but after the counter reaches the new value prevents any compare during that counter overflow period. Also, using a TIM overflow interrupt routine to write a new, smaller output compare value may cause the compare to be missed. The TIM may pass the new value before it is written.

Use the following methods to synchronize unbuffered changes in the output compare value on channel x:

- When changing to a smaller value, enable channel x output compare interrupts and write the new value in the output compare interrupt routine. The output compare interrupt occurs at the end of the current output compare pulse. The interrupt routine has until the end of the counter overflow period to write the new value.

- When changing to a larger output compare value, enable TIM overflow interrupts and write the new

value in the TIM overflow interrupt routine. The TIM overflow interrupt occurs at the end of the

current counter overflow period. Writing a larger value in an output compare interrupt routine (at

the end of the current pulse) could cause two output compares to occur in the same counter

overflow period.

### 14.4.3.2 Buffered Output Compare

Channels 0 and 1 can be linked to form a buffered output compare channel whose output appears on the TCH0 pin. The TIM channel registers of the linked pair alternately control the output.

Setting the MS0B bit in TIM channel 0 status and control register (TSC0) links channel 0 and channel 1. The output compare value in the TIM channel 0 registers initially controls the output on the TCH0 pin. Writing to the TIM channel 1 registers enables the TIM channel 1 registers to synchronously control the output after the TIM overflows. At each subsequent overflow, the TIM channel registers (0 or 1) that

# Chapter 15 Development Support

# **15.1 Introduction**

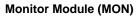

This section describes the break module, the monitor read-only memory (MON), and the monitor mode entry methods.

# 15.2 Break Module (BRK)

The break module can generate a break interrupt that stops normal program flow at a defined address to enter a background program.

Features include:

- Accessible input/output (I/O) registers during the break Interrupt

- Central processor unit (CPU) generated break interrupts

- Software-generated break interrupts

- Computer operating properly (COP) disabling during break interrupts

# 15.2.1 Functional Description

When the internal address bus matches the value written in the break address registers, the break module issues a breakpoint signal (BKPT) to the system integration module (SIM). The SIM then causes the CPU to load the instruction register with a software interrupt instruction (SWI). The program counter vectors to \$FFFC and \$FFFD (\$FEFC and \$FEFD in monitor mode).

The following events can cause a break interrupt to occur:

- A CPU generated address (the address in the program counter) matches the contents of the break address registers.

- Software writes a 1 to the BRKA bit in the break status and control register.

When a CPU generated address matches the contents of the break address registers, the break interrupt is generated. A return-from-interrupt instruction (RTI) in the break routine ends the break interrupt and returns the microcontroller unit (MCU) to normal operation.

Figure 15-2 shows the structure of the break module.

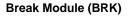

### 15.2.2.3 Break Auxiliary Register

The break auxiliary register (BRKAR) contains a bit that enables software to disable the COP while the MCU is in a state of break interrupt with monitor mode.

Figure 15-6. Break Auxiliary Register (BRKAR)

#### BDCOP — Break Disable COP Bit

This read/write bit disables the COP during a break interrupt. Reset clears the BDCOP bit.

- 1 = COP disabled during break interrupt

- 0 = COP enabled during break interrupt

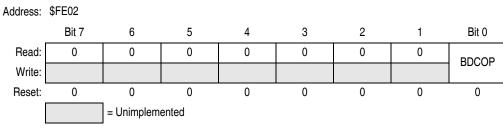

### 15.2.2.4 Break Status Register

The break status register (BSR) contains a flag to indicate that a break caused an exit from wait mode. This register is only used in emulation mode.

Figure 15-7. Break Status Register (BSR)

#### SBSW — SIM Break Stop/Wait

SBSW can be read within the break state SWI routine. The user can modify the return address on the stack by subtracting one from it.

1 = Wait mode was exited by break interrupt

0 = Wait mode was not exited by break interrupt

Figure 15-12. Monitor Mode Circuit (Internal Clock, No High Voltage)

Simple monitor commands can access any memory address. In monitor mode, the MCU can execute code downloaded into RAM by a host computer while most MCU pins retain normal operating mode functions. All communication between the host computer and the MCU is through the PTA0 pin. A level-shifting and multiplexing interface is required between PTA0 and the host computer. PTA0 is used in a wired-OR configuration and requires a pullup resistor.

The monitor code has been updated from previous versions of the monitor code to allow enabling the internal oscillator to generate the internal clock. This addition, which is enabled when  $\overline{IRQ}$  is held low out of reset, is intended to support serial communication/programming at 9600 baud in monitor mode by using the internal oscillator, and the internal oscillator user trim value OSCTRIM (FLASH location \$FFC0, if programmed) to generate the desired internal frequency (3.2 MHz). Since this feature is enabled only when  $\overline{IRQ}$  is held low out of reset, it cannot be used when the reset vector is programmed (i.e., the value is not \$FFFF) because entry into monitor mode in this case requires V<sub>TST</sub> on  $\overline{IRQ}$ . The  $\overline{IRQ}$  pin must remain low during this monitor session in order to maintain communication.

Table 15-1 shows the pin conditions for entering monitor mode. As specified in the table, monitor mode may be entered after a power-on reset (POR) and will allow communication at 9600 baud provided one of the following sets of conditions is met:

- If \$FFFE and \$FFFF do not contain \$FF (programmed state):

- The external clock is 9.8304 MHz

- IRQ = V<sub>TST</sub>

- If \$FFFE and \$FFFF contain \$FF (erased state):

- The external clock is 9.8304 MHz

- $\overline{IRQ} = V_{DD}$  (this can be implemented through the internal  $\overline{IRQ}$  pullup)

- If \$FFFE and \$FFFF contain \$FF (erased state):

- IRQ = V<sub>SS</sub> (internal oscillator is selected, no external clock required)

#### MC68HC908QY/QT Family Data Sheet, Rev. 6

**Electrical Specifications**

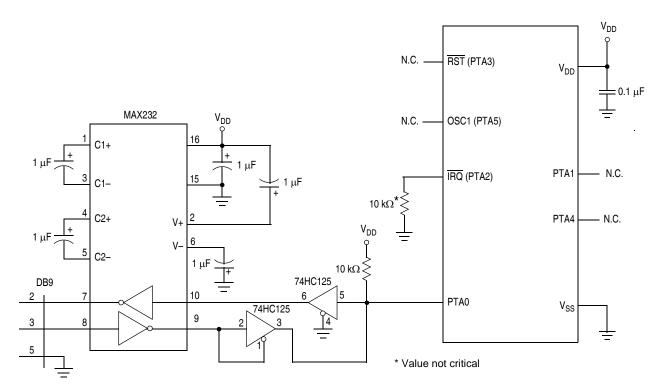

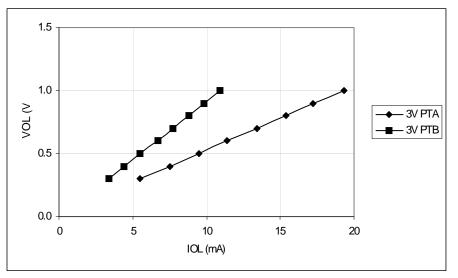

# 16.10 Typical 3.0-V Output Drive Characteristics

**Electrical Specifications**

# 16.12 3-V Oscillator Characteristics

| Characteristic                                                                                                                                                                               | Symbol             | Min             | Тур                | Max  | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------|--------------------|------|------|

| Internal oscillator frequency <sup>(1)</sup>                                                                                                                                                 | <b>f</b> INTCLK    | —               | 12.8               | —    | MHz  |

| Deviation from trimmed Internal oscillator $^{(2)(3)}$<br>12.8 MHz, fixed voltage, fixed temp<br>12.8 MHz, V <sub>DD</sub> ± 10%, 0 to 70°C<br>12.8 MHz, V <sub>DD</sub> ± 10%, -40 to 125°C | ACCINT             |                 | ± 0.4<br>± 2<br>—  | <br> | %    |

| Crystal frequency, XTALCLK <sup>(1)</sup>                                                                                                                                                    | foscxclk           | 1               | —                  | 16   | MHz  |

| External RC oscillator frequency, RCCLK <sup>(1)</sup>                                                                                                                                       | f <sub>RCCLK</sub> | 2               | —                  | 10   | MHz  |

| External clock reference frequency <sup>(1) (4)</sup>                                                                                                                                        | foscxclk           | dc              | —                  | 16   | MHz  |

| Crystal load capacitance <sup>(5)</sup>                                                                                                                                                      | CL                 | —               | 20                 | —    | pF   |

| Crystal fixed capacitance <sup>(3)</sup>                                                                                                                                                     | C <sub>1</sub>     | —               | 2 x C <sub>L</sub> | —    | —    |

| Crystal tuning capacitance <sup>(3)</sup>                                                                                                                                                    | C <sub>2</sub>     | —               | 2 x C <sub>L</sub> | —    | —    |

| Feedback bias resistor                                                                                                                                                                       | R <sub>B</sub>     | 0.5             | 1                  | 10   | MΩ   |

| RC oscillator external resistor                                                                                                                                                              | R <sub>EXT</sub>   | See Figure 16-8 |                    |      | —    |

| Crystal series damping resistor<br>$f_{OSCXCLK} = 1 MHz$<br>$f_{OSCXCLK} = 4 MHz$<br>$f_{OSCXCLK} = > 8 MHz$                                                                                 | R <sub>S</sub>     |                 | 10<br>5<br>0       |      | kΩ   |

Bus frequency, f<sub>OP</sub>, is oscillator frequency divided by 4.

Deviation values assumes trimming @25•C and midpoint of voltage range.

Values are based on characterization results, not tested in production.

4. No more than 10% duty cycle deviation from 50%

5. Consult crystal vendor data sheet

Figure 16-8. RC versus Frequency (3 Volts @ 25•C)

#### MC68HC908QY/QT Family Data Sheet, Rev. 6

# 16.14 Analog-to-Digital Converter Characteristics

| Characteristic                                         | Symbol            | Min                          | Мах                          | Unit                     | Comments                                         |

|--------------------------------------------------------|-------------------|------------------------------|------------------------------|--------------------------|--------------------------------------------------|

| Supply voltage                                         | V <sub>DDAD</sub> | 2.7<br>(V <sub>DD</sub> min) | 5.5<br>(V <sub>DD</sub> max) | V                        | —                                                |

| Input voltages                                         | V <sub>ADIN</sub> | V <sub>SS</sub>              | V <sub>DD</sub>              | V                        | —                                                |

| Resolution<br>(1 LSB)                                  | RES               | 10.5                         | 21.5                         | mV                       | —                                                |

| Absolute accuracy<br>(Total unadjusted error)          | E <sub>TUE</sub>  | _                            | ± 1.5                        | LSB                      | Includes quantization                            |

| ADC internal clock                                     | f <sub>ADIC</sub> | 0.5                          | 1.048                        | MHz                      | $t_{ADIC} = 1/f_{ADIC},$<br>tested only at 1 MHz |

| Conversion range                                       | V <sub>AIN</sub>  | V <sub>SS</sub>              | V <sub>DD</sub>              | V                        | —                                                |

| Power-up time                                          | t <sub>ADPU</sub> | 16                           | —                            | t <sub>ADIC</sub> cycles | $t_{ADIC} = 1/f_{ADIC}$                          |

| Conversion time                                        | t <sub>ADC</sub>  | 16                           | 17                           | t <sub>ADIC</sub> cycles | $t_{ADIC} = 1/f_{ADIC}$                          |

| Sample time <sup>(1)</sup>                             | t <sub>ADS</sub>  | 5                            | —                            | t <sub>ADIC</sub> cycles | $t_{ADIC} = 1/f_{ADIC}$                          |

| Zero input reading <sup>(2)</sup>                      | Z <sub>ADI</sub>  | 00                           | 01                           | Hex                      | V <sub>IN</sub> = V <sub>SS</sub>                |

| Full-scale reading <sup>(3)</sup>                      | F <sub>ADI</sub>  | FE                           | FF                           | Hex                      | $V_{IN} = V_{DD}$                                |

| Input capacitance                                      | C <sub>ADI</sub>  | _                            | 8                            | pF                       | Not tested                                       |

| Input leakage <sup>(3)</sup>                           | I <sub>IL</sub>   | —                            | ± 1                          | μΑ                       | —                                                |

| ADC supply current<br>$V_{DD} = 3 V$<br>$V_{DD} = 5 V$ | I <sub>ADAD</sub> |                              | l = 0.45<br>l = 0.65         | mA<br>mA                 | Enabled<br>Enabled                               |

1. Source impedances greater than 10 kΩ adversely affect internal RC charging time during input sampling.

2. Zero-input/full-scale reading requires sufficient decoupling measures for accurate conversions.

3. The external system error caused by input leakage current is approximately equal to the product of R source and input current.

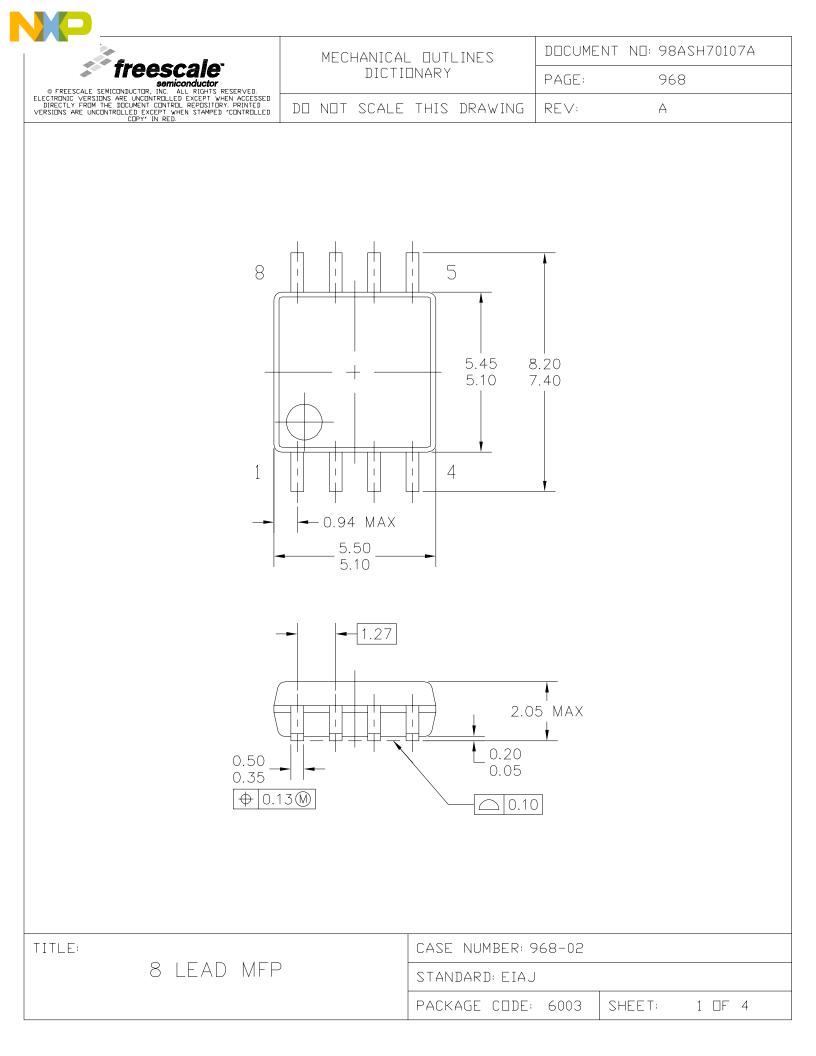

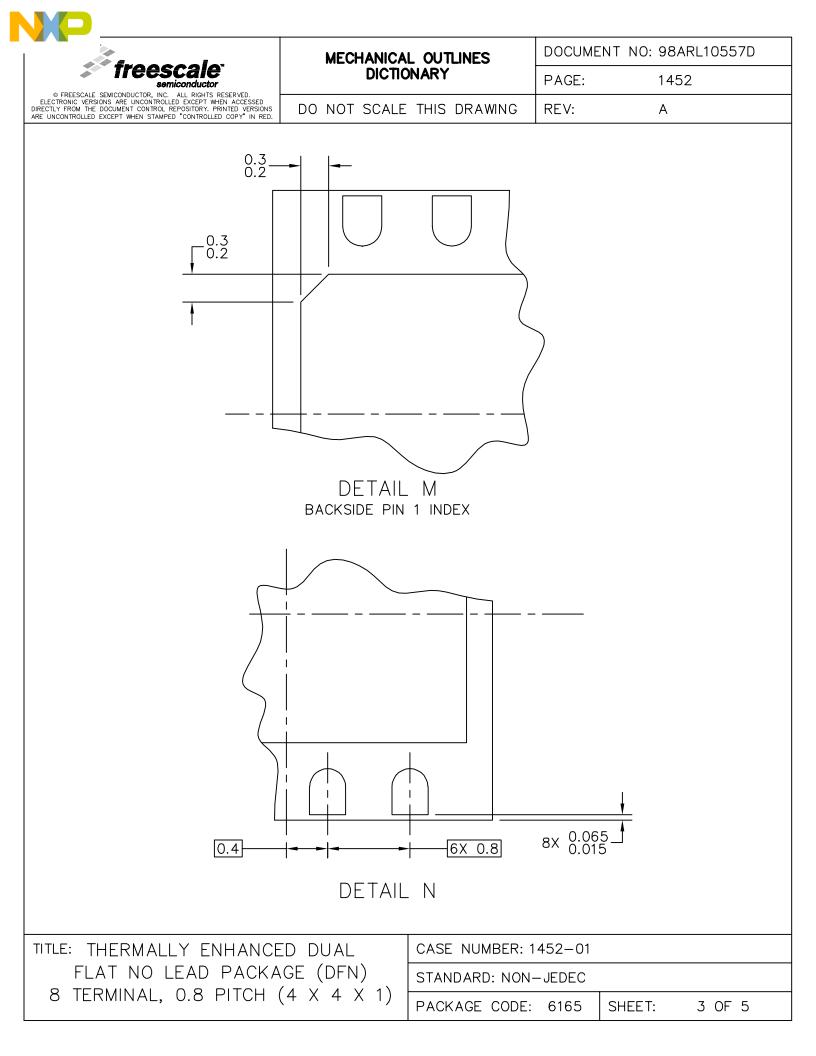

# Chapter 17 Ordering Information and Mechanical Specifications

# **17.1 Introduction**

This section contains order numbers for the MC68HC908QY1, MC68HC908QY2, MC68HC908QY4, MC68HC908QT1, MC68HC908QT2, and MC69HC908QT4. Dimensions are given for:

- 8-pin plastic dual in-line package (PDIP)

- 8-pin small outline integrated circuit (SOIC) package

- 8-pin dual flat no lead (DFN) package

- 16-pin PDIP

- 16-pin SOIC

- 16-pin thin shrink small outline package (TSSOP)

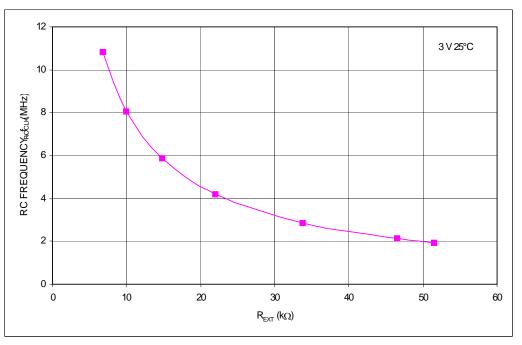

# 17.2 MC Order Numbers

| MC Order Number | ADC | FLASH Memory | Package     |

|-----------------|-----|--------------|-------------|

| MC908QY1        | —   | 1536 bytes   | 16-pins     |

| MC908QY2        | Yes | 1536 bytes   | PDIP, SOIC, |

| MC908QY4        | Yes | 4096 bytes   | and TSSOP   |

| MC908QT1        | —   | 1536 bytes   | 8-pins      |

| MC908QT2        | Yes | 1536 bytes   | PDIP, SOIC, |

| MC908QT4        | Yes | 4096 bytes   | and DFN     |

Table 17-1. MC Order Numbers

Temperature and package designators:

$$C = -40 \bullet C$$

to  $+85 \bullet C$

$V = -40 \cdot C \text{ to } +105 \cdot C$

$M = -40 \cdot C \text{ to } + 125 \cdot C$

P = Plastic dual in-line package (PDIP)

DW = Small outline integrated circuit package (SOIC)

DT = Thin shrink small outline package (TSSOP)

FQ = Dual flat no lead (DFN)

Figure 17-1. Device Numbering System

# 17.3 Package Dimensions

Refer to the following pages for detailed package dimensions.

|                                                                                                                                                                                                   | MECHANICAL OUTLINES       | DOCUMENT | NO: 98ASB42431B |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|----------|-----------------|

| Freescale     Semiconductor     Freescale seMiconductor, INC. ALL RIGHTS RESERVED.                                                                                                                | DICTIONARY                | PAGE:    | 648             |

| ELECTRONIC VERSIONS ARE UNCONTROLLED EXCEPT WHEN ACCESSED<br>DIRECTLY FROM THE DOCUMENT CONTROL REPOSITORY, PRINTED<br>VERSIONS ARE UNCONTROLLED EXCEPT WHEN STAWPED "CONTROLLED<br>COPY" IN RED. | DO NOT SCALE THIS DRAWING | REV:     | Т               |

# NOTES:

- 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

- 2. CONTROLLING DIMENSION: INCH.

- 3. DIMENSION TO CENTER OF LEADS WHEN FORMED PARALLEL.

- A DIMENSIONS DOES NOT INCLUDE MOLD FLASH.

- 5. ROUNDED CORNERS OPTIONAL.

- 6. 648-01 THRU -08 OBSOLETE, NEW STANDARD 648-09.

|            | MILLIN                           | IETERS | INC   | HES   |      | MILLIMETERS |        | INCHES |     |

|------------|----------------------------------|--------|-------|-------|------|-------------|--------|--------|-----|

| DIM        | MIN                              | MAX    | MIN   | MAX   | DIM  | MIN         | MAX    | MIN    | MAX |

| А          | 18.80                            | 19.55  | 0.740 | 0.770 |      |             |        |        |     |

| В          | 6.35                             | 6.85   | 0.250 | 0,270 |      |             |        |        |     |

| С          | 3.69                             | 4.44   | 0.145 | 0.175 |      |             |        |        |     |

| D          | 0.39                             | 0.53   | 0.015 | 0.021 |      |             |        |        |     |

| F          | 1.02                             | 1.77   | 0.040 | 0.070 |      |             |        |        |     |

| G          | 2.54                             | BSC    | 0.100 | BSC   |      |             |        |        |     |

| Н          | 1.27                             | BSC    | 0.050 | ) BSC |      |             |        |        |     |

| J          | 0.21                             | 0.38   | 0.008 | 0.015 |      |             |        |        |     |

| K          | 2.80                             | 3.30   | 0.110 | 0.130 |      |             |        |        |     |

| L          | 7.50                             | 7.74   | 0.295 | 0.305 |      |             |        |        |     |

| М          | 0.                               | 10°    | 0.    | 10°   |      |             |        |        |     |

| S          | 0.51                             | 1.01   | 0.020 | 0.040 |      |             |        |        |     |

| TITLE      | TITLE:                           |        |       |       |      | NUMBER: (   | 648-08 |        |     |

| 16 LD PDIP |                                  |        |       |       | STAN | DARD: NON   | -JEDEC |        |     |

|            | PACKAGE CODE: 0006 SHEET: 2 OF 4 |        |       |       |      |             |        | 2 OF 4 |     |