Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | HC08                                                                    |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 8MHz                                                                    |

| Connectivity               | -                                                                       |

| Peripherals                | LVD, POR, PWM                                                           |

| Number of I/O              | 5                                                                       |

| Program Memory Size        | 1.5KB (1.5K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 128 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                             |

| Data Converters            | A/D 4x8b                                                                |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

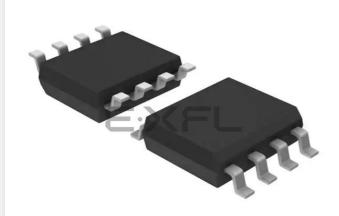

| Package / Case             | 8-SOIC (0.209", 5.30mm Width)                                           |

| Supplier Device Package    | 8-SO                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mchc908qt2mdwer |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

**Revision History**

# **Revision History (Sheet 3 of 3)**

| Date              | Revision<br>Level | Description                                                                                                                                     | Page<br>Number(s)                    |

|-------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

|                   |                   | Reformatted to meet current documentation standards                                                                                             | Throughout                           |

|                   |                   | 6.3.1 BUSCLKX4 — Clarified description of BUSCLKX4                                                                                              | 58                                   |

|                   |                   | Chapter 7 Central Processor Unit (CPU) — In 7.7 Instruction Set Summary:<br>Reworked definitions for STOP instruction<br>Added WAIT instruction | 70<br>71                             |

| November,<br>2004 | 4.0               | 13.8.1 SIM Reset Status Register — Clarified SRSR flag setting                                                                                  | 117                                  |

|                   |                   | 14.9.1 TIM Status and Control Register — Added information to TSTOP note                                                                        | 127                                  |

|                   |                   | 16.8 5-V Oscillator Characteristics — Added values for deviation from trimmed inernal oscillator                                                | 155                                  |

|                   |                   | 16.12 3-V Oscillator Characteristics — Added values for deviation from trimmed inernal oscillator                                               | 158                                  |

|                   |                   | Figure 5-2. Configuration Register 1 (CONFIG1) — Clarified bit definitions for COPRS.                                                           | 54                                   |

| July,             | 5.0               | Chapter 8 External Interrupt (IRQ) — Reworked for clarification.                                                                                | 73                                   |

| 2005              | 5.0               | 11.3.4 RC Oscillator — Improved RC oscillator wording.                                                                                          | 93                                   |

|                   |                   | 12.1 Introduction — Added note pertaining to non-bonded port pins.                                                                              | 97                                   |

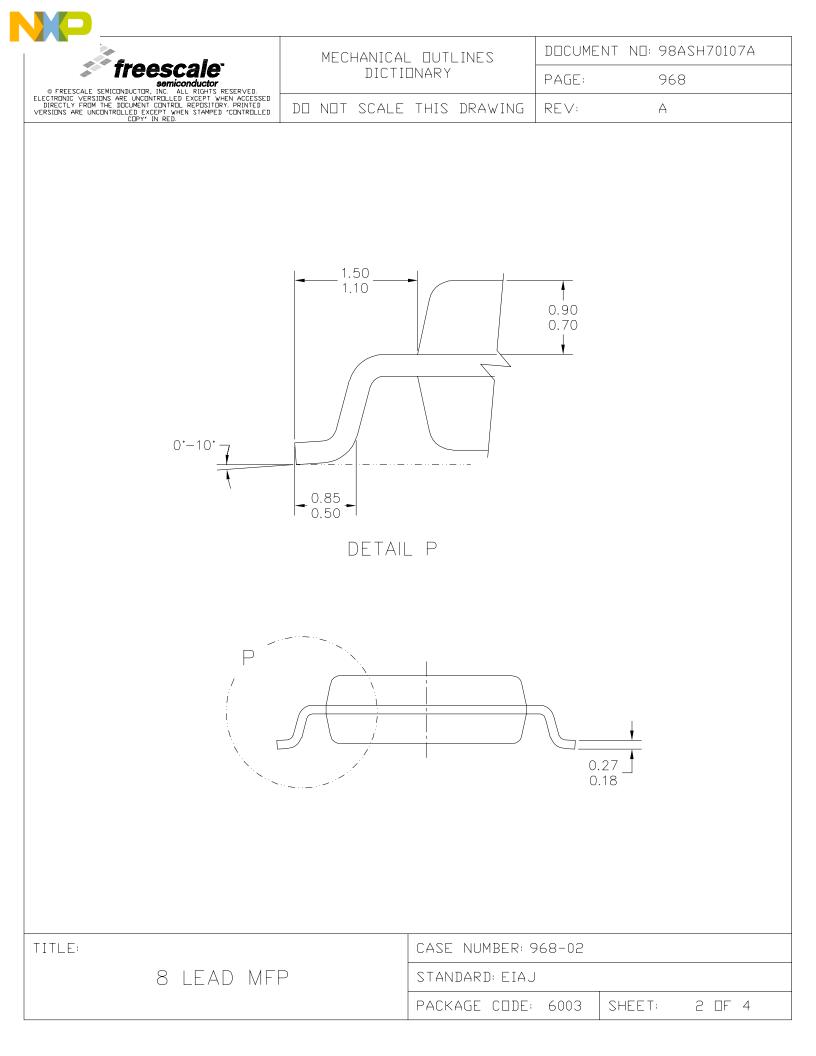

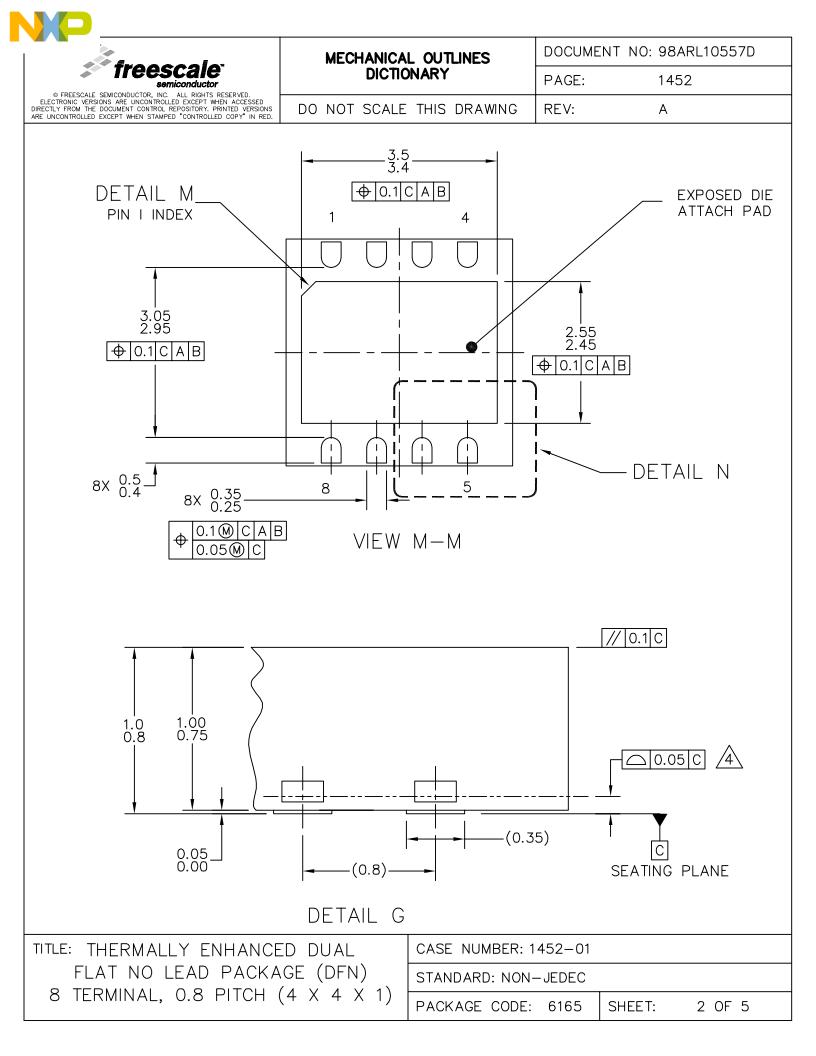

|                   |                   | 17.3 Package Dimensions — Updated package information.                                                                                          | 165                                  |

| March,<br>2010    | 6.0               | Clarify internal oscillator trim register information.                                                                                          | 26, 27, 31,<br>34, 35, 38,<br>91, 96 |

# Chapter 1 General Description

# **1.1 Introduction**

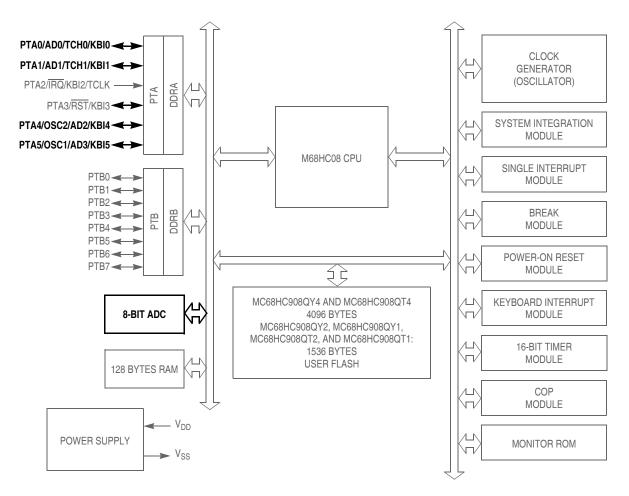

The MC68HC908QY4 is a member of the low-cost, high-performance M68HC08 Family of 8-bit microcontroller units (MCUs). The M68HC08 Family is a Complex Instruction Set Computer (CISC) with a Von Neumann architecture. All MCUs in the family use the enhanced M68HC08 central processor unit (CPU08) and are available with a variety of modules, memory sizes and types, and package types.

| Device       | FLASH<br>Memory Size | Analog-to-Digital<br>Converter | Pin<br>Count |

|--------------|----------------------|--------------------------------|--------------|

| MC68HC908QT1 | 1536 bytes           | —                              | 8 pins       |

| MC68HC908QT2 | 1536 bytes           | 4 ch, 8 bit                    | 8 pins       |

| MC68HC908QT4 | 4096 bytes           | 4 ch, 8 bit                    | 8 pins       |

| MC68HC908QY1 | 1536 bytes           | —                              | 16 pins      |

| MC68HC908QY2 | 1536 bytes           | 4 ch, 8 bit                    | 16 pins      |

| MC68HC908QY4 | 4096 bytes           | 4 ch, 8 bit                    | 16 pins      |

Table 1-1. Summary of Device Variations

# **1.2 Features**

Features include:

- High-performance M68HC08 CPU core

- Fully upward-compatible object code with M68HC05 Family

- 5-V and 3-V operating voltages (V<sub>DD</sub>)

- 8-MHz internal bus operation at 5 V, 4-MHz at 3 V

- Trimmable internal oscillator

- 3.2 MHz internal bus operation

- 8-bit trim capability allows 0.4% accuracy<sup>(1)</sup>

- ± 25% untrimmed

- Auto wakeup from STOP capability

- Configuration (CONFIG) register for MCU configuration options, including:

- Low-voltage inhibit (LVI) trip point

- In-system FLASH programming

- FLASH security<sup>(2)</sup>

<sup>1.</sup> The oscillator frequency is guaranteed to  $\pm 5\%$  over temperature and voltage range after trimming.

No security feature is absolutely secure. However, Freescale's strategy is to make reading or copying the FLASH difficult for unauthorized users.

NP

### Memory

| Addr.                 | Register Name                                        |                  | Bit 7    | 6                                 | 5       | 4                       | 3                | 2        | 1           | Bit 0            |

|-----------------------|------------------------------------------------------|------------------|----------|-----------------------------------|---------|-------------------------|------------------|----------|-------------|------------------|

| \$0006                | Unimplemented                                        |                  |          |                                   |         |                         |                  |          |             |                  |

| ↓<br>\$000A           |                                                      |                  |          |                                   |         |                         |                  |          |             |                  |

| 4000A                 | Unimplemented                                        |                  |          |                                   |         |                         |                  |          |             |                  |

| \$000B                | Port A Input Pullup Enable<br>Register (PTAPUE)      | Read:<br>Write:  | OSC2EN   | 0                                 | PTAPUE5 | PTAPUE4                 | PTAPUE3          | PTAPUE2  | PTAPUE1     | PTAPUE0          |

|                       |                                                      | Reset:           | 0        | 0                                 | 0       | 0                       | 0                | 0        | 0           | 0                |

| \$000C                | Port B Input Pullup Enable<br>Register (PTBPUE)      | Read:<br>Write:  | PTBPUE7  | PTBPUE6                           | PTBPUE5 | PTBPUE4                 | PTBPUE3          | PTBPUE2  | PTBPUE1     | PTBPUE0          |

|                       | See page 102.                                        | Reset:           | 0        | 0                                 | 0       | 0                       | 0                | 0        | 0           | 0                |

| \$000D<br>↓<br>\$0019 | Unimplemented                                        |                  |          |                                   |         |                         |                  |          |             |                  |

|                       | Keykeerd Otatus and                                  | Read:            | 0        | 0                                 | 0       | 0                       | KEYF             | 0        |             |                  |

| \$001A                | Keyboard Status and<br>Control Register (KBSCR)      | Write:           | •        | Ŭ                                 | Ŭ       | Ŭ                       | ILE II           | ACKK     | IMASKK      | MODEK            |

| ,                     | See page 83.                                         | Reset:           | 0        | 0                                 | 0       | 0                       | 0                | 0        | 0           | 0                |

| \$001B                | Keyboard Interrupt<br>Enable Register (KBIER)        | Read:<br>Write:  | 0        | AWUIE                             | KBIE5   | KBIE4                   | KBIE3            | KBIE2    | KBIE1       | KBIE0            |

|                       | See page 84.                                         | Reset:           | 0        | 0                                 | 0       | 0                       | 0                | 0        | 0           | 0                |

| \$001C                | Unimplemented                                        |                  |          |                                   |         |                         |                  |          |             |                  |

|                       |                                                      | 1                |          | -                                 | -       | -                       |                  |          |             | 1                |

| ¢001D                 | IRQ Status and Control                               | Read:            | 0        | 0                                 | 0       | 0                       | IRQF             | 0<br>ACK | IMASK       | MODE             |

| \$001D                | Register (INTSCR)<br>See page 77.                    | Write:<br>Reset: | 0        | 0                                 | 0       | 0                       | 0                | ACK<br>0 | 0           | 0                |

| \$001E                | Configuration Register 2<br>(CONFIG2) <sup>(1)</sup> | Read:<br>Write:  | IRQPUD   | IRQEN                             | R       | OSCOPT1                 | OSCOPT0          | R        | R           | RSTEN            |

| \$001E                | See page 53.                                         | Reset:           | 0        | 0                                 | 0       | 0                       | 0                | 0        | 0           | 0 <sup>(2)</sup> |

|                       |                                                      |                  |          | writable regis<br>eset to 0 by a  |         | reset.<br>et (POR) only |                  |          |             |                  |

| \$001F                | Configuration Register 1<br>(CONFIG1) <sup>(1)</sup> | Read:<br>Write:  | COPRS    | LVISTOP                           | LVIRSTD | LVIPWRD                 | LVI5OR3          | SSREC    | STOP        | COPD             |

|                       | See page 54.                                         | Reset:           | 0        | 0                                 | 0       | 0                       | 0 <sup>(2)</sup> | 0        | 0           | 0                |

|                       |                                                      |                  |          | writable regis<br>reset to 0 by a |         | reset.<br>eset (POR) on | ly.              |          |             |                  |

| \$0020                | \$0020 Register (TSC) W                              | Read:<br>Write:  | TOF<br>0 | TOIE                              | TSTOP   | 0<br>TRST               | 0                | PS2      | PS1         | PS0              |

|                       |                                                      | Reset:           | 0        | 0                                 | 1       | 0                       | 0                | 0        | 0           | 0                |

|                       | TIM Counter Register High                            | Read:            | Bit 15   | Bit 14                            | Bit 13  | Bit 12                  | Bit 11           | Bit 10   | Bit 9       | Bit 8            |

| \$0021                | (TCNTH)<br>See page 128.                             | Write:           |          |                                   |         |                         |                  |          |             |                  |

|                       | 000 paye 120.                                        | Reset:           | 0        | 0<br>Linimalam                    | 0       | 0                       | 0<br>Decented    | 0        | 0<br>Factor | 0                |

|                       |                                                      |                  |          | = Unimplem                        | lentea  | R                       | = Reserved       | U = Unaf | lected      |                  |

Figure 2-2. Control, Status, and Data Registers (Sheet 2 of 5)

#### Input/Output (I/O) Section

| Addr.                 | Register Name                             |                 | Bit 7  | 6      | 5      | 4         | 3          | 2      | 1     | Bit 0 |

|-----------------------|-------------------------------------------|-----------------|--------|--------|--------|-----------|------------|--------|-------|-------|

|                       | FLASH Control Register                    | Read:           | 0      | 0      | 0      | 0         | HVEN       | MASS   | ERASE | PGM   |

| \$FE08                | (FLCR)                                    | Write:          |        |        |        |           |            | MAGO   | LINOL |       |

|                       | See page 34.                              | Reset:          | 0      | 0      | 0      | 0         | 0          | 0      | 0     | 0     |

| \$FE09                | Break Address High<br>Register (BRKH)     | Read:<br>Write: | Bit 15 | Bit 14 | Bit 13 | Bit 12    | Bit 11     | Bit 10 | Bit 9 | Bit 8 |

|                       | See page 136.                             | Reset:          | 0      | 0      | 0      | 0         | 0          | 0      | 0     | 0     |

| \$FE0A                | Break Address low<br>Register (BRKL)      | Read:<br>Write: | Bit 7  | Bit 6  | Bit 5  | Bit 4     | Bit 3      | Bit 2  | Bit 1 | Bit 0 |

|                       | See page 136.                             | Reset:          | 0      | 0      | 0      | 0         | 0          | 0      | 0     | 0     |

|                       | Break Status and Control                  | Read:           | BRKE   | BRKA   | 0      | 0         | 0          | 0      | 0     | 0     |

| \$FE0B                | \$FE0B Register (BRKSCR)<br>See page 136. | Write:          | DAKE   | DHNA   |        |           |            |        |       |       |

|                       |                                           | Reset:          | 0      | 0      | 0      | 0         | 0          | 0      | 0     | 0     |

|                       | LVI Status Register                       | Read:           | LVIOUT | 0      | 0      | 0         | 0          | 0      | 0     | R     |

| \$FE0C                | (LVISR)                                   | Write:          |        |        |        |           |            |        |       |       |

|                       | See page 87.                              | Reset:          | 0      | 0      | 0      | 0         | 0          | 0      | 0     | 0     |

| \$FE0D<br>↓<br>\$FE0F | Reserved for FLASH Test                   |                 | R      | R      | R      | R         | R          | R      | R     | R     |

|                       |                                           | Dood:           |        |        |        |           |            | -      |       |       |

| \$FFBE                | FLASH Block Protect<br>Register (FLBPR)   | Read:<br>Write: | BPR7   | BPR6   | BPR5   | BPR4      | BPR3       | BPR2   | BPR1  | BPR0  |

|                       | See page 39.                              | Reset:          |        |        |        | Unaffecte | d by reset |        |       |       |

| \$FFBF                | Reserved                                  |                 | R      | R      | R      | R         | R          | R      | R     | R     |

| \$FFC0 | Internal Oscillator Trim<br>(Factory Programmed, | Read:<br>Write: | TRIM7               | TRIM6 | TRIM5 | TRIM4 | TRIM3 | TRIM2 | TRIM1 | TRIM0 |

|--------|--------------------------------------------------|-----------------|---------------------|-------|-------|-------|-------|-------|-------|-------|

|        | VDD = 5.0 V)                                     | Reset:          | Unaffected by reset |       |       |       |       |       |       |       |

| \$FFC1 | Internal Oscillator Trim<br>(Factory Programmed, | Read:<br>Write: | TRIM7               | TRIM6 | TRIM5 | TRIM4 | TRIM3 | TRIM2 | TRIM1 | TRIM0 |

|        | VDD = 3.0 V)                                     | Reset:          | Unaffected by reset |       |       |       |       |       |       |       |

Figure 2-2. Control, Status, and Data Registers (Sheet 5 of 5)

#### Analog-to-Digital Converter (ADC)

RST, IRQ: Pins have internal (about 30K Ohms) pull up

PTA[0:5]: High current sink and source capability

PTA[0:5]: Pins have programmable keyboard interrupt and pull up

PTB[0:7]: Not available on 8-pin devices – MC68HC908QT1, MC68HC908QT2, and MC68HC908QT4 (see note in 12.1 Introduction)

ADC: Not available on the MC68HC908QY1 and MC68HC908QT1

## Figure 3-1. Block Diagram Highlighting ADC Block and Pins

Configuration Register (CONFIG)

System Integration Module (SIM)

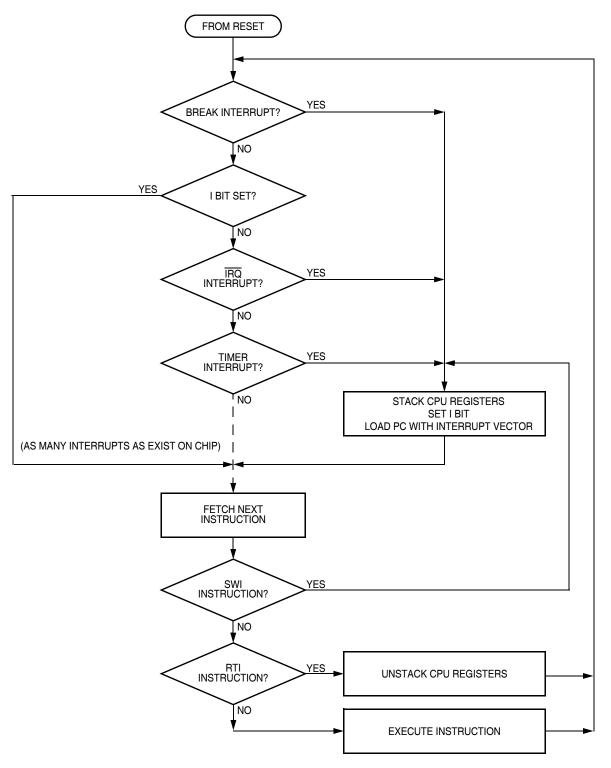

Figure 13-7. Interrupt Processing

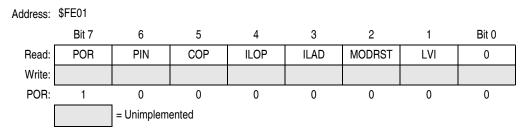

## 13.8.1 SIM Reset Status Register

The SRSR register contains flags that show the source of the last reset. The status register will automatically clear after reading SRSR. A power-on reset sets the POR bit and clears all other bits in the register. All other reset sources set the individual flag bits but do not clear the register. More than one reset source can be flagged at any time depending on the conditions at the time of the internal or external reset. For example, the POR and LVI bit can both be set if the power supply has a slow rise time.

## Figure 13-19. SIM Reset Status Register (SRSR)

### POR — Power-On Reset Bit

- 1 = Last reset caused by POR circuit

- 0 = Read of SRSR

### PIN — External Reset Bit

- 1 = Last reset caused by external reset pin ( $\overline{RST}$ )

- 0 = POR or read of SRSR

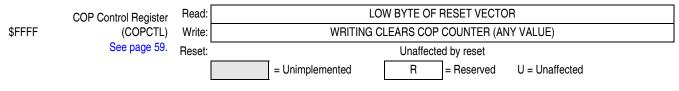

### COP — Computer Operating Properly Reset Bit

- 1 = Last reset caused by COP counter

- 0 = POR or read of SRSR

## ILOP — Illegal Opcode Reset Bit

- 1 = Last reset caused by an illegal opcode

- 0 = POR or read of SRSR

# ILAD — Illegal Address Reset Bit (illegal attempt to fetch an opcode from an unimplemented address)

- 1 = Last reset caused by an opcode fetch from an illegal address

- 0 = POR or read of SRSR

### MODRST — Monitor Mode Entry Module Reset Bit

- 1 = Last reset caused by monitor mode entry when vector locations \$FFFE and \$FFFF are \$FF after POR while  $\overline{IRQ} \neq V_{TST}$

- 0 = POR or read of SRSR

## LVI — Low Voltage Inhibit Reset Bit

- 1 = Last reset caused by LVI circuit

- 0 = POR or read of SRSR

System Integration Module (SIM)

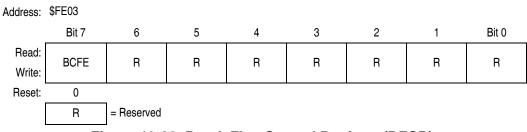

## 13.8.2 Break Flag Control Register

The break control register (BFCR) contains a bit that enables software to clear status bits while the MCU is in a break state.

## Figure 13-20. Break Flag Control Register (BFCR)

## BCFE — Break Clear Flag Enable Bit

This read/write bit enables software to clear status bits by accessing status registers while the MCU is in a break state. To clear status bits during the break state, the BCFE bit must be set.

1 = Status bits clearable during break

0 = Status bits not clearable during break

# Chapter 14 Timer Interface Module (TIM)

# 14.1 Introduction

This section describes the timer interface module (TIM). The TIM is a two-channel timer that provides a timing reference with input capture, output compare, and pulse-width-modulation functions. Figure 14-2 is a block diagram of the TIM.

# 14.2 Features

Features of the TIM include the following:

- Two input capture/output compare channels

- Rising-edge, falling-edge, or any-edge input capture trigger

- Set, clear, or toggle output compare action

- Buffered and unbuffered pulse width modulation (PWM) signal generation

- Programmable TIM clock input

- 7-frequency internal bus clock prescaler selection

- External TIM clock input

- Free-running or modulo up-count operation

- Toggle any channel pin on overflow

- TIM counter stop and reset bits

# 14.3 Pin Name Conventions

The TIM shares two input/output (I/O) pins with two port A I/O pins. The full names of the TIM I/O pins are listed in Table 14-1. The generic pin name appear in the text that follows.

## Table 14-1. Pin Name Conventions

| TIM Generic Pin Names: | TCH0      | TCH1      | TCLK      |  |

|------------------------|-----------|-----------|-----------|--|

| Full TIM Pin Names:    | PTA0/TCH0 | PTA1/TCH1 | PTA2/TCLK |  |

Timer Interface Module (TIM)

# 14.6 Wait Mode

The WAIT instruction puts the MCU in low power-consumption standby mode.

The TIM remains active after the execution of a WAIT instruction. In wait mode the TIM registers are not accessible by the CPU. Any enabled CPU interrupt request from the TIM can bring the MCU out of wait mode.

If TIM functions are not required during wait mode, reduce power consumption by stopping the TIM before executing the WAIT instruction.

# 14.7 TIM During Break Interrupts

A break interrupt stops the TIM counter.

The system integration module (SIM) controls whether status bits in other modules can be cleared during the break state. The BCFE bit in the break flag control register (BFCR) enables software to clear status bits during the break state. See 13.8.2 Break Flag Control Register.

To allow software to clear status bits during a break interrupt, write a 1 to the BCFE bit. If a status bit is cleared during the break state, it remains cleared when the MCU exits the break state.

To protect status bits during the break state, write a 0 to the BCFE bit. With BCFE at 0 (its default state), software can read and write I/O registers during the break state without affecting status bits. Some status bits have a two-step read/write clearing procedure. If software does the first step on such a bit before the break, the bit cannot change during the break state as long as BCFE is at 0. After the break, doing the second step clears the status bit.

# 14.8 Input/Output Signals

Port A shares three of its pins with the TIM. Two TIM channel I/O pins are PTA0/TCH0 and PTA1/TCH1 and an alternate clock source is PTA2/TCLK.

## 14.8.1 TIM Clock Pin (PTA2/TCLK)

PTA2/TCLK is an external clock input that can be the clock source for the TIM counter instead of the prescaled internal bus clock. Select the PTA2/TCLK input by writing 1s to the three prescaler select bits, PS[2–0]. (See 14.9.1 TIM Status and Control Register.) When the PTA2/TCLK pin is the TIM clock input, it is an input regardless of port pin initialization.

## 14.8.2 TIM Channel I/O Pins (PTA0/TCH0 and PTA1/TCH1)

Each channel I/O pin is programmable independently as an input capture pin or an output compare pin. PTA0/TCH0 can be configured as a buffered output compare or buffered PWM pin.

# 14.9 Input/Output Registers

The following I/O registers control and monitor operation of the TIM:

- TIM status and control register (TSC)

- TIM counter registers (TCNTH:TCNTL)

- TIM counter modulo registers (TMODH:TMODL)

- TIM channel status and control registers (TSC0 and TSC1)

- TIM channel registers (TCH0H:TCH0L and TCH1H:TCH1L)

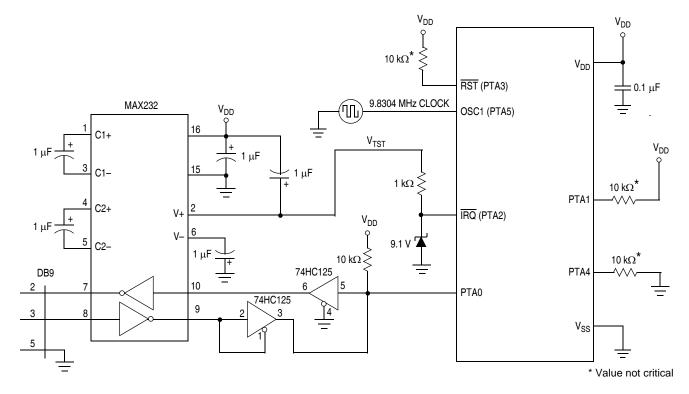

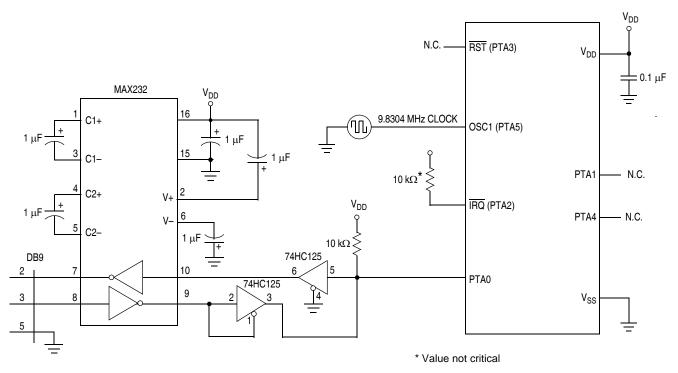

Figure 15-10. Monitor Mode Circuit (External Clock, with High Voltage)

Figure 15-11. Monitor Mode Circuit (External Clock, No High Voltage)

Development Support

| Mode                           | IRQ<br>(PTA2)           | RST<br>(PTA3)   | Reset<br>Vector   | Serial<br>Communi-<br>cation |              | ode<br>ction | СОР      | Co                | mmunicatior<br>Speed | ו            | Comments                           |  |

|--------------------------------|-------------------------|-----------------|-------------------|------------------------------|--------------|--------------|----------|-------------------|----------------------|--------------|------------------------------------|--|

|                                | (FTA2)                  | (FTA3)          | vector            | PTA0                         | PTA1         | PTA4         |          | External<br>Clock | Bus<br>Frequency     | Baud<br>Rate |                                    |  |

| Normal<br>Monitor              | V <sub>TST</sub>        | V <sub>DD</sub> | х                 | 1                            | 1            | 0            | Disabled | 9.8304<br>MHz     | 2.4576<br>MHz        | 9600         | Provide external<br>clock at OSC1. |  |

| Forced                         | V <sub>DD</sub>         | Х               | \$FFFF<br>(blank) | 1                            | Х            | х            | Disabled | 9.8304<br>MHz     | 2.4576<br>MHz        | 9600         | Provide external<br>clock at OSC1. |  |

| Monitor                        | V <sub>SS</sub>         | Х               | \$FFFF<br>(blank) | 1                            | Х            | х            | Disabled | Х                 | 3.2 MHz<br>(Trimmed) | 9600         | Internal clock<br>is active.       |  |

| User                           | Х                       | Х               | Not<br>\$FFFF     | Х                            | Х            | х            | Enabled  | Х                 | Х                    | Х            |                                    |  |

| MON08<br>Function<br>[Pin No.] | V <sub>TST</sub><br>[6] | RST<br>[4]      |                   | COM<br>[8]                   | MOD0<br>[12] | MOD1<br>[10] |          | OSC1<br>[13]      |                      |              |                                    |  |

Table 15-1. Monitor Mode Signal Requirements and Options

1. PTA0 must have a pullup resistor to  $V_{DD}$  in monitor mode.

2. Communication speed in the table is an example to obtain a baud rate of 9600. Baud rate using external oscillator is bus frequency / 256 and baud rate using internal oscillator is bus frequency / 335.

3. External clock is a 9.8304 MHz oscillator on OSC1.

4. X = don't care

5. MON08 pin refers to P&E Microcomputer Systems' MON08-Cyclone 2 by 8-pin connector.

| NC       | 1  | 2  | GND  |

|----------|----|----|------|

| NC       | 3  | 4  | RST  |

| NC       | 5  | 6  | IRQ  |

| NC       | 7  | 8  | PTA0 |

| NC       | 9  | 10 | PTA4 |

| NC       | 11 | 12 | PTA1 |

| OSC1     | 13 | 14 | NC   |

| $V_{DD}$ | 15 | 16 | NC   |

The rising edge of the internal RST signal latches the monitor mode. Once monitor mode is latched, the values on PTA1 and PTA4 pins can be changed.

Once out of reset, the MCU waits for the host to send eight security bytes (see 15.3.2 Security). After the security bytes, the MCU sends a break signal (10 consecutive logic 0s) to the host, indicating that it is ready to receive a command.

## 15.3.1.1 Normal Monitor Mode

RST and OSC1 functions will be active on the PTA3 and PTA5 pins respectively as long as  $V_{TST}$  is applied to the IRQ pin. If the IRQ pin is lowered (no longer  $V_{TST}$ ) then the chip will still be operating in monitor mode, but the pin functions will be determined by the settings in the configuration registers (see Chapter 5 Configuration Register (CONFIG)) when  $V_{TST}$  was lowered. With  $V_{TST}$  lowered, the BIH and BIL instructions will read the IRQ pin state only if IRQEN is set in the CONFIG2 register.

#### Monitor Module (MON)

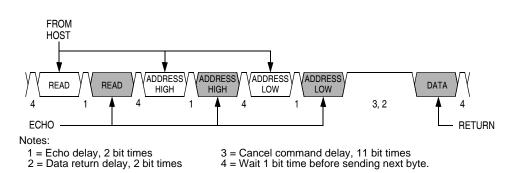

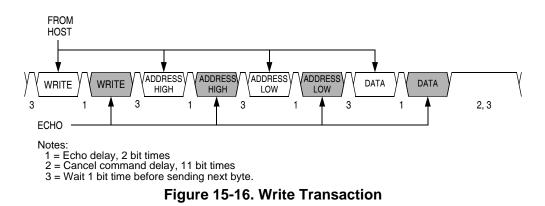

The monitor ROM firmware echoes each received byte back to the PTA0 pin for error checking. An 11-bit delay at the end of each command allows the host to send a break character to cancel the command. A delay of two bit times occurs before each echo and before READ, IREAD, or READSP data is returned. The data returned by a read command appears after the echo of the last byte of the command.

## NOTE

Wait one bit time after each echo before sending the next byte.

Figure 15-15. Read Transaction

A brief description of each monitor mode command is given in Table 15-3 through Table 15-8.

Description Read byte from memory 2-byte address in high-byte:low-byte order Operand **Data Returned** Returns contents of specified address Opcode \$4A **Command Sequence** SENT TO MONITOR ADDRESS ADDRES ADDRESS ADDRES READ READ DATA HIGH LOW HIGH IOW ECHO RETURN

Table 15-3. READ (Read Memory) Command

# 16.7 5-V Control Timing

| Characteristic <sup>(1)</sup>                  | Symbol                              | Min                 | Max | Unit             |

|------------------------------------------------|-------------------------------------|---------------------|-----|------------------|

| Internal operating frequency                   | f <sub>OP</sub> (f <sub>Bus</sub> ) | —                   | 8   | MHz              |

| Internal clock period (1/f <sub>OP</sub> )     | t <sub>cyc</sub>                    | 125                 | _   | ns               |

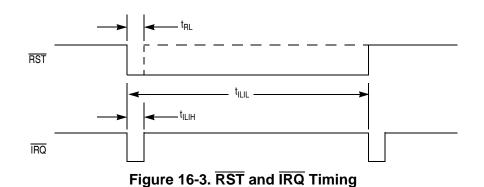

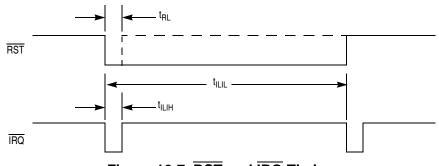

| RST input pulse width low                      | t <sub>RL</sub>                     | 100                 | _   | ns               |

| IRQ interrupt pulse width low (edge-triggered) | t <sub>ILIH</sub>                   | 100                 | _   | ns               |

| IRQ interrupt pulse period                     | t <sub>ILIL</sub>                   | Note <sup>(2)</sup> |     | t <sub>cyc</sub> |

1. V<sub>DD</sub> = 4.5 to 5.5 Vdc, V<sub>SS</sub> = 0 Vdc, T<sub>A</sub> = T<sub>L</sub> to T<sub>H</sub>; timing shown with respect to 20% V<sub>DD</sub> and 70% V<sub>SS</sub>, unless otherwise noted.

2. The minimum period is the number of cycles it takes to execute the interrupt service routine plus 1  $t_{cyc}$ .

# 16.11 3-V Control Timing

| Characteristic <sup>(1)</sup>                  | Symbol                              | Min                 | Max | Unit             |

|------------------------------------------------|-------------------------------------|---------------------|-----|------------------|

| Internal operating frequency                   | f <sub>OP</sub> (f <sub>Bus</sub> ) | —                   | 4   | MHz              |

| Internal clock period (1/f <sub>OP</sub> )     | t <sub>cyc</sub>                    | 250                 | _   | ns               |

| RST input pulse width low                      | t <sub>RL</sub>                     | 200                 |     | ns               |

| IRQ interrupt pulse width low (edge-triggered) | t <sub>ILIH</sub>                   | 200                 | _   | ns               |

| IRQ interrupt pulse period                     | t <sub>ILIL</sub>                   | Note <sup>(2)</sup> |     | t <sub>cyc</sub> |

1. V<sub>DD</sub> = 2.7 to 3.3 Vdc, V<sub>SS</sub> = 0 Vdc, T<sub>A</sub> = T<sub>L</sub> to T<sub>H</sub>; timing shown with respect to 20% V<sub>DD</sub> and 70% V<sub>DD</sub>, unless otherwise noted.

2. The minimum period is the number of cycles it takes to execute the interrupt service routine plus 1  $t_{cyc}$ .

Figure 16-7. RST and IRQ Timing

**Electrical Specifications**

# 16.12 3-V Oscillator Characteristics

| Characteristic                                                                                                                                                                               | Symbol               | Min | Тур                | Max  | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----|--------------------|------|------|

| Internal oscillator frequency <sup>(1)</sup>                                                                                                                                                 | fintclk              | —   | 12.8               | —    | MHz  |

| Deviation from trimmed Internal oscillator $^{(2)(3)}$<br>12.8 MHz, fixed voltage, fixed temp<br>12.8 MHz, V <sub>DD</sub> ± 10%, 0 to 70°C<br>12.8 MHz, V <sub>DD</sub> ± 10%, -40 to 125°C | ACCINT               |     | ± 0.4<br>± 2<br>—  | <br> | %    |

| Crystal frequency, XTALCLK <sup>(1)</sup>                                                                                                                                                    | foscxclk             | 1   | —                  | 16   | MHz  |

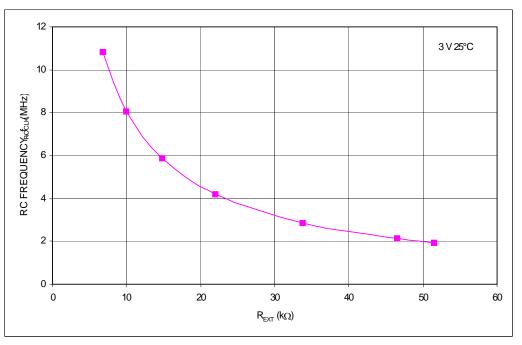

| External RC oscillator frequency, RCCLK (1)                                                                                                                                                  | f <sub>RCCLK</sub>   | 2   | —                  | 10   | MHz  |

| External clock reference frequency <sup>(1) (4)</sup>                                                                                                                                        | f <sub>OSCXCLK</sub> | dc  | —                  | 16   | MHz  |

| Crystal load capacitance <sup>(5)</sup>                                                                                                                                                      | CL                   | —   | 20                 | —    | pF   |

| Crystal fixed capacitance <sup>(3)</sup>                                                                                                                                                     | C <sub>1</sub>       | —   | 2 x C <sub>L</sub> | —    | —    |

| Crystal tuning capacitance <sup>(3)</sup>                                                                                                                                                    | C <sub>2</sub>       | —   | 2 x C <sub>L</sub> | —    | —    |

| Feedback bias resistor                                                                                                                                                                       | R <sub>B</sub>       | 0.5 | 1                  | 10   | MΩ   |

| RC oscillator external resistor                                                                                                                                                              | R <sub>EXT</sub>     | S   | See Figure 16-     | 8    | —    |

| Crystal series damping resistor<br>$f_{OSCXCLK} = 1 MHz$<br>$f_{OSCXCLK} = 4 MHz$<br>$f_{OSCXCLK} = > 8 MHz$                                                                                 | R <sub>S</sub>       |     | 10<br>5<br>0       |      | kΩ   |

Bus frequency, f<sub>OP</sub>, is oscillator frequency divided by 4.

Deviation values assumes trimming @25•C and midpoint of voltage range.

Values are based on characterization results, not tested in production.

4. No more than 10% duty cycle deviation from 50%

5. Consult crystal vendor data sheet

Figure 16-8. RC versus Frequency (3 Volts @ 25•C)