Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                    |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | HC08                                                                   |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 8MHz                                                                   |

| Connectivity               | -                                                                      |

| Peripherals                | LVD, POR, PWM                                                          |

| Number of I/O              | 13                                                                     |

| Program Memory Size        | 1.5KB (1.5K x 8)                                                       |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 128 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                            |

| Data Converters            | -                                                                      |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 16-SOIC (0.295", 7.50mm Width)                                         |

| Supplier Device Package    | 16-SOIC                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mchc908qy1cdwe |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Chapter 7 Central Processor Unit (CPU)

| 7.1   | Introduction                | 61        |

|-------|-----------------------------|-----------|

| 7.2   | Features                    | 61        |

| 7.3   | CPU Registers               | 61        |

| 7.3.1 | Accumulator                 |           |

| 7.3.2 | Index Register              | 62        |

| 7.3.3 | Stack Pointer               |           |

| 7.3.4 | Program Counter             | 63        |

| 7.3.5 | Condition Code Register     | <b>64</b> |

| 7.4   | Arithmetic/Logic Unit (ALU) | <b>65</b> |

| 7.5   | Low-Power Modes             |           |

| 7.5.1 | Wait Mode                   | 65        |

| 7.5.2 | Stop Mode                   | 65        |

| 7.6   | CPU During Break Interrupts | 65        |

| 7.7   | Instruction Set Summary     | 66        |

| 7.8   | Opcode Map                  | 71        |

## Chapter 8 External Interrupt (IRQ)

| 8.1   | Introduction                       | 73 |

|-------|------------------------------------|----|

| 8.2   | Features                           | 73 |

| 8.3   | Functional Description             |    |

| 8.3.1 | MODE = 1                           |    |

| 8.3.2 | MODE = 0                           | 75 |

| 8.4   | Interrupts                         | 76 |

| 8.5   | Low-Power Modes                    |    |

| 8.5.1 | Wait Mode                          |    |

| 8.5.2 | Stop Mode                          | 76 |

| 8.6   | IRQ Module During Break Interrupts | 76 |

| 8.7   | I/O Signals                        |    |

| 8.7.1 | IRQ Input Pins (IRQ)               | 77 |

| 8.8   | Registers                          | 77 |

## Chapter 9 Keyboard Interrupt Module (KBI)

| 9.1 | Introduction                            | 79 |

|-----|-----------------------------------------|----|

| 9.2 | Features                                | 79 |

|     | Functional Description                  |    |

|     | Keyboard Operation                      |    |

|     | Keyboard Initialization                 | 32 |

| 9.4 | Wait Mode                               | 32 |

| 9.5 | Stop Mode                               | 32 |

| 9.6 | Keyboard Module During Break Interrupts | 32 |

#### General Description

- On-chip in-application programmable FLASH memory (with internal program/erase voltage generation)

- MC68HC908QY4 and MC68HC908QT4 4096 bytes

- MC68HC908QY2, MC68HC908QY1, MC68HC908QT2, and MC68HC908QT1 1536 bytes

- 128 bytes of on-chip random-access memory (RAM)

- 2-channel, 16-bit timer interface module (TIM)

- 4-channel, 8-bit analog-to-digital converter (ADC) on MC68HC908QY2, MC68HC908QY4, MC68HC908QT2, and MC68HC908QT4

- 5 or 13 bidirectional input/output (I/O) lines and one input only:

- Six shared with keyboard interrupt function and ADC

- Two shared with timer channels

- One shared with external interrupt (IRQ)

- Eight extra I/O lines on 16-pin package only

- High current sink/source capability on all port pins

- Selectable pullups on all ports, selectable on an individual bit basis

- Three-state ability on all port pins

- 6-bit keyboard interrupt with wakeup feature (KBI)

- Low-voltage inhibit (LVI) module features:

- Software selectable trip point in CONFIG register

- System protection features:

- Computer operating properly (COP) watchdog

- Low-voltage detection with reset

- Illegal opcode detection with reset

- Illegal address detection with reset

- External asynchronous interrupt pin with internal pullup (IRQ) shared with general-purpose input pin

- Master asynchronous reset pin (RST) shared with general-purpose input/output (I/O) pin

- Power-on reset

- Internal pullups on IRQ and RST to reduce external components

- Memory mapped I/O registers

- Power saving stop and wait modes

- MC68HC908QY4, MC68HC908QY2, and MC68HC908QY1 are available in these packages:

- 16-pin plastic dual in-line package (PDIP)

- 16-pin small outline integrated circuit (SOIC) package

- 16-pin thin shrink small outline package (TSSOP)

- MC68HC908QT4, MC68HC908QT2, and MC68HC908QT1 are available in these packages:

- 8-pin PDIP

- 8-pin SOIC

- 8-pin dual flat no lead (DFN) package

# **1.6 Pin Function Priority**

Table 1-3 is meant to resolve the priority if multiple functions are enabled on a single pin.

NOTE

Upon reset all pins come up as input ports regardless of the priority table.

| Pin Name | Highest-to-Lowest Priority Sequence                                                             |

|----------|-------------------------------------------------------------------------------------------------|

| PTA0     | $AD0 \rightarrow TCH0 \rightarrow KBI0 \rightarrow PTA0$                                        |

| PTA1     | $AD1 \rightarrow TCH1 \rightarrow KBI1 \rightarrow PTA1$                                        |

| PTA2     | $\overline{\text{IRQ}} \rightarrow \text{KBI2} \rightarrow \text{TCLK} \rightarrow \text{PTA2}$ |

| PTA3     | $\overline{\text{RST}} \rightarrow \text{KBI3} \rightarrow \text{PTA3}$                         |

| PTA4     | $OSC2 \rightarrow AD2 \rightarrow KBI4 \rightarrow PTA4$                                        |

| PTA5     | $OSC1 \rightarrow AD3 \rightarrow KBI5 \rightarrow PTA5$                                        |

## Table 1-3. Function Priority in Shared Pins

NP

#### Memory

| Addr.                 | Register Name                                        |                  | Bit 7    | 6                                 | 5       | 4                       | 3                | 2        | 1           | Bit 0            |

|-----------------------|------------------------------------------------------|------------------|----------|-----------------------------------|---------|-------------------------|------------------|----------|-------------|------------------|

| \$0006                | Unimplemented                                        |                  |          |                                   |         |                         |                  |          |             |                  |

| ↓<br>\$000A           |                                                      |                  |          |                                   |         |                         |                  |          |             |                  |

| 4000A                 | Unimplemented                                        |                  |          |                                   |         |                         |                  |          |             |                  |

| \$000B                | Port A Input Pullup Enable<br>Register (PTAPUE)      | Read:<br>Write:  | OSC2EN   | 0                                 | PTAPUE5 | PTAPUE4                 | PTAPUE3          | PTAPUE2  | PTAPUE1     | PTAPUE0          |

|                       | See page 99.                                         | Reset:           | 0        | 0                                 | 0       | 0                       | 0                | 0        | 0           | 0                |

| \$000C                | Port B Input Pullup Enable<br>Register (PTBPUE)      | Read:<br>Write:  | PTBPUE7  | PTBPUE6                           | PTBPUE5 | PTBPUE4                 | PTBPUE3          | PTBPUE2  | PTBPUE1     | PTBPUE0          |

|                       | See page 102.                                        | Reset:           | 0        | 0                                 | 0       | 0                       | 0                | 0        | 0           | 0                |

| \$000D<br>↓<br>\$0019 | Unimplemented                                        |                  |          |                                   |         |                         |                  |          |             |                  |

|                       | Keykeerd Otatus and                                  | Read:            | 0        | 0                                 | 0       | 0                       | KEYF             | 0        |             |                  |

| \$001A                | Keyboard Status and<br>Control Register (KBSCR)      | Write:           | •        | Ŭ                                 | Ŭ       | Ŭ                       | ILE II           | ACKK     | IMASKK      | MODEK            |

| ,                     | See page 83.                                         | Reset:           | 0        | 0                                 | 0       | 0                       | 0                | 0        | 0           | 0                |

| \$001B                | Keyboard Interrupt<br>Enable Register (KBIER)        | Read:<br>Write:  | 0        | AWUIE                             | KBIE5   | KBIE4                   | KBIE3            | KBIE2    | KBIE1       | KBIE0            |

|                       | See page 84.                                         | Reset:           | 0        | 0                                 | 0       | 0                       | 0                | 0        | 0           | 0                |

| \$001C                | Unimplemented                                        |                  |          |                                   |         |                         |                  |          |             |                  |

|                       |                                                      | 1                |          | -                                 | -       | -                       |                  |          | [           | ]                |

| ¢001D                 | IRQ Status and Control                               | Read:            | 0        | 0                                 | 0       | 0                       | IRQF             | 0<br>ACK | IMASK       | MODE             |

| \$001D                | Register (INTSCR)<br>See page 77.                    | Write:<br>Reset: | 0        | 0                                 | 0       | 0                       | 0                | ACK<br>0 | 0           | 0                |

| \$001E                | Configuration Register 2<br>(CONFIG2) <sup>(1)</sup> | Read:<br>Write:  | IRQPUD   | IRQEN                             | R       | OSCOPT1                 | OSCOPT0          | R        | R           | RSTEN            |

| \$001E                | See page 53.                                         | Reset:           | 0        | 0                                 | 0       | 0                       | 0                | 0        | 0           | 0 <sup>(2)</sup> |

|                       |                                                      |                  |          | writable regis<br>eset to 0 by a  |         | reset.<br>et (POR) only | <b>.</b>         |          |             |                  |

| \$001F                | Configuration Register 1<br>(CONFIG1) <sup>(1)</sup> | Read:<br>Write:  | COPRS    | LVISTOP                           | LVIRSTD | LVIPWRD                 | LVI5OR3          | SSREC    | STOP        | COPD             |

|                       | See page 54.                                         | Reset:           | 0        | 0                                 | 0       | 0                       | 0 <sup>(2)</sup> | 0        | 0           | 0                |

|                       |                                                      |                  |          | writable regis<br>reset to 0 by a |         | reset.<br>eset (POR) on | ly.              |          |             |                  |

| \$0020                | TIM Status and Control<br>Register (TSC)             | Read:<br>Write:  | TOF<br>0 | TOIE                              | TSTOP   | 0<br>TRST               | 0                | PS2      | PS1         | PS0              |

|                       | See page 127.                                        | Reset:           | 0        | 0                                 | 1       | 0                       | 0                | 0        | 0           | 0                |

|                       | TIM Counter Register High                            | Read:            | Bit 15   | Bit 14                            | Bit 13  | Bit 12                  | Bit 11           | Bit 10   | Bit 9       | Bit 8            |

| \$0021                | (TCNTH)<br>See page 128.                             | Write:           |          |                                   |         |                         |                  |          |             |                  |

|                       | 000 paye 120.                                        | Reset:           | 0        | 0<br>Linimalam                    | 0       | 0                       | 0<br>Decented    | 0        | 0<br>factod | 0                |

|                       |                                                      |                  |          | = Unimplem                        | lentea  | R                       | = Reserved       | U = Unaf | ieclea      |                  |

Figure 2-2. Control, Status, and Data Registers (Sheet 2 of 5)

MC68HC908QY/QT Family Data Sheet, Rev. 6

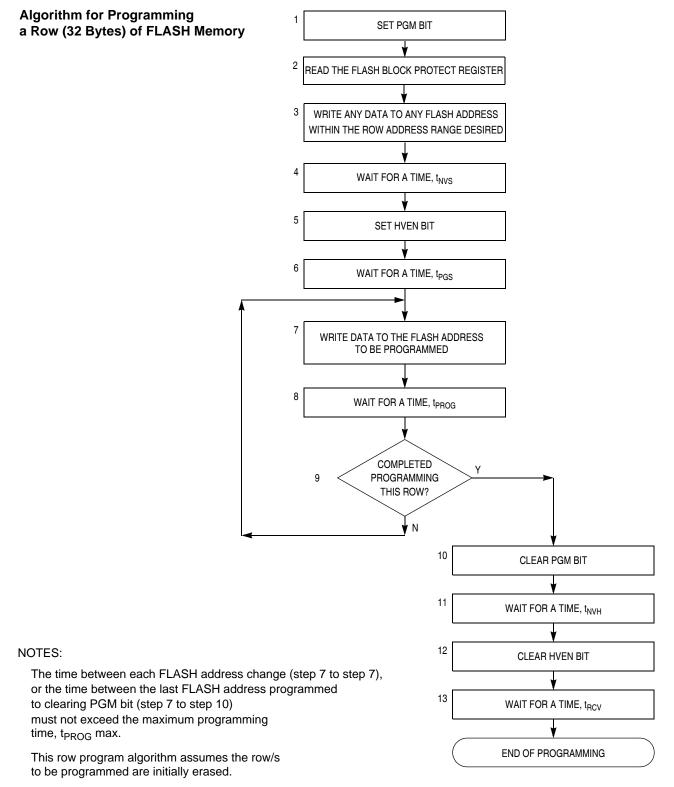

#### FLASH Memory (FLASH)

MC68HC908QY/QT Family Data Sheet, Rev. 6

#### **Configuration Register (CONFIG)**

#### IRQPUD — IRQ Pin Pullup Control Bit

- 1 = Internal pullup is disconnected

- 0 = Internal pullup is connected between  $\overline{IRQ}$  pin and  $V_{DD}$

#### IRQEN — IRQ Pin Function Selection Bit

- 1 = Interrupt request function active in pin

- 0 = Interrupt request function inactive in pin

#### OSCOPT1 and OSCOPT0 — Selection Bits for Oscillator Option

- (0, 0) Internal oscillator

- (0, 1) External oscillator

- (1, 0) External RC oscillator

- (1, 1) External XTAL oscillator

### **RSTEN** — **RST** Pin Function Selection

- 1 = Reset function active in pin

- 0 =Reset function inactive in pin

#### NOTE

The RSTEN bit is cleared by a power-on reset (POR) only. Other resets will leave this bit unaffected.

Address: \$001F

|                 | Bit 7 | 6       | 5       | 4       | 3       | 2     | 1    | Bit 0 |

|-----------------|-------|---------|---------|---------|---------|-------|------|-------|

| Read:<br>Write: | COPRS | LVISTOP | LVIRSTD | LVIPWRD | LVI5OR3 | SSREC | STOP | COPD  |

| Reset:          | 0     | 0       | 0       | 0       | U       | 0     | 0    | 0     |

| POR:            | 0     | 0       | 0       | 0       | 0       | 0     | 0    | 0     |

|                 |       |         |         |         |         |       |      |       |

U = Unaffected

#### Figure 5-2. Configuration Register 1 (CONFIG1)

#### COPRS (Out of STOP Mode) — COP Reset Period Selection Bit

- 1 = COP reset short cycle = 8176 × BUSCLKX4

- $0 = COP reset long cycle = 262,128 \times BUSCLKX4$

#### COPRS (In STOP Mode) — Auto Wakeup Period Selection Bit

- 1 = Auto wakeup short cycle =  $512 \times INTRCOSC$

- 0 = Auto wakeup long cycle =  $16,384 \times$  INTRCOSC

#### LVISTOP — LVI Enable in Stop Mode Bit

When the LVIPWRD bit is clear, setting the LVISTOP bit enables the LVI to operate during stop mode. Reset clears LVISTOP.

1 = LVI enabled during stop mode

0 = LVI disabled during stop mode

#### LVIRSTD — LVI Reset Disable Bit

LVIRSTD disables the reset signal from the LVI module.

1 = LVI module resets disabled

0 = LVI module resets enabled

# Chapter 7 Central Processor Unit (CPU)

# 7.1 Introduction

The M68HC08 CPU (central processor unit) is an enhanced and fully object-code-compatible version of the M68HC05 CPU. The *CPU08 Reference Manual* (document order number CPU08RM/AD) contains a description of the CPU instruction set, addressing modes, and architecture.

# 7.2 Features

Features of the CPU include:

- Object code fully upward-compatible with M68HC05 Family

- 16-bit stack pointer with stack manipulation instructions

- 16-bit index register with x-register manipulation instructions

- 8-MHz CPU internal bus frequency

- 64-Kbyte program/data memory space

- 16 addressing modes

- Memory-to-memory data moves without using accumulator

- Fast 8-bit by 8-bit multiply and 16-bit by 8-bit divide instructions

- Enhanced binary-coded decimal (BCD) data handling

- Modular architecture with expandable internal bus definition for extension of addressing range beyond 64 Kbytes

- Low-power stop and wait modes

# 7.3 CPU Registers

Figure 7-1 shows the five CPU registers. CPU registers are not part of the memory map.

External Interrupt (IRQ)

#### **Functional Description**

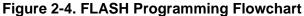

#### Figure 9-2. Keyboard Interrupt Block Diagram

If the MODEK bit is set, the keyboard interrupt inputs are both falling edge and low-level sensitive, and both of the following actions must occur to clear a keyboard interrupt request:

- Vector fetch or software clear A vector fetch generates an interrupt acknowledge signal to clear the interrupt request. Software may generate the interrupt acknowledge signal by writing a 1 to the ACKK bit in the keyboard status and control register (KBSCR). The ACKK bit is useful in applications that poll the keyboard interrupt inputs and require software to clear the keyboard interrupt request. Writing to the ACKK bit prior to leaving an interrupt service routine can also prevent spurious interrupts due to noise. Setting ACKK does not affect subsequent transitions on the keyboard interrupt inputs. A falling edge that occurs after writing to the ACKK bit latches another interrupt request. If the keyboard interrupt mask bit, IMASKK, is clear, the central processor unit (CPU) loads the program counter with the vector address at locations \$FFE0 and \$FFE1.

- Return of all enabled keyboard interrupt inputs to logic 1 As long as any enabled keyboard interrupt pin is at logic 0, the keyboard interrupt remains set. The auto wakeup interrupt input, AWUIREQ, will be cleared only by writing to ACKK bit in KBSCR or reset.

The vector fetch or software clear and the return of all enabled keyboard interrupt pins to logic 1 may occur in any order.

If the MODEK bit is clear, the keyboard interrupt pin is falling-edge sensitive only. With MODEK clear, a vector fetch or software clear immediately clears the keyboard interrupt request.

Reset clears the keyboard interrupt request and the MODEK bit, clearing the interrupt request even if a keyboard interrupt input stays at logic 0.

The keyboard flag bit (KEYF) in the keyboard status and control register can be used to see if a pending interrupt exists. The KEYF bit is not affected by the keyboard interrupt mask bit (IMASKK) which makes it useful in applications where polling is preferred.

#### Low-Voltage Inhibit (LVI)

$V_{TRIPF}$ . Setting the LVI enable in stop mode bit, LVISTOP, enables the LVI to operate in stop mode. Setting the LVI 5-V or 3-V trip point bit, LVI5OR3, enables the trip point voltage,  $V_{TRIPF}$ , to be configured for 5-V operation. Clearing the LVI5OR3 bit enables the trip point voltage,  $V_{TRIPF}$ , to be configured for 3-V operation. The actual trip thresholds are specified in 16.5 5-V DC Electrical Characteristics and 16.9 3-V DC Electrical Characteristics.

### NOTE

After a power-on reset, the LVI's default mode of operation is 3 volts. If a 5-V system is used, the user must set the LVI5OR3 bit to raise the trip point to 5-V operation.

If the user requires 5-V mode and sets the LVI5OR3 bit after power-on reset while the V<sub>DD</sub> supply is not above the V<sub>TRIPR</sub> for 5-V mode, the microcontroller unit (MCU) will immediately go into reset. The next time the LVI releases the reset, the supply will be above the V<sub>TRIPR</sub> for 5-V mode.

Once an LVI reset occurs, the MCU remains in reset until  $V_{DD}$  rises above a voltage,  $V_{TRIPR}$ , which causes the MCU to exit reset. See Chapter 13 System Integration Module (SIM) for the reset recovery sequence.

The output of the comparator controls the state of the LVIOUT flag in the LVI status register (LVISR) and can be used for polling LVI operation when the LVI reset is disabled.

## 10.3.1 Polled LVI Operation

In applications that can operate at  $V_{DD}$  levels below the  $V_{TRIPF}$  level, software can monitor  $V_{DD}$  by polling the LVIOUT bit. In the configuration register, the LVIPWRD bit must be cleared to enable the LVI module, and the LVIRSTD bit must be at set to disable LVI resets.

### 10.3.2 Forced Reset Operation

In applications that require  $V_{DD}$  to remain above the  $V_{TRIPF}$  level, enabling LVI resets allows the LVI module to reset the MCU when  $V_{DD}$  falls below the  $V_{TRIPF}$  level. In the configuration register, the LVIPWRD and LVIRSTD bits must be cleared to enable the LVI module and to enable LVI resets.

### 10.3.3 Voltage Hysteresis Protection

Once the LVI has triggered (by having  $V_{DD}$  fall below  $V_{TRIPF}$ ), the LVI will maintain a reset condition until  $V_{DD}$  rises above the rising trip point voltage,  $V_{TRIPR}$ . This prevents a condition in which the MCU is continually entering and exiting reset if  $V_{DD}$  is approximately equal to  $V_{TRIPF}$ .  $V_{TRIPR}$  is greater than  $V_{TRIPF}$  by the hysteresis voltage,  $V_{HYS}$ .

### 10.3.4 LVI Trip Selection

The LVI5OR3 bit in the configuration register selects whether the LVI is configured for 5-V or 3-V protection.

#### NOTE

The microcontroller is guaranteed to operate at a minimum supply voltage. The trip point ( $V_{TRIPF}$  [5 V] or  $V_{TRIPF}$  [3 V]) may be lower than this. See 16.5 5-V DC Electrical Characteristics and 16.9 3-V DC Electrical Characteristics for the actual trip point voltages.

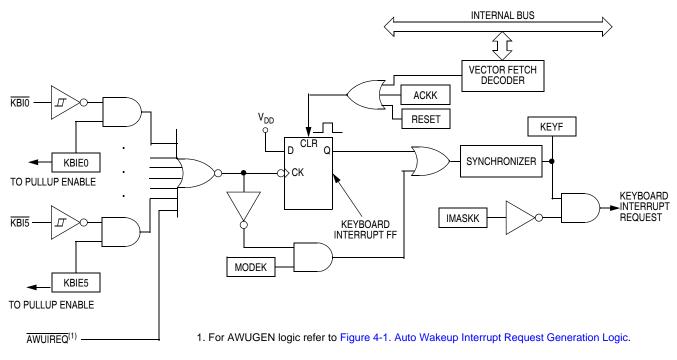

## 11.3.4 RC Oscillator

The RC oscillator circuit is designed for use with an external resistor ( $R_{EXT}$ ) to provide a clock source with a tolerance within 25% of the expected frequency. See Figure 11-3.

The capacitor (C) for the RC oscillator is internal to the MCU. The R<sub>EXT</sub> value must have a tolerance of 1% or less to minimize its effect on the frequency.

In this configuration, the OSC2 pin can be left in the reset state as PTA4. Or, the OSC2EN bit in the port A pullup enable register can be set to enable the OSC2 output function on the pin. Enabling the OSC2 output slightly increases the external RC oscillator frequency, f<sub>RCCLK</sub>.

See Chapter 16 Electrical Specifications for component value requirements.

### Figure 11-3. RC Oscillator External Connections

## **11.4 Oscillator Module Signals**

The following paragraphs describe the signals that are inputs to and outputs from the oscillator module.

### 11.4.1 Crystal Amplifier Input Pin (OSC1)

The OSC1 pin is either an input to the crystal oscillator amplifier, an input to the RC oscillator circuit, or an external clock source.

For the internal oscillator configuration, the OSC1 pin can assume other functions according to Table 1-3. Function Priority in Shared Pins.

Oscillator Module (OSC)

## 11.4.2 Crystal Amplifier Output Pin (OSC2/PTA4/BUSCLKX4)

For the XTAL oscillator device, the OSC2 pin is the crystal oscillator inverting amplifier output.

For the external clock option, the OSC2 pin is dedicated to the PTA4 I/O function. The OSC2EN bit has no effect.

For the internal oscillator or RC oscillator options, the OSC2 pin can assume other functions according to Table 1-3. Function Priority in Shared Pins, or the output of the oscillator clock (BUSCLKX4).

| Option                                  | OSC2 Pin Function                                                                                  |

|-----------------------------------------|----------------------------------------------------------------------------------------------------|

| XTAL oscillator                         | Inverting OSC1                                                                                     |

| External clock                          | PTA4 I/O                                                                                           |

| Internal oscillator or<br>RC oscillator | Controlled by OSC2EN bit in PTAPUE register<br>OSC2EN = 0: PTA4 I/O<br>OSC2EN = 1: BUSCLKX4 output |

Table 11-1. OSC2 Pin Function

## 11.4.3 Oscillator Enable Signal (SIMOSCEN)

The SIMOSCEN signal comes from the system integration module (SIM) and enables/disables either the XTAL oscillator circuit, the RC oscillator, or the internal oscillator.

## 11.4.4 XTAL Oscillator Clock (XTALCLK)

XTALCLK is the XTAL oscillator output signal. It runs at the full speed of the crystal ( $f_{XCLK}$ ) and comes directly from the crystal oscillator circuit. Figure 11-2 shows only the logical relation of XTALCLK to OSC1 and OSC2 and may not represent the actual circuitry. The duty cycle of XTALCLK is unknown and may depend on the crystal and other external factors. Also, the frequency and amplitude of XTALCLK can be unstable at start up.

## 11.4.5 RC Oscillator Clock (RCCLK)

RCCLK is the RC oscillator output signal. Its frequency is directly proportional to the time constant of external R and internal C. Figure 11-3 shows only the logical relation of RCCLK to OSC1 and may not represent the actual circuitry.

## 11.4.6 Internal Oscillator Clock (INTCLK)

INTCLK is the internal oscillator output signal. Its nominal frequency is fixed to 12.8 MHz, but it can be also trimmed using the oscillator trimming feature of the OSCTRIM register (see 11.3.1.1 Internal Oscillator Trimming).

## 11.4.7 Oscillator Out 2 (BUSCLKX4)

BUSCLKX4 is the same as the input clock (XTALCLK, RCCLK, or INTCLK). This signal is driven to the SIM module and is used to determine the COP cycles.

### 11.4.8 Oscillator Out (BUSCLKX2)

The frequency of this signal is equal to half of the BUSCLKX4, this signal is driven to the SIM for generation of the bus clocks used by the CPU and other modules on the MCU. BUSCLKX2 will be divided

Oscillator Module (OSC)

## 11.8.1 Oscillator Status Register

The oscillator status register (OSCSTAT) contains the bits for switching from internal to external clock sources.

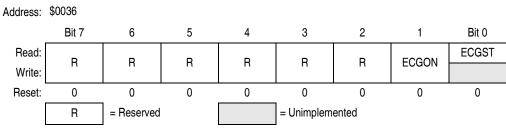

Figure 11-4. Oscillator Status Register (OSCSTAT)

### ECGON — External Clock Generator On Bit

This read/write bit enables external clock generator, so that the switching process can be initiated. This bit is forced low during reset. This bit is ignored in monitor mode with the internal oscillator bypassed, PTM or CTM mode.

1 = External clock generator enabled

0 = External clock generator disabled

### ECGST — External Clock Status Bit

This read-only bit indicates whether or not an external clock source is engaged to drive the system clock.

1 = An external clock source engaged

0 = An external clock source disengaged

## 11.8.2 Oscillator Trim Register (OSCTRIM)

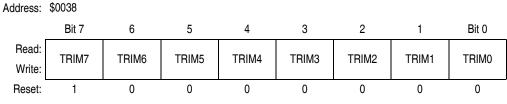

Figure 11-5. Oscillator Trim Register (OSCTRIM)

### TRIM7–TRIM0 — Internal Oscillator Trim Factor Bits

These read/write bits change the size of the internal capacitor used by the internal oscillator. By measuring the period of the internal clock and adjusting this factor accordingly, the frequency of the internal clock can be fine tuned. Increasing (decreasing) this factor by one increases (decreases) the period by approximately 0.2% of the untrimmed period (the period for TRIM = \$80). The trimmed frequency is guaranteed not to vary by more than  $\pm 5\%$  over the full specified range of temperature and voltage. The reset value is \$80, which sets the frequency to 12.8 MHz (3.2 MHz bus speed)  $\pm 25\%$ .

Applications using the internal oscillator should copy the internal oscillator trim value at location \$FFC0 or \$FFC1 into this register to trim the clock source.

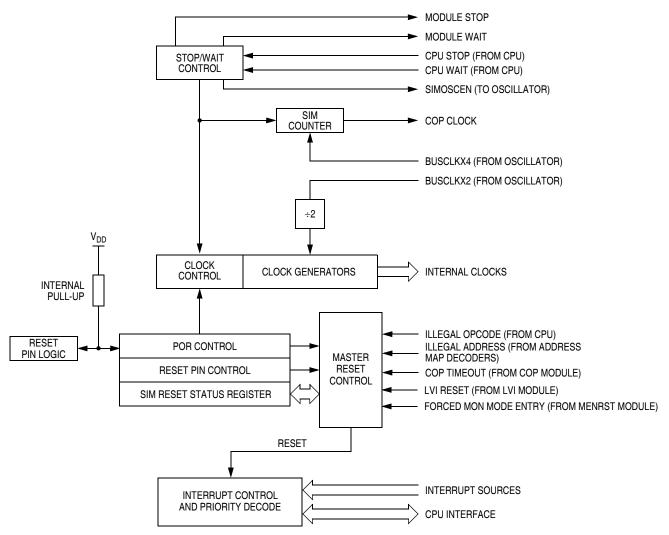

#### System Integration Module (SIM)

Figure 13-1. SIM Block Diagram

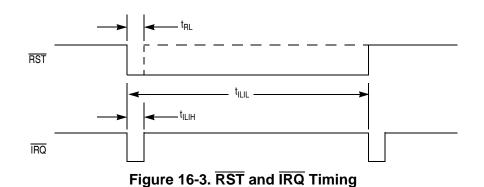

# 13.2 RST and IRQ Pins Initialization

RST and IRQ pins come out of reset as PTA3 and PTA2 respectively. RST and IRQ functions can be activated by programing CONFIG2 accordingly. Refer to Chapter 5 Configuration Register (CONFIG).

# **13.3 SIM Bus Clock Control and Generation**

The bus clock generator provides system clock signals for the CPU and peripherals on the MCU. The system clocks are generated from an incoming clock, BUSCLKX2, as shown in Figure 13-2.

# Chapter 14 Timer Interface Module (TIM)

# 14.1 Introduction

This section describes the timer interface module (TIM). The TIM is a two-channel timer that provides a timing reference with input capture, output compare, and pulse-width-modulation functions. Figure 14-2 is a block diagram of the TIM.

# 14.2 Features

Features of the TIM include the following:

- Two input capture/output compare channels

- Rising-edge, falling-edge, or any-edge input capture trigger

- Set, clear, or toggle output compare action

- Buffered and unbuffered pulse width modulation (PWM) signal generation

- Programmable TIM clock input

- 7-frequency internal bus clock prescaler selection

- External TIM clock input

- Free-running or modulo up-count operation

- Toggle any channel pin on overflow

- TIM counter stop and reset bits

# 14.3 Pin Name Conventions

The TIM shares two input/output (I/O) pins with two port A I/O pins. The full names of the TIM I/O pins are listed in Table 14-1. The generic pin name appear in the text that follows.

### Table 14-1. Pin Name Conventions

| TIM Generic Pin Names: | TCH0      | TCH1      | TCLK      |  |

|------------------------|-----------|-----------|-----------|--|

| Full TIM Pin Names:    | PTA0/TCH0 | PTA1/TCH1 | PTA2/TCLK |  |

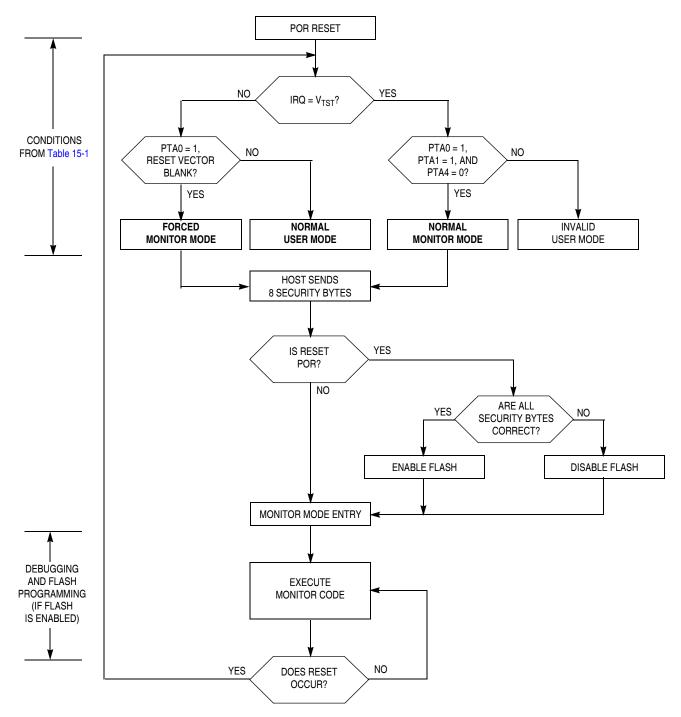

### **15.3.1 Functional Description**

Figure 15-9 shows a simplified diagram of monitor mode entry.

The monitor module receives and executes commands from a host computer. Figure 15-10, Figure 15-11, and Figure 15-12 show example circuits used to enter monitor mode and communicate with a host computer via a standard RS-232 interface.

Figure 15-9. Simplified Monitor Mode Entry Flowchart

#### Monitor Module (MON)

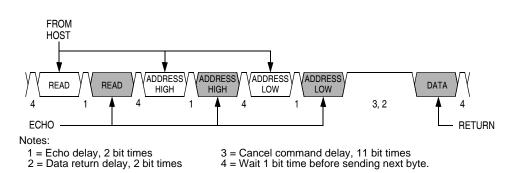

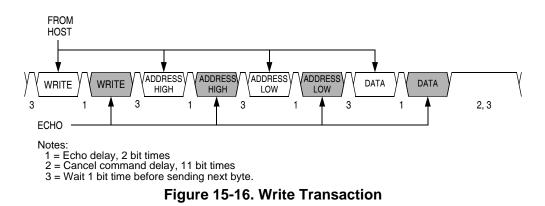

The monitor ROM firmware echoes each received byte back to the PTA0 pin for error checking. An 11-bit delay at the end of each command allows the host to send a break character to cancel the command. A delay of two bit times occurs before each echo and before READ, IREAD, or READSP data is returned. The data returned by a read command appears after the echo of the last byte of the command.

#### NOTE

Wait one bit time after each echo before sending the next byte.

Figure 15-15. Read Transaction

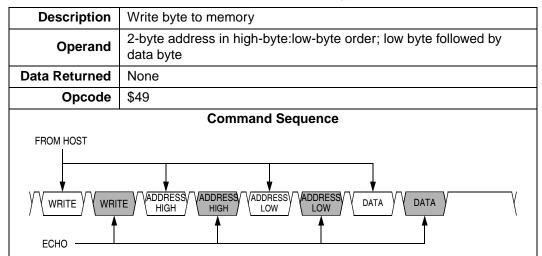

A brief description of each monitor mode command is given in Table 15-3 through Table 15-8.

Description Read byte from memory 2-byte address in high-byte:low-byte order Operand **Data Returned** Returns contents of specified address Opcode \$4A **Command Sequence** SENT TO MONITOR ADDRESS ADDRES ADDRESS ADDRES READ READ DATA HIGH LOW HIGH IOW ECHO RETURN

Table 15-3. READ (Read Memory) Command

Development Support

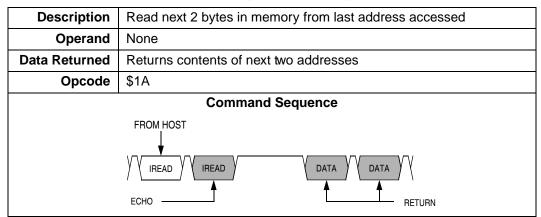

Table 15-5. IREAD (Indexed Read) Command

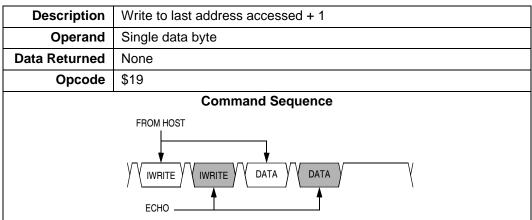

### Table 15-6. IWRITE (Indexed Write) Command

A sequence of IREAD or IWRITE commands can access a block of memory sequentially over the full 64-Kbyte memory map.

MC68HC908QY/QT Family Data Sheet, Rev. 6

# 16.7 5-V Control Timing

| Characteristic <sup>(1)</sup>                  | Symbol                              | Min                 | Max | Unit             |

|------------------------------------------------|-------------------------------------|---------------------|-----|------------------|

| Internal operating frequency                   | f <sub>OP</sub> (f <sub>Bus</sub> ) | —                   | 8   | MHz              |

| Internal clock period (1/f <sub>OP</sub> )     | t <sub>cyc</sub>                    | 125                 | _   | ns               |

| RST input pulse width low                      | t <sub>RL</sub>                     | 100                 | _   | ns               |

| IRQ interrupt pulse width low (edge-triggered) | t <sub>ILIH</sub>                   | 100                 | _   | ns               |

| IRQ interrupt pulse period                     | t <sub>ILIL</sub>                   | Note <sup>(2)</sup> |     | t <sub>cyc</sub> |

1. V<sub>DD</sub> = 4.5 to 5.5 Vdc, V<sub>SS</sub> = 0 Vdc, T<sub>A</sub> = T<sub>L</sub> to T<sub>H</sub>; timing shown with respect to 20% V<sub>DD</sub> and 70% V<sub>SS</sub>, unless otherwise noted.

2. The minimum period is the number of cycles it takes to execute the interrupt service routine plus 1  $t_{cyc}$ .

**Electrical Specifications**

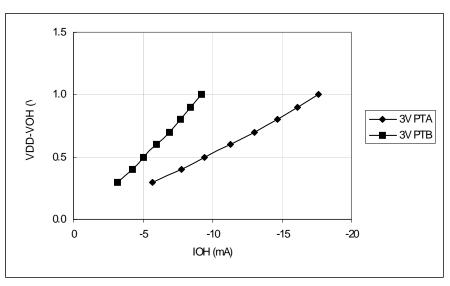

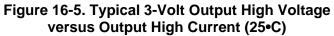

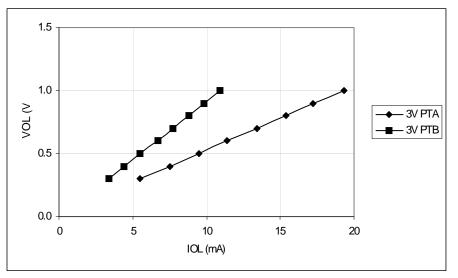

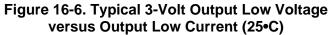

# 16.10 Typical 3.0-V Output Drive Characteristics