Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                     |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | HC08                                                                    |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 8MHz                                                                    |

| Connectivity               | -                                                                       |

| Peripherals                | LVD, POR, PWM                                                           |

| Number of I/O              | 13                                                                      |

| Program Memory Size        | 1.5KB (1.5K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 128 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                             |

| Data Converters            | -                                                                       |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

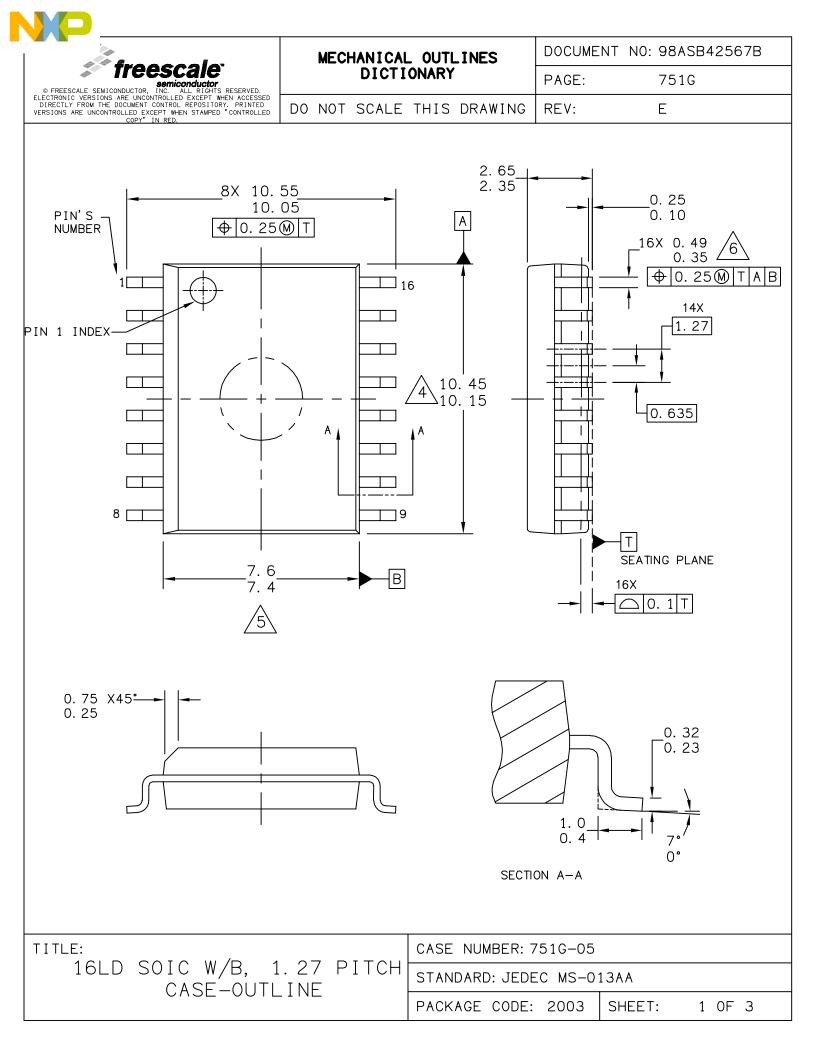

| Mounting Type              | Surface Mount                                                           |

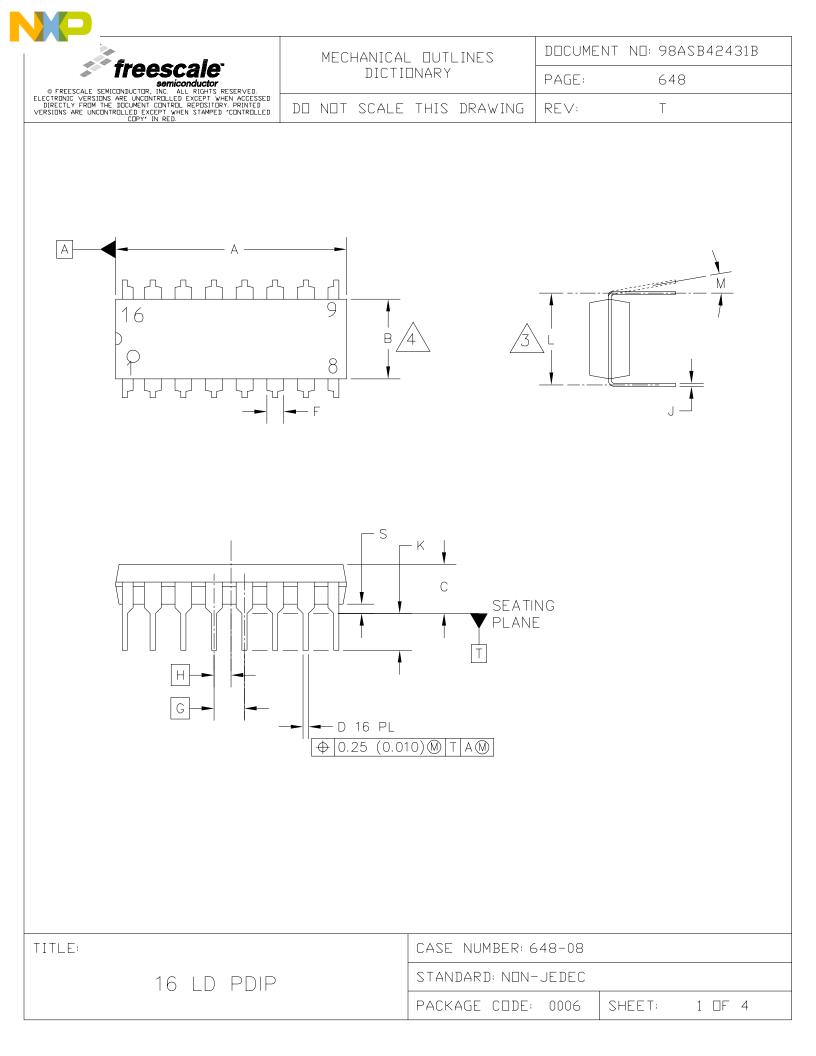

| Package / Case             | 16-SOIC (0.295", 7.50mm Width)                                          |

| Supplier Device Package    | 16-SOIC                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mchc908qy1cdwer |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

MC68HC908QY4 MC68HC908QT4 MC68HC908QY2 MC68HC908QT2 MC68HC908QY1 MC68HC908QT1

**Data Sheet**

To provide the most up-to-date information, the revision of our documents on the World Wide Web will be the most current. Your printed copy may be an earlier revision. To verify you have the latest information available, refer to:

http://freescale.com/

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. This product incorporates SuperFlash® technology licensed from SST.

© Freescale Semiconductor, Inc., 2005–2010. All rights reserved.

**Functional Description**

### 3.5.2 Stop Mode

The ADC module is inactive after the execution of a STOP instruction. Any pending conversion is aborted. ADC conversions resume when the MCU exits stop mode. Allow one conversion cycle to stabilize the analog circuitry before using ADC data after exiting stop mode.

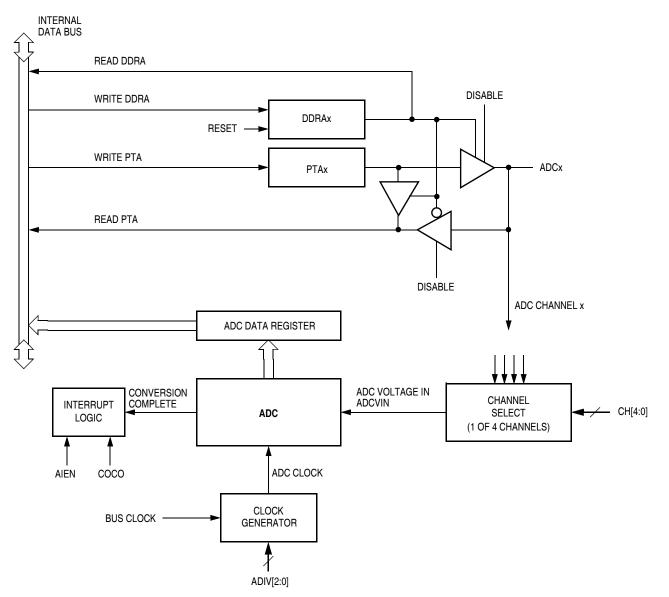

# 3.6 Input/Output Signals

The ADC module has four channels that are shared with I/O port A.

ADC voltage in (ADCVIN) is the input voltage signal from one of the four ADC channels to the ADC module.

# 3.7 Input/Output Registers

These I/O registers control and monitor ADC operation:

- ADC status and control register (ADSCR)

- ADC data register (ADR)

- ADC clock register (ADICLK)

### 3.7.1 ADC Status and Control Register

The following paragraphs describe the function of the ADC status and control register (ADSCR). When a conversion is in process and the ADSCR is written, the current conversion data should be discarded to prevent an incorrect reading.

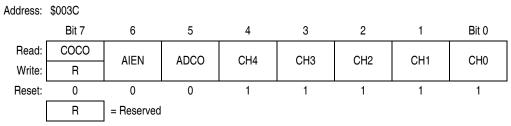

Figure 3-3. ADC Status and Control Register (ADSCR)

### COCO — Conversions Complete Bit

In non-interrupt mode (AIEN = 0), COCO is a read-only bit that is set at the end of each conversion. COCO will stay set until cleared by a read of the ADC data register. Reset clears this bit.

In interrupt mode (AIEN = 1), COCO is a read-only bit that is not set at the end of a conversion. It always reads as a 0.

1 = Conversion completed (AIEN = 0)

0 = Conversion not completed (AIEN = 0) or CPU interrupt enabled (AIEN = 1)

### NOTE

The write function of the COCO bit is reserved. When writing to the ADSCR register, always have a 0 in the COCO bit position.

#### Auto Wakeup Module (AWU)

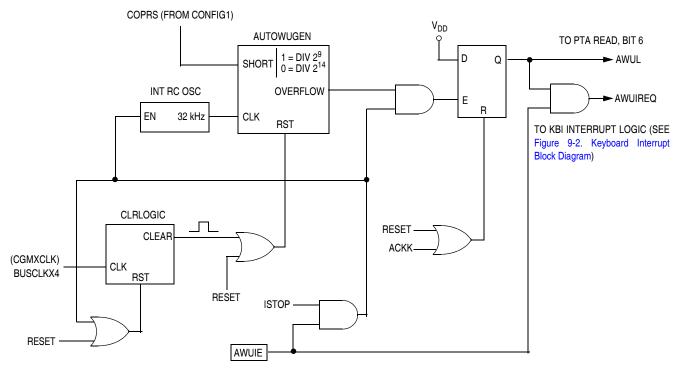

Figure 4-1. Auto Wakeup Interrupt Request Generation Logic

The auto wakeup RC oscillator is highly dependent on operating voltage and temperature. This feature is not recommended for use as a time-keeping function.

The wakeup request is latched to allow the interrupt source identification. The latched value, AWUL, can be read directly from the bit 6 position of PTA data register. This is a read-only bit which is occupying an empty bit position on PTA. No PTA associated registers, such as PTA6 data, PTA6 direction, and PTA6 pullup exist for this bit. The latch can be cleared by writing to the ACKK bit in the KBSCR register. Reset also clears the latch. AWUIE bit in KBI interrupt enable register (see Figure 4-1) has no effect on AWUL reading.

The AWU oscillator and counters are inactive in normal operating mode and become active only upon entering stop mode.

## 4.4 Wait Mode

The AWU module remains inactive in wait mode.

# 4.5 Stop Mode

When the AWU module is enabled (AWUIE = 1 in the keyboard interrupt enable register) it is activated automatically upon entering stop mode. Clearing the IMASKK bit in the keyboard status and control register enables keyboard interrupt requests to bring the MCU out of stop mode. The AWU counters start from '0' each time stop mode is entered.

#### Auto Wakeup Module (AWU)

### Bits 7-4 — Not used

These read-only bits always read as 0s.

### **KEYF** — Keyboard Flag Bit

This read-only bit is set when a keyboard interrupt is pending on port A or auto wakeup. Reset clears the KEYF bit.

1 = Keyboard/auto wakeup interrupt pending

0 = No keyboard/auto wakeup interrupt pending

### ACKK — Keyboard Acknowledge Bit

Writing a 1 to this write-only bit clears the keyboard/auto wakeup interrupt request on port A and auto wakeup logic. ACKK always reads as 0.Reset clears ACKK.

### IMASKK— Keyboard Interrupt Mask Bit

Writing a 1 to this read/write bit prevents the output of the keyboard interrupt mask from generating interrupt requests on port A or auto wakeup. Reset clears the IMASKK bit.

1 = Keyboard/auto wakeup interrupt requests masked

0 = Keyboard/auto wakeup interrupt requests not masked

### NOTE

MODEK is not used in conjuction with the auto wakeup feature. To see a description of this bit, see 9.7.1 Keyboard Status and Control Register.

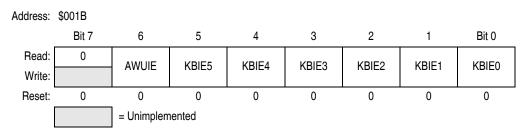

### 4.6.3 Keyboard Interrupt Enable Register

The keyboard interrupt enable register (KBIER) enables or disables the auto wakeup to operate as a keyboard/auto wakeup interrupt input.

### Figure 4-4. Keyboard Interrupt Enable Register (KBIER)

### AWUIE — Auto Wakeup Interrupt Enable Bit

This read/write bit enables the auto wakeup interrupt input to latch interrupt requests. Reset clears AWUIE.

1 = Auto wakeup enabled as interrupt input

0 = Auto wakeup not enabled as interrupt input

### NOTE

KBIE5–KBIE0 bits are not used in conjuction with the auto wakeup feature. To see a description of these bits, see 9.7.2 Keyboard Interrupt Enable Register.

# Chapter 5 Configuration Register (CONFIG)

# 5.1 Introduction

This section describes the configuration registers (CONFIG1 and CONFIG2). The configuration registers enable or disable the following options:

- Stop mode recovery time (32  $\times$  BUSCLKX4 cycles or 4096  $\times$  BUSCLKX4 cycles)

- STOP instruction

- Computer operating properly module (COP)

- COP reset period (COPRS): 8176 × BUSCLKX4 or 262,128 × BUSCLKX4

- Low-voltage inhibit (LVI) enable and trip voltage selection

- OSC option selection

- IRQ pin

- RST pin

- Auto wakeup timeout period

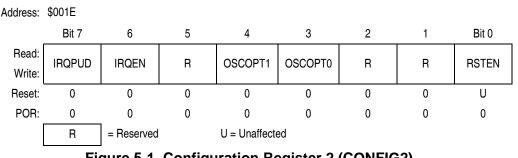

# 5.2 Functional Description

The configuration registers are used in the initialization of various options. The configuration registers can be written once after each reset. Most of the configuration register bits are cleared during reset. Since the various options affect the operation of the microcontroller unit (MCU) it is recommended that this register be written immediately after reset. The configuration registers are located at \$001E and \$001F, and may be read at anytime.

NOTE

The CONFIG registers are one-time writable by the user after each reset. Upon a reset, the CONFIG registers default to predetermined settings as shown in Figure 5-1 and Figure 5-2.

Figure 5-1. Configuration Register 2 (CONFIG2)

# Chapter 6 Computer Operating Properly (COP)

# 6.1 Introduction

The computer operating properly (COP) module contains a free-running counter that generates a reset if allowed to overflow. The COP module helps software recover from runaway code. Prevent a COP reset by clearing the COP counter periodically. The COP module can be disabled through the COPD bit in the configuration 1 (CONFIG1) register.

# 6.2 Functional Description

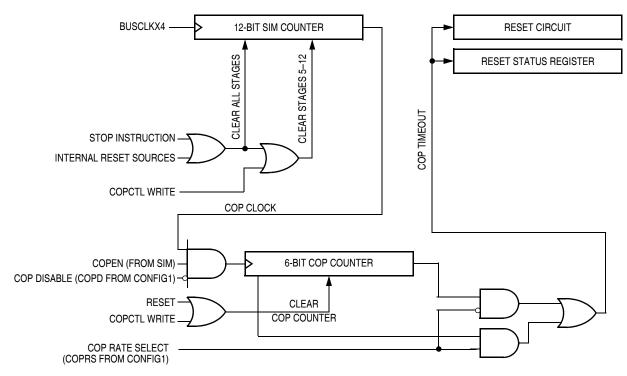

Figure 6-1. COP Block Diagram

#### Computer Operating Properly (COP)

The COP counter is a free-running 6-bit counter preceded by the 12-bit system integration module (SIM) counter. If not cleared by software, the COP counter overflows and generates an asynchronous reset after 262,128 or 8176 BUSCLKX4 cycles; depending on the state of the COP rate select bit, COPRS, in configuration register 1. With a 262,128 BUSCLKX4 cycle overflow option, the internal 12.8-MHz oscillator gives a COP timeout period of 20.48 ms. Writing any value to location \$FFFF before an overflow occurs prevents a COP reset by clearing the COP counter and stages 12–5 of the SIM counter.

### NOTE

Service the COP immediately after reset and before entering or after exiting stop mode to guarantee the maximum time before the first COP counter overflow.

A COP reset pulls the  $\overline{\text{RST}}$  pin low (if the RSTEN bit is set in the CONFIG1 register) for 32 × BUSCLKX4 cycles and sets the COP bit in the reset status register (RSR). See 13.8.1 SIM Reset Status Register.

### NOTE

Place COP clearing instructions in the main program and not in an interrupt subroutine. Such an interrupt subroutine could keep the COP from generating a reset even while the main program is not working properly.

## 6.3 I/O Signals

The following paragraphs describe the signals shown in Figure 6-1.

### 6.3.1 BUSCLKX4

BUSCLKX4 is the oscillator output signal. BUSCLKX4 frequency is equal to the internal oscillator frequency, the crystal frequency, or the RC-oscillator frequency.

### 6.3.2 STOP Instruction

The STOP instruction clears the SIM counter.

### 6.3.3 COPCTL Write

Writing any value to the COP control register (COPCTL) (see 6.4 COP Control Register) clears the COP counter and clears stages 12–5 of the SIM counter. Reading the COP control register returns the low byte of the reset vector.

### 6.3.4 Power-On Reset

The power-on reset (POR) circuit in the SIM clears the SIM counter  $4096 \times BUSCLKX4$  cycles after power up.

### 6.3.5 Internal Reset

An internal reset clears the SIM counter and the COP counter.

### 6.3.6 COPD (COP Disable)

The COPD signal reflects the state of the COP disable bit (COPD) in the configuration register 1 (CONFIG1). See Chapter 5 Configuration Register (CONFIG).

### 6.3.7 COPRS (COP Rate Select)

The COPRS signal reflects the state of the COP rate select bit (COPRS) in the configuration register 1 (CONFIG1). See Chapter 5 Configuration Register (CONFIG).

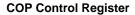

# 6.4 COP Control Register

The COP control register (COPCTL) is located at address \$FFFF and overlaps the reset vector. Writing any value to \$FFFF clears the COP counter and starts a new timeout period. Reading location \$FFFF returns the low byte of the reset vector.

Figure 6-2. COP Control Register (COPCTL)

# 6.5 Interrupts

The COP does not generate CPU interrupt requests.

## 6.6 Monitor Mode

The COP is disabled in monitor mode when  $V_{TST}$  is present on the IRQ pin.

## 6.7 Low-Power Modes

The WAIT and STOP instructions put the MCU in low power-consumption standby modes.

### 6.7.1 Wait Mode

The COP continues to operate during wait mode. To prevent a COP reset during wait mode, periodically clear the COP counter.

### 6.7.2 Stop Mode

Stop mode turns off the BUSCLKX4 input to the COP and clears the SIM counter. Service the COP immediately before entering or after exiting stop mode to ensure a full COP timeout period after entering or exiting stop mode.

# 6.8 COP Module During Break Mode

The COP is disabled during a break interrupt with monitor mode when BDCOP bit is set in break auxiliary register (BRKAR).

### 8.7.1 IRQ Input Pins (IRQ)

The IRQ pin provides a maskable external interrupt source. The IRQ pin contains an internal pullup device.

## 8.8 Registers

The IRQ status and control register (INTSCR) controls and monitors operation of the IRQ module. See Chapter 5 Configuration Register (CONFIG).

The INTSCR has the following functions:

- Shows the state of the IRQ flag

- Clears the IRQ latch

- Masks the IRQ interrupt request

- Controls triggering sensitivity of the IRQ interrupt pin

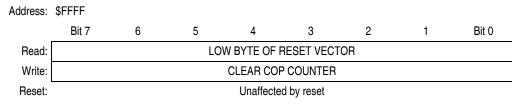

Figure 8-3. IRQ Status and Control Register (INTSCR)

### IRQF — IRQ Flag

This read-only status bit is set when the IRQ interrupt is pending.

$1 = \overline{IRQ}$  interrupt pending

$0 = \overline{IRQ}$  interrupt not pending

### ACK — IRQ Interrupt Request Acknowledge Bit

Writing a 1 to this write-only bit clears the IRQ latch. ACK always reads as 0.

### IMASK — IRQ Interrupt Mask Bit

Writing a 1 to this read/write bit disables the IRQ interrupt request.

1 = IRQ interrupt request disabled

0 = IRQ interrupt request enabled

### MODE — IRQ Edge/Level Select Bit

This read/write bit controls the triggering sensitivity of the IRQ pin.

$1 = \overline{IRQ}$  interrupt request on falling edges and low levels

$0 = \overline{IRQ}$  interrupt request on falling edges only

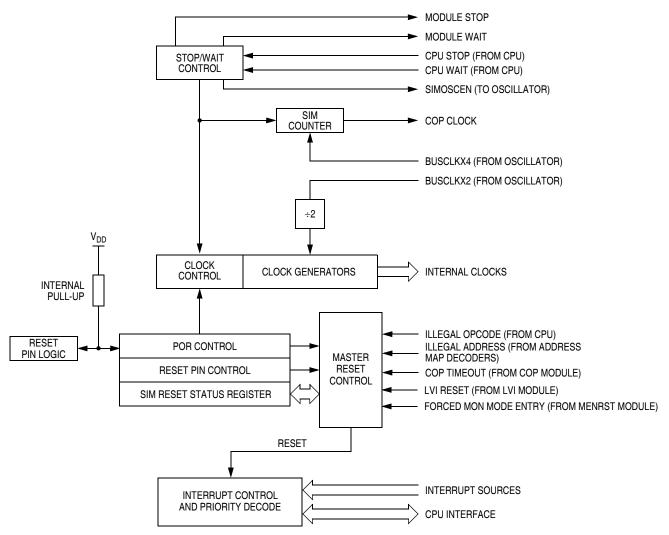

#### System Integration Module (SIM)

Figure 13-1. SIM Block Diagram

# 13.2 RST and IRQ Pins Initialization

RST and IRQ pins come out of reset as PTA3 and PTA2 respectively. RST and IRQ functions can be activated by programing CONFIG2 accordingly. Refer to Chapter 5 Configuration Register (CONFIG).

# **13.3 SIM Bus Clock Control and Generation**

The bus clock generator provides system clock signals for the CPU and peripherals on the MCU. The system clocks are generated from an incoming clock, BUSCLKX2, as shown in Figure 13-2.

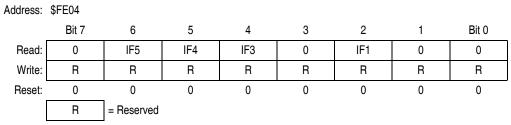

### 13.6.2.1 Interrupt Status Register 1

#### Figure 13-11. Interrupt Status Register 1 (INT1)

### IF1 and IF3–IF5 — Interrupt Flags

These flags indicate the presence of interrupt requests from the sources shown in Table 13-3.

1 = Interrupt request present

0 = No interrupt request present

#### Bit 0, 1, 3, and 7 — Always read 0

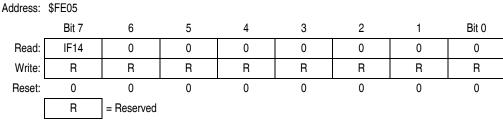

### 13.6.2.2 Interrupt Status Register 2

### Figure 13-12. Interrupt Status Register 2 (INT2)

### IF14 — Interrupt Flags

This flag indicates the presence of interrupt requests from the sources shown in Table 13-3. 1 = Interrupt request present

0 = No interrupt request present

### Bit 0-6 — Always read 0

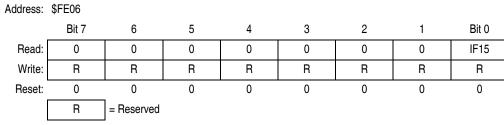

### 13.6.2.3 Interrupt Status Register 3

### Figure 13-13. Interrupt Status Register 3 (INT3)

### IF15 — Interrupt Flags

These flags indicate the presence of interrupt requests from the sources shown in Table 13-3.

- 1 = Interrupt request present

- 0 = No interrupt request present

### Bit 1–7 — Always read 0

#### System Integration Module (SIM)

The SIM counter is held in reset from the execution of the STOP instruction until the beginning of stop recovery. It is then used to time the recovery period. Figure 13-17 shows stop mode entry timing and Figure 13-18 shows the stop mode recovery time from interrupt or break.

**NOTE** To minimize stop current, all pins configured as inputs should be driven to

#### a logic 1 or logic 0. CPUSTOP ADDRESS BUS STOP ADDR STOP ADDR + 1 SAME SAME DATA BUS PREVIOUS DATA NEXT OPCODE SAME SAME R/W NOTE: Previous data can be operand data or the STOP opcode, depending on the last instruction. Figure 13-17. Stop Mode Entry Timing STOP RECOVERY PERIOD BUSCLKX4 INTERRUPT ADDRESS BUS STOP +1 STOP + 2 STOP + 2 SP SP – 1 SP – 2 SP – 3

Figure 13-18. Stop Mode Recovery from Interrupt

## 13.8 SIM Registers

The SIM has three memory mapped registers. Table 13-4 shows the mapping of these registers.

### Table 13-4. SIM Registers

| Address | Register | Access Mode |

|---------|----------|-------------|

| \$FE00  | BSR      | User        |

| \$FE01  | SRSR     | User        |

| \$FE03  | BFCR     | User        |

#### Timer Interface Module (TIM)

#### TRST — TIM Reset Bit

Setting this write-only bit resets the TIM counter and the TIM prescaler. Setting TRST has no effect on any other registers. Counting resumes from \$0000. TRST is cleared automatically after the TIM counter is reset and always reads as a 0. Reset clears the TRST bit.

1 = Prescaler and TIM counter cleared

0 = No effect

### NOTE

Setting the TSTOP and TRST bits simultaneously stops the TIM counter at a value of \$0000.

### PS[2:0] — Prescaler Select Bits

These read/write bits select either the PTA2/TCLK pin or one of the seven prescaler outputs as the input to the TIM counter as Table 14-2 shows. Reset clears the PS[2:0] bits.

| PS2 | PS1 | PS0 | TIM Clock Source        |  |

|-----|-----|-----|-------------------------|--|

| 0   | 0   | 0   | Internal bus clock ÷ 1  |  |

| 0   | 0   | 1   | Internal bus clock ÷ 2  |  |

| 0   | 1   | 0   | Internal bus clock ÷ 4  |  |

| 0   | 1   | 1   | Internal bus clock ÷ 8  |  |

| 1   | 0   | 0   | Internal bus clock ÷ 16 |  |

| 1   | 0   | 1   | Internal bus clock ÷ 32 |  |

| 1   | 1   | 0   | Internal bus clock ÷ 64 |  |

| 1   | 1   | 1   | PTA2/TCLK               |  |

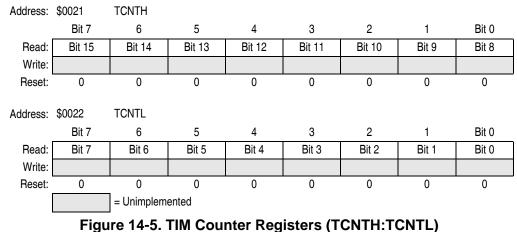

### 14.9.2 TIM Counter Registers

The two read-only TIM counter registers contain the high and low bytes of the value in the TIM counter. Reading the high byte (TCNTH) latches the contents of the low byte (TCNTL) into a buffer. Subsequent reads of TCNTH do not affect the latched TCNTL value until TCNTL is read. Reset clears the TIM counter registers. Setting the TIM reset bit (TRST) also clears the TIM counter registers.

NOTE

If you read TCNTH during a break interrupt, be sure to unlatch TCNTL by reading TCNTL before exiting the break interrupt. Otherwise, TCNTL retains the value latched during the break.

#### Timer Interface Module (TIM)

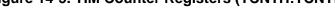

### CHxMAX — Channel x Maximum Duty Cycle Bit

When the TOVx bit is at a 1, setting the CHxMAX bit forces the duty cycle of buffered and unbuffered PWM signals to 100%. As Figure 14-8 shows, the CHxMAX bit takes effect in the cycle after it is set or cleared. The output stays at the 100% duty cycle level until the cycle after CHxMAX is cleared.

Figure 14-8. CHxMAX Latency

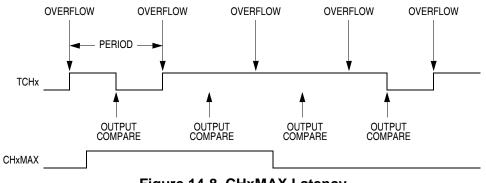

### 14.9.5 TIM Channel Registers

These read/write registers contain the captured TIM counter value of the input capture function or the output compare value of the output compare function. The state of the TIM channel registers after reset is unknown.

In input capture mode (MSxB:MSxA = 0:0), reading the high byte of the TIM channel x registers (TCHxH) inhibits input captures until the low byte (TCHxL) is read.

In output compare mode (MSxB:MSxA  $\neq$  0:0), writing to the high byte of the TIM channel x registers (TCHxH) inhibits output compares until the low byte (TCHxL) is written.

Figure 14-9. TIM Channel Registers (TCH0H/L:TCH1H/L)

Development Support

| Mode (PTA2)                    |                         | RST<br>(PTA3) | Reset<br>Vector   | Serial<br>Communi-<br>cation | Mode<br>Selection |              | СОР      | Communication<br>Speed |                      |              | Comments                           |

|--------------------------------|-------------------------|---------------|-------------------|------------------------------|-------------------|--------------|----------|------------------------|----------------------|--------------|------------------------------------|

|                                | (FTA2)                  |               |                   | PTA0                         | PTA1              | PTA4         |          | External<br>Clock      | Bus<br>Frequency     | Baud<br>Rate |                                    |

| Normal<br>Monitor              | V <sub>TST</sub>        | $V_{DD}$      | х                 | 1                            | 1                 | 0            | Disabled | 9.8304<br>MHz          | 2.4576<br>MHz        | 9600         | Provide external<br>clock at OSC1. |

| Forced                         | V <sub>DD</sub>         | Х             | \$FFFF<br>(blank) | 1                            | Х                 | х            | Disabled | 9.8304<br>MHz          | 2.4576<br>MHz        | 9600         | Provide external<br>clock at OSC1. |

| Monitor                        | V <sub>SS</sub>         | Х             | \$FFFF<br>(blank) | 1                            | Х                 | х            | Disabled | х                      | 3.2 MHz<br>(Trimmed) | 9600         | Internal clock<br>is active.       |

| User                           | Х                       | Х             | Not<br>\$FFFF     | Х                            | Х                 | х            | Enabled  | Х                      | Х                    | Х            |                                    |

| MON08<br>Function<br>[Pin No.] | V <sub>TST</sub><br>[6] | RST<br>[4]    |                   | COM<br>[8]                   | MOD0<br>[12]      | MOD1<br>[10] |          | OSC1<br>[13]           |                      |              |                                    |

Table 15-1. Monitor Mode Signal Requirements and Options

1. PTA0 must have a pullup resistor to  $V_{DD}$  in monitor mode.

2. Communication speed in the table is an example to obtain a baud rate of 9600. Baud rate using external oscillator is bus frequency / 256 and baud rate using internal oscillator is bus frequency / 335.

3. External clock is a 9.8304 MHz oscillator on OSC1.

4. X = don't care

5. MON08 pin refers to P&E Microcomputer Systems' MON08-Cyclone 2 by 8-pin connector.

| NC       | 1  | 2  | GND  |

|----------|----|----|------|

| NC       | 3  | 4  | RST  |

| NC       | 5  | 6  | IRQ  |

| NC       | 7  | 8  | PTA0 |

| NC       | 9  | 10 | PTA4 |

| NC       | 11 | 12 | PTA1 |

| OSC1     | 13 | 14 | NC   |

| $V_{DD}$ | 15 | 16 | NC   |

The rising edge of the internal RST signal latches the monitor mode. Once monitor mode is latched, the values on PTA1 and PTA4 pins can be changed.

Once out of reset, the MCU waits for the host to send eight security bytes (see 15.3.2 Security). After the security bytes, the MCU sends a break signal (10 consecutive logic 0s) to the host, indicating that it is ready to receive a command.

### 15.3.1.1 Normal Monitor Mode

RST and OSC1 functions will be active on the PTA3 and PTA5 pins respectively as long as  $V_{TST}$  is applied to the IRQ pin. If the IRQ pin is lowered (no longer  $V_{TST}$ ) then the chip will still be operating in monitor mode, but the pin functions will be determined by the settings in the configuration registers (see Chapter 5 Configuration Register (CONFIG)) when  $V_{TST}$  was lowered. With  $V_{TST}$  lowered, the BIH and BIL instructions will read the IRQ pin state only if IRQEN is set in the CONFIG2 register.

# 16.14 Analog-to-Digital Converter Characteristics

| Characteristic                                         | Symbol            | Min                              | Мах                          | Unit                     | Comments                                         |

|--------------------------------------------------------|-------------------|----------------------------------|------------------------------|--------------------------|--------------------------------------------------|

| Supply voltage                                         | V <sub>DDAD</sub> | 2.7<br>(V <sub>DD</sub> min)     | 5.5<br>(V <sub>DD</sub> max) | V                        | —                                                |

| Input voltages                                         | V <sub>ADIN</sub> | V <sub>SS</sub>                  | V <sub>DD</sub>              | V                        | —                                                |

| Resolution<br>(1 LSB)                                  | RES               | 10.5                             | 21.5                         | mV                       | —                                                |

| Absolute accuracy<br>(Total unadjusted error)          | E <sub>TUE</sub>  | _                                | ± 1.5                        | LSB                      | Includes quantization                            |

| ADC internal clock                                     | f <sub>ADIC</sub> | 0.5                              | 1.048                        | MHz                      | $t_{ADIC} = 1/f_{ADIC},$<br>tested only at 1 MHz |

| Conversion range                                       | V <sub>AIN</sub>  | V <sub>SS</sub>                  | V <sub>DD</sub>              | V                        | —                                                |

| Power-up time                                          | t <sub>ADPU</sub> | 16                               | —                            | t <sub>ADIC</sub> cycles | $t_{ADIC} = 1/f_{ADIC}$                          |

| Conversion time                                        | t <sub>ADC</sub>  | 16                               | 17                           | t <sub>ADIC</sub> cycles | $t_{ADIC} = 1/f_{ADIC}$                          |

| Sample time <sup>(1)</sup>                             | t <sub>ADS</sub>  | 5                                | —                            | t <sub>ADIC</sub> cycles | $t_{ADIC} = 1/f_{ADIC}$                          |

| Zero input reading <sup>(2)</sup>                      | Z <sub>ADI</sub>  | 00                               | 01                           | Hex                      | V <sub>IN</sub> = V <sub>SS</sub>                |

| Full-scale reading <sup>(3)</sup>                      | F <sub>ADI</sub>  | FE                               | FF                           | Hex                      | $V_{IN} = V_{DD}$                                |

| Input capacitance                                      | C <sub>ADI</sub>  | _                                | 8                            | pF                       | Not tested                                       |

| Input leakage <sup>(3)</sup>                           | I <sub>IL</sub>   | —                                | ± 1                          | μΑ                       | —                                                |

| ADC supply current<br>$V_{DD} = 3 V$<br>$V_{DD} = 5 V$ | I <sub>ADAD</sub> | Typical = 0.45<br>Typical = 0.65 |                              | mA<br>mA                 | Enabled<br>Enabled                               |

1. Source impedances greater than 10 kΩ adversely affect internal RC charging time during input sampling.

2. Zero-input/full-scale reading requires sufficient decoupling measures for accurate conversions.

3. The external system error caused by input leakage current is approximately equal to the product of R source and input current.

**Electrical Specifications**