Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                               |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | HC08                                                                   |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 8MHz                                                                   |

| Connectivity               | -                                                                      |

| Peripherals                | LVD, POR, PWM                                                          |

| Number of I/O              | 13                                                                     |

| Program Memory Size        | 1.5KB (1.5K x 8)                                                       |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 128 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                            |

| Data Converters            | A/D 4x8b                                                               |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 16-SOIC (0.295", 7.50mm Width)                                         |

| Supplier Device Package    | 16-SOIC                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mchc908qy2vdwe |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

MC68HC908QY4 MC68HC908QT4 MC68HC908QY2 MC68HC908QT2 MC68HC908QY1 MC68HC908QT1

**Data Sheet**

To provide the most up-to-date information, the revision of our documents on the World Wide Web will be the most current. Your printed copy may be an earlier revision. To verify you have the latest information available, refer to:

http://freescale.com/

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. This product incorporates SuperFlash® technology licensed from SST.

© Freescale Semiconductor, Inc., 2005–2010. All rights reserved.

Memory

### **ERASE** — Erase Control Bit

This read/write bit configures the memory for erase operation. ERASE is interlocked with the PGM bit such that both bits cannot be equal to 1 or set to 1 at the same time.

- 1 = Erase operation selected

- 0 = Erase operation unselected

### PGM — Program Control Bit

This read/write bit configures the memory for program operation. PGM is interlocked with the ERASE bit such that both bits cannot be equal to 1 or set to 1 at the same time.

- 1 = Program operation selected

- 0 = Program operation unselected

### 2.6.2 FLASH Page Erase Operation

Use the following procedure to erase a page of FLASH memory. A page consists of 64 consecutive bytes starting from addresses \$XX00, \$XX40, \$XX80, or \$XXC0. The 48-byte user interrupt vectors area also forms a page. Any FLASH memory page can be erased alone.

- 1. Set the ERASE bit and clear the MASS bit in the FLASH control register.

- 2. Read the FLASH block protect register.

- 3. Write any data to any FLASH location within the address range of the block to be erased.

- 4. Wait for a time,  $t_{NVS}$  (minimum 10  $\mu$ s).

- 5. Set the HVEN bit.

- 6. Wait for a time, t<sub>Erase</sub> (minimum 1 ms or 4 ms).

- 7. Clear the ERASE bit.

- 8. Wait for a time,  $t_{NVH}$  (minimum 5  $\mu$ s).

- 9. Clear the HVEN bit.

- 10. After time,  $t_{RCV}$  (typical 1  $\mu$ s), the memory can be accessed in read mode again.

### NOTE

Programming and erasing of FLASH locations cannot be performed by code being executed from the FLASH memory. While these operations must be performed in the order as shown, but other unrelated operations may occur between the steps.

### CAUTION

A page erase of the vector page will erase the internal oscillator trim values at \$FFC0 and \$FFC1.

In applications that require more than 1000 program/erase cycles, use the 4 ms page erase specification to get improved long-term reliability. Any application can use this 4 ms page erase specification. However, in applications where a FLASH location will be erased and reprogrammed less than 1000 times, and speed is important, use the 1 ms page erase specification to get a shorter cycle time.

#### Memory

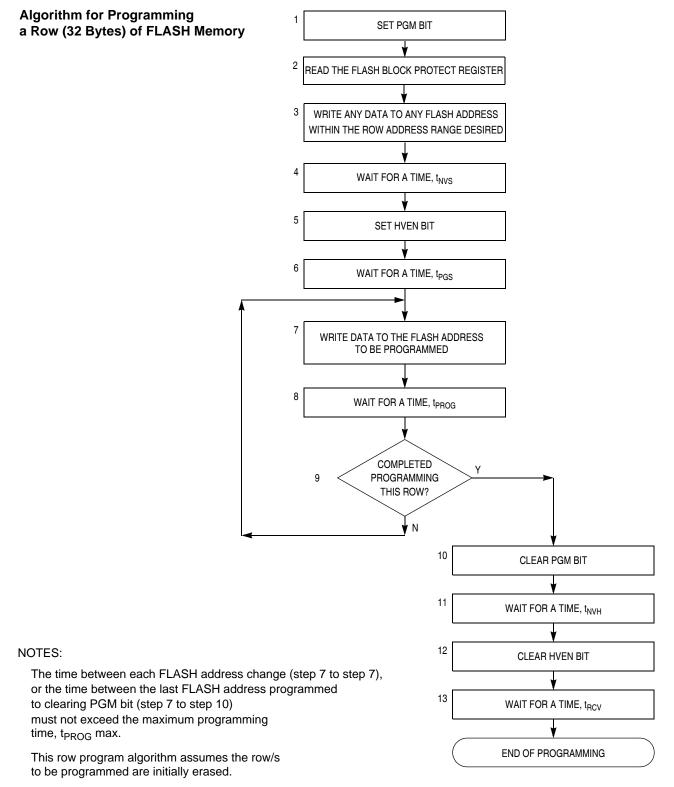

- 8. Wait for time,  $t_{PROG}$  (minimum 30  $\mu$ s).

- 9. Repeat step 7 and 8 until all desired bytes within the row are programmed.

- 10. Clear the PGM  $bit^{(1)}$ .

- 11. Wait for time,  $t_{NVH}$  (minimum 5  $\mu$ s).

- 12. Clear the HVEN bit.

- 13. After time,  $t_{RCV}$  (typical 1  $\mu$ s), the memory can be accessed in read mode again.

### NOTE

The COP register at location \$FFFF should not be written between steps 5–12, when the HVEN bit is set. Since this register is located at a valid FLASH address, unpredictable behavior may occur if this location is written while HVEN is set.

This program sequence is repeated throughout the memory until all data is programmed.

### NOTE

Programming and erasing of FLASH locations cannot be performed by code being executed from the FLASH memory. While these operations must be performed in the order shown, other unrelated operations may occur between the steps. Do not exceed  $t_{PROG}$  maximum, see 16.16 Memory Characteristics.

### 2.6.5 FLASH Protection

Due to the ability of the on-board charge pump to erase and program the FLASH memory in the target application, provision is made to protect blocks of memory from unintentional erase or program operations due to system malfunction. This protection is done by use of a FLASH block protect register (FLBPR). The FLBPR determines the range of the FLASH memory which is to be protected. The range of the protected area starts from a location defined by FLBPR and ends to the bottom of the FLASH memory (\$FFFF). When the memory is protected, the HVEN bit cannot be set in either ERASE or PROGRAM operations.

### NOTE

In performing a program or erase operation, the FLASH block protect register must be read after setting the PGM or ERASE bit and before asserting the HVEN bit.

When the FLBPR is programmed with all 0 s, the entire memory is protected from being programmed and erased. When all the bits are erased (all 1's), the entire memory is accessible for program and erase.

When bits within the FLBPR are programmed, they lock a block of memory. The address ranges are shown in 2.6.6 FLASH Block Protect Register. Once the FLBPR is programmed with a value other than FF, any erase or program of the FLBPR or the protected block of FLASH memory is prohibited. Mass erase is disabled whenever any block is protected (FLBPR does not equal FF). The FLBPR itself can be erased or programmed only with an external voltage,  $V_{TST}$ , present on the IRQ pin. This voltage also allows entry from reset into the monitor mode.

<sup>2.</sup> The time between each FLASH address change, or the time between the last FLASH address programmed to clearing PGM bit, must not exceed the maximum programming time, t<sub>PROG</sub> maximum.

#### FLASH Memory (FLASH)

#### **Configuration Register (CONFIG)**

### IRQPUD — IRQ Pin Pullup Control Bit

- 1 = Internal pullup is disconnected

- 0 = Internal pullup is connected between  $\overline{IRQ}$  pin and  $V_{DD}$

### IRQEN — IRQ Pin Function Selection Bit

- 1 = Interrupt request function active in pin

- 0 = Interrupt request function inactive in pin

### OSCOPT1 and OSCOPT0 — Selection Bits for Oscillator Option

- (0, 0) Internal oscillator

- (0, 1) External oscillator

- (1, 0) External RC oscillator

- (1, 1) External XTAL oscillator

### **RSTEN** — **RST** Pin Function Selection

- 1 = Reset function active in pin

- 0 =Reset function inactive in pin

### NOTE

The RSTEN bit is cleared by a power-on reset (POR) only. Other resets will leave this bit unaffected.

Address: \$001F

|                 | Bit 7 | 6       | 5       | 4       | 3       | 2     | 1    | Bit 0 |

|-----------------|-------|---------|---------|---------|---------|-------|------|-------|

| Read:<br>Write: | COPRS | LVISTOP | LVIRSTD | LVIPWRD | LVI5OR3 | SSREC | STOP | COPD  |

| Reset:          | 0     | 0       | 0       | 0       | U       | 0     | 0    | 0     |

| POR:            | 0     | 0       | 0       | 0       | 0       | 0     | 0    | 0     |

|                 |       |         |         |         |         |       |      |       |

U = Unaffected

### Figure 5-2. Configuration Register 1 (CONFIG1)

### COPRS (Out of STOP Mode) — COP Reset Period Selection Bit

- 1 = COP reset short cycle = 8176 × BUSCLKX4

- $0 = COP reset long cycle = 262,128 \times BUSCLKX4$

### COPRS (In STOP Mode) — Auto Wakeup Period Selection Bit

- 1 = Auto wakeup short cycle =  $512 \times INTRCOSC$

- 0 = Auto wakeup long cycle =  $16,384 \times$  INTRCOSC

### LVISTOP — LVI Enable in Stop Mode Bit

When the LVIPWRD bit is clear, setting the LVISTOP bit enables the LVI to operate during stop mode. Reset clears LVISTOP.

1 = LVI enabled during stop mode

0 = LVI disabled during stop mode

### LVIRSTD — LVI Reset Disable Bit

LVIRSTD disables the reset signal from the LVI module.

1 = LVI module resets disabled

0 = LVI module resets enabled

Configuration Register (CONFIG)

# Chapter 6 Computer Operating Properly (COP)

# 6.1 Introduction

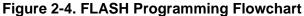

The computer operating properly (COP) module contains a free-running counter that generates a reset if allowed to overflow. The COP module helps software recover from runaway code. Prevent a COP reset by clearing the COP counter periodically. The COP module can be disabled through the COPD bit in the configuration 1 (CONFIG1) register.

# 6.2 Functional Description

Figure 6-1. COP Block Diagram

# Chapter 11 Oscillator Module (OSC)

## **11.1 Introduction**

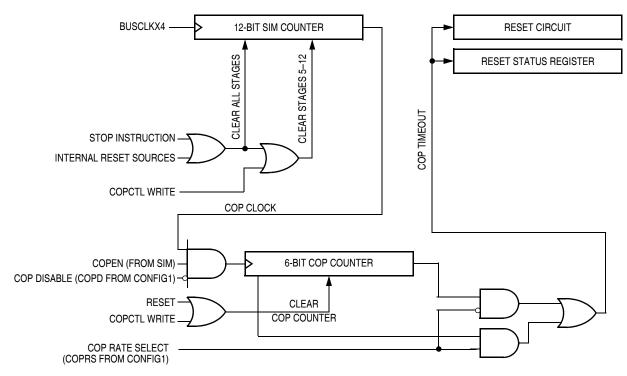

The oscillator module is used to provide a stable clock source for the microcontroller system and bus. The oscillator module generates two output clocks, BUSCLKX2 and BUSCLKX4. The BUSCLKX4 clock is used by the system integration module (SIM) and the computer operating properly module (COP). The BUSCLKX2 clock is divided by two in the SIM to be used as the bus clock for the microcontroller. Therefore the bus frequency will be one fourth of the BUSCLKX4 frequency.

### **11.2 Features**

The oscillator has these four clock source options available:

- 1. Internal oscillator: An internally generated, fixed frequency clock, trimmable to ±5%. This is the default option out of reset.

- 2. External oscillator: An external clock that can be driven directly into OSC1.

- 3. External RC: A built-in oscillator module (RC oscillator) that requires an external R connection only. The capacitor is internal to the chip.

- 4. External crystal: A built-in oscillator module (XTAL oscillator) that requires an external crystal or ceramic-resonator.

# **11.3 Functional Description**

The oscillator contains these major subsystems:

- Internal oscillator circuit

- Internal or external clock switch control

- External clock circuit

- External crystal circuit

- External RC clock circuit

### 11.3.1.1 Internal Oscillator Trimming

The 8-bit trimming register, OSCTRIM, allows a clock period adjust of +127 and -128 steps. Increasing OSCTRIM value increases the clock period. Trimming allows the internal clock frequency to be set to 12.8 MHz  $\pm$  5%.

All devices are factory programmed with trim values in reserved FLASH memory locations \$FFC0 and \$FFC1. The trim value is not automatically loaded into the OSCTRIM register. User software must copy the trim value from \$FFC0 or \$FFC1 into OSCTRIM if needed. The factory trim value provides the accuracy required for communication using forced monitor mode. Some production programmers erase the factory trim values, so confirm with your programmer vendor that the trim values at \$FFC0 and \$FFC1 are preserved, or are re-trimmed. Trimming the device in the user application board will provide the most accurate trim value.

### 11.3.1.2 Internal to External Clock Switching

When external clock source (external OSC, RC, or XTAL) is desired, the user must perform the following steps:

- 1. For external crystal circuits only, OSCOPT[1:0] = 1:1: To help precharge an external crystal oscillator, set PTA4 (OSC2) as an output and drive high for several cycles. This may help the crystal circuit start more robustly.

- Set CONFIG2 bits OSCOPT[1:0] according to . The oscillator module control logic will then set OSC1 as an external clock input and, if the external crystal option is selected, OSC2 will also be set as the clock output.

- 3. Create a software delay to wait the stabilization time needed for the selected clock source (crystal, resonator, RC) as recommended by the component manufacturer. A good rule of thumb for crystal oscillators is to wait 4096 cycles of the crystal frequency, i.e., for a 4-MHz crystal, wait approximately 1 msec.

- 4. After the manufacturer's recommended delay has elapsed, the ECGON bit in the OSC status register (OSCSTAT) needs to be set by the user software.

- 5. After ECGON set is detected, the OSC module checks for oscillator activity by waiting two external clock rising edges.

- 6. The OSC module then switches to the external clock. Logic provides a glitch free transition.

- 7. The OSC module first sets the ECGST bit in the OSCSTAT register and then stops the internal oscillator.

### NOTE

Once transition to the external clock is done, the internal oscillator will only be reactivated with reset. No post-switch clock monitor feature is implemented (clock does not switch back to internal if external clock dies).

### 11.3.2 External Oscillator

The external clock option is designed for use when a clock signal is available in the application to provide a clock source to the microcontroller. The OSC1 pin is enabled as an input by the oscillator module. The clock signal is used directly to create BUSCLKX4 and also divided by two to create BUSCLKX2.

In this configuration, the OSC2 pin cannot output BUSCLKX4.So the OSC2EN bit in the port A pullup enable register will be clear to enable PTA4 I/O functions on the pin

# Chapter 13 System Integration Module (SIM)

# **13.1 Introduction**

This section describes the system integration module (SIM), which supports up to 24 external and/or internal interrupts. Together with the central processor unit (CPU), the SIM controls all microcontroller unit (MCU) activities. A block diagram of the SIM is shown in Figure 13-1. The SIM is a system state controller that coordinates CPU and exception timing.

The SIM is responsible for:

- Bus clock generation and control for CPU and peripherals

- Stop/wait/reset/break entry and recovery

- Internal clock control

- Master reset control, including power-on reset (POR) and computer operating properly (COP) timeout

- Interrupt control:

- Acknowledge timing

- Arbitration control timing

- Vector address generation

- CPU enable/disable timing

| Signal Name | Description                                                                                                                                                |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BUSCLKX4    | Buffered clock from the internal, RC or XTAL oscillator circuit.                                                                                           |

| BUSCLKX2    | The BUSCLKX4 frequency divided by two. This signal is again divided by two in the SIM to generate the internal bus clocks (bus clock = BUSCLKX4 $\div$ 4). |

| Address bus | Internal address bus                                                                                                                                       |

| Data bus    | Internal data bus                                                                                                                                          |

| PORRST      | Signal from the power-on reset module to the SIM                                                                                                           |

| IRST        | Internal reset signal                                                                                                                                      |

| R/W         | Read/write signal                                                                                                                                          |

### Table 13-1. Signal Name Conventions

Figure 13-2. SIM Clock Signals

### 13.3.1 Bus Timing

In user mode, the internal bus frequency is the oscillator frequency (BUSCLKX4) divided by four.

### 13.3.2 Clock Start-Up from POR

When the power-on reset module generates a reset, the clocks to the CPU and peripherals are inactive and held in an inactive phase until after the 4096 BUSCLKX4 cycle POR time out has completed. The IBUS clocks start upon completion of the time out.

### 13.3.3 Clocks in Stop Mode and Wait Mode

Upon exit from stop mode by an interrupt or reset, the SIM allows BUSCLKX4 to clock the SIM counter. The CPU and peripheral clocks do not become active until after the stop delay time out. This time out is selectable as 4096 or 32 BUSCLKX4 cycles. See 13.7.2 Stop Mode.

In wait mode, the CPU clocks are inactive. The SIM also produces two sets of clocks for other modules. Refer to the wait mode subsection of each module to see if the module is active or inactive in wait mode. Some modules can be programmed to be active in wait mode.

## 13.4 Reset and System Initialization

The MCU has these reset sources:

- Power-on reset module (POR)

- External reset pin (RST)

- Computer operating properly module (COP)

- Low-voltage inhibit module (LVI)

- Illegal opcode

- Illegal address

All of these resets produce the vector \$FFFE\_FFF (\$FEFE\_FEFF in monitor mode) and assert the internal reset signal (IRST). IRST causes all registers to be returned to their default values and all modules to be returned to their reset states.

An internal reset clears the SIM counter (see 13.5 SIM Counter), but an external reset does not. Each of the resets sets a corresponding bit in the SIM reset status register (SRSR). See 13.8 SIM Registers.

A module that is active during wait mode can wake up the CPU with an interrupt if the interrupt is enabled. Stacking for the interrupt begins one cycle after the WAIT instruction during which the interrupt occurred. In wait mode, the CPU clocks are inactive. Refer to the wait mode subsection of each module to see if the module is active or inactive in wait mode. Some modules can be programmed to be active in wait mode.

Wait mode can also be exited by a reset (or break in emulation mode). A break interrupt during wait mode sets the SIM break stop/wait bit, SBSW, in the break status register (BSR). If the COP disable bit, COPD, in the configuration register is 0, then the computer operating properly module (COP) is enabled and remains active in wait mode.

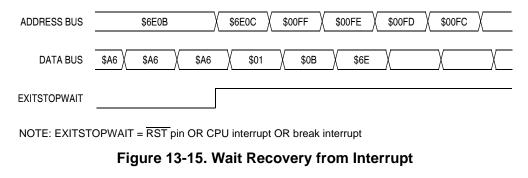

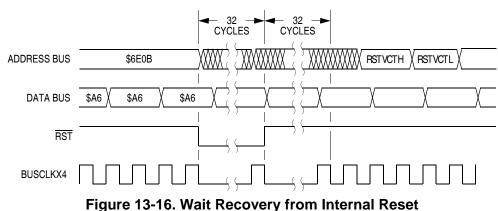

Figure 13-15 and Figure 13-16 show the timing for wait recovery.

# 13.7.2 Stop Mode

In stop mode, the SIM counter is reset and the system clocks are disabled. An interrupt request from a module can cause an exit from stop mode. Stacking for interrupts begins after the selected stop recovery time has elapsed. Reset or break also causes an exit from stop mode.

The SIM disables the oscillator signals (BUSCLKX2 and BUSCLKX4) in stop mode, stopping the CPU and peripherals. Stop recovery time is selectable using the SSREC bit in the configuration register 1 (CONFIG1). If SSREC is set, stop recovery is reduced from the normal delay of 4096 BUSCLKX4 cycles down to 32. This is ideal for the internal oscillator, RC oscillator, and external oscillator options which do not require long start-up times from stop mode.

### NOTE

External crystal applications should use the full stop recovery time by clearing the SSREC bit.

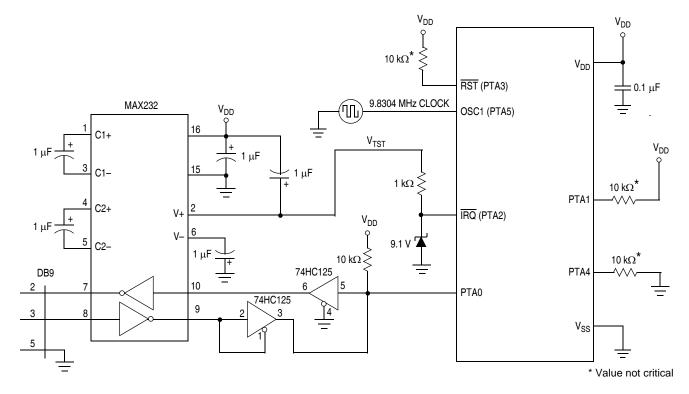

Figure 15-10. Monitor Mode Circuit (External Clock, with High Voltage)

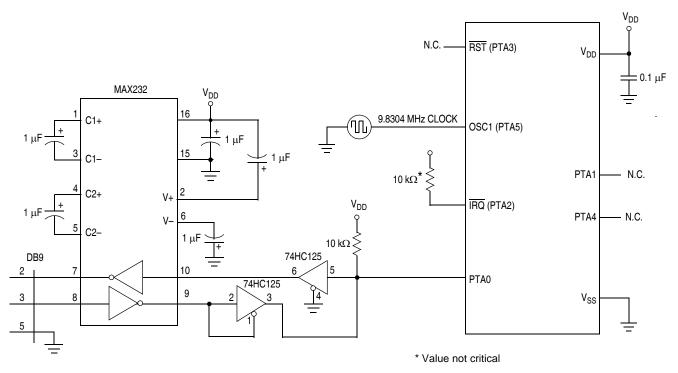

Figure 15-11. Monitor Mode Circuit (External Clock, No High Voltage)

# 16.5 5-V DC Electrical Characteristics

| Characteristic <sup>(1)</sup>                                                                                                                         | Symbol                              | Min                                                                  | Typ <sup>(2)</sup> | Max                   | Unit |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|----------------------------------------------------------------------|--------------------|-----------------------|------|

| Output high voltage<br>$I_{Load} = -2.0$ mA, all I/O pins<br>$I_{Load} = -10.0$ mA, all I/O pins<br>$I_{Load} = -15.0$ mA, PTA0, PTA1, PTA3–PTA5 only | V <sub>OH</sub>                     | V <sub>DD</sub> -0.4<br>V <sub>DD</sub> -1.5<br>V <sub>DD</sub> -0.8 |                    |                       | v    |

| Maximum combined I <sub>OH</sub> (all I/O pins)                                                                                                       | I <sub>OHT</sub>                    | —                                                                    | —                  | 50                    | mA   |

| Output low voltage<br>$I_{Load} = 1.6$ mA, all I/O pins<br>$I_{Load} = 10.0$ mA, all I/O pins<br>$I_{Load} = 15.0$ mA, PTA0, PTA1, PTA3–PTA5 only     | V <sub>OL</sub>                     | <br>                                                                 |                    | 0.4<br>1.5<br>0.8     | v    |

| Maximum combined I <sub>OL</sub> (all I/O pins)                                                                                                       | I <sub>OLT</sub>                    | —                                                                    | —                  | 50                    | mA   |

| Input high voltage<br>PTA0–PTA5, PTB0–PTB7                                                                                                            | V <sub>IH</sub>                     | 0.7 x V <sub>DD</sub>                                                | _                  | V <sub>DD</sub>       | V    |

| Input low voltage<br>PTA0–PTA5, PTB0–PTB7                                                                                                             | V <sub>IL</sub>                     | V <sub>SS</sub>                                                      | _                  | 0.3 x V <sub>DD</sub> | V    |

| Input hysteresis                                                                                                                                      | V <sub>HYS</sub>                    | 0.06 x V <sub>DD</sub>                                               | —                  | —                     | V    |

| DC injection current, all ports                                                                                                                       | I <sub>INJ</sub>                    | -2                                                                   | —                  | +2                    | mA   |

| Total dc current injection (sum of all I/O)                                                                                                           | I <sub>INJTOT</sub>                 | -25                                                                  | —                  | +25                   | mA   |

| Ports Hi-Z leakage current                                                                                                                            | IIL                                 | -1                                                                   | ±0.1               | +1                    | μA   |

| Capacitance<br>Ports (as input)<br>Ports (as input)                                                                                                   | C <sub>IN</sub><br>C <sub>OUT</sub> |                                                                      |                    | 12<br>8               | pF   |

| POR rearm voltage <sup>(3)</sup>                                                                                                                      | V <sub>POR</sub>                    | 0                                                                    | —                  | 100                   | mV   |

| POR rise time ramp rate <sup>(4)</sup>                                                                                                                | R <sub>POR</sub>                    | 0.035                                                                | —                  | _                     | V/ms |

| Monitor mode entry voltage                                                                                                                            | V <sub>TST</sub>                    | V <sub>DD</sub> + 2.5                                                | —                  | 9.1                   | V    |

| Pullup resistors <sup>(5)</sup><br>PTA0–PTA5, PTB0–PTB7                                                                                               | R <sub>PU</sub>                     | 16                                                                   | 26                 | 36                    | kΩ   |

| Low-voltage inhibit reset, trip falling voltage                                                                                                       | V <sub>TRIPF</sub>                  | 3.90                                                                 | 4.20               | 4.50                  | V    |

| Low-voltage inhibit reset, trip rising voltage                                                                                                        | V <sub>TRIPR</sub>                  | 4.00                                                                 | 4.30               | 4.60                  | V    |

| Low-voltage inhibit reset/recover hysteresis                                                                                                          | V <sub>HYS</sub>                    | _                                                                    | 100                | —                     | mV   |

1.  $V_{DD}$  = 4.5 to 5.5 Vdc,  $V_{SS}$  = 0 Vdc,  $T_A$  =  $T_L$  to  $T_H$ , unless otherwise noted. 2. Typical values reflect average measurements at midpoint of voltage range, 25•C only.

3. Maximum is highest voltage that POR is guaranteed.

4. If minimum V<sub>DD</sub> is not reached before the internal POR reset is released, the LVI will hold the part in reset until minimum  $V_{DD}$  is reached. 5.  $R_{PU}$  is measured at  $V_{DD}$  = 5.0 V.

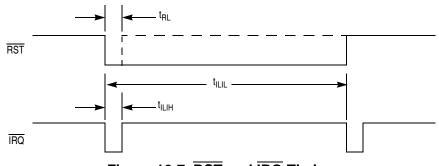

# 16.11 3-V Control Timing

| Characteristic <sup>(1)</sup>                  | Symbol                              | Min                 | Max | Unit             |

|------------------------------------------------|-------------------------------------|---------------------|-----|------------------|

| Internal operating frequency                   | f <sub>OP</sub> (f <sub>Bus</sub> ) | -                   | 4   | MHz              |

| Internal clock period (1/f <sub>OP</sub> )     | t <sub>cyc</sub>                    | 250                 | _   | ns               |

| RST input pulse width low                      | t <sub>RL</sub>                     | 200                 |     | ns               |

| IRQ interrupt pulse width low (edge-triggered) | t <sub>ILIH</sub>                   | 200                 | _   | ns               |

| IRQ interrupt pulse period                     | t <sub>ILIL</sub>                   | Note <sup>(2)</sup> |     | t <sub>cyc</sub> |

1. V<sub>DD</sub> = 2.7 to 3.3 Vdc, V<sub>SS</sub> = 0 Vdc, T<sub>A</sub> = T<sub>L</sub> to T<sub>H</sub>; timing shown with respect to 20% V<sub>DD</sub> and 70% V<sub>DD</sub>, unless otherwise noted.

2. The minimum period is the number of cycles it takes to execute the interrupt service routine plus 1  $t_{cyc}$ .

Figure 16-7. RST and IRQ Timing

**Electrical Specifications**

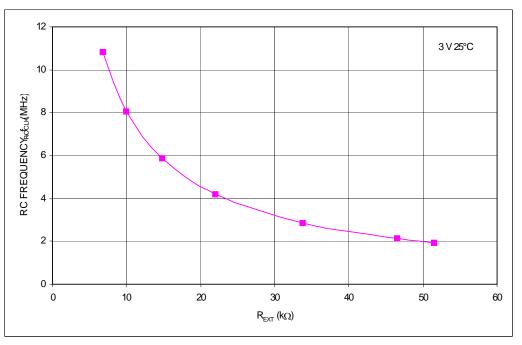

# 16.12 3-V Oscillator Characteristics

| Characteristic                                                                                                                                                                               | Symbol               | Min | Тур                | Max  | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----|--------------------|------|------|

| Internal oscillator frequency <sup>(1)</sup>                                                                                                                                                 | <b>f</b> INTCLK      | —   | 12.8               | —    | MHz  |

| Deviation from trimmed Internal oscillator $^{(2)(3)}$<br>12.8 MHz, fixed voltage, fixed temp<br>12.8 MHz, V <sub>DD</sub> ± 10%, 0 to 70°C<br>12.8 MHz, V <sub>DD</sub> ± 10%, -40 to 125°C | ACCINT               |     | ± 0.4<br>± 2<br>—  | <br> | %    |

| Crystal frequency, XTALCLK <sup>(1)</sup>                                                                                                                                                    | foscxclk             | 1   | —                  | 16   | MHz  |

| External RC oscillator frequency, RCCLK (1)                                                                                                                                                  | f <sub>RCCLK</sub>   | 2   | —                  | 10   | MHz  |

| External clock reference frequency <sup>(1) (4)</sup>                                                                                                                                        | f <sub>OSCXCLK</sub> | dc  | —                  | 16   | MHz  |

| Crystal load capacitance <sup>(5)</sup>                                                                                                                                                      | CL                   | —   | 20                 | —    | pF   |

| Crystal fixed capacitance <sup>(3)</sup>                                                                                                                                                     | C <sub>1</sub>       | —   | 2 x C <sub>L</sub> | —    | —    |

| Crystal tuning capacitance <sup>(3)</sup>                                                                                                                                                    | C <sub>2</sub>       | —   | 2 x C <sub>L</sub> | —    | —    |

| Feedback bias resistor                                                                                                                                                                       | R <sub>B</sub>       | 0.5 | 1                  | 10   | MΩ   |

| RC oscillator external resistor                                                                                                                                                              | R <sub>EXT</sub>     | S   | See Figure 16-     | 8    | —    |

| Crystal series damping resistor<br>$f_{OSCXCLK} = 1 MHz$<br>$f_{OSCXCLK} = 4 MHz$<br>$f_{OSCXCLK} = > 8 MHz$                                                                                 | R <sub>S</sub>       |     | 10<br>5<br>0       |      | kΩ   |

Bus frequency, f<sub>OP</sub>, is oscillator frequency divided by 4.

Deviation values assumes trimming @25•C and midpoint of voltage range.

Values are based on characterization results, not tested in production.

4. No more than 10% duty cycle deviation from 50%

5. Consult crystal vendor data sheet

Figure 16-8. RC versus Frequency (3 Volts @ 25•C)

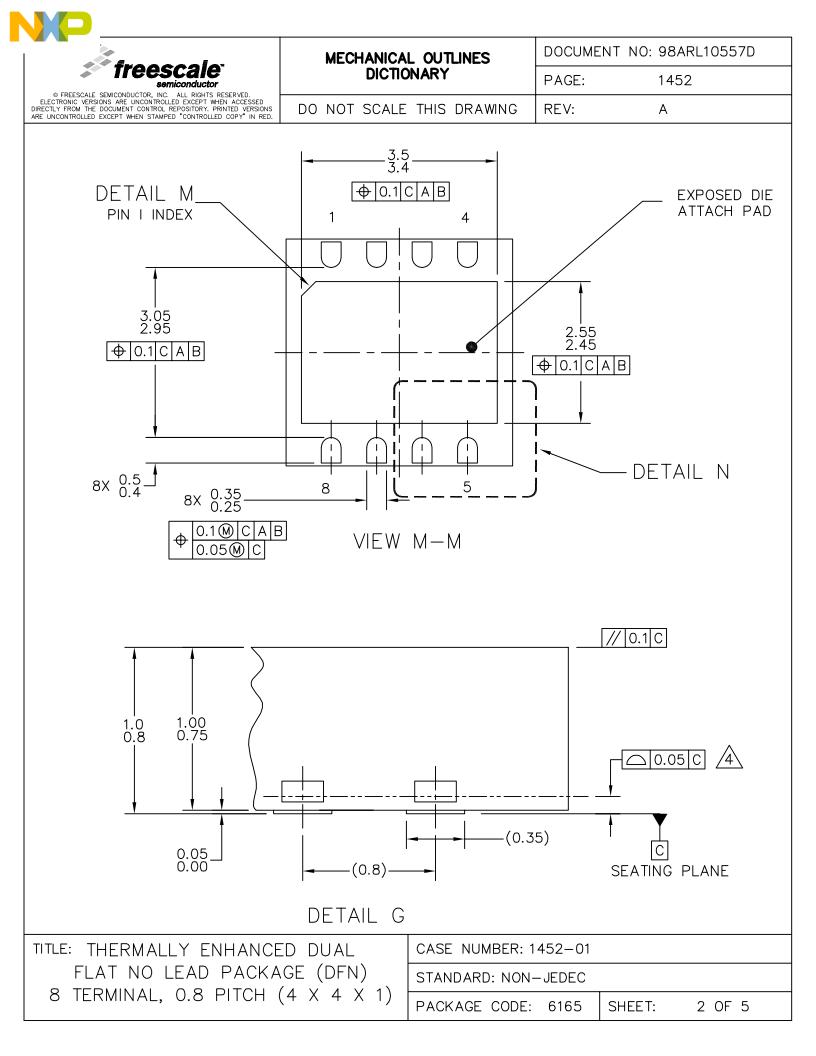

| <br>          |                                                                                                                                                       | ME    | CHANICA | L OUTI | INES    | DOCUMENT N | NO: 98ARL10557D |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---------|--------|---------|------------|-----------------|

| © FREESCALE S | FICESCALE<br>semiconcluctor<br>EMICONDUCTOR, INC. ALL RIGHTS RESERVED.                                                                                |       | DICTI   | ONARY  |         | PAGE:      | 1452            |

| DIRECTLY FROM | IONS ARE UNCONTROLLED EXCEPT WHEN ACCESSED<br>THE DOCUMENT CONTROL REPOSITORY. PRINTED<br>CONTROLLED EXCEPT WHEN STAMPED "CONTROLLED<br>COPY" IN RED. | DO NO | T SCALE | THIS   | DRAWING | REV:       | A               |

NOTES:

- 1. ALL DIMENSIONS ARE IN MILLIMETERS.

- 2. INTERPRET DIMENSIONS AND TOLERANCES PER ASME Y14.5M-1994.

- 3. THE COMPLETE JEDEC DESIGNATOR FOR THIS PACKAGE IS: HP-VFDFP-N.

4. COPLANARITY APPLIES TO LEADS AND DIE ATTACH PAD.

| TITLE:THERMALLY ENHANCED DUAL                  | CASE NUMBER: 1452-01             |

|------------------------------------------------|----------------------------------|

| FLAT NO LEAD PACKAGE (DFN)                     | STANDARD: NON-JEDEC              |

| 8 TERMINAL, 0. 8 PITCH $(4 \times 4 \times 1)$ | PACKAGE CODE: 6165 SHEET: 4 OF 5 |

#### How to Reach Us:

Home Page: www.freescale.com

E-mail: support@freescale.com

#### USA/Europe or Locations Not Listed:

Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 +1-800-521-6274 or +1-480-768-2130 support@freescale.com

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street Tai Po Industrial Estate Tai Po, N.T., Hong Kong +800 2666 8080 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 1-800-441-2447 or 303-675-2140 Fax: 303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc. 2005–2010. All rights reserved.

MC68HC908QY4 Rev. 6, 03/2010