Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                       |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | HC08                                                         |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 8MHz                                                         |

| Connectivity               | -                                                            |

| Peripherals                | LVD, POR, PWM                                                |

| Number of I/O              | 13                                                           |

| Program Memory Size        | 4KB (4K x 8)                                                 |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | -                                                            |

| RAM Size                   | 128 x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                  |

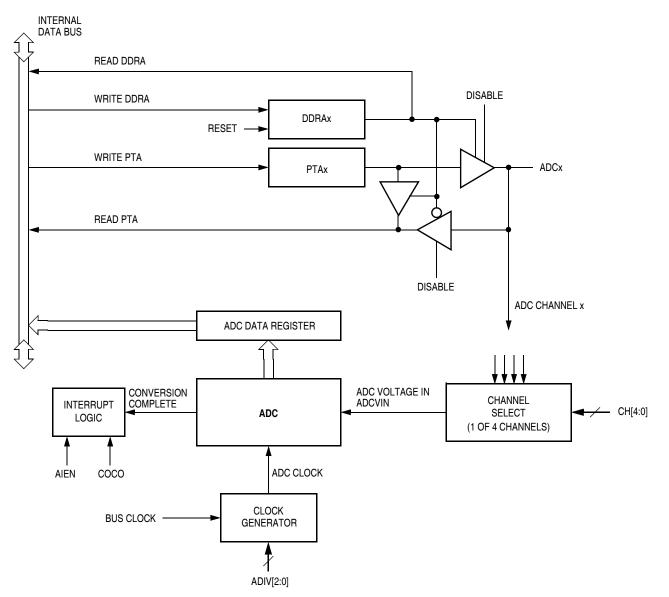

| Data Converters            | A/D 4x8b                                                     |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                           |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 16-SOIC (0.295", 7.50mm Width)                               |

| Supplier Device Package    | 16-SOIC                                                      |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mchc908qy4mdwer |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

**Table of Contents**

# Chapter 1 General Description

# **1.1 Introduction**

The MC68HC908QY4 is a member of the low-cost, high-performance M68HC08 Family of 8-bit microcontroller units (MCUs). The M68HC08 Family is a Complex Instruction Set Computer (CISC) with a Von Neumann architecture. All MCUs in the family use the enhanced M68HC08 central processor unit (CPU08) and are available with a variety of modules, memory sizes and types, and package types.

| Device       | FLASH<br>Memory Size | Analog-to-Digital<br>Converter | Pin<br>Count |

|--------------|----------------------|--------------------------------|--------------|

| MC68HC908QT1 | 1536 bytes           | —                              | 8 pins       |

| MC68HC908QT2 | 1536 bytes           | 4 ch, 8 bit                    | 8 pins       |

| MC68HC908QT4 | 4096 bytes           | 4 ch, 8 bit                    | 8 pins       |

| MC68HC908QY1 | 1536 bytes           | —                              | 16 pins      |

| MC68HC908QY2 | 1536 bytes           | 4 ch, 8 bit                    | 16 pins      |

| MC68HC908QY4 | 4096 bytes           | 4 ch, 8 bit                    | 16 pins      |

Table 1-1. Summary of Device Variations

# **1.2 Features**

Features include:

- High-performance M68HC08 CPU core

- Fully upward-compatible object code with M68HC05 Family

- 5-V and 3-V operating voltages (V<sub>DD</sub>)

- 8-MHz internal bus operation at 5 V, 4-MHz at 3 V

- Trimmable internal oscillator

- 3.2 MHz internal bus operation

- 8-bit trim capability allows 0.4% accuracy<sup>(1)</sup>

- ± 25% untrimmed

- Auto wakeup from STOP capability

- Configuration (CONFIG) register for MCU configuration options, including:

- Low-voltage inhibit (LVI) trip point

- In-system FLASH programming

- FLASH security<sup>(2)</sup>

<sup>1.</sup> The oscillator frequency is guaranteed to  $\pm 5\%$  over temperature and voltage range after trimming.

No security feature is absolutely secure. However, Freescale's strategy is to make reading or copying the FLASH difficult for unauthorized users.

# **1.6 Pin Function Priority**

Table 1-3 is meant to resolve the priority if multiple functions are enabled on a single pin.

NOTE

Upon reset all pins come up as input ports regardless of the priority table.

| Pin Name | Highest-to-Lowest Priority Sequence                                                             |

|----------|-------------------------------------------------------------------------------------------------|

| PTA0     | $AD0 \rightarrow TCH0 \rightarrow KBI0 \rightarrow PTA0$                                        |

| PTA1     | $AD1 \rightarrow TCH1 \rightarrow KBI1 \rightarrow PTA1$                                        |

| PTA2     | $\overline{\text{IRQ}} \rightarrow \text{KBI2} \rightarrow \text{TCLK} \rightarrow \text{PTA2}$ |

| PTA3     | $\overline{\text{RST}} \rightarrow \text{KBI3} \rightarrow \text{PTA3}$                         |

| PTA4     | $OSC2 \rightarrow AD2 \rightarrow KBI4 \rightarrow PTA4$                                        |

| PTA5     | $OSC1 \rightarrow AD3 \rightarrow KBI5 \rightarrow PTA5$                                        |

### Table 1-3. Function Priority in Shared Pins

**Functional Description**

#### **Configuration Register (CONFIG)**

#### IRQPUD — IRQ Pin Pullup Control Bit

- 1 = Internal pullup is disconnected

- 0 = Internal pullup is connected between  $\overline{IRQ}$  pin and  $V_{DD}$

#### IRQEN — IRQ Pin Function Selection Bit

- 1 = Interrupt request function active in pin

- 0 = Interrupt request function inactive in pin

#### OSCOPT1 and OSCOPT0 — Selection Bits for Oscillator Option

- (0, 0) Internal oscillator

- (0, 1) External oscillator

- (1, 0) External RC oscillator

- (1, 1) External XTAL oscillator

### **RSTEN** — **RST** Pin Function Selection

- 1 = Reset function active in pin

- 0 =Reset function inactive in pin

#### NOTE

The RSTEN bit is cleared by a power-on reset (POR) only. Other resets will leave this bit unaffected.

Address: \$001F

|                 | Bit 7 | 6       | 5       | 4       | 3       | 2     | 1    | Bit 0 |

|-----------------|-------|---------|---------|---------|---------|-------|------|-------|

| Read:<br>Write: | COPRS | LVISTOP | LVIRSTD | LVIPWRD | LVI5OR3 | SSREC | STOP | COPD  |

| Reset:          | 0     | 0       | 0       | 0       | U       | 0     | 0    | 0     |

| POR:            | 0     | 0       | 0       | 0       | 0       | 0     | 0    | 0     |

|                 |       |         |         |         |         |       |      |       |

U = Unaffected

#### Figure 5-2. Configuration Register 1 (CONFIG1)

#### COPRS (Out of STOP Mode) — COP Reset Period Selection Bit

- 1 = COP reset short cycle = 8176 × BUSCLKX4

- $0 = COP reset long cycle = 262,128 \times BUSCLKX4$

#### COPRS (In STOP Mode) — Auto Wakeup Period Selection Bit

- 1 = Auto wakeup short cycle =  $512 \times INTRCOSC$

- $0 = Auto wakeup long cycle = 16,384 \times INTRCOSC$

#### LVISTOP — LVI Enable in Stop Mode Bit

When the LVIPWRD bit is clear, setting the LVISTOP bit enables the LVI to operate during stop mode. Reset clears LVISTOP.

1 = LVI enabled during stop mode

0 = LVI disabled during stop mode

#### LVIRSTD — LVI Reset Disable Bit

LVIRSTD disables the reset signal from the LVI module.

1 = LVI module resets disabled

0 = LVI module resets enabled

### Z — Zero Flag

The CPU sets the zero flag when an arithmetic operation, logic operation, or data manipulation produces a result of \$00.

- 1 = Zero result

- 0 = Non-zero result

### C — Carry/Borrow Flag

The CPU sets the carry/borrow flag when an addition operation produces a carry out of bit 7 of the accumulator or when a subtraction operation requires a borrow. Some instructions — such as bit test and branch, shift, and rotate — also clear or set the carry/borrow flag.

1 = Carry out of bit 7

0 = No carry out of bit 7

# 7.4 Arithmetic/Logic Unit (ALU)

The ALU performs the arithmetic and logic operations defined by the instruction set.

Refer to the *CPU08 Reference Manual* (document order number CPU08RM/AD) for a description of the instructions and addressing modes and more detail about the architecture of the CPU.

# 7.5 Low-Power Modes

The WAIT and STOP instructions put the MCU in low power-consumption standby modes.

### 7.5.1 Wait Mode

The WAIT instruction:

- Clears the interrupt mask (I bit) in the condition code register, enabling interrupts. After exit from wait mode by interrupt, the I bit remains clear. After exit by reset, the I bit is set.

- Disables the CPU clock

## 7.5.2 Stop Mode

The STOP instruction:

- Clears the interrupt mask (I bit) in the condition code register, enabling external interrupts. After exit from stop mode by external interrupt, the I bit remains clear. After exit by reset, the I bit is set.

- Disables the CPU clock

After exiting stop mode, the CPU clock begins running after the oscillator stabilization delay.

# 7.6 CPU During Break Interrupts

If a break module is present on the MCU, the CPU starts a break interrupt by:

- Loading the instruction register with the SWI instruction

- Loading the program counter with \$FFFC:\$FFFD or with \$FEFC:\$FEFD in monitor mode

The break interrupt begins after completion of the CPU instruction in progress. If the break address register match occurs on the last cycle of a CPU instruction, the break interrupt begins immediately.

A return-from-interrupt instruction (RTI) in the break routine ends the break interrupt and returns the MCU to normal operation if the break interrupt has been deasserted.

\_\_\_\_\_

| Source                                                                                         | Operation                                         | Description                                                                                                                                                                                                                                                                                                                                   |   |   |   | fect<br>CCR |   |   | Effect<br>n CCR                                                                                          |                                                  |                                                                               |                                      | Opcode | Operand | es |

|------------------------------------------------------------------------------------------------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|-------------|---|---|----------------------------------------------------------------------------------------------------------|--------------------------------------------------|-------------------------------------------------------------------------------|--------------------------------------|--------|---------|----|

| Form                                                                                           | • • • • • • • •                                   | p                                                                                                                                                                                                                                                                                                                                             | v | Н | I | Ν           | Ζ | С | Add<br>Moc                                                                                               | opc                                              | Ope                                                                           | Cycles                               |        |         |    |

| BHS rel                                                                                        | Branch if Higher or Same<br>(Same as BCC)         | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (C) = 0$                                                                                                                                                                                                                                                                                             | - | - | - | Ι           | - | - | REL                                                                                                      | 24                                               | rr                                                                            | 3                                    |        |         |    |

| BIH rel                                                                                        | Branch if IRQ Pin High                            | $PC \leftarrow (PC) + 2 + rel ? \overline{IRQ} = 1$                                                                                                                                                                                                                                                                                           | - | - | - | -           | - | - | REL                                                                                                      | 2F                                               | rr                                                                            | 3                                    |        |         |    |

| BIL rel                                                                                        | Branch if IRQ Pin Low                             | $PC \leftarrow (PC) + 2 + \mathit{rel} ? \overline{IRQ} = 0$                                                                                                                                                                                                                                                                                  | - | - | - | -           | - | - | REL                                                                                                      | 2E                                               | rr                                                                            | 3                                    |        |         |    |

| BIT #opr<br>BIT opr<br>BIT opr<br>BIT opr,X<br>BIT opr,X<br>BIT ,X<br>BIT opr,SP<br>BIT opr,SP | Bit Test                                          | (A) & (M)                                                                                                                                                                                                                                                                                                                                     | 0 | _ | 1 | ţ           | ţ | _ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2                                                      | A5<br>B5<br>C5<br>D5<br>E5<br>F5<br>9ED5<br>9ED5 | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ee ff                                     | 23443245                             |        |         |    |

| BLE opr                                                                                        | Branch if Less Than or Equal To (Signed Operands) | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (Z) \mid (N \oplus V) = 1$                                                                                                                                                                                                                                                                           | - | - | - | I           | 1 | - | REL                                                                                                      | 93                                               | rr                                                                            | 3                                    |        |         |    |

| BLO rel                                                                                        | Branch if Lower (Same as BCS)                     | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (C) = 1$                                                                                                                                                                                                                                                                                             | — | - |   | -           | I | - | REL                                                                                                      | 25                                               | rr                                                                            | 3                                    |        |         |    |

| BLS rel                                                                                        | Branch if Lower or Same                           | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (C) \mid (Z) = 1$                                                                                                                                                                                                                                                                                    | - | - | - | -           | Ι | - | REL                                                                                                      | 23                                               | rr                                                                            | 3                                    |        |         |    |

| BLT opr                                                                                        | Branch if Less Than (Signed Operands)             | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (N \oplus V) = 1$                                                                                                                                                                                                                                                                                    | - | - | - | -           | - | - | REL                                                                                                      | 91                                               | rr                                                                            | 3                                    |        |         |    |

| BMC rel                                                                                        | Branch if Interrupt Mask Clear                    | $PC \leftarrow (PC) + 2 + rel? (I) = 0$                                                                                                                                                                                                                                                                                                       | - | - | - | -           | - | - | REL                                                                                                      | 2C                                               | rr                                                                            | 3                                    |        |         |    |

| BMI rel                                                                                        | Branch if Minus                                   | PC ← (PC) + 2 + <i>rel</i> ? (N) = 1                                                                                                                                                                                                                                                                                                          | - | - | - | -           | I | - | REL                                                                                                      | 2B                                               | rr                                                                            | 3                                    |        |         |    |

| BMS rel                                                                                        | Branch if Interrupt Mask Set                      | PC ← (PC) + 2 + <i>rel</i> ? (I) = 1                                                                                                                                                                                                                                                                                                          | - | - | - | -           | - | - | REL                                                                                                      | 2D                                               | rr                                                                            | 3                                    |        |         |    |

| BNE rel                                                                                        | Branch if Not Equal                               | $PC \leftarrow (PC) + 2 + rel? (Z) = 0$                                                                                                                                                                                                                                                                                                       | - | - | - | -           | Ι | - | REL                                                                                                      | 26                                               | rr                                                                            | 3                                    |        |         |    |

| BPL rel                                                                                        | Branch if Plus                                    | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (N) = 0$                                                                                                                                                                                                                                                                                             | - | Ι | - | -           | I | - | REL                                                                                                      | 2A                                               | rr                                                                            | 3                                    |        |         |    |

| BRA rel                                                                                        | Branch Always                                     | $PC \leftarrow (PC) + 2 + \mathit{rel}$                                                                                                                                                                                                                                                                                                       | - | Ι | - | -           | I | - | REL                                                                                                      | 20                                               | rr                                                                            | 3                                    |        |         |    |

| BRCLR n,opr,rel                                                                                | Branch if Bit <i>n</i> in M Clear                 | PC ← (PC) + 3 + <i>rel</i> ? (Mn) = 0                                                                                                                                                                                                                                                                                                         | _ | _ | _ | _           | _ | ţ | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7) | 01<br>03<br>05<br>07<br>09<br>0B<br>0D<br>0F     | dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr | 55555555                             |        |         |    |

| BRN rel                                                                                        | Branch Never                                      | $PC \leftarrow (PC) + 2$                                                                                                                                                                                                                                                                                                                      | - | - | - | -           | I | - | REL                                                                                                      | 21                                               | rr                                                                            | 3                                    |        |         |    |

| BRSET n,opr,rel                                                                                | Branch if Bit <i>n</i> in M Set                   | PC ← (PC) + 3 + <i>rel</i> ? (Mn) = 1                                                                                                                                                                                                                                                                                                         | _ | _ | - | _           | _ | ţ | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7)             | 00<br>02<br>04<br>06<br>08<br>0A<br>0C<br>0E     | dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr | 555555555                            |        |         |    |

| BSET n,opr                                                                                     | Set Bit <i>n</i> in M                             | Mn ← 1                                                                                                                                                                                                                                                                                                                                        | _ | _ | _ | _           | _ | _ | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7)             | 10<br>12<br>14<br>16<br>18<br>1A<br>1C<br>1E     | dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd                            | 4<br>4<br>4<br>4<br>4<br>4<br>4<br>4 |        |         |    |

| BSR rel                                                                                        | Branch to Subroutine                              | $\begin{array}{l} PC \leftarrow (PC) + 2;  push \; (PCL) \\ SP \leftarrow (SP) - 1;  push \; (PCH) \\ & SP \leftarrow (SP) - 1 \\ & PC \leftarrow (PC) + \mathit{rel} \end{array}$                                                                                                                                                            | _ | _ | _ | _           | - | _ | REL                                                                                                      | AD                                               | rr                                                                            | 4                                    |        |         |    |

| CBEQ X+,rel<br>CBEQ<br>opr,SP,rel                                                              | Compare and Branch if Equal                       | $\begin{array}{l} PC \leftarrow (PC) + 3 + rel ? (A) - (M) = \$00 \\ PC \leftarrow (PC) + 3 + rel ? (A) - (M) = \$00 \\ PC \leftarrow (PC) + 3 + rel ? (X) - (M) = \$00 \\ PC \leftarrow (PC) + 3 + rel ? (A) - (M) = \$00 \\ PC \leftarrow (PC) + 2 + rel ? (A) - (M) = \$00 \\ PC \leftarrow (PC) + 4 + rel ? (A) - (M) = \$00 \end{array}$ | _ | _ | _ | _           | - | _ | DIR<br>IMM<br>IX1+<br>IX+<br>SP1                                                                         |                                                  | dd rr<br>ii rr<br>ii rr<br>ff rr<br>rr<br>ff rr                               | 5<br>4<br>4<br>5<br>4<br>6           |        |         |    |

| CLC                                                                                            | Clear Carry Bit                                   | C ← 0                                                                                                                                                                                                                                                                                                                                         | - | - | - | -           | - | 0 | INH                                                                                                      | 98                                               |                                                                               | 1                                    |        |         |    |

| Table 7-1. | Instruction | Set | Summary | , ( | (Sheet 2 of 6) |

|------------|-------------|-----|---------|-----|----------------|

|            |             | 000 | Cannary |     |                |

**Central Processor Unit (CPU)**

| Source                                                                                         | Operation                                                         | Description                                                                                                                                                                                                                               |   |   |   |   |   |   | Address<br>Mode                                     | Opcode                                           | Operand                             | es                              |

|------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|---|---|---|-----------------------------------------------------|--------------------------------------------------|-------------------------------------|---------------------------------|

| Form                                                                                           | - Portanen                                                        |                                                                                                                                                                                                                                           | ۷ | н | I | Ν | z | С | Add<br>Mod                                          | Opc                                              | Ope                                 | Cycles                          |

| PULA                                                                                           | Pull A from Stack                                                 | $SP \leftarrow (SP + 1); Pull (A)$                                                                                                                                                                                                        | - | - | - | - | - | - | INH                                                 | 86                                               |                                     | 2                               |

| PULH                                                                                           | Pull H from Stack                                                 | $SP \leftarrow (SP + 1); Pull (H)$                                                                                                                                                                                                        | - | - | - | - | - | - | INH                                                 | 8A                                               |                                     | 2                               |

| PULX                                                                                           | Pull X from Stack                                                 | $SP \leftarrow (SP + 1); Pull (X)$                                                                                                                                                                                                        | - | - | - | - | - | - | INH                                                 | 88                                               |                                     | 2                               |

| ROL opr<br>ROLA<br>ROLX<br>ROL opr,X<br>ROL ,X<br>ROL opr,SP                                   | Rotate Left through Carry                                         | C ← [] ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓                                                                                                                                                                                                | ţ | _ | _ | ţ | ţ | ţ | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 39<br>49<br>59<br>69<br>79<br>9E69               | dd<br>ff<br>ff                      | 4<br>1<br>4<br>3<br>5           |

| ROR opr<br>RORA<br>RORX<br>ROR opr,X<br>ROR ,X<br>ROR opr,SP                                   | Rotate Right through Carry                                        | b7 b0                                                                                                                                                                                                                                     | ţ | _ | _ | ţ | ţ | ţ | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 36<br>46<br>56<br>66<br>76<br>9E66               | dd<br>ff<br>ff                      | 4<br>1<br>4<br>3<br>5           |

| RSP                                                                                            | Reset Stack Pointer                                               | $SP \leftarrow \$FF$                                                                                                                                                                                                                      | - | - | - | - | - | - | INH                                                 | 9C                                               |                                     | 1                               |

| RTI                                                                                            | Return from Interrupt                                             | $\begin{array}{l} SP \leftarrow (SP) + 1; \ Pull \ (CCR) \\ SP \leftarrow (SP) + 1; \ Pull \ (A) \\ SP \leftarrow (SP) + 1; \ Pull \ (X) \\ SP \leftarrow (SP) + 1; \ Pull \ (PCH) \\ SP \leftarrow (SP) + 1; \ Pull \ (PCL) \end{array}$ | t | ţ | ţ | ţ | ţ | ţ | INH                                                 | 80                                               |                                     | 7                               |

| RTS                                                                                            | Return from Subroutine                                            | $SP \leftarrow SP + 1$ ; Pull (PCH)<br>$SP \leftarrow SP + 1$ ; Pull (PCL)                                                                                                                                                                | - | - | - | - | - | - | INH                                                 | 81                                               |                                     | 4                               |

| SBC #opr<br>SBC opr<br>SBC opr<br>SBC opr,X<br>SBC opr,X<br>SBC ,X<br>SBC opr,SP<br>SBC opr,SP | Subtract with Carry                                               | $A \leftarrow (A) - (M) - (C)$                                                                                                                                                                                                            | ţ | _ | _ | ţ | ţ | ţ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | A2<br>B2<br>C2<br>D2<br>E2<br>F2<br>9EE2<br>9ED2 |                                     | 23443245                        |

| SEC                                                                                            | Set Carry Bit                                                     | C ← 1                                                                                                                                                                                                                                     | - | - | - | - | - | 1 | INH                                                 | 99                                               |                                     | 1                               |

| SEI                                                                                            | Set Interrupt Mask                                                | l ← 1                                                                                                                                                                                                                                     | - | - | 1 | - | - | - | INH                                                 | 9B                                               |                                     | 2                               |

| STA opr<br>STA opr<br>STA opr,X<br>STA opr,X<br>STA ,X<br>STA opr,SP<br>STA opr,SP             | Store A in M                                                      | M ← (A)                                                                                                                                                                                                                                   | 0 | _ | _ | ţ | ţ | _ | DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2        | B7<br>C7<br>D7<br>E7<br>F7<br>9EE7<br>9ED7       | dd<br>hh II<br>ee ff<br>ff<br>ee ff | 3<br>4<br>4<br>3<br>2<br>4<br>5 |

| STHX opr                                                                                       | Store H:X in M                                                    | (M:M + 1) ← (H:X)                                                                                                                                                                                                                         | 0 | - | - | 1 | 1 | - | DIR                                                 | 35                                               | dd                                  | 4                               |

| STOP                                                                                           | Enable Interrupts, Stop Processing,<br>Refer to MCU Documentation | $I \leftarrow 0$ ; Stop Processing                                                                                                                                                                                                        | - | - | 0 | - | - | - | INH                                                 | 8E                                               |                                     | 1                               |

| STX opr<br>STX opr<br>STX opr,X<br>STX opr,X<br>STX ,X<br>STX opr,SP<br>STX opr,SP             | Store X in M                                                      | M ← (X)                                                                                                                                                                                                                                   | 0 | _ | _ | ţ | ţ | _ | DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2        | BF<br>CF<br>DF<br>EF<br>FF<br>9EEF<br>9EDF       | dd<br>hh II<br>ee ff<br>ff<br>ee ff | 3<br>4<br>3<br>2<br>4<br>5      |

| SUB #opr<br>SUB opr<br>SUB opr<br>SUB opr,X<br>SUB opr,X<br>SUB opr,SP<br>SUB opr,SP           | Subtract                                                          | A ← (A) – (M)                                                                                                                                                                                                                             | ţ | _ | _ | ţ | ţ | ţ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | A0<br>B0<br>C0<br>D0<br>E0<br>F0<br>9EE0<br>9ED0 |                                     | 2<br>3<br>4<br>3<br>2<br>4<br>5 |

To protect the latch during the break state, write a 0 to the BCFE bit. With BCFE at 0 (its default state), writing to the keyboard acknowledge bit (ACKK) in the keyboard status and control register during the break state has no effect.

# 9.7 Input/Output Registers

The following I/O registers control and monitor operation of the keyboard interrupt module:

- Keyboard interrupt status and control register (KBSCR)

- Keyboard interrupt enable register (KBIER)

### 9.7.1 Keyboard Status and Control Register

The keyboard status and control register (KBSCR):

- Flags keyboard interrupt requests

- Acknowledges keyboard interrupt requests

- Masks keyboard interrupt requests

- Controls keyboard interrupt triggering sensitivity

Address: \$001A Bit 7 6 5 4 3 2 1 Bit 0 0 0 0 0 **KEYF** 0 Read: IMASKK MODFK ACKK Write: 0 Reset: 0 0 0 0 0 0 0 = Unimplemented

### Figure 9-3. Keyboard Status and Control Register (KBSCR)

#### Bits 7-4 — Not used

These read-only bits always read as 0s.

#### **KEYF** — Keyboard Flag Bit

This read-only bit is set when a keyboard interrupt is pending on port A or auto wakeup. Reset clears the KEYF bit.

- 1 = Keyboard interrupt pending

- 0 = No keyboard interrupt pending

#### ACKK — Keyboard Acknowledge Bit

Writing a 1 to this write-only bit clears the keyboard interrupt request on port A and auto wakeup logic. ACKK always reads as 0. Reset clears ACKK.

#### IMASKK— Keyboard Interrupt Mask Bit

Writing a 1 to this read/write bit prevents the output of the keyboard interrupt mask from generating interrupt requests on port A or auto wakeup. Reset clears the IMASKK bit.

1 = Keyboard interrupt requests masked

0 = Keyboard interrupt requests not masked

#### MODEK — Keyboard Triggering Sensitivity Bit

This read/write bit controls the triggering sensitivity of the keyboard interrupt pins on port A and auto wakeup. Reset clears MODEK.

1 = Keyboard interrupt requests on falling edges and low levels

0 = Keyboard interrupt requests on falling edges only

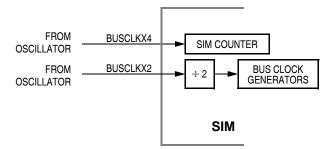

Figure 13-2. SIM Clock Signals

## 13.3.1 Bus Timing

In user mode, the internal bus frequency is the oscillator frequency (BUSCLKX4) divided by four.

### 13.3.2 Clock Start-Up from POR

When the power-on reset module generates a reset, the clocks to the CPU and peripherals are inactive and held in an inactive phase until after the 4096 BUSCLKX4 cycle POR time out has completed. The IBUS clocks start upon completion of the time out.

### 13.3.3 Clocks in Stop Mode and Wait Mode

Upon exit from stop mode by an interrupt or reset, the SIM allows BUSCLKX4 to clock the SIM counter. The CPU and peripheral clocks do not become active until after the stop delay time out. This time out is selectable as 4096 or 32 BUSCLKX4 cycles. See 13.7.2 Stop Mode.

In wait mode, the CPU clocks are inactive. The SIM also produces two sets of clocks for other modules. Refer to the wait mode subsection of each module to see if the module is active or inactive in wait mode. Some modules can be programmed to be active in wait mode.

# 13.4 Reset and System Initialization

The MCU has these reset sources:

- Power-on reset module (POR)

- External reset pin (RST)

- Computer operating properly module (COP)

- Low-voltage inhibit module (LVI)

- Illegal opcode

- Illegal address

All of these resets produce the vector \$FFFE\_FFF (\$FEFE\_FEFF in monitor mode) and assert the internal reset signal (IRST). IRST causes all registers to be returned to their default values and all modules to be returned to their reset states.

An internal reset clears the SIM counter (see 13.5 SIM Counter), but an external reset does not. Each of the resets sets a corresponding bit in the SIM reset status register (SRSR). See 13.8 SIM Registers.

#### Timer Interface Module (TIM)

#### TRST — TIM Reset Bit

Setting this write-only bit resets the TIM counter and the TIM prescaler. Setting TRST has no effect on any other registers. Counting resumes from \$0000. TRST is cleared automatically after the TIM counter is reset and always reads as a 0. Reset clears the TRST bit.

1 = Prescaler and TIM counter cleared

0 = No effect

#### NOTE

Setting the TSTOP and TRST bits simultaneously stops the TIM counter at a value of \$0000.

#### PS[2:0] — Prescaler Select Bits

These read/write bits select either the PTA2/TCLK pin or one of the seven prescaler outputs as the input to the TIM counter as Table 14-2 shows. Reset clears the PS[2:0] bits.

| PS2 | PS1 | PS0 | TIM Clock Source        |

|-----|-----|-----|-------------------------|

| 0   | 0   | 0   | Internal bus clock ÷ 1  |

| 0   | 0   | 1   | Internal bus clock ÷ 2  |

| 0   | 1   | 0   | Internal bus clock ÷ 4  |

| 0   | 1   | 1   | Internal bus clock ÷ 8  |

| 1   | 0   | 0   | Internal bus clock ÷ 16 |

| 1   | 0   | 1   | Internal bus clock ÷ 32 |

| 1   | 1   | 0   | Internal bus clock ÷ 64 |

| 1   | 1   | 1   | PTA2/TCLK               |

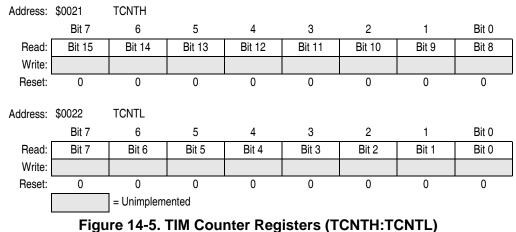

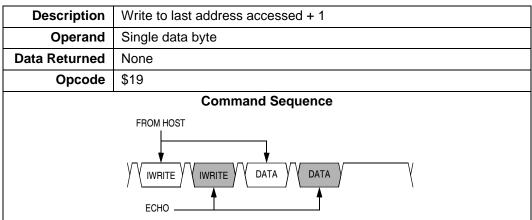

### 14.9.2 TIM Counter Registers

The two read-only TIM counter registers contain the high and low bytes of the value in the TIM counter. Reading the high byte (TCNTH) latches the contents of the low byte (TCNTL) into a buffer. Subsequent reads of TCNTH do not affect the latched TCNTL value until TCNTL is read. Reset clears the TIM counter registers. Setting the TIM reset bit (TRST) also clears the TIM counter registers.

**NOTE** If you read TCNTH during a break interrupt, be sure to unlatch TCNTL by reading TCNTL before exiting the break interrupt. Otherwise, TCNTL retains the value latched during the break.

Development Support

| Mode                           | IRQ<br>(PTA2)           | RST             | Reset<br>Vector   | Serial<br>Communi-<br>cation |              | ode<br>ction | СОР      | Communication<br>Speed |                      |              | Comments                           |

|--------------------------------|-------------------------|-----------------|-------------------|------------------------------|--------------|--------------|----------|------------------------|----------------------|--------------|------------------------------------|

|                                | (FTA2)                  | (PTA3)          | vector            | PTA0                         | PTA1         | PTA4         |          | External<br>Clock      | Bus<br>Frequency     | Baud<br>Rate |                                    |

| Normal<br>Monitor              | V <sub>TST</sub>        | V <sub>DD</sub> | х                 | 1                            | 1            | 0            | Disabled | 9.8304<br>MHz          | 2.4576<br>MHz        | 9600         | Provide external clock at OSC1.    |

| Forced                         | V <sub>DD</sub>         | Х               | \$FFFF<br>(blank) | 1                            | Х            | х            | Disabled | 9.8304<br>MHz          | 2.4576<br>MHz        | 9600         | Provide external<br>clock at OSC1. |

| Monitor                        | V <sub>SS</sub>         | Х               | \$FFFF<br>(blank) | 1                            | Х            | х            | Disabled | Х                      | 3.2 MHz<br>(Trimmed) | 9600         | Internal clock<br>is active.       |

| User                           | Х                       | Х               | Not<br>\$FFFF     | Х                            | Х            | х            | Enabled  | Х                      | Х                    | Х            |                                    |

| MON08<br>Function<br>[Pin No.] | V <sub>TST</sub><br>[6] | RST<br>[4]      |                   | COM<br>[8]                   | MOD0<br>[12] | MOD1<br>[10] |          | OSC1<br>[13]           |                      |              |                                    |

Table 15-1. Monitor Mode Signal Requirements and Options

1. PTA0 must have a pullup resistor to  $V_{DD}$  in monitor mode.

2. Communication speed in the table is an example to obtain a baud rate of 9600. Baud rate using external oscillator is bus frequency / 256 and baud rate using internal oscillator is bus frequency / 335.

3. External clock is a 9.8304 MHz oscillator on OSC1.

4. X = don't care

5. MON08 pin refers to P&E Microcomputer Systems' MON08-Cyclone 2 by 8-pin connector.

| NC       | 1  | 2  | GND  |

|----------|----|----|------|

| NC       | 3  | 4  | RST  |

| NC       | 5  | 6  | IRQ  |

| NC       | 7  | 8  | PTA0 |

| NC       | 9  | 10 | PTA4 |

| NC       | 11 | 12 | PTA1 |

| OSC1     | 13 | 14 | NC   |

| $V_{DD}$ | 15 | 16 | NC   |

The rising edge of the internal RST signal latches the monitor mode. Once monitor mode is latched, the values on PTA1 and PTA4 pins can be changed.

Once out of reset, the MCU waits for the host to send eight security bytes (see 15.3.2 Security). After the security bytes, the MCU sends a break signal (10 consecutive logic 0s) to the host, indicating that it is ready to receive a command.

### 15.3.1.1 Normal Monitor Mode

RST and OSC1 functions will be active on the PTA3 and PTA5 pins respectively as long as  $V_{TST}$  is applied to the IRQ pin. If the IRQ pin is lowered (no longer  $V_{TST}$ ) then the chip will still be operating in monitor mode, but the pin functions will be determined by the settings in the configuration registers (see Chapter 5 Configuration Register (CONFIG)) when  $V_{TST}$  was lowered. With  $V_{TST}$  lowered, the BIH and BIL instructions will read the IRQ pin state only if IRQEN is set in the CONFIG2 register.

Development Support

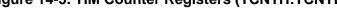

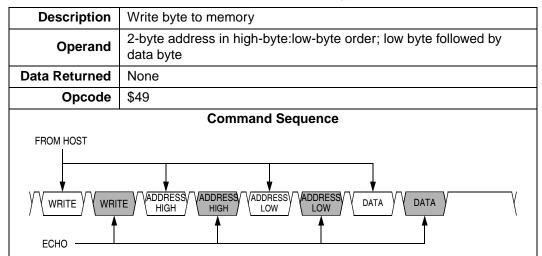

Table 15-5. IREAD (Indexed Read) Command

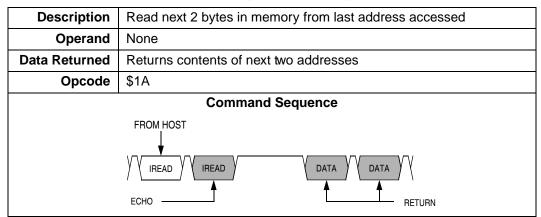

### Table 15-6. IWRITE (Indexed Write) Command

A sequence of IREAD or IWRITE commands can access a block of memory sequentially over the full 64-Kbyte memory map.

# Chapter 16 Electrical Specifications

# **16.1 Introduction**

This section contains electrical and timing specifications.

# 16.2 Absolute Maximum Ratings

Maximum ratings are the extreme limits to which the microcontroller unit (MCU) can be exposed without permanently damaging it.

NOTE

This device is not guaranteed to operate properly at the maximum ratings. Refer to 16.5 5-V DC Electrical Characteristics and 16.9 3-V DC Electrical Characteristics for guaranteed operating conditions.

| Characteristic <sup>(1)</sup>                                                                          | Symbol                               | Value                          | Unit |

|--------------------------------------------------------------------------------------------------------|--------------------------------------|--------------------------------|------|

| Supply voltage                                                                                         | V <sub>DD</sub>                      | -0.3 to +6.0                   | V    |

| Input voltage                                                                                          | V <sub>IN</sub>                      | $V_{SS}$ –0.3 to $V_{DD}$ +0.3 | V    |

| Mode entry voltage, IRQ pin                                                                            | V <sub>TST</sub>                     | V <sub>SS</sub> –0.3 to +9.1   | V    |

| Maximum current per pin excluding PTA0–PTA5, $\mathrm{V}_{\mathrm{DD}}$ and $\mathrm{V}_{\mathrm{SS}}$ | I                                    | ±15                            | mA   |

| Maximum current for pins PTA0–PTA5                                                                     | I <sub>PTA0</sub> _I <sub>PTA5</sub> | ±25                            | mA   |

| Storage temperature                                                                                    | T <sub>STG</sub>                     | -55 to +150                    | °C   |

| Maximum current out of V <sub>SS</sub>                                                                 | I <sub>MVSS</sub>                    | 100                            | mA   |

| Maximum current into V <sub>DD</sub>                                                                   | I <sub>MVDD</sub>                    | 100                            | mA   |

1. Voltages references to  $V_{SS}$ .

### NOTE

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum-rated voltages to this high-impedance circuit. For proper operation, it is recommended that  $V_{IN}$  and  $V_{OUT}$  be constrained to the range  $V_{SS} \leq (V_{IN} \text{ or } V_{OUT}) \leq V_{DD}$ . Reliability of operation is enhanced if unused inputs are connected to an appropriate logic voltage level (for example, either  $V_{SS}$  or  $V_{DD}$ .)

**Electrical Specifications**

# 16.8 5-V Oscillator Characteristics

| Characteristic                                                                                                                                                                               | Symbol             | Min | Тур                | Max  | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|--------------------|------|------|

| Internal oscillator frequency <sup>(1)</sup>                                                                                                                                                 | fintclk            | —   | 12.8               | _    | MHz  |

| Deviation from trimmed Internal oscillator $^{(2)(3)}$<br>12.8 MHz, fixed voltage, fixed temp<br>12.8 MHz, V <sub>DD</sub> ± 10%, 0 to 70°C<br>12.8 MHz, V <sub>DD</sub> ± 10%, -40 to 125°C | ACC <sub>INT</sub> |     | ±0.4<br>±2<br>—    | <br> | %    |

| Crystal frequency, XTALCLK <sup>(1)</sup>                                                                                                                                                    | foscxclk           | 1   | —                  | 24   | MHz  |

| External RC oscillator frequency, RCCLK <sup>(1)</sup>                                                                                                                                       | f <sub>RCCLK</sub> | 2   | —                  | 12   | MHz  |

| External clock reference frequency <sup>(1) (4)</sup>                                                                                                                                        | foscxclk           | dc  | —                  | 32   | MHz  |

| Crystal load capacitance <sup>(5)</sup>                                                                                                                                                      | CL                 | —   | 20                 |      | pF   |

| Crystal fixed capacitance <sup>(3)</sup>                                                                                                                                                     | C <sub>1</sub>     | —   | 2 x C <sub>L</sub> | _    | —    |

| Crystal tuning capacitance <sup>(3)</sup>                                                                                                                                                    | C <sub>2</sub>     | —   | 2 x C <sub>L</sub> | _    | —    |

| Feedback bias resistor                                                                                                                                                                       | R <sub>B</sub>     | 0.5 | 1                  | 10   | MΩ   |

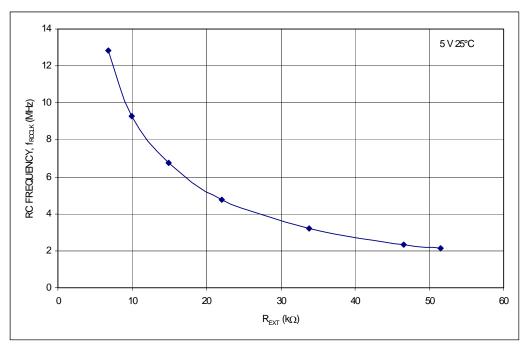

| RC oscillator external resistor                                                                                                                                                              | R <sub>EXT</sub>   | S   | See Figure 16-     | 4    | —    |

| Crystal series damping resistor<br>$f_{OSCXCLK} = 1 MHz$<br>$f_{OSCXCLK} = 4 MHz$<br>$f_{OSCXCLK} = > 8 MHz$                                                                                 | R <sub>S</sub>     |     | 20<br>10<br>0      | <br> | kΩ   |

Bus frequency, f<sub>OP</sub>, is oscillator frequency divided by 4.

Deviation values assumes trimming @25•C and midpoint of voltage range.

Values are based on characterization results, not tested in production.

No more than 10% duty cycle deviation from 50%.

5. Consult crystal vendor data sheet.

Figure 16-4. RC versus Frequency (5 Volts @ 25•C)

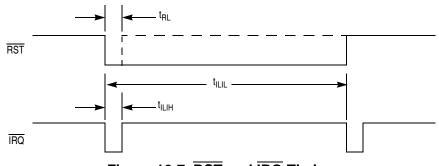

# 16.11 3-V Control Timing

| Characteristic <sup>(1)</sup>                  | Symbol                              | Min                 | Max | Unit             |

|------------------------------------------------|-------------------------------------|---------------------|-----|------------------|

| Internal operating frequency                   | f <sub>OP</sub> (f <sub>Bus</sub> ) | -                   | 4   | MHz              |

| Internal clock period (1/f <sub>OP</sub> )     | t <sub>cyc</sub>                    | 250                 | _   | ns               |

| RST input pulse width low                      | t <sub>RL</sub>                     | 200                 |     | ns               |

| IRQ interrupt pulse width low (edge-triggered) | t <sub>ILIH</sub>                   | 200                 | _   | ns               |

| IRQ interrupt pulse period                     | t <sub>ILIL</sub>                   | Note <sup>(2)</sup> |     | t <sub>cyc</sub> |

1. V<sub>DD</sub> = 2.7 to 3.3 Vdc, V<sub>SS</sub> = 0 Vdc, T<sub>A</sub> = T<sub>L</sub> to T<sub>H</sub>; timing shown with respect to 20% V<sub>DD</sub> and 70% V<sub>DD</sub>, unless otherwise noted.

2. The minimum period is the number of cycles it takes to execute the interrupt service routine plus 1  $t_{cyc}$ .

Figure 16-7. RST and IRQ Timing

# **16.16 Memory Characteristics**

| Characteristic                                      | Symbol                           | Min        | Тур    | Max        | Unit   |

|-----------------------------------------------------|----------------------------------|------------|--------|------------|--------|

| RAM data retention voltage                          | V <sub>RDR</sub>                 | 1.3        | —      | _          | V      |

| FLASH program bus clock frequency                   | _                                | 1          | —      |            | MHz    |

| FLASH read bus clock frequency                      | f <sub>Read</sub> <sup>(1)</sup> | 0          | —      | 8 M        | Hz     |

| FLASH page erase time<br><1 k cycles<br>>1 k cycles | t <sub>Erase</sub>               | 0.9<br>3.6 | 1<br>4 | 1.1<br>5.5 | ms     |

| FLASH mass erase time                               | t <sub>MErase</sub>              | 4          | —      | _          | ms     |

| FLASH PGM/ERASE to HVEN setup time                  | t <sub>NVS</sub>                 | 10         | —      | _          | μs     |

| FLASH high-voltage hold time                        | t <sub>NVH</sub>                 | 5          | —      | _          | μs     |

| FLASH high-voltage hold time (mass erase)           | t <sub>NVHL</sub>                | 100        | —      | _          | μs     |

| FLASH program hold time                             | t <sub>PGS</sub>                 | 5          | —      | _          | μs     |

| FLASH program time                                  | t <sub>PROG</sub>                | 30         | —      | 40         | μs     |

| FLASH return to read time                           | t <sub>RCV</sub> <sup>(2)</sup>  | 1          | —      | _          | μS     |

| FLASH cumulative program HV period                  | t <sub>HV</sub> <sup>(3)</sup>   | _          | —      | 4          | ms     |

| FLASH endurance <sup>(4)</sup>                      | _                                | 10 k       | 100 k  | _          | Cycles |

| FLASH data retention time <sup>(5)</sup>            | —                                | 15         | 100    | _          | Years  |

1.  $f_{Read}$  is defined as the frequency range for which the FLASH memory can be read.

2. t<sub>RCV</sub> is defined as the time it needs before the FLASH can be read after turning off the high voltage charge pump, by clearing HVEN to 0.

3.  $t_{HV}$  is defined as the cumulative high voltage programming time to the same row before next erase.

$t_{HV}$  must satisfy this condition:  $t_{NVS}$  +  $t_{NVH}$  +  $t_{PGS}$  +  $(t_{PROG} \ x \ 32) \ \leq t_{HV}$  maximum.

4. Typical endurance was evaluated for this product family. For additional information on how Freescale defines *Typical Endurance*, please refer to Engineering Bulletin EB619.

5. Typical data retention values are based on intrinsic capability of the technology measured at high temperature and de-rated to 25•C using the Arrhenius equation. For additional information on how Freescale defines *Typical Data Retention*, please refer to Engineering Bulletin EB618.

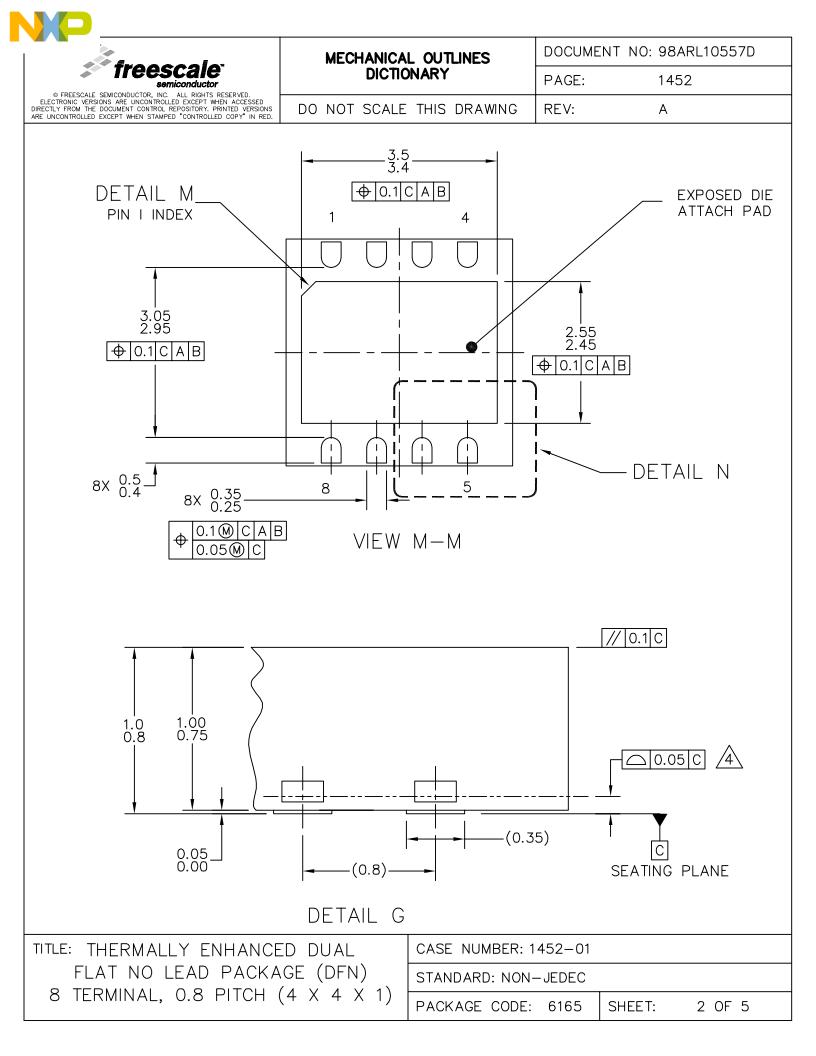

|                                                                                                                                                                                                | MECHANICAL     | DUTLINES                      | DOCUMENT | ND: 98ASH70247A   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------------------------|----------|-------------------|

| FREESCALE SEMICIDUCTOR, INC. ALL RIGHTS RESERVED.                                                                                                                                              | DICTI          |                               | PAGE:    | 948F              |

| CETRONIC VERSIONS ARE UNCONTROLLED EXCEPT VHEN ACCESSED<br>DIRECTLY FROM THE DECUMENT CONTROL REPOSITORY, PRINTED<br>RISIONS ARE UNCONTROLLED EXCEPT VHEN STAMPED "CONTROLLED<br>COPY' IN RED. | DO NOT SCALE   | THIS DRAWING                  | REV:     | В                 |

| NOTES:                                                                                                                                                                                         |                |                               |          |                   |

| 1. CONTROLLING DIMENSI                                                                                                                                                                         | ON: MILLIMETE  | R                             |          |                   |

| 2. DIMENSIONS AND TOLE                                                                                                                                                                         | RANCES PER AN  | NSI Y14.5M-19                 | 82.      |                   |

| 3 DIMENSION DOES NOT<br>BURRS. MOLD FLASH O                                                                                                                                                    |                | FLASH, PROTR<br>Shall Not Ex  |          |                   |

| DIMENSION DOES NOT                                                                                                                                                                             |                | RLEAD FLASH O<br>All Not Exce |          | SION.<br>Er side. |

| 5 DIMENSION DOES NOT<br>DAMBAR PROTRUSION SI<br>THE DIMENSION AT MA                                                                                                                            | HALL BE 0.08   |                               | ESS OF   | BLE               |

| 6. TERMINAL NUMBERS AR                                                                                                                                                                         | E SHOWN FOR F  | REFERENCE ONL                 | Υ.       |                   |

| $\overline{/7}$ dimensions are to be                                                                                                                                                           | e determined . | AT DATUM PLAN                 | VE       |                   |

|                                                                                                                                                                                                |                |                               |          |                   |

|                                                                                                                                                                                                |                |                               |          |                   |

| ITLE:                                                                                                                                                                                          |                | CASE NUMBER: 9                |          |                   |