Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                      |

|----------------------------|-------------------------------------------------------------|

| Core Processor             | HC08                                                        |

| Core Size                  | 8-Bit                                                       |

| Speed                      | 8MHz                                                        |

| Connectivity               | -                                                           |

| Peripherals                | LVD, POR, PWM                                               |

| Number of I/O              | 13                                                          |

| Program Memory Size        | 4KB (4K x 8)                                                |

| Program Memory Type        | FLASH                                                       |

| EEPROM Size                | -                                                           |

| RAM Size                   | 128 x 8                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                 |

| Data Converters            | A/D 4x8b                                                    |

| Oscillator Type            | Internal                                                    |

| Operating Temperature      | -40°C ~ 105°C (TA)                                          |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 16-SOIC (0.295", 7.50mm Width)                              |

| Supplier Device Package    | 16-SOIC                                                     |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mchc908qy4vdwe |

|                            |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **List of Chapters**

\_\_\_\_\_

| Chapter 1 General Description                                 |

|---------------------------------------------------------------|

| Chapter 2 Memory                                              |

| Chapter 3 Analog-to-Digital Converter (ADC)41                 |

| Chapter 4 Auto Wakeup Module (AWU)49                          |

| Chapter 5 Configuration Register (CONFIG)53                   |

| Chapter 6 Computer Operating Properly (COP)57                 |

| Chapter 7 Central Processor Unit (CPU)61                      |

| Chapter 8 External Interrupt (IRQ)73                          |

| Chapter 9 Keyboard Interrupt Module (KBI)79                   |

| Chapter 10 Low-Voltage Inhibit (LVI)                          |

| Chapter 11 Oscillator Module (OSC)                            |

| Chapter 12 Input/Output Ports (PORTS)                         |

| Chapter 13 System Integration Module (SIM)103                 |

| Chapter 14 Timer Interface Module (TIM)119                    |

| Chapter 15 Development Support                                |

| Chapter 16 Electrical Specifications149                       |

| Chapter 17 Ordering Information and Mechanical Specifications |

**Table of Contents**

# Chapter 1 General Description

# **1.1 Introduction**

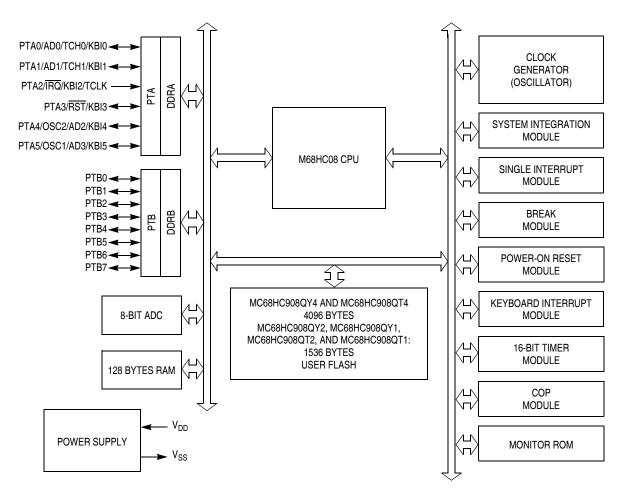

The MC68HC908QY4 is a member of the low-cost, high-performance M68HC08 Family of 8-bit microcontroller units (MCUs). The M68HC08 Family is a Complex Instruction Set Computer (CISC) with a Von Neumann architecture. All MCUs in the family use the enhanced M68HC08 central processor unit (CPU08) and are available with a variety of modules, memory sizes and types, and package types.

| Device       | FLASH<br>Memory Size | Analog-to-Digital<br>Converter | Pin<br>Count |

|--------------|----------------------|--------------------------------|--------------|

| MC68HC908QT1 | 1536 bytes           | —                              | 8 pins       |

| MC68HC908QT2 | 1536 bytes           | 4 ch, 8 bit                    | 8 pins       |

| MC68HC908QT4 | 4096 bytes           | 4 ch, 8 bit                    | 8 pins       |

| MC68HC908QY1 | 1536 bytes           | —                              | 16 pins      |

| MC68HC908QY2 | 1536 bytes           | 4 ch, 8 bit                    | 16 pins      |

| MC68HC908QY4 | 4096 bytes           | 4 ch, 8 bit                    | 16 pins      |

Table 1-1. Summary of Device Variations

# **1.2 Features**

Features include:

- High-performance M68HC08 CPU core

- Fully upward-compatible object code with M68HC05 Family

- 5-V and 3-V operating voltages (V<sub>DD</sub>)

- 8-MHz internal bus operation at 5 V, 4-MHz at 3 V

- Trimmable internal oscillator

- 3.2 MHz internal bus operation

- 8-bit trim capability allows 0.4% accuracy<sup>(1)</sup>

- ± 25% untrimmed

- Auto wakeup from STOP capability

- Configuration (CONFIG) register for MCU configuration options, including:

- Low-voltage inhibit (LVI) trip point

- In-system FLASH programming

- FLASH security<sup>(2)</sup>

<sup>1.</sup> The oscillator frequency is guaranteed to  $\pm 5\%$  over temperature and voltage range after trimming.

No security feature is absolutely secure. However, Freescale's strategy is to make reading or copying the FLASH difficult for unauthorized users.

#### General Description

- On-chip in-application programmable FLASH memory (with internal program/erase voltage generation)

- MC68HC908QY4 and MC68HC908QT4 4096 bytes

- MC68HC908QY2, MC68HC908QY1, MC68HC908QT2, and MC68HC908QT1 1536 bytes

- 128 bytes of on-chip random-access memory (RAM)

- 2-channel, 16-bit timer interface module (TIM)

- 4-channel, 8-bit analog-to-digital converter (ADC) on MC68HC908QY2, MC68HC908QY4, MC68HC908QT2, and MC68HC908QT4

- 5 or 13 bidirectional input/output (I/O) lines and one input only:

- Six shared with keyboard interrupt function and ADC

- Two shared with timer channels

- One shared with external interrupt (IRQ)

- Eight extra I/O lines on 16-pin package only

- High current sink/source capability on all port pins

- Selectable pullups on all ports, selectable on an individual bit basis

- Three-state ability on all port pins

- 6-bit keyboard interrupt with wakeup feature (KBI)

- Low-voltage inhibit (LVI) module features:

- Software selectable trip point in CONFIG register

- System protection features:

- Computer operating properly (COP) watchdog

- Low-voltage detection with reset

- Illegal opcode detection with reset

- Illegal address detection with reset

- External asynchronous interrupt pin with internal pullup (IRQ) shared with general-purpose input pin

- Master asynchronous reset pin (RST) shared with general-purpose input/output (I/O) pin

- Power-on reset

- Internal pullups on IRQ and RST to reduce external components

- Memory mapped I/O registers

- Power saving stop and wait modes

- MC68HC908QY4, MC68HC908QY2, and MC68HC908QY1 are available in these packages:

- 16-pin plastic dual in-line package (PDIP)

- 16-pin small outline integrated circuit (SOIC) package

- 16-pin thin shrink small outline package (TSSOP)

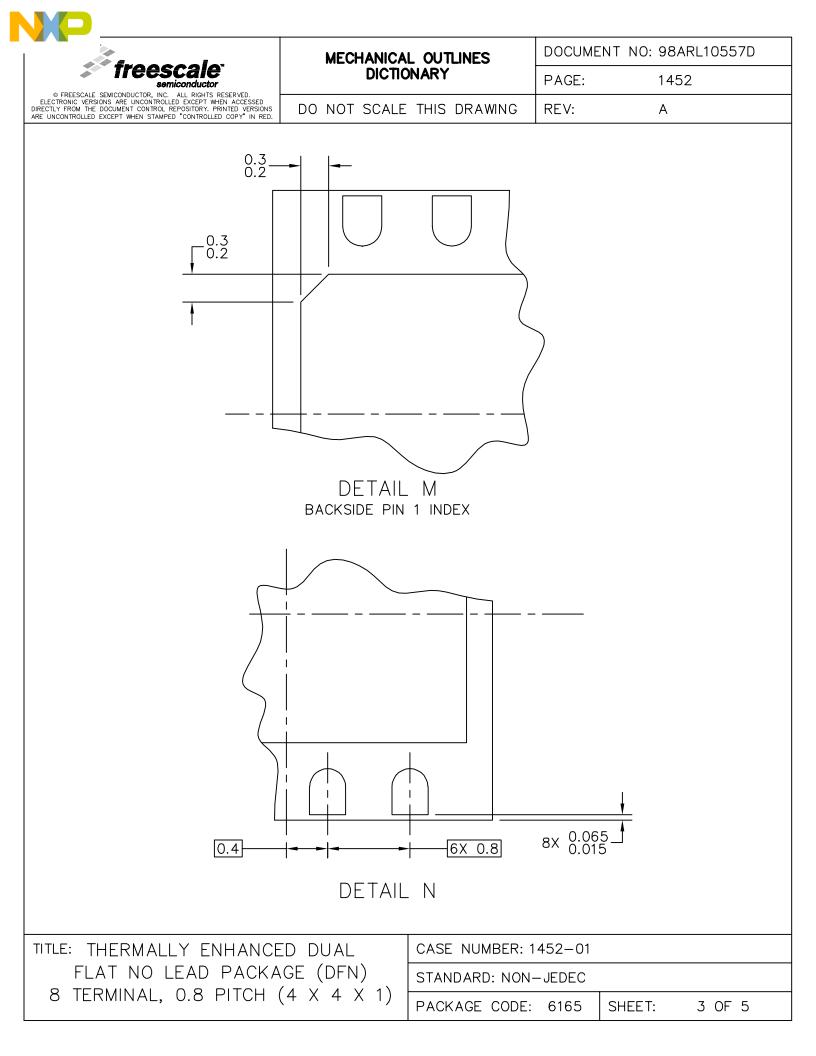

- MC68HC908QT4, MC68HC908QT2, and MC68HC908QT1 are available in these packages:

- 8-pin PDIP

- 8-pin SOIC

- 8-pin dual flat no lead (DFN) package

#### **General Description**

RST, IRQ: Pins have internal (about 30K Ohms) pull up

PTA[0:5]: High current sink and source capability

PTA[0:5]: Pins have programmable keyboard interrupt and pull up

PTB[0:7]: Not available on 8-pin devices – MC68HC908QT1, MC68HC908QT2, and MC68HC908QT4 (see note in 12.1 Introduction)

ADC: Not available on the MC68HC908QY1 and MC68HC908QT1

### Figure 1-1. Block Diagram

# Chapter 4 Auto Wakeup Module (AWU)

# 4.1 Introduction

This section describes the auto wakeup module (AWU). The AWU generates a periodic interrupt during stop mode to wake the part up without requiring an external signal. Figure 4-1 is a block diagram of the AWU.

# 4.2 Features

Features of the auto wakeup module include:

- One internal interrupt with separate interrupt enable bit, sharing the same keyboard interrupt vector and keyboard interrupt mask bit

- Exit from low-power stop mode without external signals

- Selectable timeout periods

- Dedicated low-power internal oscillator separate from the main system clock sources

# 4.3 Functional Description

The function of the auto wakeup logic is to generate periodic wakeup requests to bring the microcontroller unit (MCU) out of stop mode. The wakeup requests are treated as regular keyboard interrupt requests, with the difference that instead of a pin, the interrupt signal is generated by an internal logic.

Writing the AWUIE bit in the keyboard interrupt enable register enables or disables the auto wakeup interrupt input (see Figure 4-1). A logic 1 applied to the AWUIREQ input with auto wakeup interrupt request enabled, latches an auto wakeup interrupt request.

Auto wakeup latch, AWUL, can be read directly from the bit 6 position of port A data register (PTA). This is a read-only bit which is occupying an empty bit position on PTA. No PTA associated registers, such as PTA6 data direction or PTA6 pullup exist for this bit.

Entering stop mode will enable the auto wakeup generation logic. An internal RC oscillator (exclusive for the auto wakeup feature) drives the wakeup request generator. Once the overflow count is reached in the generator counter, a wakeup request, AWUIREQ, is latched and sent to the KBI logic. See Figure 4-1.

Wakeup interrupt requests will only be serviced if the associated interrupt enable bit, AWUIE, in KBIER is set. The AWU shares the keyboard interrupt vector.

The overflow count can be selected from two options defined by the COPRS bit in CONFIG1. This bit was "borrowed" from the computer operating properly (COP) using the fact that the COP feature is idle (no MCU clock available) in stop mode. The typical values of the periodic wakeup request are (at room temperature):

- COPRS = 0: 650 ms @ 5 V, 875 ms @ 3 V

- COPRS = 1: 16 ms @ 5 V, 22 ms @ 3 V

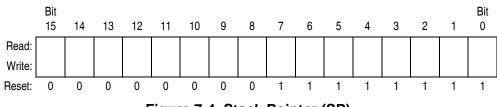

### 7.3.3 Stack Pointer

The stack pointer is a 16-bit register that contains the address of the next location on the stack. During a reset, the stack pointer is preset to \$00FF. The reset stack pointer (RSP) instruction sets the least significant byte to \$FF and does not affect the most significant byte. The stack pointer decrements as data is pushed onto the stack and increments as data is pulled from the stack.

In the stack pointer 8-bit offset and 16-bit offset addressing modes, the stack pointer can function as an index register to access data on the stack. The CPU uses the contents of the stack pointer to determine the conditional address of the operand.

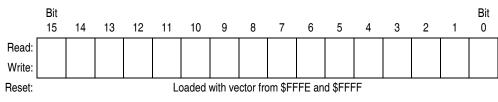

Figure 7-4. Stack Pointer (SP)

#### NOTE

The location of the stack is arbitrary and may be relocated anywhere in random-access memory (RAM). Moving the SP out of page 0 (\$0000 to \$00FF) frees direct address (page 0) space. For correct operation, the stack pointer must point only to RAM locations.

## 7.3.4 Program Counter

The program counter is a 16-bit register that contains the address of the next instruction or operand to be fetched.

Normally, the program counter automatically increments to the next sequential memory location every time an instruction or operand is fetched. Jump, branch, and interrupt operations load the program counter with an address other than that of the next sequential location.

During reset, the program counter is loaded with the reset vector address located at \$FFFE and \$FFFF. The vector address is the address of the first instruction to be executed after exiting the reset state.

Figure 7-5. Program Counter (PC)

Oscillator Module (OSC)

# 11.4.2 Crystal Amplifier Output Pin (OSC2/PTA4/BUSCLKX4)

For the XTAL oscillator device, the OSC2 pin is the crystal oscillator inverting amplifier output.

For the external clock option, the OSC2 pin is dedicated to the PTA4 I/O function. The OSC2EN bit has no effect.

For the internal oscillator or RC oscillator options, the OSC2 pin can assume other functions according to Table 1-3. Function Priority in Shared Pins, or the output of the oscillator clock (BUSCLKX4).

| Option                                  | OSC2 Pin Function                                                                                  |

|-----------------------------------------|----------------------------------------------------------------------------------------------------|

| XTAL oscillator                         | Inverting OSC1                                                                                     |

| External clock                          | PTA4 I/O                                                                                           |

| Internal oscillator or<br>RC oscillator | Controlled by OSC2EN bit in PTAPUE register<br>OSC2EN = 0: PTA4 I/O<br>OSC2EN = 1: BUSCLKX4 output |

Table 11-1. OSC2 Pin Function

# 11.4.3 Oscillator Enable Signal (SIMOSCEN)

The SIMOSCEN signal comes from the system integration module (SIM) and enables/disables either the XTAL oscillator circuit, the RC oscillator, or the internal oscillator.

# 11.4.4 XTAL Oscillator Clock (XTALCLK)

XTALCLK is the XTAL oscillator output signal. It runs at the full speed of the crystal ( $f_{XCLK}$ ) and comes directly from the crystal oscillator circuit. Figure 11-2 shows only the logical relation of XTALCLK to OSC1 and OSC2 and may not represent the actual circuitry. The duty cycle of XTALCLK is unknown and may depend on the crystal and other external factors. Also, the frequency and amplitude of XTALCLK can be unstable at start up.

# 11.4.5 RC Oscillator Clock (RCCLK)

RCCLK is the RC oscillator output signal. Its frequency is directly proportional to the time constant of external R and internal C. Figure 11-3 shows only the logical relation of RCCLK to OSC1 and may not represent the actual circuitry.

# 11.4.6 Internal Oscillator Clock (INTCLK)

INTCLK is the internal oscillator output signal. Its nominal frequency is fixed to 12.8 MHz, but it can be also trimmed using the oscillator trimming feature of the OSCTRIM register (see 11.3.1.1 Internal Oscillator Trimming).

# 11.4.7 Oscillator Out 2 (BUSCLKX4)

BUSCLKX4 is the same as the input clock (XTALCLK, RCCLK, or INTCLK). This signal is driven to the SIM module and is used to determine the COP cycles.

### 11.4.8 Oscillator Out (BUSCLKX2)

The frequency of this signal is equal to half of the BUSCLKX4, this signal is driven to the SIM for generation of the bus clocks used by the CPU and other modules on the MCU. BUSCLKX2 will be divided

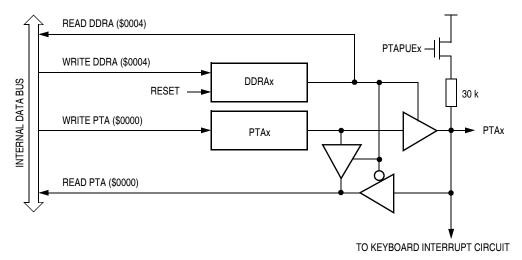

Figure 12-3 shows the port A I/O logic.

Figure 12-3. Port A I/O Circuit

**NOTE** Figure 12-3 does not apply to PTA2

When DDRAx is a 1, reading address \$0000 reads the PTAx data latch. When DDRAx is a 0, reading address \$0000 reads the voltage level on the pin. The data latch can always be written, regardless of the state of its data direction bit.

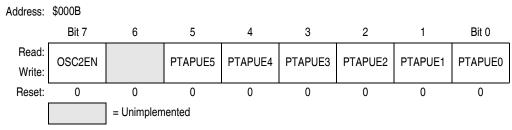

### 12.2.3 Port A Input Pullup Enable Register

The port A input pullup enable register (PTAPUE) contains a software configurable pullup device for each if the six port A pins. Each bit is individually configurable and requires the corresponding data direction register, DDRAx, to be configured as input. Each pullup device is automatically and dynamically disabled when its corresponding DDRAx bit is configured as output.

### **OSC2EN** — Enable PTA4 on OSC2 Pin

This read/write bit configures the OSC2 pin function when internal oscillator or RC oscillator option is selected. This bit has no effect for the XTAL or external oscillator options.

1 = OSC2 pin outputs the internal or RC oscillator clock (BUSCLKX4)

0 = OSC2 pin configured for PTA4 I/O, having all the interrupt and pullup functions

#### System Integration Module (SIM)

The SIM counter is held in reset from the execution of the STOP instruction until the beginning of stop recovery. It is then used to time the recovery period. Figure 13-17 shows stop mode entry timing and Figure 13-18 shows the stop mode recovery time from interrupt or break.

**NOTE** To minimize stop current, all pins configured as inputs should be driven to

#### a logic 1 or logic 0. CPUSTOP ADDRESS BUS STOP ADDR STOP ADDR + 1 SAME SAME DATA BUS PREVIOUS DATA NEXT OPCODE SAME SAME R/W NOTE: Previous data can be operand data or the STOP opcode, depending on the last instruction. Figure 13-17. Stop Mode Entry Timing STOP RECOVERY PERIOD BUSCLKX4 INTERRUPT ADDRESS BUS STOP +1 STOP + 2 STOP + 2 SP SP – 1 SP – 2 SP – 3

Figure 13-18. Stop Mode Recovery from Interrupt

# **13.8 SIM Registers**

The SIM has three memory mapped registers. Table 13-4 shows the mapping of these registers.

#### Table 13-4. SIM Registers

| Address | Register | Access Mode |

|---------|----------|-------------|

| \$FE00  | BSR      | User        |

| \$FE01  | SRSR     | User        |

| \$FE03  | BFCR     | User        |

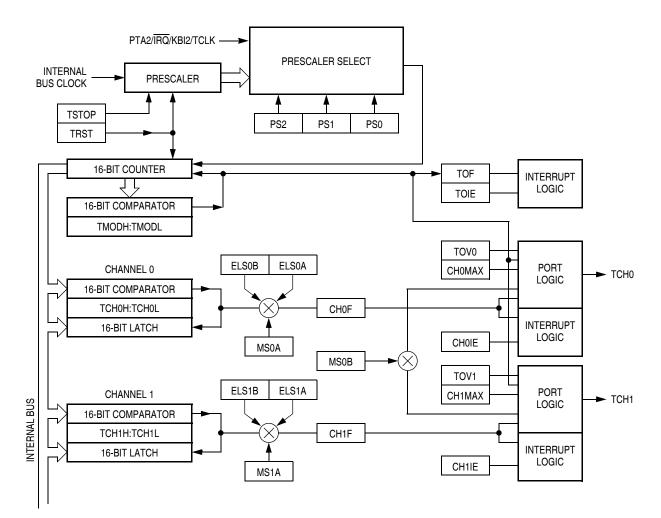

# 14.4 Functional Description

Figure 14-2 shows the structure of the TIM. The central component of the TIM is the 16-bit TIM counter that can operate as a free-running counter or a modulo up-counter. The TIM counter provides the timing reference for the input capture and output compare functions. The TIM counter modulo registers, TMODH:TMODL, control the modulo value of the TIM counter. Software can read the TIM counter value at any time without affecting the counting sequence.

The two TIM channels are programmable independently as input capture or output compare channels.

Figure 14-2. TIM Block Diagram

#### Input/Output Registers

When ELSxB:A = 00, this read/write bit selects the initial output level of the TCHx pin (see Table 14-3). Reset clears the MSxA bit.

1 = Initial output level low

0 = Initial output level high

#### NOTE

Before changing a channel function by writing to the MSxB or MSxA bit, set the TSTOP and TRST bits in the TIM status and control register (TSC).

| MSxB | MSxA | ELSxB | ELSxA | Mode            | Configuration                                     |

|------|------|-------|-------|-----------------|---------------------------------------------------|

| Х    | 0    | 0     | 0     | Output preset   | Pin under port control; initial output level high |

| Х    | 1    | 0     | 0     |                 | Pin under port control; initial output level low  |

| 0    | 0    | 0     | 1     |                 | Capture on rising edge only                       |

| 0    | 0    | 1     | 0     | Input capture   | Capture on falling edge only                      |

| 0    | 0    | 1     | 1     |                 | Capture on rising or falling edge                 |

| 0    | 1    | 0     | 0     |                 | Software compare only                             |

| 0    | 1    | 0     | 1     | Output compare  | Toggle output on compare                          |

| 0    | 1    | 1     | 0     | or PWM          | Clear output on compare                           |

| 0    | 1    | 1     | 1     |                 | Set output on compare                             |

| 1    | Х    | 0     | 1     | Buffered output | Toggle output on compare                          |

| 1    | Х    | 1     | 0     | compare or      | Clear output on compare                           |

| 1    | Х    | 1     | 1     | buffered PWM    | Set output on compare                             |

Table 14-3. Mode, Edge, and Level Selection

#### ELSxB and ELSxA — Edge/Level Select Bits

When channel x is an input capture channel, these read/write bits control the active edge-sensing logic on channel x.

When channel x is an output compare channel, ELSxB and ELSxA control the channel x output behavior when an output compare occurs.

When ELSxB and ELSxA are both clear, channel x is not connected to an I/O port, and pin TCHx is available as a general-purpose I/O pin. Table 14-3 shows how ELSxB and ELSxA work. Reset clears the ELSxB and ELSxA bits.

#### NOTE

After initially enabling a TIM channel register for input capture operation and selecting the edge sensitivity, clear CHxF to ignore any erroneous edge detection flags.

#### TOVx — Toggle-On-Overflow Bit

When channel x is an output compare channel, this read/write bit controls the behavior of the channel x output when the TIM counter overflows. When channel x is an input capture channel, TOVx has no effect Reset clears the TOVx bit.

1 = Channel x pin toggles on TIM counter overflow.

0 = Channel x pin does not toggle on TIM counter overflow.

#### NOTE

When TOVx is set, a TIM counter overflow takes precedence over a channel x output compare if both occur at the same time.

#### MC68HC908QY/QT Family Data Sheet, Rev. 6

Development Support

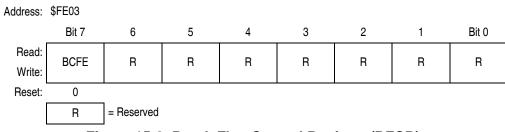

### 15.2.2.5 Break Flag Control Register

The break control register (BFCR) contains a bit that enables software to clear status bits while the MCU is in a break state.

Figure 15-8. Break Flag Control Register (BFCR)

### BCFE — Break Clear Flag Enable Bit

This read/write bit enables software to clear status bits by accessing status registers while the MCU is in a break state. To clear status bits during the break state, the BCFE bit must be set.

- 1 = Status bits clearable during break

- 0 = Status bits not clearable during break

## 15.2.3 Low-Power Modes

The WAIT and STOP instructions put the MCU in low power- consumption standby modes. If enabled, the break module will remain enabled in wait and stop modes. However, since the internal address bus does not increment in these modes, a break interrupt will never be triggered.

# 15.3 Monitor Module (MON)

This subsection describes the monitor module (MON) and the monitor mode entry methods. The monitor allows debugging and programming of the microcontroller unit (MCU) through a single-wire interface with a host computer. Monitor mode entry can be achieved without use of the higher test voltage,  $V_{TST}$ , as long as vector addresses \$FFFE and \$FFFF are blank, thus reducing the hardware requirements for in-circuit programming.

Features include:

- Normal user-mode pin functionality on most pins

- One pin dedicated to serial communication between MCU and host computer

- Standard non-return-to-zero (NRZ) communication with host computer

- Execution of code in random-access memory (RAM) or FLASH

- FLASH memory security feature<sup>(1)</sup>

- FLASH memory programming interface

- Use of external 9.8304 MHz oscillator to generate internal frequency of 2.4576 MHz

- Simple internal oscillator mode of operation (no external clock or high voltage)

- Monitor mode entry without high voltage, V<sub>TST</sub>, if reset vector is blank (\$FFFE and \$FFFF contain \$FF)

- Standard monitor mode entry if high voltage is applied to IRQ

<sup>1.</sup> No security feature is absolutely secure. However, Freescale's strategy is to make reading or copying the FLASH difficult for unauthorized users.

**Development Support**

|         | Functions            |                     |                      |                     |                    |                   |

|---------|----------------------|---------------------|----------------------|---------------------|--------------------|-------------------|

| Modes   | Reset<br>Vector High | Reset<br>Vector Low | Break<br>Vector High | Break<br>Vector Low | SWI<br>Vector High | SWI<br>Vector Low |

| User    | \$FFFE               | \$FFFF              | \$FFFC               | \$FFFD              | \$FFFC             | \$FFFD            |

| Monitor | \$FEFE               | \$FEFF              | \$FEFC               | \$FEFD              | \$FEFC             | \$FEFD            |

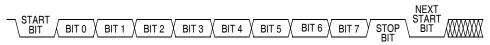

### 15.3.1.4 Data Format

Communication with the monitor ROM is in standard non-return-to-zero (NRZ) mark/space data format. Transmit and receive baud rates must be identical.

Figure 15-13. Monitor Data Format

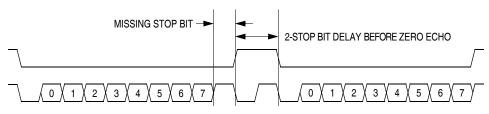

### 15.3.1.5 Break Signal

A start bit (logic 0) followed by nine logic 0 bits is a break signal. When the monitor receives a break signal, it drives the PTA0 pin high for the duration of two bits and then echoes back the break signal.

Figure 15-14. Break Transaction

### 15.3.1.6 Baud Rate

The monitor communication baud rate is controlled by the frequency of the external or internal oscillator and the state of the appropriate pins as shown in Table 15-1.

Table 15-1 also lists the bus frequencies to achieve standard baud rates. The effective baud rate is the bus frequency divided by 256 when using an external oscillator. When using the internal oscillator in forced monitor mode, the effective baud rate is the bus frequency divided by 335.

### 15.3.1.7 Commands

The monitor ROM firmware uses these commands:

- READ (read memory)

- WRITE (write memory)

- IREAD (indexed read)

- IWRITE (indexed write)

- READSP (read stack pointer)

- RUN (run user program)

**Electrical Specifications**

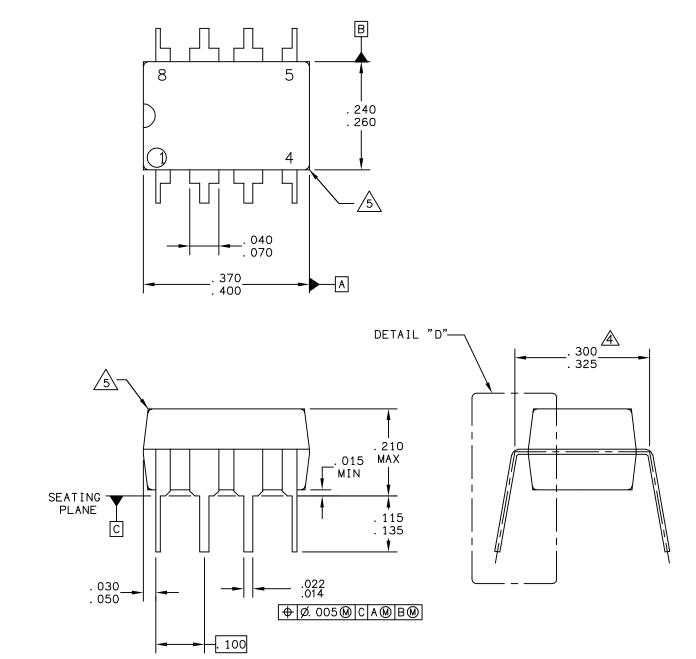

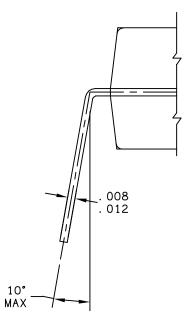

| © FREESCALE SEMICONDUCTOR, INC.<br>All RIGHTS RESERVED. | MECHANICAL OUTLINE | PRINT VERSION NO              | DT TO SCALE |

|---------------------------------------------------------|--------------------|-------------------------------|-------------|

| TITLE:                                                  | DOCUMENT N         | 0: 98ASB42420B                | REV: N      |

| 8 LD PDIP                                               | CASE NUMBE         | CASE NUMBER: 626-06 19 MAY 20 |             |

|                                                         | STANDARD: N        | ON-JEDEC                      |             |

DETAIL "D"

| © FREESCALE SEMICONDUCTOR, INC.<br>All rights reserved. |    | UTLINE                         | PRINT VERSION NO | DT TO SCALE |

|---------------------------------------------------------|----|--------------------------------|------------------|-------------|

| TITLE:                                                  | DO | CUMENT NO                      | ): 98ASB42420B   | REV: N      |

| 8 LD PDIP                                               | CA | CASE NUMBER: 626-06 19 MAY 200 |                  | 19 MAY 2005 |

|                                                         | ST | ANDARD: NO                     | N-JEDEC          |             |

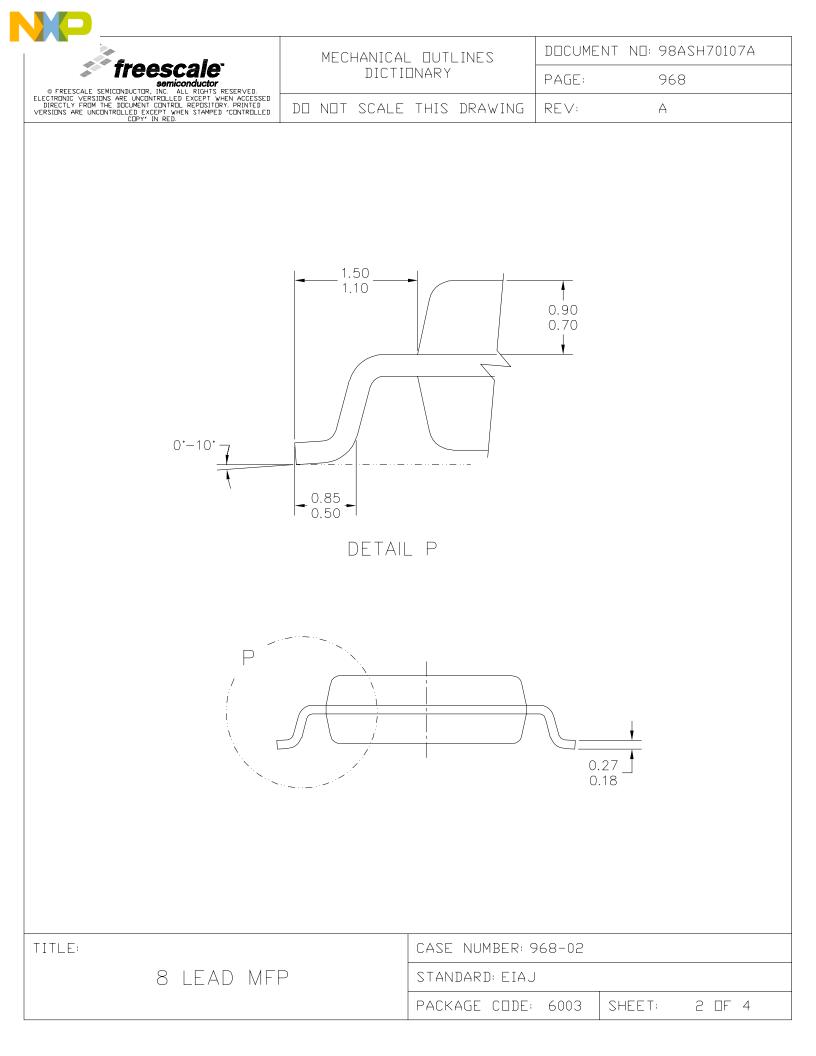

| NP                                                                                                                                                                                                |                           |                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|--------------------------|

|                                                                                                                                                                                                   | MECHANICAL OUTLINES       | DOCUMENT NO: 98ASH70107A |

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED.                                                                                                                                              | DICTIONARY                | PAGE: 968                |

| ELECTRONIC VERSIONS ARE UNCONTROLLED EXCEPT WHEN ACCESSED<br>DIRECTLY FROM THE DOCUMENT CONTROL REPOSITORY. PRINTED<br>VERSIONS ARE UNCONTROLLED EXCEPT WHEN STAMPED "CONTROLLED<br>COPY" IN RED. | DO NOT SCALE THIS DRAWING | REV: A                   |

NOTES:

1. DIMENSIONS AND TOLERANCES PER ASME Y14.5-1994.

2. CONTROLLING DIMENSION: MILLIMETER.

3. DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS AND ARE MEASURED AT THE PARTING LINE. MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEDD 0.15mm PER SIDE.

4. TERMINAL NUMBERS ARE SHOWN FOR REFERENCE ONLY.

5. THE LEAD WIDTH DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION SHALL BE 0.08mm TOTAL IN EXCESS OF THE LEAD WIDTH DIMENSION AT MAXIMUM MATERIAL CONDITION. DAMBAR CANNOT BE LOCATED ON THE LOWER RADIUS OR THE FOOT. MINIMUM SPACE BETWEEN PROTRUSIONS AND ADJACENT LEAD TO BE 0.46mm.

| TITLE: |                    | CASE NUMBER: 968-02 |  |  |

|--------|--------------------|---------------------|--|--|

|        | STANDARD: EIAJ     |                     |  |  |

|        | PACKAGE CODE: 6003 | SHEET: 3 OF 4       |  |  |