Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                                         |

|--------------------------------|-------------------------------------------------------------------------|

| Product Status                 | Active                                                                  |

| Number of LABs/CLBs            | 18144                                                                   |

| Number of Logic Elements/Cells | -                                                                       |

| Total RAM Bits                 | 165888                                                                  |

| Number of I/O                  | 418                                                                     |

| Number of Gates                | 1000000                                                                 |

| Voltage - Supply               | 1.425V ~ 1.575V                                                         |

| Mounting Type                  | Surface Mount                                                           |

| Operating Temperature          | 0°C ~ 70°C (TA)                                                         |

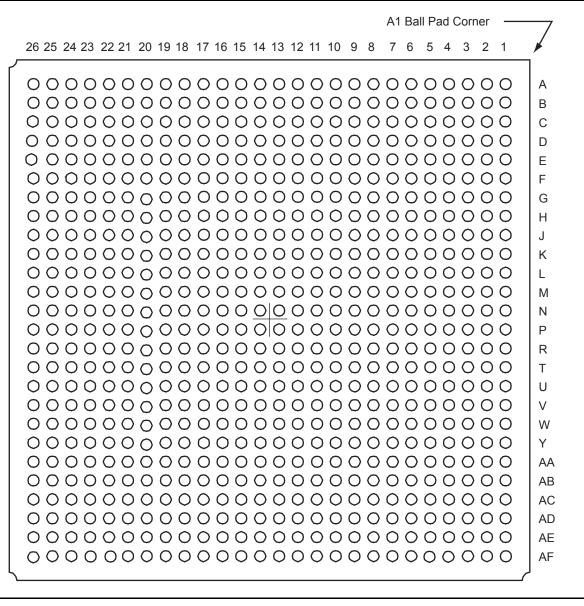

| Package / Case                 | 676-BGA                                                                 |

| Supplier Device Package        | 676-FBGA (27x27)                                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/ax1000-2fg676 |

|                                |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

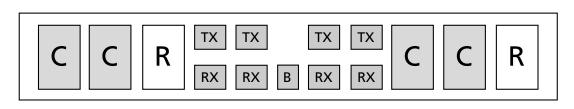

Two C-cells, a single R-cell, two Transmit (TX), and two Receive (RX) routing buffers form a Cluster, while two Clusters comprise a SuperCluster (Figure 1-4). Each SuperCluster also contains an independent Buffer (B) module, which supports buffer insertion on high-fanout nets by the place-and-route tool, minimizing system delays while improving logic utilization.

#### Figure 1-4 • AX SuperCluster

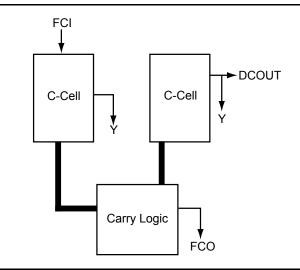

The logic modules within the SuperCluster are arranged so that two combinatorial modules are side-byside, giving a C–C–R – C–C–R pattern to the SuperCluster. This C–C–R pattern enables efficient implementation (minimum delay) of two-bit carry logic for improved arithmetic performance (Figure 1-5 on page 1-3).

Figure 1-5 • AX 2-Bit Carry Logic

The AX architecture is fully fracturable, meaning that if one or more of the logic modules in a SuperCluster are used by a particular signal path, the other logic modules are still available for use by other paths.

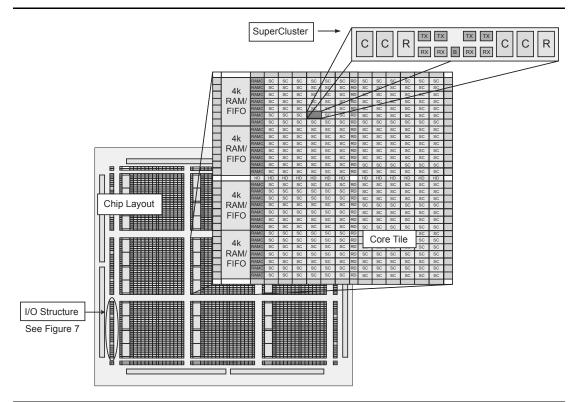

At the chip level, SuperClusters are organized into core tiles, which are arrayed to build up the full chip. For example, the AX1000 is composed of a 3x3 array of nine core tiles. Surrounding the array of core tiles are blocks of I/O Clusters and the I/O bank ring (Table 1-1). Each core tile consists of an array of 336 SuperClusters and four SRAM blocks (176 SuperClusters and three SRAM blocks for the AX250).

| Table 1-1 | • Number | of Core | Tiles | per | Device |

|-----------|----------|---------|-------|-----|--------|

|-----------|----------|---------|-------|-----|--------|

| Device | Number of Core Tiles |

|--------|----------------------|

| AX125  | 1 regular tile       |

| AX250  | 4 smaller tiles      |

| AX500  | 4 regular tiles      |

| AX1000 | 9 regular tiles      |

| AX2000 | 16 regular tiles     |

General Description

The SRAM blocks are arranged in a column on the west side of the tile (Figure 1-6 on page 1-4).

Figure 1-6 • AX Device Architecture (AX1000 shown)

# Embedded Memory

As mentioned earlier, each core tile has either three (in a smaller tile) or four (in the regular tile) embedded SRAM blocks along the west side, and each variable-aspect-ratio SRAM block is 4,608 bits in size. Available memory configurations are: 128x36, 256x18, 512x9, 1kx4, 2kx2 or 4kx1 bits. The individual blocks have separate read and write ports that can be configured with different bit widths on each port. For example, data can be written in by eight and read out by one.

In addition, every SRAM block has an embedded FIFO control unit. The control unit allows the SRAM block to be configured as a synchronous FIFO without using core logic modules. The FIFO width and depth are programmable. The FIFO also features programmable ALMOST-EMPTY (AEMPTY) and ALMOST-FULL (AFULL) flags in addition to the normal EMPTY and FULL flags. In addition to the flag logic, the embedded FIFO control unit also contains the counters necessary for the generation of the read and write address pointers as well as control circuitry to prevent metastability and erroneous operation. The embedded SRAM/FIFO blocks can be cascaded to create larger configurations.

# I/O Logic

The Axcelerator family of FPGAs features a flexible I/O structure, supporting a range of mixed voltages with its bank-selectable I/Os: 1.5V, 1.8V, 2.5V, and 3.3V. In all, Axcelerator FPGAs support at least 14 different I/O standards (single-ended, differential, voltage-referenced). The I/Os are organized into banks, with eight banks per device (two per side). The configuration of these banks determines the I/O standards supported (see "User I/Os" on page 2-11 for more information). All I/O standards are available in each bank.

Each I/O module has an input register (InReg), an output register (OutReg), and an enable register (EnReg) (Figure 1-7 on page 1-5). An I/O Cluster includes two I/O modules, four RX modules, two TX modules, and a buffer (B) module.

# **Design Environment**

The Axcelerator family of FPGAs is fully supported by both Microsemi's Libero<sup>®</sup> Integrated Design Environment and Designer FPGA Development software. Libero IDE is an integrated design manager that seamlessly integrates design tools while guiding the user through the design flow, managing all design and log files, and passing necessary design data among tools. Additionally, Libero IDE allows users to integrate both schematic and HDL synthesis into a single flow and verify the entire design in a single environment (see the *Libero IDE Flow* diagram located on the Microsemi SoC Products Group website). Libero IDE includes Synplify<sup>®</sup> Actel Edition (AE) from Synplicity<sup>®</sup>, ViewDraw<sup>®</sup> AE from Mentor Graphics<sup>®</sup>, Model*Sim<sup>®</sup>* HDL Simulator from Mentor Graphics, WaveFormer Lite<sup>™</sup> AE from SynaptiCAD<sup>®</sup>, and Designer software from Microsemi.

Designer software is a place-and-route tool and provides a comprehensive suite of backend support tools for FPGA development. The Designer software includes the following:

- Timer a world-class integrated static timing analyzer and constraints editor which support timing-driven place-and-route

- NetlistViewer a design netlist schematic viewer

- · ChipPlanner a graphical floorplanner viewer and editor

- SmartPower allows the designer to quickly estimate the power consumption of a design

- PinEditor a graphical application for editing pin assignments and I/O attributes

- I/O Attribute Editor displays all assigned and unassigned I/O macros and their attributes in a spreadsheet format

With the Designer software, a user can lock the design pins before layout while minimally impacting the results of place-and-route. Additionally, Microsemi's back-annotation flow is compatible with all the major simulators and the simulation results can be cross-probed with Silicon Explorer II, Microsemi's integrated verification and logic analysis tool. Another tool included in the Designer software is the SmartGen core generator, which easily creates popular and commonly used logic functions for implementation into your schematic or HDL design.

Designer software is compatible with the most popular FPGA design entry and verification tools from EDA vendors, such as Mentor Graphics, Synplicity, Synopsys, and Cadence Design Systems. The Designer software is available for both the Windows and UNIX operating systems.

# Programming

Programming support is provided through Silicon Sculptor II, a single-site programmer driven via a PCbased GUI. In addition, BP Microsystems offers multi-site programmers that provide qualified support for Microsemi devices. Factory programming is available for high-volume production needs.

# In-System Diagnostic and Debug Capabilities

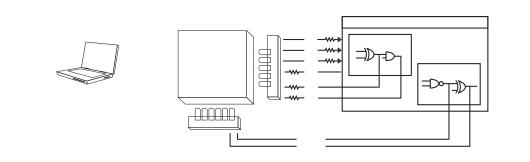

The Axcelerator family of FPGAs includes internal probe circuitry, allowing the designer to dynamically observe and analyze any signal inside the FPGA without disturbing normal device operation (Figure 1-9).

The maximum power dissipation allowed for Military temperature and Mil-Std 883B devices is specified as a function of  $\theta_{\text{ic}}$ .

| Package Type                                  | Pin Count | $\theta_{jc}$ | $\theta_{\text{ja}}\text{Still}\text{Air}$ | $\theta_{ja}$ 1.0m/s | $\theta_{ja}$ 2.5m/s | Units |

|-----------------------------------------------|-----------|---------------|--------------------------------------------|----------------------|----------------------|-------|

| Chip Scale Package (CSP)                      | 180       | N/A           | 57.8                                       | 51.0                 | 50                   | °C/W  |

| Plastic Quad Flat Pack (PQFP)                 | 208       | 8.0           | 26                                         | 23.5                 | 20.9                 | °C/W  |

| Plastic Ball Grid Array (PBGA)                | 729       | 2.2           | 13.7                                       | 10.6                 | 9.6                  | °C/W  |

| Fine Pitch Ball Grid Array (FBGA)             | 256       | 3.0           | 26.6                                       | 22.8                 | 21.5                 | °C/W  |

| Fine Pitch Ball Grid Array (FBGA)             | 324       | 3.0           | 25.8                                       | 22.1                 | 20.9                 | °C/W  |

| Fine Pitch Ball Grid Array (FBGA)             | 484       | 3.2           | 20.5                                       | 17.0                 | 15.9                 | °C/W  |

| Fine Pitch Ball Grid Array (FBGA)             | 676       | 3.2           | 16.4                                       | 13.0                 | 12.0                 | °C/W  |

| Fine Pitch Ball Grid Array (FBGA)             | 896       | 2.4           | 13.6                                       | 10.4                 | 9.4                  | °C/W  |

| Fine Pitch Ball Grid Array (FBGA)             | 1152      | 1.8           | 12.0                                       | 8.9                  | 7.9                  | °C/W  |

| Ceramic Quad Flat Pack (CQFP) <sup>1</sup>    | 208       | 2.0           | 22                                         | 19.8                 | 18.0                 | °C/W  |

| Ceramic Quad Flat Pack (CQFP) <sup>1</sup>    | 352       | 2.0           | 17.9                                       | 16.1                 | 14.7                 | °C/W  |

| Ceramic Column Grid Array (CCGA) <sup>2</sup> | 624       | 6.5           | 8.9                                        | 8.5                  | 8                    | °C/W  |

Table 2-6 • Package Thermal Characteristics

Notes:

1.  $\theta_{jc}$  for the 208-pin and 352-pin CQFP refers to the thermal resistance between the junction and the bottom of the package.

2.  $\theta_{jc}$  for the 624-pin CCGA refers to the thermal resistance between the junction and the top surface of the package. Thermal resistance from junction to board ( $\theta_{ib}$ ) for CCGA 624 package is 3.4°C/W.

## **Timing Characteristics**

Axcelerator devices are manufactured in a CMOS process, therefore, device performance varies according to temperature, voltage, and process variations. Minimum timing parameters reflect maximum operating voltage, minimum operating temperature, and best-case processing. Maximum timing parameters reflect minimum operating voltage, maximum operating temperature, and worst-case processing. The derating factors shown in Table 2-7 should be applied to all timing data contained within this datasheet.

|         | Junction Temperature |       |      |      |      |      |       |  |  |

|---------|----------------------|-------|------|------|------|------|-------|--|--|

| VCCA    | –55°C                | –40°C | 0°C  | 25°C | 70°C | 85°C | 125°C |  |  |

| 1.4 V   | 0.83                 | 0.86  | 0.91 | 0.96 | 1.02 | 1.05 | 1.15  |  |  |

| 1.425 V | 0.82                 | 0.84  | 0.90 | 0.94 | 1.00 | 1.04 | 1.13  |  |  |

| 1.5 V   | 0.78                 | 0.80  | 0.85 | 0.89 | 0.95 | 0.98 | 1.07  |  |  |

| 1.575 V | 0.74                 | 0.76  | 0.81 | 0.85 | 0.90 | 0.94 | 1.02  |  |  |

| 1.6 V   | 0.73                 | 0.75  | 0.80 | 0.84 | 0.89 | 0.92 | 1.01  |  |  |

Table 2-7 • Temperature and Voltage Timing Derating Factors(Normalized to Worst-Case Commercial, T<sub>J</sub> = 70°C, VCCA = 1.425V)

Notes:

1. The user can set the junction temperature in Designer software to be any integer value in the range of – 55°C to 175°C.

2. The user can set the core voltage in Designer software to be any value between 1.4V and 1.6V.

All timing numbers listed in this datasheet represent sample timing characteristics of Axcelerator devices. Actual timing delay values are design-specific and can be derived from the Timer tool in Microsemi's Designer software after place-and-route.

## **Timing Characteristics**

### Table 2-28 • 1.8V LVCMOS I/O Module

Worst-Case Commercial Conditions VCCA = 1.425 V, VCCI = 1.7 V, TJ = 70°C

|                     |                                                                           | -2 S | peed | –1 S | peed | Std S | Speed |       |  |

|---------------------|---------------------------------------------------------------------------|------|------|------|------|-------|-------|-------|--|

| Parameter           | Description                                                               | Min. | Max. | Min. | Max. | Min.  | Max.  | Units |  |

| LVCMOS18            | Output Module Timing                                                      |      |      |      |      |       |       |       |  |

| t <sub>DP</sub>     | Input Buffer                                                              |      | 3.26 |      | 3.71 |       | 4.37  | ns    |  |

| t <sub>PY</sub>     | Output Buffer                                                             |      | 4.55 |      | 5.18 |       | 6.09  | ns    |  |

| t <sub>ENZL</sub>   | Enable to Pad Delay through the Output Buffer—Z to Low                    |      | 2.82 |      | 2.83 |       | 2.84  | ns    |  |

| t <sub>ENZH</sub>   | Enable to Pad Delay through the Output Buffer—Z to High                   |      | 3.43 |      | 3.45 |       | 3.46  | ns    |  |

| t <sub>ENLZ</sub>   | Enable to Pad Delay through the Output Buffer—Low to Z                    |      | 6.01 |      | 6.85 |       | 8.05  | ns    |  |

| t <sub>ENHZ</sub>   | Enable to Pad Delay through the Output Buffer—High to Z                   |      | 6.73 |      | 7.67 |       | 9.01  | ns    |  |

| t <sub>IOCLKQ</sub> | Sequential Clock-to-Q for the I/O Input Register                          |      | 0.67 |      | 0.77 |       | 0.90  | ns    |  |

| t <sub>IOCLKY</sub> | Clock-to-output Y for the I/O Output Register and the I/O Enable Register |      | 0.67 |      | 0.77 |       | 0.90  | ns    |  |

| t <sub>SUD</sub>    | Data Input Set-Up                                                         |      | 0.23 |      | 0.27 |       | 0.31  | ns    |  |

| t <sub>SUE</sub>    | Enable Input Set-Up                                                       |      | 0.26 |      | 0.30 |       | 0.35  | ns    |  |

| t <sub>HD</sub>     | Data Input Hold                                                           |      | 0.00 |      | 0.00 |       | 0.00  | ns    |  |

| t <sub>HE</sub>     | Enable Input Hold                                                         |      | 0.00 |      | 0.00 |       | 0.00  | ns    |  |

| t <sub>CPWHL</sub>  | Clock Pulse Width High to Low                                             | 0.39 |      | 0.39 |      | 0.39  |       | ns    |  |

| t <sub>CPWLH</sub>  | Clock Pulse Width Low to High                                             | 0.39 |      | 0.39 |      | 0.39  |       | ns    |  |

| t <sub>WASYN</sub>  | Asynchronous Pulse Width                                                  | 0.37 |      | 0.37 |      | 0.37  |       | ns    |  |

| t <sub>REASYN</sub> | Asynchronous Recovery Time                                                |      | 0.13 |      | 0.15 |       | 0.17  | ns    |  |

| t <sub>HASYN</sub>  | Asynchronous Removal Time                                                 |      | 0.00 |      | 0.00 |       | 0.00  | ns    |  |

| t <sub>CLR</sub>    | Asynchronous Clear-to-Q                                                   |      | 0.23 |      | 0.27 |       | 0.31  | ns    |  |

| t <sub>PRESET</sub> | Asynchronous Preset-to-Q                                                  |      | 0.23 |      | 0.27 |       | 0.31  | ns    |  |

# **Module Specifications**

## **C-Cell**

### Introduction

The C-cell is one of the two logic module types in the AX architecture. It is the combinatorial logic resource in the Axcelerator device. The AX architecture implements a new combinatorial cell that is an extension of the C-cell implemented in the SX-A family. The main enhancement of the new C-cell is the addition of carry-chain logic.

The C-cell can be used in a carry-chain mode to construct arithmetic functions. If carry-chain logic is not required, it can be disabled.

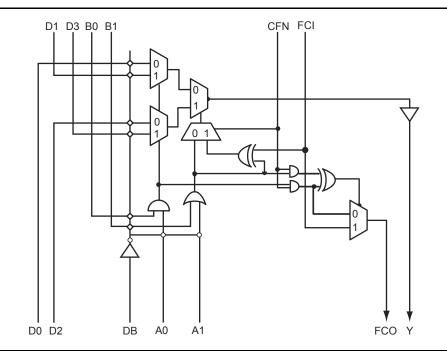

The C-cell features the following (Figure 2-27):

- Eight-input MUX (data: D0-D3, select: A0, A1, B0, B1). User signals can be routed to any one of these inputs. Any of the C-cell inputs (D0-D3, A0, A1, B0, B1) can be tied to one of the four routed clocks (CLKE/F/G/H).

- Inverter (DB input) can be used to drive a complement signal of any of the inputs to the C-cell.

- A carry input and a carry output. The carry input signal of the C-cell is the carry output from the C-cell directly to the north.

- · Carry connect for carry-chain logic with a signal propagation time of less than 0.1 ns.

- A hardwired connection (direct connect) to the adjacent R-cell (Register Cell) for all C-cells on the east side of a SuperCluster with a signal propagation time of less than 0.1 ns.

This layout of the C-cell (and the C-cell Cluster) enables the implementation of over 4,000 functions of up to five bits. For example, two C-cells can be used together to implement a four-input XOR function in a single cell delay.

The carry-chain configuration is handled automatically for the user with Microsemi's extensive macro library (please see the *Antifuse Macro Library Guide* for a complete listing of available Axcelerator macros).

Figure 2-27 • C-Cell

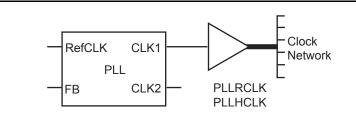

## PLLRCLK and PLLHCLK

PLLRCLK (PLLHCLK) is used to drive global resource CLK (HCLK) from a PLL (Figure 2-44).

Figure 2-44 • PLLRCLK and PLLHCLK

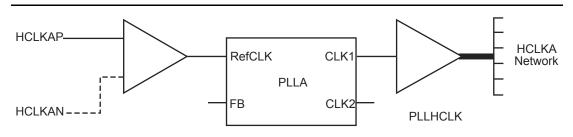

## **Using Global Resources with PLLs**

Each global resource has an associated PLL at its root. For example, PLLA can drive HCLKA, PLLE can drive CLKE, etc. (Figure 2-45).

Figure 2-45 • Example of HCLKA Driven from a PLL with External Clock Source

In addition, each clock pin of the package can be used to drive either its associated global resource or PLL. For example, package pins CLKEP and CLKEN can drive either the RefCLK input of PLLE or CLKE.

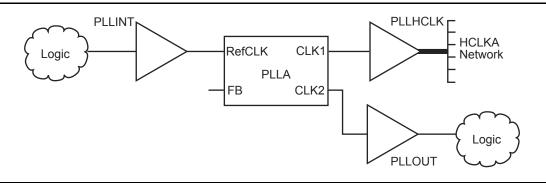

There are two macros required when interfacing the embedded PLLs with the global resources: PLLINT and PLLOUT.

## PLLINT

This macro is used to drive the RefCLK input of the PLL internally from user signals.

### PLLOUT

This macro is used to connect either the CLK1 or CLK2 output of a PLL to the regular routing network (Figure 2-46).

Figure 2-46 • Example of PLLINT and PLLOUT Usage

### Table 2-80 • PLL Interface Signals

| o              | _      | User       | Allowable                                                                           |                                                                                             |

|----------------|--------|------------|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| Signal Name    | Туре   | Accessible | Values                                                                              | Function                                                                                    |

| RefCLK         | Input  | Yes        |                                                                                     | Reference Clock for the PLL                                                                 |

| FB             | Input  | Yes        |                                                                                     | Feedback port for the PLL                                                                   |

| PowerDown      | Input  | Yes        |                                                                                     | PLL power down control                                                                      |

|                |        |            | 0                                                                                   | PLL powered down                                                                            |

|                |        |            | 1                                                                                   | PLL active                                                                                  |

|                |        |            |                                                                                     |                                                                                             |

| DIVI[5:0]      | Input  | Yes        | 1 to 64, in                                                                         | Sets value for feedback divider (multiplier)                                                |

| DIVJ[5:0]      | Input  | Yes        | unsigned binary<br>notation offset by<br>-1                                         | Sets value for CLK1 divider                                                                 |

| LowFreq        | Input  | Yes        |                                                                                     | Input frequency range selector                                                              |

|                |        |            | 0                                                                                   | 50–200 MHz                                                                                  |

|                |        |            | 1                                                                                   | 14–50 MHz                                                                                   |

| Osc[2:0]       | Input  | Yes        |                                                                                     | Output frequency range selector                                                             |

|                |        |            | XX0                                                                                 | 400–1000 MHZ                                                                                |

|                |        |            | 001                                                                                 | 200–400 MHZ                                                                                 |

|                |        |            | 011                                                                                 | 100–200 MHZ                                                                                 |

|                |        |            | 101                                                                                 | 50–100 MHZ                                                                                  |

|                |        |            | 111                                                                                 | 20–50 MHZ                                                                                   |

| DelayLine[4:0] | Input  | Yes        | -15 to +15<br>(increments), in<br>signed-and-<br>magnitude binary<br>representation | Clock Delay (positive/negative) in increments<br>of 250 ps, with maximum value of ± 3.75 ns |

| FBMuxSel       | Input  | No         |                                                                                     | Selects the source for the feedback input                                                   |

| REFSEL         | Input  | No         |                                                                                     | Selects the source for the reference clock                                                  |

| OUTSEL         | Input  | No         |                                                                                     | Selects the source for the routed net output                                                |

| PLLSEL         | Input  | No         |                                                                                     | ROOTSEL & PLLSEL are used to select the<br>source of the global clock network               |

| ROOTSEL        | Input  | No         |                                                                                     |                                                                                             |

| Lock           | Output | Yes        |                                                                                     | High value indicates PLL has locked                                                         |

| CLK1           | Output | Yes        |                                                                                     | PLL clock output                                                                            |

| CLK2           | Output | Yes        |                                                                                     | PLL clock output                                                                            |

Note: If the input RefClk is taken outside its operating range, the outputs Lock, CLK1 and CLK2 are indeterminate.

**Detailed Specifications**

# Programming

Device programming is supported through the Silicon Sculptor II, a single-site, robust and compact device programmer for the PC. Up to four Silicon Sculptor IIs can be daisy-chained and controlled from a single PC host. With standalone software for the PC, Silicon Sculptor II is designed to allow concurrent programming of multiple units from the same PC when daisy-chained.

Silicon Sculptor II programs devices independently to achieve the fastest programming times possible. Each fuse is verified by Silicon Sculptor II to ensure correct programming. Furthermore, at the end of programming, there are integrity tests that are run to ensure that programming was completed properly. Not only does it test programmed and nonprogrammed fuses, Silicon Sculptor II also provides a self-test to test its own hardware extensively.

Programming an Axcelerator device using Silicon Sculptor II is similar to programming any other antifuse device. The procedure is as follows:

- 1. Load the \*.AFM file.

- 2. Select the device to be programmed.

- 3. Begin programming.

When the design is ready to go to production, Microsemi offers device volume-programming services either through distribution partners or via our In-House Programming Center.

In addition, BP Microsystems offers multi-site programmers that provide qualified support for Axcelerator devices.

For more details on programming the Axcelerator devices, please refer to the Silicon Sculptor II User's Guide.

# Microsemi

| BG729           |               | BG729           |               |  |  |

|-----------------|---------------|-----------------|---------------|--|--|

| AX1000 Function | Pin<br>Number | AX1000 Function | Pin<br>Number |  |  |

| VCCIB0          | B4            | VCCIB4          | W17           |  |  |

| VCCIB0          | C4            | VCCIB4          | W18           |  |  |

| VCCIB0          | J10           | VCCIB5          | AE4           |  |  |

| VCCIB0          | J11           | VCCIB5          | AF4           |  |  |

| VCCIB0          | J12           | VCCIB5          | AG4           |  |  |

| VCCIB0          | K12           | VCCIB5          | V12           |  |  |

| VCCIB0          | K13           | VCCIB5          | V13           |  |  |

| VCCIB1          | A24           | VCCIB5          | W10           |  |  |

| VCCIB1          | B24           | VCCIB5          | W11           |  |  |

| VCCIB1          | C24           | VCCIB5          | W12           |  |  |

| VCCIB1          | J16           | VCCIB6          | AD1           |  |  |

| VCCIB1          | J17           | VCCIB6          | AD2           |  |  |

| VCCIB1          | J18           | VCCIB6          | AD3           |  |  |

| VCCIB1          | K15           | VCCIB6          | R10           |  |  |

| VCCIB1          | K16           | VCCIB6          | T10           |  |  |

| VCCIB2          | D25           | VCCIB6          | Т9            |  |  |

| VCCIB2          | D26           | VCCIB6          | U9            |  |  |

| VCCIB2          | D27           | VCCIB6          | V9            |  |  |

| VCCIB2          | K19           | VCCIB7          | D1            |  |  |

| VCCIB2          | L19           | VCCIB7          | D2            |  |  |

| VCCIB2          | M18           | VCCIB7          | D3            |  |  |

| VCCIB2          | M19           | VCCIB7          | K9            |  |  |

| VCCIB2          | N18           | VCCIB7          | L9            |  |  |

| VCCIB3          | AD25          | VCCIB7          | M10           |  |  |

| VCCIB3          | AD26          | VCCIB7          | M9            |  |  |

| VCCIB3          | AD27          | VCCIB7          | N10           |  |  |

| VCCIB3          | R18           | VCOMPLA         | B13           |  |  |

| VCCIB3          | T18           | VCOMPLB         | A14           |  |  |

| VCCIB3          | T19           | VCOMPLC         | A15           |  |  |

| VCCIB3          | U19           | VCOMPLD         | J15           |  |  |

| VCCIB3          | V19           | VCOMPLE         | AG15          |  |  |

| VCCIB4          | AE24          | VCOMPLF         | W15           |  |  |

| VCCIB4          | AF24          | VCOMPLG         | AC14          |  |  |

| VCCIB4          | AG24          | VCOMPLH         | W13           |  |  |

| VCCIB4          | V15           | VPUMP           | D24           |  |  |

| VCCIB4          | V16           |                 |               |  |  |

| VCCIB4          | W16           |                 |               |  |  |

Pin Number F17 D18 E17 E21 D21 E20 D20 G16 G15

> F19 E19 J16 H16 E22 D22 H19 G19 G22 F22 J17 H17 G20 F20 J18 H18 G21 F21 K19 J19 J21 H21 J20 H20 J22

| FG484          |               | FG484            |               | FG484          |  |  |

|----------------|---------------|------------------|---------------|----------------|--|--|

| AX500 Function | Pin<br>Number | AX500 Function   | Pin<br>Number | AX500 Function |  |  |

| Bank 0         |               | IO19NB0F1/HCLKAN | E11           | IO37PB1F3      |  |  |

| IO00NB0F0      | E3            | IO19PB0F1/HCLKAP | E10           | IO38NB1F3      |  |  |

| IO00PB0F0      | D3            | IO20NB0F1/HCLKBN | D12           | IO38PB1F3      |  |  |

| IO01NB0F0      | E7            | IO20PB0F1/HCLKBP | D11           | IO39NB1F3      |  |  |

| IO01PB0F0      | E6            | Bank 1           |               | IO39PB1F3      |  |  |

| IO02NB0F0      | C5            | IO21NB1F2/HCLKCN | F13           | IO40NB1F3      |  |  |

| IO02PB0F0      | C4            | IO21PB1F2/HCLKCP | F12           | IO40PB1F3      |  |  |

| IO03NB0F0      | D7            | IO22NB1F2/HCLKDN | E14           | IO41NB1F3      |  |  |

| IO03PB0F0      | D6            | IO22PB1F2/HCLKDP | E13           | IO41PB1F3      |  |  |

| IO04NB0F0      | B5            | IO24NB1F2        | A14           | Bank 2         |  |  |

| IO04PB0F0      | B4            | IO24PB1F2        | A13           | IO42NB2F4      |  |  |

| IO05NB0F0      | C7            | IO25NB1F2        | B14           | IO42PB2F4      |  |  |

| IO05PB0F0      | C6            | IO25PB1F2        | B13           | IO43NB2F4      |  |  |

| IO06NB0F0      | A5            | IO26NB1F2        | C15           | IO43PB2F4      |  |  |

| IO06PB0F0      | A4            | IO27NB1F2        | A16           | IO44NB2F4      |  |  |

| IO07NB0F0      | A7            | IO27PB1F2        | A15           | IO44PB2F4      |  |  |

| IO07PB0F0      | A6            | IO28NB1F2        | B16           | IO45NB2F4      |  |  |

| IO08NB0F0      | B7            | IO28PB1F2        | B15           | IO45PB2F4      |  |  |

| IO08PB0F0      | B6            | IO29NB1F2        | D16           | IO46NB2F4      |  |  |

| IO10NB0F0      | B9            | IO29PB1F2        | D15           | IO46PB2F4      |  |  |

| IO10PB0F0      | B8            | IO30NB1F2        | A18           | IO47NB2F4      |  |  |

| IO11NB0F0      | E9            | IO30PB1F2        | A17           | IO47PB2F4      |  |  |

| IO11PB0F0      | E8            | IO31NB1F2        | F15           | IO48NB2F4      |  |  |

| IO12NB0F1      | D9            | IO31PB1F2        | F14           | IO48PB2F4      |  |  |

| IO12PB0F1      | D8            | IO32NB1F3        | C17           | IO49NB2F4      |  |  |

| IO13NB0F1      | C9            | IO32PB1F3        | C16           | IO49PB2F4      |  |  |

| IO13PB0F1      | C8            | IO33NB1F3        | E16           | IO50NB2F4      |  |  |

| IO14NB0F1      | A9            | IO33PB1F3        | E15           | IO50PB2F4      |  |  |

| IO14PB0F1      | A8            | IO34NB1F3        | B18           | IO51NB2F4      |  |  |

| IO15NB0F1      | B10           | IO34PB1F3        | B17           | IO51PB2F4      |  |  |

| IO15PB0F1      | A10           | IO35NB1F3        | B19           | IO52NB2F5      |  |  |

| IO16NB0F1      | B12           | IO35PB1F3        | A19           | IO52PB2F5      |  |  |

| IO16PB0F1      | B11           | IO36NB1F3        | C19           | IO53NB2F5      |  |  |

| IO18NB0F1      | C13           | IO36PB1F3        | C18           | IO53PB2F5      |  |  |

| IO18PB0F1      | C12           | IO37NB1F3        | F18           | IO54NB2F5      |  |  |

| FG484          |               | FG484          |               | FG484             |               |

|----------------|---------------|----------------|---------------|-------------------|---------------|

| AX500 Function | Pin<br>Number | AX500 Function | Pin<br>Number | AX500 Function    | Pin<br>Number |

| IO54PB2F5      | H22           | IO72PB3F6      | P20           | IO90NB4F8         | Y17           |

| IO55NB2F5      | L17           | IO73PB3F6      | R19           | IO90PB4F8         | Y18           |

| IO55PB2F5      | K17           | IO74NB3F7      | V21           | IO91NB4F8         | V15           |

| IO56NB2F5      | K21           | IO74PB3F7      | U21           | IO91PB4F8         | V16           |

| IO56PB2F5      | K22           | IO75NB3F7      | V22           | IO92PB4F8         | AB17          |

| IO58NB2F5      | L20           | IO75PB3F7      | U22           | IO93NB4F8         | Y15           |

| IO58PB2F5      | K20           | IO76NB3F7      | U20           | IO93PB4F8         | Y16           |

| IO59NB2F5      | L18           | IO76PB3F7      | T20           | IO94NB4F9         | AA16          |

| IO59PB2F5      | K18           | IO77NB3F7      | R17           | IO94PB4F9         | AA17          |

| IO60NB2F5      | M21           | IO77PB3F7      | P17           | IO95NB4F9         | AB14          |

| IO60PB2F5      | L21           | IO78NB3F7      | W21           | IO95PB4F9         | AB15          |

| IO61NB2F5      | L16           | IO78PB3F7      | W22           | IO96NB4F9         | W15           |

| IO61PB2F5      | K16           | IO79NB3F7      | T18           | IO96PB4F9         | W16           |

| IO62NB2F5      | M19           | IO79PB3F7      | R18           | IO97NB4F9         | AA13          |

| IO62PB2F5      | L19           | IO80NB3F7      | W20           | IO97PB4F9         | AB13          |

| Bank 3         | 1             | IO80PB3F7      | V20           | IO98NB4F9         | AA14          |

| IO63NB3F6      | N16           | IO81NB3F7      | U19           | IO98PB4F9         | AA15          |

| IO63PB3F6      | M16           | IO81PB3F7      | T19           | IO100NB4F9        | Y14           |

| IO64NB3F6      | P22           | IO82NB3F7      | U18           | IO100PB4F9        | W14           |

| IO64PB3F6      | N22           | IO82PB3F7      | V19           | IO101NB4F9        | Y12           |

| IO65NB3F6      | N20           | IO83NB3F7      | R16           | IO101PB4F9        | Y13           |

| IO65PB3F6      | M20           | IO83PB3F7      | P16           | IO102NB4F9        | AA11          |

| IO66NB3F6      | P21           | Bank 4         |               | IO102PB4F9        | AA12          |

| IO66PB3F6      | N21           | IO84NB4F8      | AB18          | IO103NB4F9/CLKEN  | V12           |

| IO67NB3F6      | N18           | IO84PB4F8      | AB19          | IO103PB4F9/CLKEP  | V13           |

| IO67PB3F6      | N19           | IO85NB4F8      | T15           | IO104NB4F9/CLKFN  | W11           |

| IO68NB3F6      | T22           | IO85PB4F8      | T16           | IO104PB4F9/CLKFP  | W12           |

| IO68PB3F6      | R22           | IO86NB4F8      | AA18          | Bank 5            |               |

| IO69NB3F6      | N17           | IO86PB4F8      | AA19          | IO105NB5F10/CLKGN | U10           |

| IO69PB3F6      | M17           | IO87NB4F8      | W17           | IO105PB5F10/CLKGP | U11           |

| IO70NB3F6      | T21           | IO87PB4F8      | V17           | IO106NB5F10/CLKHN | V9            |

| IO70PB3F6      | R21           | IO88NB4F8      | Y19           | IO106PB5F10/CLKHP | V10           |

| IO71NB3F6      | P18           | IO88PB4F8      | W18           | IO107NB5F10       | Y10           |

| IO71PB3F6      | P19           | IO89NB4F8      | U14           | IO107PB5F10       | Y11           |

| IO72NB3F6      | R20           | IO89PB4F8      | U15           | IO108NB5F10       | AA9           |

| FG484           |               | FG484           |               | FG484           | FG484         |  |  |  |

|-----------------|---------------|-----------------|---------------|-----------------|---------------|--|--|--|

| AX1000 Function | Pin<br>Number | AX1000 Function | Pin<br>Number | AX1000 Function | Pin<br>Number |  |  |  |

| IO246NB7F22     | F3            | GND             | D4            | GND             | V5            |  |  |  |

| IO246PB7F22     | G3            | GND             | E18           | GND             | W19           |  |  |  |

| IO250NB7F23     | F4            | GND             | E5            | GND             | W4            |  |  |  |

| IO250PB7F23     | G4            | GND             | G18           | GND             | Y20           |  |  |  |

| IO253NB7F23     | G5            | GND             | H15           | GND             | Y3            |  |  |  |

| IO253PB7F23     | G6            | GND             | H8            | GND/LP          | G7            |  |  |  |

| IO254NB7F23     | D1            | GND             | J14           | PRA             | G11           |  |  |  |

| IO254PB7F23     | E1            | GND             | J9            | PRB             | F11           |  |  |  |

| IO257NB7F23     | F5            | GND             | K10           | PRC             | T12           |  |  |  |

| IO257PB7F23     | E4            | GND             | K11           | PRD             | U12           |  |  |  |

| Dedicated I/    | 0             | GND             | K12           | ТСК             | G8            |  |  |  |

| VCCDA           | H7            | GND             | K13           | TDI             | F9            |  |  |  |

| GND             | A1            | GND             | L1            | TDO             | F7            |  |  |  |

| GND             | A11           | GND             | L10           | TMS             | F6            |  |  |  |

| GND             | A12           | GND             | L11           | TRST            | F8            |  |  |  |

| GND             | A2            | GND             | L12           | VCCA            | G17           |  |  |  |

| GND             | A21           | GND             | L13           | VCCA            | J10           |  |  |  |

| GND             | A22           | GND             | L22           | VCCA            | J11           |  |  |  |

| GND             | AA1           | GND             | M1            | VCCA            | J12           |  |  |  |

| GND             | AA2           | GND             | M10           | VCCA            | J13           |  |  |  |

| GND             | AA21          | GND             | M11           | VCCA            | J7            |  |  |  |

| GND             | AA22          | GND             | M12           | VCCA            | K14           |  |  |  |

| GND             | AB1           | GND             | M13           | VCCA            | K9            |  |  |  |

| GND             | AB11          | GND             | M22           | VCCA            | L14           |  |  |  |

| GND             | AB12          | GND             | N10           | VCCA            | L9            |  |  |  |

| GND             | AB2           | GND             | N11           | VCCA            | M14           |  |  |  |

| GND             | AB21          | GND             | N12           | VCCA            | M9            |  |  |  |

| GND             | AB22          | GND             | N13           | VCCA            | N14           |  |  |  |

| GND             | B1            | GND             | P14           | VCCA            | N9            |  |  |  |

| GND             | B2            | GND             | P9            | VCCA            | P10           |  |  |  |

| GND             | B21           | GND             | R15           | VCCA            | P11           |  |  |  |

| GND             | B22           | GND             | R8            | VCCA            | P12           |  |  |  |

| GND             | C20           | GND             | U16           | VCCA            | P13           |  |  |  |

| GND             | C3            | GND             | U6            | VCCA            | Т6            |  |  |  |

| GND             | D19           | GND             | V18           | VCCA            | U17           |  |  |  |

## Note

For Package Manufacturing and Environmental information, visit Resource center at http://www.microsemi.com/soc/products/rescenter/package/index.html.

Pin Number M8 Μ7 K4 L4 L6 M6 K5 L5 J4 J3 G2 H2 L8 L7 G3 H3 G4 H4 J6 K6 H5 J5 F2 F1 K8 K7 F4 F3 G6 H6 F5 G5 H7 J7

| FG896           |               | FG896           |               | FG896           |   |  |

|-----------------|---------------|-----------------|---------------|-----------------|---|--|

| AX1000 Function | Pin<br>Number | AX1000 Function | Pin<br>Number | AX1000 Function |   |  |

| IO206PB6F19     | AB4           | IO224NB6F20     | R2            | IO241NB7F22     |   |  |

| IO207NB6F19     | W6            | IO224PB6F20     | T2            | IO241PB7F22     |   |  |

| IO207PB6F19     | W7            | Bank 7          |               | IO242NB7F22     |   |  |

| IO208NB6F19     | AB3           | IO225NB7F21     | R7            | IO242PB7F22     |   |  |

| IO208PB6F19     | AC3           | IO225PB7F21     | R6            | IO243NB7F22     |   |  |

| IO209NB6F19     | V8            | IO226NB7F21     | R4            | IO243PB7F22     | Γ |  |

| IO209PB6F19     | V9            | IO226PB7F21     | R5            | IO244NB7F22     |   |  |

| IO210NB6F19     | AA2           | IO227NB7F21     | R8            | IO244PB7F22     | Γ |  |

| IO210PB6F19     | AA1           | IO227PB7F21     | R9            | IO245NB7F22     | T |  |

| IO211NB6F19     | V5            | IO228NB7F21     | P1            | IO245PB7F22     |   |  |

| IO211PB6F19     | W5            | IO228PB7F21     | R1            | IO246NB7F22     |   |  |

| IO212NB6F19     | Y3            | IO229NB7F21     | P9            | IO246PB7F22     |   |  |

| IO212PB6F19     | Y4            | IO229PB7F21     | P8            | IO247NB7F23     |   |  |

| IO213NB6F19     | V7            | IO230NB7F21     | N2            | IO247PB7F23     | T |  |

| IO213PB6F19     | V6            | IO230PB7F21     | P2            | IO248NB7F23     |   |  |

| IO214NB6F20     | W3            | IO231NB7F21     | P7            | IO248PB7F23     |   |  |

| IO214PB6F20     | W4            | IO231PB7F21     | P6            | IO249NB7F23     |   |  |

| IO215NB6F20     | U8            | IO232NB7F21     | N3            | IO249PB7F23     |   |  |

| IO215PB6F20     | U9            | IO232PB7F21     | P3            | IO250NB7F23     |   |  |

| IO216NB6F20     | W1            | IO233NB7F21     | P4            | IO250PB7F23     |   |  |

| IO216PB6F20     | W2            | IO233PB7F21     | P5            | IO251NB7F23     |   |  |

| IO217NB6F20     | U7            | IO234NB7F21     | L1            | IO251PB7F23     |   |  |

| IO217PB6F20     | U6            | IO234PB7F21     | M1            | IO252NB7F23     |   |  |

| IO218NB6F20     | U4            | IO235NB7F21     | M4            | IO252PB7F23     |   |  |

| IO218PB6F20     | V4            | IO235PB7F21     | N4            | IO253NB7F23     |   |  |

| IO219NB6F20     | T5            | IO236NB7F22     | N7            | IO253PB7F23     |   |  |

| IO219PB6F20     | U5            | IO236PB7F22     | N6            | IO254NB7F23     |   |  |

| IO220NB6F20     | U3            | IO237NB7F22     | N8            | IO254PB7F23     |   |  |

| IO220PB6F20     | V3            | IO237PB7F22     | N9            | IO255NB7F23     |   |  |

| IO221NB6F20     | Т8            | IO238NB7F22     | M5            | IO255PB7F23     |   |  |

| IO221PB6F20     | Т9            | IO238PB7F22     | N5            | IO256NB7F23     |   |  |

| IO222NB6F20     | U2            | IO239NB7F22     | L2            | IO256PB7F23     |   |  |

| IO222PB6F20     | V2            | IO239PB7F22     | M2            | IO257NB7F23     | Ī |  |

| IO223NB6F20     | T7            | IO240NB7F22     | L3            | IO257PB7F23     |   |  |

| IO223PB6F20     | T6            | IO240PB7F22     | M3            | Dedicated I/    | 0 |  |

| FG896           |               | FG896           |               |  |

|-----------------|---------------|-----------------|---------------|--|

| AX2000 Function | Pin<br>Number | AX2000 Function | Pin<br>Number |  |

| VCCIB3          | AH30          | VCCIB6          | W9            |  |

| VCCIB3          | T21           | VCCIB6          | Y10           |  |

| VCCIB3          | U21           | VCCIB6          | Y9            |  |

| VCCIB3          | V21           | VCCIB7          | C1            |  |

| VCCIB3          | W21           | VCCIB7          | C2            |  |

| VCCIB3          | W22           | VCCIB7          | K9            |  |

| VCCIB3          | Y21           | VCCIB7          | L10           |  |

| VCCIB3          | Y22           | VCCIB7          | L9            |  |

| VCCIB4          | AA16          | VCCIB7          | M10           |  |

| VCCIB4          | AA17          | VCCIB7          | M9            |  |

| VCCIB4          | AA18          | VCCIB7          | N10           |  |

| VCCIB4          | AA19          | VCCIB7          | P10           |  |

| VCCIB4          | AA20          | VCCIB7          | R10           |  |

| VCCIB4          | AB19          | VCCPLA          | G14           |  |

| VCCIB4          | AB20          | VCCPLB          | H15           |  |

| VCCIB4          | AB21          | VCCPLC          | G17           |  |

| VCCIB4          | AJ28          | VCCPLD          | J16           |  |

| VCCIB4          | AK28          | VCCPLE          | AH17          |  |

| VCCIB5          | AA11          | VCCPLF          | AC16          |  |

| VCCIB5          | AA12          | VCCPLG          | AH14          |  |

| VCCIB5          | AA13          | VCCPLH          | AD15          |  |

| VCCIB5          | AA14          | VCOMPLA         | F14           |  |

| VCCIB5          | AA15          | VCOMPLB         | J15           |  |

| VCCIB5          | AB10          | VCOMPLC         | F17           |  |

| VCCIB5          | AB11          | VCOMPLD         | H16           |  |

| VCCIB5          | AB12          | VCOMPLE         | AF17          |  |

| VCCIB5          | AJ3           | VCOMPLF         | AD16          |  |

| VCCIB5          | AK3           | VCOMPLG         | AF14          |  |

| VCCIB6          | AA9           | VCOMPLH         | AB15          |  |

| VCCIB6          | AH1           | VPUMP           | G24           |  |

| VCCIB6          | AH2           |                 |               |  |

| VCCIB6          | T10           |                 |               |  |

| VCCIB6          | U10           |                 |               |  |

| VCCIB6          | V10           |                 |               |  |

| VCCIB6          | W10           |                 |               |  |

| FG1152          |               | FG1152          |               | FG1152          |               |

|-----------------|---------------|-----------------|---------------|-----------------|---------------|

| AX2000 Function | Pin<br>Number | AX2000 Function | Pin<br>Number | AX2000 Function | Pin<br>Number |

| IO103PB2F9      | M28           | IO121NB2F11     | T27           | IO138NB3F12     | Y29           |

| IO104NB2F9      | M34           | IO121PB2F11     | T26           | IO138PB3F12     | W29           |

| IO104PB2F9      | L34           | IO122NB2F11     | T30           | IO139NB3F13     | Y27           |

| IO105NB2F9      | P27           | IO122PB2F11     | T29           | IO139PB3F13     | W27           |

| IO105PB2F9      | N27           | IO123NB2F11     | U28           | IO140NB3F13     | AA33          |

| IO106NB2F9      | M32           | IO123PB2F11     | T28           | IO140PB3F13     | Y33           |

| IO106PB2F9      | M31           | IO124NB2F11     | T31           | IO141NB3F13     | Y25           |

| IO107NB2F10     | P25           | IO124PB2F11     | T32           | IO141PB3F13     | Y24           |

| IO107PB2F10     | P26           | IO125NB2F11     | U24           | IO142NB3F13     | AA31          |

| IO108NB2F10     | N33           | IO125PB2F11     | U25           | IO142PB3F13     | Y31           |

| IO108PB2F10     | M33           | IO126NB2F11     | U33           | IO143NB3F13     | AA28          |

| IO109NB2F10     | P29           | IO126PB2F11     | U34           | IO143PB3F13     | Y28           |

| IO109PB2F10     | N29           | IO127NB2F11     | U26           | IO144NB3F13     | AA34          |

| IO110NB2F10     | P30           | IO127PB2F11     | U27           | IO144PB3F13     | Y34           |

| IO110PB2F10     | N30           | IO128NB2F11     | U31           | IO145NB3F13     | AA26          |

| IO111NB2F10     | R24           | IO128PB2F11     | U32           | IO145PB3F13     | Y26           |

| IO111PB2F10     | R25           | Bank 3          |               | IO146NB3F13     | AA29          |

| IO112NB2F10     | P31           | IO129NB3F12     | V29           | IO146PB3F13     | AA30          |

| IO112PB2F10     | N31           | IO129PB3F12     | U29           | IO147NB3F13     | AB30          |

| IO113NB2F10     | R28           | IO130NB3F12     | V31           | IO147PB3F13     | AB29          |

| IO113PB2F10     | P28           | IO130PB3F12     | V32           | IO148NB3F13     | AB32          |

| IO114NB2F10     | P32           | IO131NB3F12     | V24           | IO148PB3F13     | AA32          |

| IO114PB2F10     | N32           | IO131PB3F12     | V25           | IO149NB3F13     | AB27          |

| IO115NB2F10     | R30           | IO132NB3F12     | W28           | IO149PB3F13     | AA27          |

| IO115PB2F10     | R29           | IO132PB3F12     | V28           | IO150NB3F14     | AC31          |

| IO116NB2F10     | P34           | IO133NB3F12     | W26           | IO150PB3F14     | AB31          |

| IO116PB2F10     | P33           | IO133PB3F12     | V26           | IO151NB3F14     | AD33          |

| IO117NB2F10     | R27           | IO134NB3F12     | W33           | IO151PB3F14     | AC33          |

| IO117PB2F10     | R26           | IO134PB3F12     | V33           | IO152NB3F14     | AC28          |

| IO118NB2F11     | R34           | IO135NB3F12     | W25           | IO152PB3F14     | AB28          |

| IO118PB2F11     | R33           | IO135PB3F12     | W24           | IO153NB3F14     | AB25          |

| IO119NB2F11     | T24           | IO136NB3F12     | W31           | IO153PB3F14     | AA25          |

| IO119PB2F11     | T25           | IO136PB3F12     | W32           | IO154NB3F14     | AD32          |

| IO120NB2F11     | Т33           | IO137NB3F12     | Y30           | IO154PB3F14     | AC32          |

| IO120PB2F11     | T34           | IO137PB3F12     | W30           | IO155NB3F14     | AD29          |

| CQ352          |               |  |  |

|----------------|---------------|--|--|

| AX250 Function | Pin<br>Number |  |  |

| VCCDA          | 346           |  |  |

| VCCIB0         | 321           |  |  |

| VCCIB0         | 333           |  |  |

| VCCIB0         | 344           |  |  |

| VCCIB1         | 273           |  |  |

| VCCIB1         | 285           |  |  |

| VCCIB1         | 297           |  |  |

| VCCIB2         | 227           |  |  |

| VCCIB2         | 239           |  |  |

| VCCIB2         | 245           |  |  |

| VCCIB2         | 257           |  |  |

| VCCIB3         | 185           |  |  |

| VCCIB3         | 197           |  |  |

| VCCIB3         | 203           |  |  |

| VCCIB3         | 215           |  |  |

| VCCIB4         | 144           |  |  |

| VCCIB4         | 156           |  |  |

| VCCIB4         | 168           |  |  |

| VCCIB5         | 96            |  |  |

| VCCIB5         | 108           |  |  |

| VCCIB5         | 120           |  |  |

| VCCIB6         | 50            |  |  |

| VCCIB6         | 62            |  |  |

| VCCIB6         | 68            |  |  |

| VCCIB6         | 80            |  |  |

| VCCIB7         | 8             |  |  |

| VCCIB7         | 20            |  |  |

| VCCIB7         | 26            |  |  |

| VCCIB7         | 38            |  |  |

| VCCPLA         | 317           |  |  |

| VCCPLB         | 315           |  |  |

| VCCPLC         | 303           |  |  |

| VCCPLD         | 301           |  |  |

| VCCPLE         | 140           |  |  |

| VCCPLF         | 138           |  |  |

| CQ352          |               |

|----------------|---------------|

| AX250 Function | Pin<br>Number |

| VCCPLG         | 126           |

| VCCPLH         | 124           |

| VCOMPLA        | 318           |

| VCOMPLB        | 316           |

| VCOMPLC        | 304           |

| VCOMPLD        | 302           |

| VCOMPLE        | 141           |

| VCOMPLF        | 139           |

| VCOMPLG        | 127           |

| VCOMPLH        | 125           |

| VPUMP          | 267           |

3-102

| CG624           |               | CG624            |               | CG624           |               |

|-----------------|---------------|------------------|---------------|-----------------|---------------|

| AX2000 Function | Pin<br>Number | AX2000 Function  | Pin<br>Number | AX2000 Function | Pin<br>Number |

| Bank 0          |               | IO27NB0F2        | H10           | IO51NB1F4       | E15           |

| IO00NB0F0       | D7*           | IO27PB0F2        | H9            | IO51PB1F4       | F15           |

| IO00PB0F0       | E7*           | IO28NB0F2        | A9            | IO52NB1F4       | A17           |

| IO01NB0F0       | G7            | IO28PB0F2        | B9            | IO55NB1F5       | G16           |

| IO01PB0F0       | G6            | IO30NB0F2        | B11           | IO55PB1F5       | H16           |

| IO02NB0F0       | B5            | IO30PB0F2        | B10           | IO56NB1F5       | A20           |

| IO02PB0F0       | B4            | IO31NB0F2        | E11           | IO56PB1F5       | A19           |

| IO04PB0F0       | C7            | IO31PB0F2        | F11           | IO57NB1F5       | D16           |

| IO05NB0F0       | F8            | IO33NB0F2        | D12           | IO57PB1F5       | D15           |

| IO05PB0F0       | F7            | IO33PB0F2        | D11           | IO58NB1F5       | A22           |

| IO06NB0F0       | H8            | IO34NB0F3        | A11           | IO58PB1F5       | A21           |

| IO06PB0F0       | H7            | IO34PB0F3        | A10           | IO59NB1F5       | F16           |

| IO11NB0F0       | J8            | IO37NB0F3        | J13           | IO61NB1F5       | G17           |

| IO11PB0F0       | J7            | IO37PB0F3        | K13           | IO61PB1F5       | H17           |

| IO12PB0F1       | B6            | IO38NB0F3        | H11           | IO62NB1F5       | B17           |

| IO13NB0F1       | E9*           | IO38PB0F3        | G11           | IO62PB1F5       | B16           |

| IO13PB0F1       | D8*           | IO40PB0F3        | B12           | IO63NB1F5       | H18           |

| IO15NB0F1       | C9            | IO41NB0F3/HCLKAN | G13           | IO65NB1F6       | C17           |

| IO15PB0F1       | C8            | IO41PB0F3/HCLKAP | G12           | IO66PB1F6       | B18           |

| IO16NB0F1       | A5            | IO42NB0F3/HCLKBN | C13           | IO67NB1F6       | J18           |

| IO16PB0F1       | A4            | IO42PB0F3/HCLKBP | C12           | IO67PB1F6       | J19           |

| IO17NB0F1       | D10           | Bank 1           |               | IO68NB1F6       | B20           |

| IO17PB0F1       | D9            | IO43NB1F4/HCLKCN | G15           | IO68PB1F6       | B19           |

| IO18NB0F1       | A7            | IO43PB1F4/HCLKCP | G14           | IO69NB1F6       | E17           |

| IO18PB0F1       | A6            | IO44NB1F4/HCLKDN | B14           | IO69PB1F6       | F17           |

| IO19NB0F1       | G9            | IO44PB1F4/HCLKDP | B13           | IO70NB1F6       | B22           |

| IO19PB0F1       | G8            | IO45NB1F4        | H13           | IO70PB1F6       | B21           |

| IO20PB0F1       | B7            | IO47NB1F4        | D14           | IO71PB1F6       | G18           |

| IO23NB0F2       | F10           | IO47PB1F4        | C14           | IO73NB1F6       | G19           |

| IO23PB0F2       | F9            | IO48NB1F4        | A16           | IO74NB1F6       | C19           |

| IO26NB0F2       | C11*          | IO48PB1F4        | A15           | IO74PB1F6       | C18           |

| IO26PB0F2       | B8*           | IO49PB1F4        | H15           | IO75NB1F6       | D18           |

Note: \*Not routed on the same package layer and to adjacent LGA pads as its differential pair complement. Recommended to be used as a single-ended I/O. Note: \*Not routed on the same package layer and to adjacent LGA pads as its differential pair complement. Recommended to be used as a single-ended I/O.

Note: \*Not routed on the same package layer and to adjacent LGA pads as its differential pair complement. Recommended to be used as a single-ended I/O.

| Revision                     | Changes                                                                                                                                                                                                                                                                                                                                                                           | Page                                     |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| Revision 8<br>(continued)    | The following changes were made in the "FG676"(AX500) section:         AE2, AE25       Change from NC to GND.         AF2, AF25       Changed from GND to NC         AB4, AF24, C1, C26       Changed from V <sub>CCDA</sub> to V <sub>CCA</sub> AD15       Change from V <sub>CCDA</sub> to V <sub>COMPLE</sub> AD17       Changed from V <sub>COMPLE</sub> to V <sub>CCDA</sub> | 3-37                                     |

|                              | In the "FG896" (AX2000) section, the AK28 changed from VCCIB5 to VCCIB4.                                                                                                                                                                                                                                                                                                          | 3-52                                     |

|                              | The "CQ352" and "CG624" sections are new.                                                                                                                                                                                                                                                                                                                                         | 3-98, 3-115                              |

| Revision 7                   | All I/O FIFO capability was removed.                                                                                                                                                                                                                                                                                                                                              | n/a                                      |

| (Advance v1.6)               | Table 1 was updated.                                                                                                                                                                                                                                                                                                                                                              | i                                        |

|                              | Figure 1-9 was updated.                                                                                                                                                                                                                                                                                                                                                           | 1-7                                      |

|                              | Figure 2-5 was updated.                                                                                                                                                                                                                                                                                                                                                           | 2-16                                     |

|                              | The "Using an I/O Register" section was updated.                                                                                                                                                                                                                                                                                                                                  | 2-16                                     |

|                              | The AX250 and AX1000 descriptions were added to the "FG484"section.                                                                                                                                                                                                                                                                                                               | 3-21                                     |

| Revision 6                   | Table 2-3 was updated.                                                                                                                                                                                                                                                                                                                                                            | 2-2                                      |

| (Advance v1.5)               | Figure 2-1 was updated.                                                                                                                                                                                                                                                                                                                                                           | 2-8                                      |

|                              | Figure 2-48 was updated.                                                                                                                                                                                                                                                                                                                                                          | 2-75                                     |

|                              | Figure 2-52 was updated.                                                                                                                                                                                                                                                                                                                                                          | 2-82                                     |

| Revision 5<br>(Advance v1.4) | In the "PQ208" table, pin 196 was missing, but it has been added in this version with a function of GND.                                                                                                                                                                                                                                                                          | 3-84                                     |

|                              | The following pins in the "FG484" table for AX500 were changed:<br>Pin G7 is GND/LP<br>Pins AB8, C10, C11, C14, AB16 are NC.                                                                                                                                                                                                                                                      | 3-21                                     |

|                              | The "FG676" table was updated.                                                                                                                                                                                                                                                                                                                                                    | 3-37                                     |

| Revision 4                   | The "Device Resources" section was updated for the CS180.                                                                                                                                                                                                                                                                                                                         | ii                                       |

| (Advance v1.3)               | The "Programmable Interconnect Element" and Figure 1-2 are new.                                                                                                                                                                                                                                                                                                                   | "<br>1-1 and 1-2                         |

|                              | The "CS180" table is new.                                                                                                                                                                                                                                                                                                                                                         | 3-1                                      |

|                              | The "PQ208" tables for the AX500 were updated. The following pins were not<br>defined in the previous version:<br>GND 21<br>IO106PB5F10/CLKHP 71<br>GND 136                                                                                                                                                                                                                       | 3-84                                     |

| Revision 3<br>(Advance v1.2) | Table 1, "Ordering Information", "Device Resources", and the Product Plan table were updated.                                                                                                                                                                                                                                                                                     | i, ii                                    |

|                              | The following figures and tables were updated:<br>Figure 1-3<br>Figure 1-8 (new)<br>Table 2-3<br>Figure 2-2<br>Table 2-8<br>Figure 2-11                                                                                                                                                                                                                                           | 1-2<br>1-6<br>2-2<br>2-9<br>2-12<br>2-23 |

|                              | The "Design Environment" section was updated.                                                                                                                                                                                                                                                                                                                                     | 1-7                                      |

|                              | The "Package Thermal Characteristics" was updated.                                                                                                                                                                                                                                                                                                                                | 2-6                                      |