Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                                         |

|--------------------------------|-------------------------------------------------------------------------|

| Product Status                 | Active                                                                  |

| Number of LABs/CLBs            | 18144                                                                   |

| Number of Logic Elements/Cells | -                                                                       |

| Total RAM Bits                 | 165888                                                                  |

| Number of I/O                  | 317                                                                     |

| Number of Gates                | 1000000                                                                 |

| Voltage - Supply               | 1.425V ~ 1.575V                                                         |

| Mounting Type                  | Surface Mount                                                           |

| Operating Temperature          | -40°C ~ 85°C (TA)                                                       |

| Package / Case                 | 484-BGA                                                                 |

| Supplier Device Package        | 484-FPBGA (23x23)                                                       |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/ax1000-fg484i |

|                                |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 – General Description

Axcelerator devices offer high performance at densities of up to two million equivalent system gates. Based upon the Microsemi AX architecture, Axcelerator has several system-level features such as embedded SRAM (with complete FIFO control logic), PLLs, segmentable clocks, chip-wide highway routing, and carry logic.

# **Device Architecture**

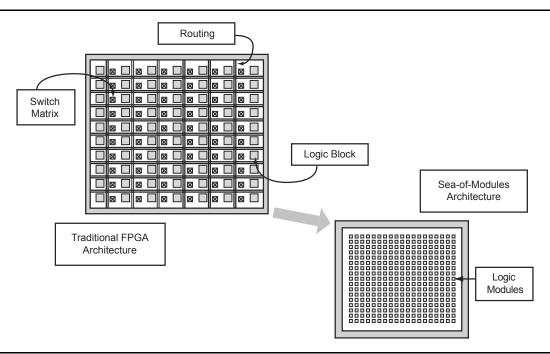

AX architecture, derived from the highly-successful SX-A sea-of-modules architecture, has been designed for high performance and total logic module utilization (Figure 1-1). Unlike in traditional FPGAs, the entire floor of the Axcelerator device is covered with a grid of logic modules, with virtually no chip area lost to interconnect elements or routing.

# Programmable Interconnect Element

The Axcelerator family uses a patented metal-to-metal antifuse programmable interconnect element that resides between the upper two layers of metal (Figure 1-2 on page 1-2). This completely eliminates the channels of routing and interconnect resources between logic modules (as implemented on traditional FPGAs) and enables the efficient sea-of-modules architecture. The antifuses are normally open circuit and, when programmed, form a permanent, passive, low-impedance connection, leading to the fastest signal propagation in the industry. In addition, the extremely small size of these interconnect elements gives the Axcelerator family abundant routing resources.

The very nature of Microsemi's nonvolatile antifuse technology provides excellent protection against design pirating and cloning (FuseLock technology). Typical cloning attempts are impossible (even if the security fuse is left unprogrammed) as no bitstream or programming file is ever downloaded or stored in the device. Reverse engineering is virtually impossible due to the difficulty of trying to distinguish between programmed and unprogrammed antifuses and also due to the programming methodology of antifuse devices (see "Security" on page 2-108).

Figure 1-1 • Sea-of-Modules Comparison

# **Calculating Power Dissipation**

### Table 2-3 • Standby Current

|        |                 | ICCA              | ICCDA               | ICCE          | BANK          | ICCPLL             | IC                              | CCP <sup>1</sup> |                               |       |

|--------|-----------------|-------------------|---------------------|---------------|---------------|--------------------|---------------------------------|------------------|-------------------------------|-------|

|        |                 | Standby           | Standby<br>Current, |               |               | Standby            | Standby Current,<br>Charge Pump |                  |                               |       |

| Device | Temperature     | Current<br>(Core) | Differential<br>I/O | 2.5 V<br>VCCI | 3.3 V<br>VCCI | Current<br>per PLL | Active                          | Bypassed<br>Mode | IIH, IIL,<br>IOZ <sup>2</sup> | Units |

| AX125  | Typical at 25°C | 1.5               | 1.5                 | 0.2           | 0.3           | 0.2                | 0.3                             | 0.01             | ±0.01                         | mA    |

|        | 70°C            | 15                | 6                   | 0.5           | 0.75          | 1                  | 0.4                             | 0.01             | ±0.01                         | mA    |

|        | 85°C            | 25                | 6                   | 0.6           | 0.8           | 1                  | 0.4                             | 0.2              | ±0.01                         | mA    |

|        | 125°C           | 50                | 8                   | 1             | 1.5           | 2                  | 0.4                             | 0.5              | ±0.01                         | mA    |

| AX250  | Typical at 25°C | 1.5               | 1.4                 | 0.25          | 0.4           | 0.2                | 0.3                             | 0.01             | ±0.01                         | mA    |

|        | 70°C            | 30                | 7                   | 0.8           | 0.9           | 1                  | 0.4                             | 0.01             | ±0.01                         | mA    |

|        | 85°C            | 40                | 7                   | 0.8           | 1             | 1                  | 0.4                             | 0.2              | ±0.01                         | mA    |

|        | 125°C           | 70                | 9                   | 1.3           | 1.8           | 2                  | 0.4                             | 0.5              | ±0.01                         | mA    |

| AX500  | Typical at 25°C | 5                 | 1.4                 | 0.4           | 0.75          | 0.2                | 0.3                             | 0.01             | ±0.01                         | mA    |

|        | 70°C            | 60                | 7                   | 1             | 1.5           | 1                  | 0.4                             | 0.01             | ±0.01                         | mA    |

|        | 85°C            | 80                | 7                   | 1             | 1.9           | 1                  | 0.4                             | 0.2              | ±0.01                         | mA    |

|        | 125°C           | 180               | 9                   | 1.75          | 2.5           | 1.5                | 0.4                             | 0.5              | ±0.01                         | mA    |

| AX1000 | Typical at 25°C | 7.5               | 1.5                 | 0.5           | 1.25          | 0.2                | 0.3                             | 0.01             | ±0.01                         | mA    |

|        | 70°C            | 80                | 8                   | 1.5           | 3             | 1                  | 0.4                             | 0.01             | ±0.01                         | mA    |

|        | 85°C            | 120               | 8                   | 1.5           | 3.4           | 1                  | 0.4                             | 0.2              | ±0.01                         | mA    |

|        | 125°C           | 200               | 10                  | 3             | 4             | 1.5                | 0.4                             | 0.5              | ±0.01                         | mA    |

| AX2000 | Typical at 25°C | 20                | 1.6                 | 0.7           | 1.5           | 0.2                | 0.3                             | 0.01             | ±0.01                         | mA    |

|        | 70°C            | 160               | 10                  | 2             | 7             | 1                  | 0.4                             | 0.01             | ±0.01                         | mA    |

|        | 85°C            | 200               | 10                  | 3             | 8             | 1                  | 0.4                             | 0.2              | ±0.01                         | mA    |

|        | 125°C           | 500               | 15                  | 4             | 10            | 1.5                | 0.4                             | 0.5              | ±0.01                         | mA    |

Notes:

1. ICCCP Active is the ICCDA or the Internal Charge Pump current. ICCCP Bypassed mode is the External Charge Pump current IIH (VPUMP pin).

2. IIH, IIL, or IOZ values are measured with inputs at the same level as VCCI for IIH and GND for IIL and IOZ.

# I/O Banks and Compatibility

Since each I/O bank has its own user-assigned input reference voltage (VREF) and an input/output supply voltage (VCCI), only I/Os with compatible standards can be assigned to the same bank.

Table 2-11 shows the compatible I/O standards for a common VREF (for voltage-referenced standards). Similarly, Table 2-12 shows compatible standards for a common VCCI.

#### Table 2-11 • Compatible I/O Standards for Different VREF Values

| VREF   | Compatible Standards         |

|--------|------------------------------|

| 1.5 V  | SSTL 3 (Class I and II)      |

| 1.25 V | SSTL 2 (Class I and II)      |

| 1.0 V  | GTL+ (2.5V and 3.3V Outputs) |

| 0.75 V | HSTL (Class I)               |

#### Table 2-12 • Compatible I/O Standards for Different VCCI Values

| VCCI <sup>1</sup> | Compatible Standards                                       | VREF |

|-------------------|------------------------------------------------------------|------|

| 3.3 V             | LVTTL, PCI, PCI-X, LVPECL, GTL+ 3.3 V                      | 1.0  |

| 3.3 V             | SSTL 3 (Class I and II), LVTTL, PCI, LVPECL                | 1.5  |

| 2.5 V             | LVCMOS 2.5 V, GTL+ 2.5 V, LVDS <sup>2</sup>                | 1.0  |

| 2.5 V             | LVCMOS 2.5 V, SSTL 2 (Classes I and II), LVDS <sup>2</sup> | 1.25 |

| 1.8 V             | LVCMOS 1.8 V                                               | N/A  |

| 1.5 V             | LVCMOS 1.5 V, HSTL Class I                                 | 0.75 |

Notes:

1. VCCI is used for both inputs and outputs

2. VCCI tolerance is ±5%

### Using the Differential I/O Standards

Differential I/O macros should be instantiated in the netlist. The settings for these I/O standards cannot be changed inside Designer. Note that there are no tristated or bidirectional I/O buffers for differential standards.

### Using the Voltage-Referenced I/O Standards

Using these I/O standards is similar to that of single-ended I/O standards. Their settings can be changed in Designer.

### Using DDR (Double Data Rate)

In Double Data Rate mode, new data is present on every transition of the clock signal. Clock and data lines have identical bandwidth and signal integrity requirements, making it very efficient for implementing very high-speed systems.

To implement a DDR, users need to:

- 1. Instantiate an input buffer (with the required I/O standard)

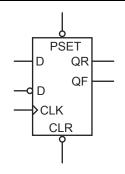

- 2. Instantiate the DDR\_REG macro (Figure 2-6)

- 3. Connect the output from the Input buffer to the input of the DDR macro

Figure 2-6 • DDR Register

### Macros for Specific I/O Standards

There are different macro types for any I/O standard or feature that determine the required VCCI and VREF voltages for an I/O. The generic buffer macros require the LVTTL standard with slow slew rate and 24 mA-drive strength. LVTTL can support high slew rate but this should only be used for critical signals.

Most of the macro symbols represent variations of the six generic symbol types:

- CLKBUF: Clock Buffer

- HCLKBUF: Hardwired Clock Buffer

- INBUF: Input Buffer

- OUTBUF: Output Buffer

- TRIBUF: Tristate Buffer

- BIBUF: Bidirectional Buffer

Other macros include the following:

- Differential I/O standard macros: The LVDS and LVPECL macros either have a pair of differential inputs (e.g. INBUF\_LVDS) or a pair of differential outputs (e.g. OUTBUF\_LVPECL).

- Pull-up and pull-down variations of the INBUF, BIBUF, and TRIBUF macros. These are available only with TTL and LVCMOS thresholds. They can be used to model the behavior of the pull-up and pull-down resistors available in the architecture. Whenever an input pin is left unconnected, the output pin will either go high or low rather than unknown. This allows users to leave inputs unconnected without having the negative effect on simulation of propagating unknowns.

- DDR\_REG macro. It can be connected to any I/O standard input buffers (i.e. INBUF) to implement a double data rate register. Designer software will map it to the I/O module in the same way it maps the other registers to the I/O module.

#### Table 2-22 • 3.3 V LVTTL I/O Module

## Worst-Case Commercial Conditions VCCA = 1.425 V, VCCI = 3.0 V, $T_J$ = 70°C (continued)

|                     | -2 Speed                                                                  |      | peed  | –1 S | peed  | Std Speed |       |       |

|---------------------|---------------------------------------------------------------------------|------|-------|------|-------|-----------|-------|-------|

| Parameter           | Description                                                               | Min. | Max.  | Min. | Max.  | Min.      | Max.  | Units |

| LVTTL Outp          | out Drive Strength = 4 (24 mA) / Low Slew Rate                            |      |       |      |       |           |       |       |

| t <sub>DP</sub>     | Input Buffer                                                              |      | 1.68  |      | 1.92  |           | 2.26  | ns    |

| t <sub>PY</sub>     | Output Buffer                                                             |      | 10.45 |      | 11.90 |           | 13.99 | ns    |

| t <sub>ENZL</sub>   | Enable to Pad Delay through the Output Buffer—Z to Low                    |      | 10.61 |      | 12.08 |           | 14.21 | ns    |

| t <sub>ENZH</sub>   | Enable to Pad Delay through the Output Buffer—Z to High                   |      | 10.47 |      | 11.93 |           | 14.02 | ns    |

| t <sub>ENLZ</sub>   | Enable to Pad Delay through the Output Buffer—Low to Z                    |      | 1.92  |      | 1.94  |           | 1.94  | ns    |

| t <sub>ENHZ</sub>   | Enable to Pad Delay through the Output Buffer—High to Z                   |      | 2.57  |      | 2.58  |           | 2.59  | ns    |

| t <sub>IOCLKQ</sub> | Sequential Clock-to-Q for the I/O Input Register                          |      | 0.67  |      | 0.77  |           | 0.90  | ns    |

| t <sub>IOCLKY</sub> | Clock-to-output Y for the I/O Output Register and the I/O Enable Register |      | 0.67  |      | 0.77  |           | 0.90  | ns    |

| t <sub>SUD</sub>    | Data Input Set-Up                                                         |      | 0.23  |      | 0.27  |           | 0.31  | ns    |

| t <sub>SUE</sub>    | Enable Input Set-Up                                                       |      | 0.26  |      | 0.30  |           | 0.35  | ns    |

| t <sub>HD</sub>     | Data Input Hold                                                           |      | 0.00  |      | 0.00  |           | 0.00  | ns    |

| t <sub>HE</sub>     | Enable Input Hold                                                         |      | 0.00  |      | 0.00  |           | 0.00  | ns    |

| t <sub>CPWHL</sub>  | Clock Pulse Width High to Low                                             | 0.39 |       | 0.39 |       | 0.39      |       | ns    |

| t <sub>CPWLH</sub>  | Clock Pulse Width Low to High                                             | 0.39 |       | 0.39 |       | 0.39      |       | ns    |

| t <sub>WASYN</sub>  | Asynchronous Pulse Width                                                  | 0.37 |       | 0.37 |       | 0.37      |       | ns    |

| t <sub>REASYN</sub> | Asynchronous Recovery Time                                                |      | 0.13  |      | 0.15  |           | 0.17  | ns    |

| t <sub>HASYN</sub>  | Asynchronous Removal Time                                                 |      | 0.00  |      | 0.00  |           | 0.00  | ns    |

| t <sub>CLR</sub>    | Asynchronous Clear-to-Q                                                   |      | 0.23  |      | 0.27  |           | 0.31  | ns    |

| t <sub>PRESET</sub> | Asynchronous Preset-to-Q                                                  |      | 0.23  |      | 0.27  |           | 0.31  | ns    |

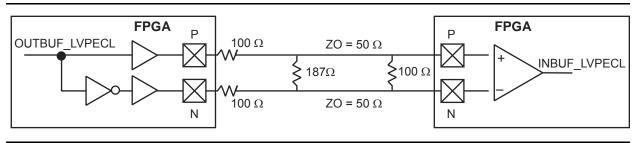

# LVPECL

Low-Voltage Positive Emitter-Coupled Logic (LVPECL) is another differential I/O standard. It requires that one data bit is carried through two signal lines. Like LVDS, two pins are needed. It also requires external resistor termination. The voltage swing between these two signal lines is approximately 850 mV.

#### Figure 2-26 • LVPECL Board-Level Implementation

The LVPECL circuit is similar to the LVDS scheme. It requires four external resistors, three for the driver and one for the receiver. The values for the three driver resistors are different from that of LVDS since the output voltage levels are different. Please note that the VOH levels are 200 mV below the standard LVPECL levels.

|                               | Min. |       | Ту   | Тур.  |      | Max.  |       |  |

|-------------------------------|------|-------|------|-------|------|-------|-------|--|

| DC Parameter                  | Min. | Max.  | Min. | Max.  | Min. | Max.  | Units |  |

| VCCI                          |      | 3     | 3    | .3    | 3    | .6    | V     |  |

| VOH                           | 1.8  | 2.11  | 1.92 | 2.28  | 2.13 | 2.41  | V     |  |

| VOL                           | 0.96 | 1.27  | 1.06 | 1.43  | 1.3  | 1.57  | V     |  |

| VIH                           | 1.49 | 2.72  | 1.49 | 2.72  | 1.49 | 2.72  | V     |  |

| VIL                           | 0.86 | 2.125 | 0.86 | 2.125 | 0.86 | 2.125 | V     |  |

| Differential Input<br>Voltage | 0.3  |       | 0.3  |       | 0.3  |       | V     |  |

#### Table 2-59 • DC Input and Output Levels

Table 2-60 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) |

|---------------|----------------|----------------------|

| 1.6 – 0.3     | 1.6 + 0.3      | 1.6                  |

Note: \* Measuring Point = VTRIP

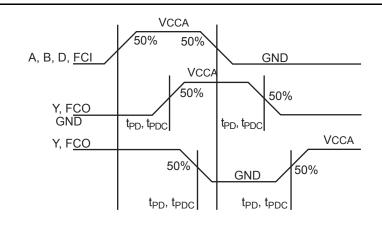

# Timing Model and Waveforms

# **Timing Characteristics**

### Table 2-62 • C-Cell

Worst-Case Commercial Conditions VCCA = 1.425 V, VCCI = 3.0 V, T<sub>J</sub> =  $70^{\circ}$ C

|                           |                                                        | -2 Speed |      | -1 Speed |      | Std Speed |      |       |

|---------------------------|--------------------------------------------------------|----------|------|----------|------|-----------|------|-------|

| Parameter                 | Description                                            | Min.     | Max. | Min.     | Max. | Min.      | Max. | Units |

| C-Cell Propagation Delays |                                                        |          |      |          |      |           |      |       |

| t <sub>PD</sub>           | Any input to output Y                                  |          | 0.74 |          | 0.84 |           | 0.99 | ns    |

| t <sub>PDC</sub>          | Any input to carry chain output (FCO)                  |          | 0.57 |          | 0.64 |           | 0.76 | ns    |

| t <sub>PDB</sub>          | Any input through DB when one input is used            |          | 0.95 |          | 1.09 |           | 1.28 | ns    |

| t <sub>CCY</sub>          | Input to carry chain (FCI) to Y                        |          | 0.61 |          | 0.69 |           | 0.82 | ns    |

| tcc                       | Input to carry chain (FCI) to carry chain output (FCO) |          | 0.08 |          | 0.09 |           | 0.11 | ns    |

# **Routed Clocks**

The routed clock (CLK) is a low-skew network that can drive the clock inputs of all sequential modules in the device (logically equivalent to the HCLK), but has the added flexibility in that it can drive the S0 (Enable), S1, PSET, and CLR input of a register (R-cells and I/O registers) as well as any of the inputs of any C-cell in the device. This allows CLKs to be used not only as clocks, but also for other global signals or high fanout nets. All four CLKs are available everywhere on the chip.

### Timing Characteristics

#### Table 2-75 • AX125 Routed Array Clock Networks Worst-Case Commercial Conditions VCCA = 1.425 V, VCCI = 3.0 V, T<sub>J</sub> = 70°C

|                             |                          | -2 Speed |      | -1 Speed |      | Std Speed |      |       |  |

|-----------------------------|--------------------------|----------|------|----------|------|-----------|------|-------|--|

| Parameter                   | Description              | Min.     | Max. | Min.     | Max. | Min.      | Max. | Units |  |

| Routed Array Clock Networks |                          |          |      |          |      |           |      |       |  |

| t <sub>RCKL</sub>           | Input Low to High        |          | 3.08 |          | 3.50 |           | 4.12 | ns    |  |

| t <sub>RCKH</sub>           | Input High to Low        |          | 3.13 |          | 3.56 |           | 4.19 | ns    |  |

| t <sub>RPWH</sub>           | Minimum Pulse Width High | 0.57     |      | 0.64     |      | 0.75      |      | ns    |  |

| t <sub>RPWL</sub>           | Minimum Pulse Width Low  | 0.52     |      | 0.59     |      | 0.69      |      | ns    |  |

| t <sub>RCKSW</sub>          | Maximum Skew             |          | 0.35 |          | 0.39 |           | 0.46 | ns    |  |

| t <sub>RP</sub>             | Minimum Period           | 1.15     |      | 1.31     |      | 1.54      |      | ns    |  |

| t <sub>RMAX</sub>           | Maximum Frequency        |          | 870  |          | 763  |           | 649  | MHz   |  |

### Table 2-76 • AX250 Routed Array Clock Networks

#### Worst-Case Commercial Conditions VCCA = 1.425 V, VCCI = 3.0 V, T<sub>J</sub> = $70^{\circ}$ C

|                             |                          | -2 Speed |      | -1 Speed |      | Std Speed |      |       |

|-----------------------------|--------------------------|----------|------|----------|------|-----------|------|-------|

| Parameter                   | Description              | Min.     | Max. | Min.     | Max. | Min.      | Max. | Units |

| Routed Array Clock Networks |                          |          |      |          |      |           |      |       |

| t <sub>RCKL</sub>           | Input Low to High        |          | 2.52 |          | 2.87 |           | 3.37 | ns    |

| t <sub>RCKH</sub>           | Input High to Low        |          | 2.59 |          | 2.95 |           | 3.47 | ns    |

| t <sub>RPWH</sub>           | Minimum Pulse Width High | 0.57     |      | 0.64     |      | 0.75      |      | ns    |

| t <sub>RPWL</sub>           | Minimum Pulse Width Low  | 0.52     |      | 0.59     |      | 0.69      |      | ns    |

| t <sub>RCKSW</sub>          | Maximum Skew             |          | 0.35 |          | 0.39 |           | 0.46 | ns    |

| t <sub>RP</sub>             | Minimum Period           | 1.15     |      | 1.31     |      | 1.54      |      | ns    |

| t <sub>RMAX</sub>           | Maximum Frequency        |          | 870  |          | 763  |           | 649  | MHz   |

throughout the fabric of the device and may be programmed by the user to thwart attempts to reverse engineer the device by attempting to exploit either the programming or probing interfaces. Both invasive and noninvasive attacks against an Axcelerator device that access or bypass these security fuses will destroy access to the rest of the device. (refer to the *Design Security in Nonvolatile Flash and Antifuse FPGAs* white paper).

Look for this symbol to ensure your valuable IP is protected with highest level of security in the industry.

#### Figure 2-69 • FuseLock Logo

To ensure maximum security in Axcelerator devices, it is recommended that the user program the device security fuse (SFUS). When programmed, the Silicon Explorer II testing probes are disabled to prevent internal probing, and the programming interface is also disabled. All JTAG public instructions are still accessible by the user.

For more information, refer to the Implementation of Security in Actel Antifuse FPGAs application note.

### **Global Set Fuse**

The Global Set Fuse determines if all R-cells and I/O registers (InReg, OutReg, and EnReg) are either cleared or preset by driving the GCLR and GPSET inputs of all R-cells and I/O Registers (Figure 2-31 on page 2-58). Default setting is to clear all registers (GCLR = 0 and GPSET =1) at device power-up. When the GBSETFUS option is checked during FUSE file generation, all registers are preset (GCLR = 1 and GPSET = 0). A local CLR or PRESET will take precedence over this setting. Both pins are pulled High during normal device operation. For use details, see the Libero IDE online help.

# Silicon Explorer II Probe Interface

Silicon Explorer II is an integrated hardware and software solution that, in conjunction with the Designer tools, allows users to examine any of the internal nets (except I/O registers) of the device while it is operating in a prototype or a production system. The user can probe up to four nodes at a time without changing the placement and routing of the design and without using any additional device resources. Highlighted nets in Designer's ChipPlanner can be accessed using Silicon Explorer II in order to observe their real time values.

Silicon Explorer II's noninvasive method does not alter timing or loading effects, thus shortening the debug cycle. In addition, Silicon Explorer II does not require relayout or additional MUXes to bring signals out to external pins, which is necessary when using programmable logic devices from other suppliers. By eliminating multiple place-and-route program cycles, the integrity of the design is maintained throughout the debug process.

Each member of the Axcelerator family has four external pads: PRA, PRB, PRC, and PRD. These can be used to bring out four probe signals from the Axcelerator device (note that the AX125 only has two probe signals that can be observed: PRA and PRB). Each core tile has up to two probe signals. To disallow probing, the SFUS security fuse in the silicon signature has to be programmed (see "Special Fuses" on page 2-108).

Silicon Explorer II connects to the host PC using a standard serial port connector. Connections to the circuit board are achieved using a nine-pin D-Sub connector (Figure 1-9 on page 1-7). Once the design has been placed-and-routed, and the Axcelerator device has been programmed, Silicon Explorer II can be connected and the Explorer software can be launched.

Silicon Explorer II comes with an additional optional PC hosted tool that emulates an 18-channel logic analyzer. Four channels are used to monitor four internal nodes, and 14 channels are available to probe external signals. The software included with the tool provides the user with an intuitive interface that allows for easy viewing and editing of signal waveforms.

| FG324          |               |  |  |  |  |  |

|----------------|---------------|--|--|--|--|--|

| AX125 Function | Pin<br>Number |  |  |  |  |  |

| VCCIB5         | N7            |  |  |  |  |  |

| VCCIB5         | N8            |  |  |  |  |  |

| VCCIB5         | N9            |  |  |  |  |  |

| VCCIB6         | K6            |  |  |  |  |  |

| VCCIB6         | L6            |  |  |  |  |  |

| VCCIB6         | M6            |  |  |  |  |  |

| VCCIB7         | G6            |  |  |  |  |  |

| VCCIB7         | H6            |  |  |  |  |  |

| VCCIB7         | J6            |  |  |  |  |  |

| VCOMPLA        | B8            |  |  |  |  |  |

| VCOMPLB        | E8            |  |  |  |  |  |

| VCOMPLC        | C10           |  |  |  |  |  |

| VCOMPLD        | E12           |  |  |  |  |  |

| VCOMPLE        | U11           |  |  |  |  |  |

| VCOMPLF        | P11           |  |  |  |  |  |

| VCOMPLG        | Т9            |  |  |  |  |  |

| VCOMPLH        | P7            |  |  |  |  |  |

| VPUMP          | B15           |  |  |  |  |  |

| FG676           |            |  |  |  |  |  |  |

|-----------------|------------|--|--|--|--|--|--|

| AX1000 Function | Pin Number |  |  |  |  |  |  |

| VCCIB4          | W18        |  |  |  |  |  |  |

| VCCIB4          | Y17        |  |  |  |  |  |  |

| VCCIB4          | Y18        |  |  |  |  |  |  |

| VCCIB4          | Y19        |  |  |  |  |  |  |

| VCCIB5          | W10        |  |  |  |  |  |  |

| VCCIB5          | W11        |  |  |  |  |  |  |

| VCCIB5          | W12        |  |  |  |  |  |  |

| VCCIB5          | W13        |  |  |  |  |  |  |

| VCCIB5          | W9         |  |  |  |  |  |  |

| VCCIB5          | Y10        |  |  |  |  |  |  |

| VCCIB5          | Y8         |  |  |  |  |  |  |

| VCCIB5          | Y9         |  |  |  |  |  |  |

| VCCIB6          | P8         |  |  |  |  |  |  |

| VCCIB6          | R8         |  |  |  |  |  |  |

| VCCIB6          | Т8         |  |  |  |  |  |  |

| VCCIB6          | U7         |  |  |  |  |  |  |

| VCCIB6          | U8         |  |  |  |  |  |  |

| VCCIB6          | V7         |  |  |  |  |  |  |

| VCCIB6          | V8         |  |  |  |  |  |  |

| VCCIB6          | W7         |  |  |  |  |  |  |

| VCCIB7          | H7         |  |  |  |  |  |  |

| VCCIB7          | J7         |  |  |  |  |  |  |

| VCCIB7          | J8         |  |  |  |  |  |  |

| VCCIB7          | K7         |  |  |  |  |  |  |

| VCCIB7          | K8         |  |  |  |  |  |  |

| VCCIB7          | L8         |  |  |  |  |  |  |

| VCCIB7          | M8         |  |  |  |  |  |  |

| VCCIB7          | N8         |  |  |  |  |  |  |

| VCOMPLA         | D12        |  |  |  |  |  |  |

| VCOMPLB         | G13        |  |  |  |  |  |  |

| VCOMPLC         | D15        |  |  |  |  |  |  |

| VCOMPLD         | F14        |  |  |  |  |  |  |

| VCOMPLE         | AD15       |  |  |  |  |  |  |

| VCOMPLF         | AB14       |  |  |  |  |  |  |

| VCOMPLG         | AD12       |  |  |  |  |  |  |

| FG676           |            |  |  |  |  |

|-----------------|------------|--|--|--|--|

| AX1000 Function | Pin Number |  |  |  |  |

| VCOMPLH         | Y13        |  |  |  |  |

| VPUMP           | E22        |  |  |  |  |

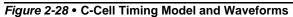

# FG896

## Note

For Package Manufacturing and Environmental information, visit Resource center at http://www.microsemi.com/soc/products/rescenter/package/index.html.

| FG896           |               | FG896           | FG896 FG896   |                 |               |  |

|-----------------|---------------|-----------------|---------------|-----------------|---------------|--|

| AX1000 Function | Pin<br>Number | AX1000 Function | Pin<br>Number | AX1000 Function | Pin<br>Number |  |

| IO51PB1F4       | E21           | IO68PB2F6       | K24           | IO86NB2F8       | N28           |  |

| IO52NB1F4       | F22           | IO69NB2F6       | F27           | IO86PB2F8       | N27           |  |

| IO52PB1F4       | E22           | IO69PB2F6       | E27           | IO87NB2F8       | P29           |  |

| IO53NB1F4       | B25           | IO70NB2F6       | J26           | IO87PB2F8       | P30           |  |

| IO53PB1F4       | B24           | IO70PB2F6       | J25           | IO88NB2F8       | P25           |  |

| IO54NB1F5       | D24           | IO71NB2F6       | H27           | IO88PB2F8       | P24           |  |

| IO54PB1F5       | D23           | IO71PB2F6       | G27           | IO89NB2F8       | P28           |  |

| IO55NB1F5       | F23           | IO72NB2F6       | J28           | IO89PB2F8       | P27           |  |

| IO55PB1F5       | E23           | IO72PB2F6       | H28           | IO90NB2F8       | P22           |  |

| IO56NB1F5       | H21           | IO73NB2F6       | G28           | IO90PB2F8       | P23           |  |

| IO56PB1F5       | G21           | IO73PB2F6       | F28           | IO91NB2F8       | R26           |  |

| IO57NB1F5       | D25           | IO74NB2F7       | L23           | IO91PB2F8       | P26           |  |

| IO57PB1F5       | C25           | IO74PB2F7       | L24           | IO92NB2F8       | R24           |  |

| IO58NB1F5       | F24           | IO75NB2F7       | L26           | IO92PB2F8       | R25           |  |

| IO58PB1F5       | E24           | IO75PB2F7       | K26           | IO93NB2F8       | R29           |  |

| IO59NB1F5       | D26           | IO76NB2F7       | M25           | IO93PB2F8       | R30           |  |

| IO59PB1F5       | C26           | IO76PB2F7       | L25           | IO94NB2F8       | R22           |  |

| IO60NB1F5       | G23           | IO77NB2F7       | K27           | IO94PB2F8       | R23           |  |

| IO60PB1F5       | G22           | IO77PB2F7       | J27           | IO95NB2F8       | T27           |  |

| IO61NB1F5       | B27           | IO78NB2F7       | M27           | IO95PB2F8       | R27           |  |

| IO61PB1F5       | A27           | IO78PB2F7       | L27           | Bank 3          |               |  |

| IO62NB1F5       | F25           | IO79NB2F7       | K30           | IO96NB3F9       | T29           |  |

| IO62PB1F5       | E25           | IO79PB2F7       | K29           | IO96PB3F9       | T30           |  |

| IO63NB1F5       | H23           | IO80NB2F7       | M23           | IO97NB3F9       | U29           |  |

| IO63PB1F5       | H22           | IO80PB2F7       | M24           | IO97PB3F9       | U30           |  |

| Bank 2          |               | IO81NB2F7       | M28           | IO98NB3F9       | T22           |  |

| IO64NB2F6       | K23           | IO81PB2F7       | L28           | IO98PB3F9       | T23           |  |

| IO64PB2F6       | J23           | IO82NB2F7       | N26           | IO99NB3F9       | U26           |  |

| IO65NB2F6       | J24           | IO82PB2F7       | M26           | IO99PB3F9       | T26           |  |

| IO65PB2F6       | H24           | IO83NB2F7       | N25           | IO100NB3F9      | U24           |  |

| IO66NB2F6       | H26           | IO83PB2F7       | N24           | IO100PB3F9      | T24           |  |

| IO66PB2F6       | H25           | IO84NB2F7       | N22           | IO101NB3F9      | V28           |  |

| IO67NB2F6       | G26           | IO84PB2F7       | N23           | IO101PB3F9      | U28           |  |

| IO67PB2F6       | G25           | IO85NB2F8       | M29           | IO102NB3F9      | U23           |  |

| IO68NB2F6       | K25           | IO85PB2F8       | L29           | IO102PB3F9      | U22           |  |

| FG896                  |     | FG896            | FG896         |                  | FG896         |  |

|------------------------|-----|------------------|---------------|------------------|---------------|--|

| AX2000 Function Number |     | AX2000 Function  | Pin<br>Number | AX2000 Function  | Pin<br>Number |  |

| Bank 0                 | •   | IO19NB0F1        | D11           | Bank 1           |               |  |

| IO00NB0F0              | B4  | IO19PB0F1        | E11           | IO43NB1F4/HCLKCN | E17           |  |

| IO00PB0F0              | A4  | IO20PB0F1        | B8            | IO43PB1F4/HCLKCP | E16           |  |

| IO01NB0F0              | F8  | IO21NB0F1        | H12           | IO44NB1F4/HCLKDN | C17           |  |

| IO01PB0F0              | F7  | IO21PB0F1        | H11           | IO44PB1F4/HCLKDP | D17           |  |

| IO02NB0F0              | D6  | IO23NB0F2        | A10           | IO45NB1F4        | A16           |  |

| IO02PB0F0              | E6  | IO23PB0F2        | A9            | IO45PB1F4        | B16           |  |

| IO04NB0F0              | A5  | IO25NB0F2        | F12           | IO47NB1F4        | H17           |  |

| IO04PB0F0              | B5  | IO25PB0F2        | G12           | IO47PB1F4        | J17           |  |

| IO05NB0F0              | H8  | IO26NB0F2        | B11           | IO48NB1F4        | A17           |  |

| IO05PB0F0              | G8  | IO26PB0F2        | B10           | IO48PB1F4        | B17           |  |

| IO06NB0F0              | D7  | IO27NB0F2        | D12           | IO49NB1F4        | H18           |  |

| IO06PB0F0              | E7  | IO27PB0F2        | E12           | IO49PB1F4        | J18           |  |

| IO07NB0F0              | D8  | IO28NB0F2        | C12           | IO51NB1F4        | F18           |  |

| IO07PB0F0              | E8  | IO28PB0F2        | C11           | IO51PB1F4        | G18           |  |

| IO08NB0F0              | C7  | IO30NB0F2        | A12           | IO52NB1F4        | B18           |  |

| IO08PB0F0              | C6  | IO30PB0F2        | A11           | IO53NB1F4        | D18           |  |

| IO09NB0F0              | G9  | IO31NB0F2        | F13           | IO53PB1F4        | C18           |  |

| IO09PB0F0              | H9  | IO31PB0F2        | G13           | IO55NB1F5        | H19           |  |

| IO10NB0F0              | A6  | IO33NB0F2        | H13           | IO55PB1F5        | G19           |  |

| IO10PB0F0              | B6  | IO33PB0F2        | J13           | IO56NB1F5        | B19           |  |

| IO11NB0F0              | H10 | IO34NB0F3        | B13           | IO56PB1F5        | A19           |  |

| IO11PB0F0              | G10 | IO34PB0F3        | B12           | IO57NB1F5        | E20           |  |

| IO12NB0F1              | E9  | IO37NB0F3        | E14           | IO57PB1F5        | E19           |  |

| IO12PB0F1              | F9  | IO37PB0F3        | E13           | IO58NB1F5        | C20           |  |

| IO13NB0F1              | E10 | IO38NB0F3        | B14           | IO58PB1F5        | C19           |  |

| IO13PB0F1              | F10 | IO38PB0F3        | A14           | IO59NB1F5        | B20           |  |

| IO15NB0F1              | F11 | IO39NB0F3        | H14           | IO59PB1F5        | A20           |  |

| IO15PB0F1              | G11 | IO39PB0F3        | J14           | IO61NB1F5        | F20           |  |

| IO16NB0F1              | A7  | IO40NB0F3        | B15           | IO61PB1F5        | F19           |  |

| IO16PB0F1              | B7  | IO40PB0F3        | A15           | IO62NB1F5        | A22           |  |

| IO17NB0F1              | D10 | IO41NB0F3/HCLKAN | C14           | IO62PB1F5        | A21           |  |

| IO17PB0F1              | D9  | IO41PB0F3/HCLKAP | D14           | IO63NB1F5        | D21           |  |

| IO18NB0F1              | C9  | IO42NB0F3/HCLKBN | E15           | IO63PB1F5        | D20           |  |

| IO18PB0F1              | C8  | IO42PB0F3/HCLKBP | D15           | IO65NB1F6        | G20           |  |

| FG896           |               | FG896           |               |  |

|-----------------|---------------|-----------------|---------------|--|

| AX2000 Function | Pin<br>Number | AX2000 Function | Pin<br>Number |  |

| VCCIB3          | AH30          | VCCIB6          | W9            |  |

| VCCIB3          | T21           | VCCIB6          | Y10           |  |

| VCCIB3          | U21           | VCCIB6          | Y9            |  |

| VCCIB3          | V21           | VCCIB7          | C1            |  |

| VCCIB3          | W21           | VCCIB7          | C2            |  |

| VCCIB3          | W22           | VCCIB7          | K9            |  |

| VCCIB3          | Y21           | VCCIB7          | L10           |  |

| VCCIB3          | Y22           | VCCIB7          | L9            |  |

| VCCIB4          | AA16          | VCCIB7          | M10           |  |

| VCCIB4          | AA17          | VCCIB7          | M9            |  |

| VCCIB4          | AA18          | VCCIB7          | N10           |  |

| VCCIB4          | AA19          | VCCIB7          | P10           |  |

| VCCIB4          | AA20          | VCCIB7          | R10           |  |

| VCCIB4          | AB19          | VCCPLA          | G14           |  |

| VCCIB4          | AB20          | VCCPLB          | H15           |  |

| VCCIB4          | AB21          | VCCPLC          | G17           |  |

| VCCIB4          | AJ28          | VCCPLD          | J16           |  |

| VCCIB4          | AK28          | VCCPLE          | AH17          |  |

| VCCIB5          | AA11          | VCCPLF          | AC16          |  |

| VCCIB5          | AA12          | VCCPLG          | AH14          |  |

| VCCIB5          | AA13          | VCCPLH          | AD15          |  |

| VCCIB5          | AA14          | VCOMPLA         | F14           |  |

| VCCIB5          | AA15          | VCOMPLB         | J15           |  |

| VCCIB5          | AB10          | VCOMPLC         | F17           |  |

| VCCIB5          | AB11          | VCOMPLD         | H16           |  |

| VCCIB5          | AB12          | VCOMPLE         | AF17          |  |

| VCCIB5          | AJ3           | VCOMPLF         | AD16          |  |

| VCCIB5          | AK3           | VCOMPLG         | AF14          |  |

| VCCIB6          | AA9           | VCOMPLH         | AB15          |  |

| VCCIB6          | AH1           | VPUMP           | G24           |  |

| VCCIB6          | AH2           |                 |               |  |

| VCCIB6          | T10           |                 |               |  |

| VCCIB6          | U10           |                 |               |  |

| VCCIB6          | V10           |                 |               |  |

| VCCIB6          | W10           |                 |               |  |

| FG1152          |               | FG1152          |               | FG1152          |               |

|-----------------|---------------|-----------------|---------------|-----------------|---------------|

| AX2000 Function | Pin<br>Number | AX2000 Function | Pin<br>Number | AX2000 Function | Pin<br>Number |

| GND             | AK12          | GND             | AN34          | GND             | D1            |

| GND             | AK17          | GND             | AN4           | GND             | D11           |

| GND             | AK18          | GND             | AN9           | GND             | D2            |

| GND             | AK23          | GND             | AP13          | GND             | D24           |

| GND             | AK30          | GND             | AP2           | GND             | D3            |

| GND             | AK5           | GND             | AP22          | GND             | D31           |

| GND             | AL1           | GND             | AP27          | GND             | D32           |

| GND             | AL11          | GND             | AP3           | GND             | D33           |

| GND             | AL2           | GND             | AP31          | GND             | D34           |

| GND             | AL24          | GND             | AP32          | GND             | D4            |

| GND             | AL3           | GND             | AP33          | GND             | E12           |

| GND             | AL31          | GND             | AP4           | GND             | E17           |

| GND             | AL32          | GND             | AP8           | GND             | E18           |

| GND             | AL33          | GND             | B1            | GND             | E23           |

| GND             | AL34          | GND             | B2            | GND             | E30           |

| GND             | AL4           | GND             | B26           | GND             | E5            |

| GND             | AM1           | GND             | B3            | GND             | F29           |

| GND             | AM10          | GND             | B31           | GND             | F30           |

| GND             | AM15          | GND             | B32           | GND             | F6            |

| GND             | AM2           | GND             | B33           | GND             | G28           |

| GND             | AM20          | GND             | B34           | GND             | G7            |

| GND             | AM25          | GND             | B4            | GND             | H1            |

| GND             | AM3           | GND             | B9            | GND             | H34           |

| GND             | AM31          | GND             | C1            | GND             | J2            |

| GND             | AM32          | GND             | C10           | GND             | J33           |

| GND             | AM33          | GND             | C15           | GND             | K3            |

| GND             | AM34          | GND             | C2            | GND             | K32           |

| GND             | AM4           | GND             | C20           | GND             | L11           |

| GND             | AN1           | GND             | C25           | GND             | L24           |

| GND             | AN2           | GND             | C3            | GND             | L31           |

| GND             | AN26          | GND             | C31           | GND             | L4            |

| GND             | AN3           | GND             | C32           | GND             | M12           |

| GND             | AN31          | GND             | C33           | GND             | M23           |

| GND             | AN32          | GND             | C34           | GND             | M30           |

| GND             | AN33          | GND             | C4            | GND             | M5            |

| CQ352           |               | CQ352          | 2 CQ352       |                |               |  |

|-----------------|---------------|----------------|---------------|----------------|---------------|--|

| AX250 Function  | Pin<br>Number | AX250 Function | Pin<br>Number | AX250 Function | Pin<br>Number |  |

| IO64PB4F4       | 167           | IO85PB5F5      | 105           | IO106NB6F6     | 46            |  |

| IO65NB4F4       | 170           | IO86NB5F5      | 98            | IO106PB6F6     | 47            |  |

| IO65PB4F4       | 171           | IO86PB5F5      | 99            | Bank 7         |               |  |

| IO66NB4F4       | 164           | IO87NB5F5      | 94            | IO107NB7F7     | 40            |  |

| IO66PB4F4       | 165           | IO87PB5F5      | 95            | IO107PB7F7     | 41            |  |

| IO67NB4F4       | 160           | IO89NB5F5      | 92            | IO108NB7F7     | 42            |  |

| IO67PB4F4       | 161           | IO89PB5F5      | 93            | IO108PB7F7     | 43            |  |

| IO68NB4F4       | 158           | Bank 6         |               | IO109NB7F7     | 36            |  |

| IO68PB4F4       | 159           | IO90PB6F6      | 86            | IO109PB7F7     | 37            |  |

| IO70NB4F4       | 154           | IO91NB6F6      | 84            | IO110NB7F7     | 34            |  |

| IO70PB4F4       | 155           | IO91PB6F6      | 85            | IO110PB7F7     | 35            |  |

| IO72NB4F4       | 152           | IO92NB6F6      | 78            | IO111NB7F7     | 30            |  |

| IO72PB4F4       | 153           | IO92PB6F6      | 79            | IO111PB7F7     | 31            |  |

| IO73NB4F4       | 146           | IO93NB6F6      | 82            | IO113NB7F7     | 28            |  |

| IO73PB4F4       | 147           | IO93PB6F6      | 83            | IO113PB7F7     | 29            |  |

| IO74NB4F4/CLKEN | 142           | IO95NB6F6      | 76            | IO114NB7F7     | 24            |  |

| IO74PB4F4/CLKEP | 143           | IO95PB6F6      | 77            | IO114PB7F7     | 25            |  |

| IO75NB4F4/CLKFN | 136           | IO96NB6F6      | 72            | IO115NB7F7     | 22            |  |

| IO75PB4F4/CLKFP | 137           | IO96PB6F6      | 73            | IO115PB7F7     | 23            |  |

| Bank 5          |               | IO97NB6F6      | 70            | IO116NB7F7     | 18            |  |

| IO76NB5F5/CLKGN | 128           | IO97PB6F6      | 71            | IO116PB7F7     | 19            |  |

| IO76PB5F5/CLKGP | 129           | IO98NB6F6      | 66            | IO117NB7F7     | 16            |  |

| IO77NB5F5/CLKHN | 122           | IO98PB6F6      | 67            | IO117PB7F7     | 17            |  |

| IO77PB5F5/CLKHP | 123           | IO99NB6F6      | 64            | IO118NB7F7     | 12            |  |

| IO78NB5F5       | 112           | IO99PB6F6      | 65            | IO118PB7F7     | 13            |  |

| IO78PB5F5       | 113           | IO100NB6F6     | 60            | IO119NB7F7     | 10            |  |

| IO79NB5F5       | 118           | IO100PB6F6     | 61            | IO119PB7F7     | 11            |  |

| IO79PB5F5       | 119           | IO101NB6F6     | 58            | IO121NB7F7     | 6             |  |

| IO80NB5F5       | 110           | IO101PB6F6     | 59            | IO121PB7F7     | 7             |  |

| IO80PB5F5       | 111           | IO103NB6F6     | 54            | IO123NB7F7     | 4             |  |

| IO82NB5F5       | 106           | IO103PB6F6     | 55            | IO123PB7F7     | 5             |  |

| IO82PB5F5       | 107           | IO104NB6F6     | 52            | Dedicated I/C  | )             |  |

| IO84NB5F5       | 100           | IO104PB6F6     | 53            | GND            | 1             |  |

| IO84PB5F5       | 101           | IO105NB6F6     | 48            | GND            | 9             |  |

| IO85NB5F5       | 104           | IO105PB6F6     | 49            | GND            | 15            |  |

| CG624           |               | CG624            | CG624         |                 |               |  |

|-----------------|---------------|------------------|---------------|-----------------|---------------|--|

| AX2000 Function | Pin<br>Number | AX2000 Function  | Pin<br>Number | AX2000 Function | Pin<br>Number |  |

| Bank 0          |               | IO27NB0F2        | H10           | IO51NB1F4       | E15           |  |

| IO00NB0F0       | D7*           | IO27PB0F2        | H9            | IO51PB1F4       | F15           |  |

| IO00PB0F0       | E7*           | IO28NB0F2        | A9            | IO52NB1F4       | A17           |  |

| IO01NB0F0       | G7            | IO28PB0F2        | B9            | IO55NB1F5       | G16           |  |

| IO01PB0F0       | G6            | IO30NB0F2        | B11           | IO55PB1F5       | H16           |  |

| IO02NB0F0       | B5            | IO30PB0F2        | B10           | IO56NB1F5       | A20           |  |

| IO02PB0F0       | B4            | IO31NB0F2        | E11           | IO56PB1F5       | A19           |  |

| IO04PB0F0       | C7            | IO31PB0F2        | F11           | IO57NB1F5       | D16           |  |

| IO05NB0F0       | F8            | IO33NB0F2        | D12           | IO57PB1F5       | D15           |  |

| IO05PB0F0       | F7            | IO33PB0F2        | D11           | IO58NB1F5       | A22           |  |

| IO06NB0F0       | H8            | IO34NB0F3        | A11           | IO58PB1F5       | A21           |  |

| IO06PB0F0       | H7            | IO34PB0F3        | A10           | IO59NB1F5       | F16           |  |

| IO11NB0F0       | J8            | IO37NB0F3        | J13           | IO61NB1F5       | G17           |  |

| IO11PB0F0       | J7            | IO37PB0F3        | K13           | IO61PB1F5       | H17           |  |

| IO12PB0F1       | B6            | IO38NB0F3        | H11           | IO62NB1F5       | B17           |  |

| IO13NB0F1       | E9*           | IO38PB0F3        | G11           | IO62PB1F5       | B16           |  |

| IO13PB0F1       | D8*           | IO40PB0F3        | B12           | IO63NB1F5       | H18           |  |

| IO15NB0F1       | C9            | IO41NB0F3/HCLKAN | G13           | IO65NB1F6       | C17           |  |

| IO15PB0F1       | C8            | IO41PB0F3/HCLKAP | G12           | IO66PB1F6       | B18           |  |

| IO16NB0F1       | A5            | IO42NB0F3/HCLKBN | C13           | IO67NB1F6       | J18           |  |

| IO16PB0F1       | A4            | IO42PB0F3/HCLKBP | C12           | IO67PB1F6       | J19           |  |

| IO17NB0F1       | D10           | Bank 1           |               | IO68NB1F6       | B20           |  |

| IO17PB0F1       | D9            | IO43NB1F4/HCLKCN | G15           | IO68PB1F6       | B19           |  |

| IO18NB0F1       | A7            | IO43PB1F4/HCLKCP | G14           | IO69NB1F6       | E17           |  |

| IO18PB0F1       | A6            | IO44NB1F4/HCLKDN | B14           | IO69PB1F6       | F17           |  |

| IO19NB0F1       | G9            | IO44PB1F4/HCLKDP | B13           | IO70NB1F6       | B22           |  |

| IO19PB0F1       | G8            | IO45NB1F4        | H13           | IO70PB1F6       | B21           |  |

| IO20PB0F1       | B7            | IO47NB1F4        | D14           | IO71PB1F6       | G18           |  |

| IO23NB0F2       | F10           | IO47PB1F4        | C14           | IO73NB1F6       | G19           |  |

| IO23PB0F2       | F9            | IO48NB1F4        | A16           | IO74NB1F6       | C19           |  |

| IO26NB0F2       | C11*          | IO48PB1F4        | A15           | IO74PB1F6       | C18           |  |

| IO26PB0F2       | B8*           | IO49PB1F4        | H15           | IO75NB1F6       | D18           |  |

Note: \*Not routed on the same package layer and to adjacent LGA pads as its differential pair complement. Recommended to be used as a single-ended I/O. Note: \*Not routed on the same package layer and to adjacent LGA pads as its differential pair complement. Recommended to be used as a single-ended I/O.

Note: \*Not routed on the same package layer and to adjacent LGA pads as its differential pair complement. Recommended to be used as a single-ended I/O.

| Revision                     | Changes                                                                                                                                                                                                                                                                                                                           | Page                                     |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| Revision 8<br>(continued)    | The following changes were made in the "FG676"(AX500) section:   AE2, AE25 Change from NC to GND.   AF2, AF25 Changed from GND to NC   AB4, AF24, C1, C26 Changed from V <sub>CCDA</sub> to V <sub>CCA</sub> AD15 Change from V <sub>CCDA</sub> to V <sub>COMPLE</sub> AD17 Changed from V <sub>COMPLE</sub> to V <sub>CCDA</sub> | 3-37                                     |

|                              | In the "FG896" (AX2000) section, the AK28 changed from VCCIB5 to VCCIB4.                                                                                                                                                                                                                                                          | 3-52                                     |

|                              | The "CQ352" and "CG624" sections are new.                                                                                                                                                                                                                                                                                         | 3-98, 3-115                              |

| Revision 7                   | All I/O FIFO capability was removed.                                                                                                                                                                                                                                                                                              | n/a                                      |

| (Advance v1.6)               | Table 1 was updated.                                                                                                                                                                                                                                                                                                              | i                                        |

|                              | Figure 1-9 was updated.                                                                                                                                                                                                                                                                                                           | 1-7                                      |

|                              | Figure 2-5 was updated.                                                                                                                                                                                                                                                                                                           | 2-16                                     |

|                              | The "Using an I/O Register" section was updated.                                                                                                                                                                                                                                                                                  | 2-16                                     |

|                              | The AX250 and AX1000 descriptions were added to the "FG484"section.                                                                                                                                                                                                                                                               | 3-21                                     |

| Revision 6                   | Table 2-3 was updated.                                                                                                                                                                                                                                                                                                            | 2-2                                      |

| (Advance v1.5)               | Figure 2-1 was updated.                                                                                                                                                                                                                                                                                                           | 2-8                                      |

|                              | Figure 2-48 was updated.                                                                                                                                                                                                                                                                                                          | 2-75                                     |

|                              | Figure 2-52 was updated.                                                                                                                                                                                                                                                                                                          | 2-82                                     |

| Revision 5<br>(Advance v1.4) | In the "PQ208" table, pin 196 was missing, but it has been added in this version with a function of GND.                                                                                                                                                                                                                          | 3-84                                     |

|                              | The following pins in the "FG484" table for AX500 were changed:<br>Pin G7 is GND/LP<br>Pins AB8, C10, C11, C14, AB16 are NC.                                                                                                                                                                                                      | 3-21                                     |

|                              | The "FG676" table was updated.                                                                                                                                                                                                                                                                                                    | 3-37                                     |

| Revision 4                   | The "Device Resources" section was updated for the CS180.                                                                                                                                                                                                                                                                         | ii                                       |

| (Advance v1.3)               | The "Programmable Interconnect Element" and Figure 1-2 are new.                                                                                                                                                                                                                                                                   | "<br>1-1 and 1-2                         |

|                              | The "CS180" table is new.                                                                                                                                                                                                                                                                                                         | 3-1                                      |

|                              | The "PQ208" tables for the AX500 were updated. The following pins were not<br>defined in the previous version:<br>GND 21<br>IO106PB5F10/CLKHP 71<br>GND 136                                                                                                                                                                       | 3-84                                     |

| Revision 3<br>(Advance v1.2) | Table 1, "Ordering Information", "Device Resources", and the Product Plan table were updated.                                                                                                                                                                                                                                     | i, ii                                    |

|                              | The following figures and tables were updated:<br>Figure 1-3<br>Figure 1-8 (new)<br>Table 2-3<br>Figure 2-2<br>Table 2-8<br>Figure 2-11                                                                                                                                                                                           | 1-2<br>1-6<br>2-2<br>2-9<br>2-12<br>2-23 |

|                              | The "Design Environment" section was updated.                                                                                                                                                                                                                                                                                     | 1-7                                      |

|                              | The "Package Thermal Characteristics" was updated.                                                                                                                                                                                                                                                                                | 2-6                                      |