# E·XFL

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Obsolete                                                    |

| Number of LABs/CLBs            | 2016                                                        |

| Number of Logic Elements/Cells | -                                                           |

| Total RAM Bits                 | 18432                                                       |

| Number of I/O                  | 168                                                         |

| Number of Gates                | 125000                                                      |

| Voltage - Supply               | 1.425V ~ 1.575V                                             |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | 0°C ~ 70°C (TA)                                             |

| Package / Case                 | 324-BGA                                                     |

| Supplier Device Package        | 324-FBGA (19x19)                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microsemi/ax125-2fg324 |

|                                |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The maximum power dissipation allowed for Military temperature and Mil-Std 883B devices is specified as a function of  $\theta_{\text{ic}}$ .

| Package Type                                  | Pin Count | $\theta_{jc}$ | $\theta_{\textbf{ja}}  \textbf{Still}  \textbf{Air}$ | $\theta_{ja}$ 1.0m/s | $\theta_{ja}$ 2.5m/s | Units |

|-----------------------------------------------|-----------|---------------|------------------------------------------------------|----------------------|----------------------|-------|

| Chip Scale Package (CSP)                      | 180       | N/A           | 57.8                                                 | 51.0                 | 50                   | °C/W  |

| Plastic Quad Flat Pack (PQFP)                 | 208       | 8.0           | 26                                                   | 23.5                 | 20.9                 | °C/W  |

| Plastic Ball Grid Array (PBGA)                | 729       | 2.2           | 13.7                                                 | 10.6                 | 9.6                  | °C/W  |

| Fine Pitch Ball Grid Array (FBGA)             | 256       | 3.0           | 26.6                                                 | 22.8                 | 21.5                 | °C/W  |

| Fine Pitch Ball Grid Array (FBGA)             | 324       | 3.0           | 25.8                                                 | 22.1                 | 20.9                 | °C/W  |

| Fine Pitch Ball Grid Array (FBGA)             | 484       | 3.2           | 20.5                                                 | 17.0                 | 15.9                 | °C/W  |

| Fine Pitch Ball Grid Array (FBGA)             | 676       | 3.2           | 16.4                                                 | 13.0                 | 12.0                 | °C/W  |

| Fine Pitch Ball Grid Array (FBGA)             | 896       | 2.4           | 13.6                                                 | 10.4                 | 9.4                  | °C/W  |

| Fine Pitch Ball Grid Array (FBGA)             | 1152      | 1.8           | 12.0                                                 | 8.9                  | 7.9                  | °C/W  |

| Ceramic Quad Flat Pack (CQFP) <sup>1</sup>    | 208       | 2.0           | 22                                                   | 19.8                 | 18.0                 | °C/W  |

| Ceramic Quad Flat Pack (CQFP) <sup>1</sup>    | 352       | 2.0           | 17.9                                                 | 16.1                 | 14.7                 | °C/W  |

| Ceramic Column Grid Array (CCGA) <sup>2</sup> | 624       | 6.5           | 8.9                                                  | 8.5                  | 8                    | °C/W  |

Table 2-6 • Package Thermal Characteristics

Notes:

1.  $\theta_{jc}$  for the 208-pin and 352-pin CQFP refers to the thermal resistance between the junction and the bottom of the package.

2.  $\theta_{jc}$  for the 624-pin CCGA refers to the thermal resistance between the junction and the top surface of the package. Thermal resistance from junction to board ( $\theta_{ib}$ ) for CCGA 624 package is 3.4°C/W.

# **Timing Characteristics**

Axcelerator devices are manufactured in a CMOS process, therefore, device performance varies according to temperature, voltage, and process variations. Minimum timing parameters reflect maximum operating voltage, minimum operating temperature, and best-case processing. Maximum timing parameters reflect minimum operating voltage, maximum operating temperature, and worst-case processing. The derating factors shown in Table 2-7 should be applied to all timing data contained within this datasheet.

|         | Junction Temperature |       |      |      |      |      |       |  |  |  |

|---------|----------------------|-------|------|------|------|------|-------|--|--|--|

| VCCA    | –55°C                | –40°C | 0°C  | 25°C | 70°C | 85°C | 125°C |  |  |  |

| 1.4 V   | 0.83                 | 0.86  | 0.91 | 0.96 | 1.02 | 1.05 | 1.15  |  |  |  |

| 1.425 V | 0.82                 | 0.84  | 0.90 | 0.94 | 1.00 | 1.04 | 1.13  |  |  |  |

| 1.5 V   | 0.78                 | 0.80  | 0.85 | 0.89 | 0.95 | 0.98 | 1.07  |  |  |  |

| 1.575 V | 0.74                 | 0.76  | 0.81 | 0.85 | 0.90 | 0.94 | 1.02  |  |  |  |

| 1.6 V   | 0.73                 | 0.75  | 0.80 | 0.84 | 0.89 | 0.92 | 1.01  |  |  |  |

Table 2-7 • Temperature and Voltage Timing Derating Factors(Normalized to Worst-Case Commercial, T<sub>J</sub> = 70°C, VCCA = 1.425V)

Notes:

1. The user can set the junction temperature in Designer software to be any integer value in the range of – 55°C to 175°C.

2. The user can set the core voltage in Designer software to be any value between 1.4V and 1.6V.

All timing numbers listed in this datasheet represent sample timing characteristics of Axcelerator devices. Actual timing delay values are design-specific and can be derived from the Timer tool in Microsemi's Designer software after place-and-route.

# **Timing Model**

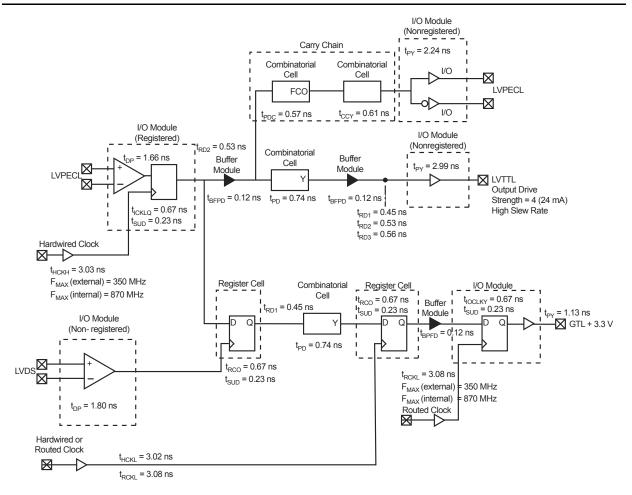

Note: Worst case timing data for the AX1000, -2 speed grade

#### Figure 2-1 • Worst Case Timing Data

### Hardwired Clock – Using LVTTL 24 mA High Slew Clock I/O

External Setup

=  $(t_{DP} + t_{RD2} + t_{SUD}) - t_{HCKL}$ = (1.72 + 0.53 + 0.23) - 3.02 = -0.54 ns Clock-to-Out (Pad-to-Pad)

=  $t_{HCKL} + t_{RCO} + t_{RD1} + t_{PY}$ = 3.02 + 0.67 + 0.45 + 2.99 = 7.13 ns

## Routed Clock – Using LVTTL 24 mA High Slew Clock I/O

External Setup

$= (t_{DP} + t_{RD2} + t_{SUD}) - t_{RCKH}$ = (1.72 + 0.53 + 0.23) - 3.13 = -0.65 ns Clock-to-Out (Pad-to-Pad) = t\_{RCKH} + t\_{RCO} + t\_{RD1} + t\_{PY} = 3.13 + 0.67 + 0.45 + 3.03 = 7.24 ns

#### Table 2-8 • I/O Standards Supported by the Axcelerator Family

| I/O Standard            | Input/Output Supply<br>Voltage (VCCI) | Input Reference<br>Voltage (VREF) | Board Termination<br>Voltage (VTT) |

|-------------------------|---------------------------------------|-----------------------------------|------------------------------------|

| LVTTL                   | 3.3                                   | N/A                               | N/A                                |

| LVCMOS 2.5 V            | 2.5                                   | N/A                               | N/A                                |

| LVCMOS 1.8 V            | 1.8                                   | N/A                               | N/A                                |

| LVCMOS 1.5 V (JDEC8-11) | 1.5                                   | N/A                               | N/A                                |

| 3.3V PCI/PCI-X          | 3.3                                   | N/A                               | N/A                                |

| GTL+ 3.3 V              | 3.3                                   | 1.0                               | 1.2                                |

| GTL+ 2.5 V <sup>*</sup> | 2.5                                   | 1.0                               | 1.2                                |

| HSTL Class 1            | 1.5                                   | 0.75                              | 0.75                               |

| SSTL3 Class 1 and II    | 3.3                                   | 1.5                               | 1.5                                |

| SSTL2 Class1 and II     | 2.5                                   | 1.25                              | 1.25                               |

| LVDS                    | 2.5                                   | N/A                               | N/A                                |

| LVPECL                  | 3.3                                   | N/A                               | N/A                                |

Note: \*2.5 V GTL+ is not supported across the full military temperature range.

#### Table 2-9 • Supply Voltages

| VCCA  | VCCI  | Input Tolerance | Output Drive Level |

|-------|-------|-----------------|--------------------|

| 1.5 V | 1.5 V | 3.3 V           | 1.5 V              |

| 1.5 V | 1.8 V | 3.3 V           | 1.8 V              |

| 1.5 V | 2.5 V | 3.3 V           | 2.5 V              |

| 1.5 V | 3.3 V | 3.3 V           | 3.3 V              |

Table 2-10 • I/O Features Comparison

| I/O Assignment                    | Clamp<br>Diode | Hot<br>Insertion | 5 V<br>Tolerance    | Input<br>Buffer  | Output<br>Buffer      |  |

|-----------------------------------|----------------|------------------|---------------------|------------------|-----------------------|--|

| LVTTL                             | No             | Yes              | Yes <sup>1</sup>    | Enabled/         | Disabled              |  |

| 3.3 V PCI, 3.3 V PCI-X            | Yes            | No               | Yes <sup>1, 2</sup> | Enabled/         | Disabled              |  |

| LVCMOS 2.5 V                      | No             | Yes              | No                  | Enabled/Disabled |                       |  |

| LVCMOS 1.8 V                      | No             | Yes              | No                  | Enabled/         | Disabled              |  |

| LVCMOS 1.5 V (JESD8-11)           | No             | Yes              | No                  | Enabled/         | Disabled              |  |

| Voltage-Referenced Input Buffer   | No             | Yes              | No                  | Enabled/         | Disabled              |  |

| Differential, LVDS/LVPECL, Input  | No             | Yes              | No                  | Enabled          | Disabled <sup>3</sup> |  |

| Differential, LVDS/LVPECL, Output | No             | Yes              | No                  | Disabled         | Enabled <sup>4</sup>  |  |

Notes:

1. Can be implemented with an IDT bus switch.

2. Can be implemented with an external resistor.

3. The OE input of the output buffer must be deasserted permanently (handled by software).

4. The OE input of the output buffer must be asserted permanently (handled by software).

# Using the Weak Pull-Up and Pull-Down Circuits

Each Axcelerator I/O comes with a weak pull-up/down circuit (on the order of 10 k $\Omega$ ). These are weak transistors with the gates tied on, so the on resistance of the transistor emulates a resistor. The weak pull-up and pull-down is active only when the device is powered up, and they must be biased to be on. When the rails are coming up, they are not biased fully, so they do not behave as resistors until the voltage is at sufficient levels to bias the transistors. The key is they really are transistors; they are not traces of poly silicon, which is another way to do an on-chip resistor (those take much more room). I/O macros are provided for combinations of pull up/down for LVTTL, LVCMOS (2.5 V, 1.8 V, and 1.5 V) standards. These macros can be instantiated if a keeper circuit for any input buffer is required.

## Customizing the I/O

- A five-bit programmable input delay element is associated with each I/O. The value of this delay is

set on a bank-wide basis (Table 2-14). It is optional for each input buffer within the bank (i.e. the

user can enable or disable the delay element for the I/O). When the input buffer drives a register

within the I/O, the delay element is activated by default to ensure a zero hold-time. The default

setting for this property can be set in Designer. When the input buffer does not drive a register, the

delay element is deactivated to provide higher performance. Again, this can be overridden by

changing the default setting for this property in Designer.

- The slew-rate value for the LVTTL output buffer can be programmed and can be set to either slow or fast.

- The drive strength value for LVTTL output buffers can be programmed as well. There are four different drive strength values – 8 mA, 12 mA, 16 mA, or 24 mA – that can be specified in Designer.<sup>5</sup>

| Bits Setting | Delay (ns) | Bits Setting | Delay (ns) |

|--------------|------------|--------------|------------|

| 0            | 0.54       | 16           | 2.01       |

| 1            | 0.65       | 17           | 2.13       |

| 2            | 0.71       | 18           | 2.19       |

| 3            | 0.83       | 19           | 2.3        |

| 4            | 0.9        | 20           | 2.38       |

| 5            | 1.01       | 21           | 2.49       |

| 6            | 1.08       | 22           | 2.55       |

| 7            | 1.19       | 23           | 2.67       |

| 8            | 1.27       | 24           | 2.75       |

| 9            | 1.39       | 25           | 2.87       |

| 10           | 1.45       | 26           | 2.93       |

| 11           | 1.56       | 27           | 3.04       |

| 12           | 1.64       | 28           | 3.12       |

| 13           | 1.75       | 29           | 3.23       |

| 14           | 1.81       | 30           | 3.29       |

| 15           | 1.93       | 31           | 3.41       |

Table 2-14 • Bank-Wide Delay Values

Note: Delay values are approximate and will vary with process, temperature, and voltage.

<sup>5.</sup> These values are minimum drive strengths.

# **1.8 V LVCMOS**

Low-Voltage Complementary Metal-Oxide Semiconductor for 1.8 V is an extension of the LVCMOS standard (JESD8-5) used for general-purpose 1.8 V applications. It uses a 3.3 V tolerant CMOS input buffer and a push-pull output buffer.

#### Table 2-26 • DC Input and Output Levels

|         | VIL      | VIH      |         | VIH VOL |            | IOL  | IOH   |

|---------|----------|----------|---------|---------|------------|------|-------|

| Min., V | Max., V  | Min., V  | Max., V | Max., V | Min., V    | mA   | mA    |

| -0.3    | 0.2 VCCI | 0.7 VCCI | 3.6     | 0.2     | VCCI – 0.2 | 8 mA | –8 mA |

# AC Loadings

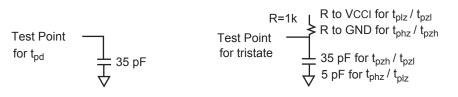

#### Figure 2-17 • AC Test Loads

#### Table 2-27 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | VREF (typ) (V) | C <sub>load</sub> (pF) |

|---------------|----------------|----------------------|----------------|------------------------|

| 0             | 1.8            | 0.5 VCCI             | N/A            | 35                     |

*Note:* \* *Measuring Point* = *VTRIP*

# **Timing Characteristics**

## Table 2-28 • 1.8V LVCMOS I/O Module

Worst-Case Commercial Conditions VCCA = 1.425 V, VCCI = 1.7 V, TJ = 70°C

|                     |                                                                           | -2 S | peed | –1 S | peed | Std S | Speed |       |

|---------------------|---------------------------------------------------------------------------|------|------|------|------|-------|-------|-------|

| Parameter           | Description                                                               | Min. | Max. | Min. | Max. | Min.  | Max.  | Units |

| LVCMOS18            | Output Module Timing                                                      |      |      |      |      |       |       |       |

| t <sub>DP</sub>     | Input Buffer                                                              |      | 3.26 |      | 3.71 |       | 4.37  | ns    |

| t <sub>PY</sub>     | Output Buffer                                                             |      | 4.55 |      | 5.18 |       | 6.09  | ns    |

| t <sub>ENZL</sub>   | Enable to Pad Delay through the Output Buffer—Z to Low                    |      | 2.82 |      | 2.83 |       | 2.84  | ns    |

| t <sub>ENZH</sub>   | Enable to Pad Delay through the Output Buffer—Z to High                   |      | 3.43 |      | 3.45 |       | 3.46  | ns    |

| t <sub>ENLZ</sub>   | Enable to Pad Delay through the Output Buffer—Low to Z                    |      | 6.01 |      | 6.85 |       | 8.05  | ns    |

| t <sub>ENHZ</sub>   | Enable to Pad Delay through the Output Buffer—High to Z                   |      | 6.73 |      | 7.67 |       | 9.01  | ns    |

| t <sub>IOCLKQ</sub> | Sequential Clock-to-Q for the I/O Input Register                          |      | 0.67 |      | 0.77 |       | 0.90  | ns    |

| t <sub>IOCLKY</sub> | Clock-to-output Y for the I/O Output Register and the I/O Enable Register |      | 0.67 |      | 0.77 |       | 0.90  | ns    |

| t <sub>SUD</sub>    | Data Input Set-Up                                                         |      | 0.23 |      | 0.27 |       | 0.31  | ns    |

| t <sub>SUE</sub>    | Enable Input Set-Up                                                       |      | 0.26 |      | 0.30 |       | 0.35  | ns    |

| t <sub>HD</sub>     | Data Input Hold                                                           |      | 0.00 |      | 0.00 |       | 0.00  | ns    |

| t <sub>HE</sub>     | Enable Input Hold                                                         |      | 0.00 |      | 0.00 |       | 0.00  | ns    |

| t <sub>CPWHL</sub>  | Clock Pulse Width High to Low                                             | 0.39 |      | 0.39 |      | 0.39  |       | ns    |

| t <sub>CPWLH</sub>  | Clock Pulse Width Low to High                                             | 0.39 |      | 0.39 |      | 0.39  |       | ns    |

| t <sub>WASYN</sub>  | Asynchronous Pulse Width                                                  | 0.37 |      | 0.37 |      | 0.37  |       | ns    |

| t <sub>REASYN</sub> | Asynchronous Recovery Time                                                |      | 0.13 |      | 0.15 |       | 0.17  | ns    |

| t <sub>HASYN</sub>  | Asynchronous Removal Time                                                 |      | 0.00 |      | 0.00 |       | 0.00  | ns    |

| t <sub>CLR</sub>    | Asynchronous Clear-to-Q                                                   |      | 0.23 |      | 0.27 |       | 0.31  | ns    |

| t <sub>PRESET</sub> | Asynchronous Preset-to-Q                                                  |      | 0.23 |      | 0.27 |       | 0.31  | ns    |

# **Timing Characteristics**

## Table 2-32 • 1.5V LVCMOS I/O Module

## Worst-Case Commercial Conditions VCCA = 1.425 V, VCCI = 1.4 V, TJ = 70°C

|                     |                                                                           | –2 S | peed | –1 S | peed | Std S | Speed |       |

|---------------------|---------------------------------------------------------------------------|------|------|------|------|-------|-------|-------|

| Parameter           | Description                                                               | Min. | Max. | Min. | Max. | Min.  | Max.  | Units |

| LVCMOS15            | (JESD8-11) I/O Module Timing                                              |      |      |      |      |       |       |       |

| t <sub>DP</sub>     | Input Buffer                                                              |      | 3.59 |      | 4.09 |       | 4.81  | ns    |

| t <sub>PY</sub>     | Output Buffer                                                             |      | 6.05 |      | 6.89 |       | 8.10  | ns    |

| t <sub>ENZL</sub>   | Enable to Pad Delay through the Output Buffer—Z to Low                    |      | 3.31 |      | 3.34 |       | 3.34  | ns    |

| t <sub>ENZH</sub>   | Enable to Pad Delay through the Output Buffer—Z to High                   |      | 4.56 |      | 4.58 |       | 4.59  | ns    |

| t <sub>ENLZ</sub>   | Enable to Pad Delay through the Output Buffer—Low to Z                    |      | 6.37 |      | 7.25 |       | 8.52  | ns    |

| t <sub>ENHZ</sub>   | Enable to Pad Delay through the Output Buffer—High to Z                   |      | 6.94 |      | 7.90 |       | 9.29  | ns    |

| t <sub>IOCLKQ</sub> | Sequential Clock-to-Q for the I/O Input Register                          |      | 0.67 |      | 0.77 |       | 0.90  | ns    |

| t <sub>IOCLKY</sub> | Clock-to-output Y for the I/O Output Register and the I/O Enable Register |      | 0.67 |      | 0.77 |       | 0.90  | ns    |

| t <sub>SUD</sub>    | Data Input Set-Up                                                         |      | 0.23 |      | 0.27 |       | 0.31  | ns    |

| t <sub>SUE</sub>    | Enable Input Set-Up                                                       |      | 0.26 |      | 0.30 |       | 0.35  | ns    |

| t <sub>HD</sub>     | Data Input Hold                                                           |      | 0.00 |      | 0.00 |       | 0.00  | ns    |

| t <sub>HE</sub>     | Enable Input Hold                                                         |      | 0.00 |      | 0.00 |       | 0.00  | ns    |

| t <sub>CPWHL</sub>  | Clock Pulse Width High to Low                                             | 0.39 |      | 0.39 |      | 0.39  |       | ns    |

| t <sub>CPWLH</sub>  | Clock Pulse Width Low to High                                             | 0.39 |      | 0.39 |      | 0.39  |       | ns    |

| t <sub>WASYN</sub>  | Asynchronous Pulse Width                                                  | 0.37 |      | 0.37 |      | 0.37  |       | ns    |

| t <sub>REASYN</sub> | Asynchronous Recovery Time                                                |      | 0.13 |      | 0.15 |       | 0.17  | ns    |

| t <sub>HASYN</sub>  | Asynchronous Removal Time                                                 |      | 0.00 |      | 0.00 |       | 0.00  | ns    |

| t <sub>CLR</sub>    | Asynchronous Clear-to-Q                                                   |      | 0.23 |      | 0.27 |       | 0.31  | ns    |

| t <sub>PRESET</sub> | Asynchronous Preset-to-Q                                                  |      | 0.23 |      | 0.27 |       | 0.31  | ns    |

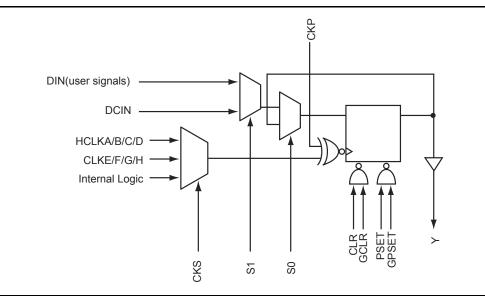

# R-Cell

#### Introduction

The R-cell, the sequential logic resource of the Axcelerator devices, is the second logic module type in the AX family architecture. It includes clock inputs for all eight global resources of the Axcelerator architecture as well as global presets and clears (Figure 2-31).

The main features of the R-cell include the following:

- Direct connection to the adjacent logic module through the hardwired connection DCIN. DCIN is driven by the DCOUT of an adjacent C-cell via the Direct-Connect routing resource, providing a connection with less than 0.1 ns of routing delay.

- The R-cell can be used as a standalone flip-flop. It can be driven by any C-cell or I/O modules through the regular routing structure (using DIN as a routable data input). This gives the option of using the R-Cell as a 2:1 MUXed flip-flop as well.

- Provision of data enable-input (S0).

- Independent active-low asynchronous clear (CLR).

- Independent active-low asynchronous preset (PSET). If both CLR and PSET are low, CLR has higher priority.

- · Clock can be driven by any of the following (CKP selects clock polarity):

- One of the four high performance hardwired fast clocks (HCLKs)

- One of the four routed clocks (CLKs)

- User signals

- Global power-on clear (GCLR) and preset (GPSET), which drive each flip-flop on a chip-wide basis.

- When the Global Set Fuse option in the Designer software is unchecked (by default), GCLR = 0 and GPSET = 1 at device power-up. When the option is checked, GCLR = 1 and GPSET = 0. Both pins are pulled High when the device is in user mode. Refer to the "Simulation Support for GCLR/GPSET in Axcelerator" section of the *Antifuse Macro Library Guide* for information on simulation support for GCLR and GPSET.

- S0, S1, PSET, and CLR can be driven by routed clocks CLKE/F/G/H or user signals.

- DIN and S1 can be driven by user signals.

As with the C-cell, the configuration of the R-cell to perform various functions is handled automatically for the user through Microsemi's extensive macro library (see the *Antifuse Macro Library Guide* for a complete listing of available AX macros).

The HM and CM modules can select between:

- The HCLK or CLK source respectively

- · A local signal routed on generic routing resources

This allows each core tile to have eight clocks independent of the other core tiles in the device.

Both HCLK and CLK are segmentable, meaning that individual branches of the global resource can be used independently.

Like the HM and CM modules, the HD and RD modules can select between:

- The HCLK or CLK source from the HM or CM module respectively

- A local signal routed on generic routing resources

The AX architecture is capable of supporting a large number of local clocks—24 segments per HCLK driving north-south and 28 segments per CLK driving east-west per core tile.

Microsemi's Designer software's place-and-route takes advantage of the segmented clock structure found in Axcelerator devices by turning off any unused clock segments. This results in not only better performance but also lower power consumption.

## **Global Resource Access Macros**

Global resources can be driven by one of three sources: external pad(s), an internal net, or the output of a PLL. These connections can be made by using one of three types of macros: CLKBUF, CLKINT, and PLLCLK.

## CLKBUF and HCLKBUF

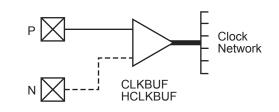

CLKBUF (HCLKBUF) is used to drive a CLK (HCLK) from external pads. These macros can be used either generically or with the specific I/O standard desired (e.g. CLKBUF\_LVCMOS25, HCLKBUF\_LVDS, etc.) (Figure 2-42).

Figure 2-42 • CLKBUF and HCLKBUF

Package pins CLKEP and CLKEN are associated with CLKE; package pins HCLKAP and HCLKAN are associated with HCLKA, etc.

Note that when CLKBUF (HCLKBUF) is used with a single-ended I/O standard, it must be tied to the P-pad of the CLK (HCLK) package pin. In this case, the CLK (HCLK) N-pad can be used for user signals.

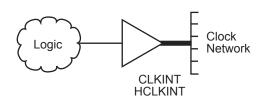

## CLKINT and HCLKINT

CLKINT (HCLKINT) is used to access the CLK (HCLK) resource internally from the user signals (Figure 2-43).

# **Clock Skew Minimization**

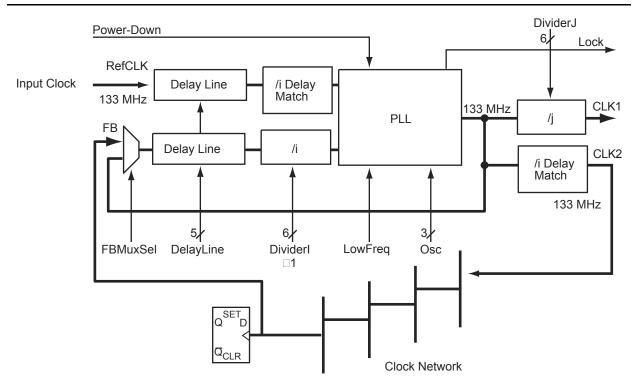

Figure 2-56 indicates how feedback from the clock network can be used to create minimal skew between the distributed clock network and the input clock. The input clock is fed to the reference clock input of the PLL. The output clock (CLK2) feeds a routed clock network. The feedback input to the PLL uses a clock input delayed by a routing network. The PLL then adjusts the phase of the input clock to match the delayed clock, thus providing nearly zero effective skew between the two clocks. Refer to the *Axcelerator Family PLL and Clock Management* application note for more information.

Figure 2-56 • Using the PLL for Clock Deskewing

```

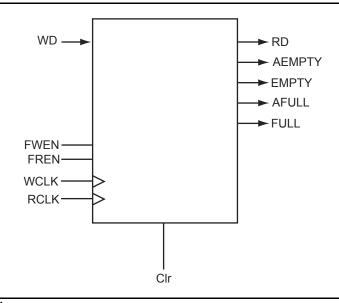

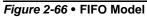

Figure 2-67 • FIFO Write Timing

```

|                      |                              | –2 S | peed  | –1 S | peed  | Std S | Speed |       |

|----------------------|------------------------------|------|-------|------|-------|-------|-------|-------|

| Parameter            | Description                  | Min. | Max.  | Min. | Max.  | Min.  | Max.  | Units |

| FIFO Module          | e Timing                     |      |       |      |       |       |       |       |

| t <sub>WSU</sub>     | Write Setup                  |      | 13.75 |      | 15.66 |       | 18.41 | ns    |

| t <sub>WHD</sub>     | Write Hold                   |      | 0.00  |      | 0.00  |       | 0.00  | ns    |

| t <sub>wcкн</sub>    | WCLK High                    |      | 0.75  |      | 0.75  |       | 0.75  | ns    |

| t <sub>WCKL</sub>    | WCLK Low                     |      | 1.76  |      | 1.76  |       | 1.76  | ns    |

| t <sub>WCKP</sub>    | Minimum WCLK Period          | 2.51 |       | 2.51 |       | 2.51  |       | ns    |

| t <sub>RSU</sub>     | Read Setup                   |      | 14.33 |      | 16.32 |       | 19.19 | ns    |

| t <sub>RHD</sub>     | Read Hold                    |      | 0.00  |      | 0.00  |       | 0.00  | ns    |

| t <sub>RCKH</sub>    | RCLK High                    |      | 0.73  |      | 0.73  |       | 0.73  | ns    |

| t <sub>RCKL</sub>    | RCLK Low                     |      | 1.89  |      | 1.89  |       | 1.89  | ns    |

| t <sub>RCKP</sub>    | Minimum RCLK period          | 2.62 |       | 2.62 |       | 2.62  |       | ns    |

| t <sub>CLRHF</sub>   | Clear High                   |      | 0.00  |      | 0.00  |       | 0.00  | ns    |

| t <sub>CLR2FF</sub>  | Clear-to-flag (EMPTY/FULL)   |      | 1.92  |      | 2.18  |       | 2.57  | ns    |

| t <sub>CLR2AF</sub>  | Clear-to-flag (AEMPTY/AFULL) |      | 4.39  |      | 5.00  |       | 5.88  | ns    |

| t <sub>CK2FF</sub>   | Clock-to-flag (EMPTY/FULL)   |      | 2.13  |      | 2.42  |       | 2.85  | ns    |

| t <sub>CK2AF</sub>   | Clock-to-flag (AEMPTY/AFULL) |      | 5.04  |      | 5.75  |       | 6.75  | ns    |

| t <sub>RCK2RD1</sub> | RCLK-To-OUT (Pipelined)      |      | 1.43  |      | 1.63  |       | 1.92  | ns    |

| t <sub>RCK2RD2</sub> | RCLK-To-OUT (Nonpipelined)   |      | 2.26  |      | 2.58  |       | 3.03  | ns    |

#### Table 2-99 • Two FIFO Blocks Cascaded

Worst-Case Commercial Conditions VCCA = 1.425 V, VCCI = 3.0 V, T<sub>J</sub> =  $70^{\circ}$ C

Note: Timing data for these two cascaded FIFO blocks uses a depth of 8,192. For all other combinations, use Microsemi's timing software.

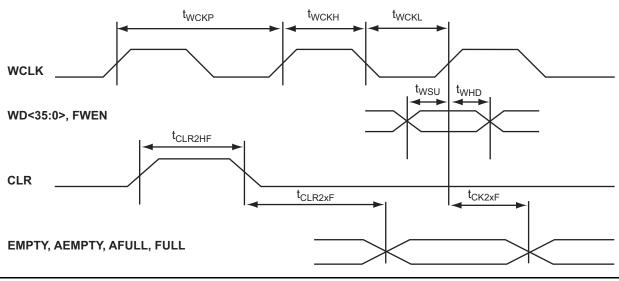

Package Pin Assignments

| FG324          |               |  |

|----------------|---------------|--|

| AX125 Function | Pin<br>Number |  |

| VCCIB5         | N7            |  |

| VCCIB5         | N8            |  |

| VCCIB5         | N9            |  |

| VCCIB6         | K6            |  |

| VCCIB6         | L6            |  |

| VCCIB6         | M6            |  |

| VCCIB7         | G6            |  |

| VCCIB7         | H6            |  |

| VCCIB7         | J6            |  |

| VCOMPLA        | B8            |  |

| VCOMPLB        | E8            |  |

| VCOMPLC        | C10           |  |

| VCOMPLD        | E12           |  |

| VCOMPLE        | U11           |  |

| VCOMPLF        | P11           |  |

| VCOMPLG        | Т9            |  |

| VCOMPLH        | P7            |  |

| VPUMP          | B15           |  |

Axcelerator Family FPGAs

| FG48           | 34         | FG48           | 4          | FG48           | ; <b>4</b> |

|----------------|------------|----------------|------------|----------------|------------|

| AX250 Function | Pin Number | AX250 Function | Pin Number | AX250 Function | Pin Number |

| NC             | A19        | NC             | G22        | PRA            | G11        |

| NC             | A4         | NC             | G3         | PRB            | F11        |

| NC             | A5         | NC             | H3         | PRC            | T12        |

| NC             | AA11       | NC             | J3         | PRD            | U12        |

| NC             | AA12       | NC             | K21        | ТСК            | G8         |

| NC             | AA18       | NC             | K22        | TDI            | F9         |

| NC             | AA19       | NC             | N22        | TDO            | F7         |

| NC             | AA4        | NC             | P22        | TMS            | F6         |

| NC             | AB16       | NC             | R19        | TRST           | F8         |

| NC             | AB17       | NC             | R22        | VCCA           | G17        |

| NC             | AB4        | NC             | T1         | VCCA           | J10        |

| NC             | AB7        | NC             | T22        | VCCA           | J11        |

| NC             | AB8        | NC             | U1         | VCCA           | J12        |

| NC             | B11        | NC             | U2         | VCCA           | J13        |

| NC             | B12        | NC             | U21        | VCCA           | J7         |

| NC             | B17        | NC             | U22        | VCCA           | K14        |

| NC             | B18        | NC             | V1         | VCCA           | K9         |

| NC             | B19        | NC             | V2         | VCCA           | L14        |

| NC             | B4         | NC             | V21        | VCCA           | L9         |

| NC             | B5         | NC             | V22        | VCCA           | M14        |

| NC             | C10        | NC             | V3         | VCCA           | M9         |

| NC             | C11        | NC             | W1         | VCCA           | N14        |

| NC             | C14        | NC             | W2         | VCCA           | N9         |

| NC             | C15        | NC             | W21        | VCCA           | P10        |

| NC             | C18        | NC             | W22        | VCCA           | P11        |

| NC             | C19        | NC             | W3         | VCCA           | P12        |

| NC             | D1         | NC             | Y10        | VCCA           | P13        |

| NC             | D2         | NC             | Y11        | VCCA           | Т6         |

| NC             | D21        | NC             | Y12        | VCCA           | U17        |

| NC             | D3         | NC             | Y13        | VCCPLA         | F10        |

| NC             | E1         | NC             | Y15        | VCCPLB         | G9         |

| NC             | E2         | NC             | Y16        | VCCPLC         | D13        |

| NC             | E21        | NC             | Y17        | VCCPLD         | G13        |

| NC             | E3         | NC             | Y18        | VCCPLE         | U13        |

| NC             | F22        | NC             | Y8         | VCCPLF         | T14        |

| NC             | F3         | NC             | Y9         | VCCPLG         | W10        |

| FG484           |               |   |

|-----------------|---------------|---|

| AX1000 Function | Pin<br>Number | A |

| IO87PB2F8       | H20           |   |

| IO88NB2F8       | L18           |   |

| IO88PB2F8       | K18           |   |

| IO89NB2F8       | K19           |   |

| IO89PB2F8       | J19           |   |

| IO90NB2F8       | J21           |   |

| IO90PB2F8       | H21           |   |

| IO91NB2F8       | J22           |   |

| IO91PB2F8       | H22           |   |

| IO93NB2F8       | K21           |   |

| IO93PB2F8       | K22           |   |

| IO94NB2F8       | L20           |   |

| IO94PB2F8       | K20           |   |

| IO95NB2F8       | M21           |   |

| IO95PB2F8       | L21           |   |

| Bank 3          |               |   |

| IO96NB3F9       | N16           |   |

| IO96PB3F9       | M16           |   |

| IO97NB3F9       | M19           |   |

| IO97PB3F9       | L19           |   |

| IO98NB3F9       | P22           |   |

| IO98PB3F9       | N22           |   |

| IO99NB3F9       | N20           |   |

| IO99PB3F9       | M20           |   |

| IO100NB3F9      | N17           |   |

| IO100PB3F9      | M17           |   |

| IO101NB3F9      | P21           |   |

| IO101PB3F9      | N21           |   |

| IO103NB3F9      | R20           |   |

| IO103PB3F9      | P20           |   |

| IO104NB3F9      | N18           |   |

| IO104PB3F9      | N19           |   |

| IO105NB3F9      | T22           |   |

| IO105PB3F9      | R22           |   |

| IO106NB3F9      | R17           |   |

|                 |               |   |

| FG484           |               |

|-----------------|---------------|

| AX1000 Function | Pin<br>Number |

| IO106PB3F9      | P17           |

| IO107NB3F10     | T21           |

| IO107PB3F10     | R21           |

| IO110NB3F10     | V22           |

| IO110PB3F10     | U22           |

| IO113NB3F10     | V21           |

| IO113PB3F10     | U21           |

| IO114NB3F10     | P18           |

| IO114PB3F10     | P19           |

| IO116PB3F10     | R19           |

| IO117NB3F10     | U20           |

| IO117PB3F10     | T20           |

| IO118NB3F11     | T18           |

| IO118PB3F11     | R18           |

| IO121NB3F11     | U19           |

| IO121PB3F11     | T19           |

| IO124NB3F11     | R16           |

| IO124PB3F11     | P16           |

| IO127NB3F11     | W21           |

| IO127PB3F11     | W22           |

| Bank 4          |               |

| IO129PB4F12     | AB17          |

| IO132NB4F12     | Y19           |

| IO132PB4F12     | W18           |

| IO133NB4F12     | W17           |

| IO133PB4F12     | V17           |

| IO135NB4F12     | T15           |

| IO135PB4F12     | T16           |

| IO138NB4F12     | Y17           |

| IO138PB4F12     | Y18           |

| IO139NB4F13     | V15           |

| IO139PB4F13     | V16           |

| IO140NB4F13     | U18           |

| IO140PB4F13     | V19           |

| IO142NB4F13     | W20           |

| FG484             |               |  |  |  |

|-------------------|---------------|--|--|--|

| AX1000 Function   | Pin<br>Number |  |  |  |

| IO142PB4F13       | V20           |  |  |  |

| IO143NB4F13       | W15           |  |  |  |

| IO143PB4F13       | W16           |  |  |  |

| IO144NB4F13       | AA18          |  |  |  |

| IO144PB4F13       | AA19          |  |  |  |

| IO145NB4F13       | U14           |  |  |  |

| IO145PB4F13       | U15           |  |  |  |

| IO146NB4F13       | Y15           |  |  |  |

| IO146PB4F13       | Y16           |  |  |  |

| IO147NB4F13       | AB18          |  |  |  |

| IO147PB4F13       | AB19          |  |  |  |

| IO149NB4F13       | Y14           |  |  |  |

| IO149PB4F13       | W14           |  |  |  |

| IO150NB4F13       | AA16          |  |  |  |

| IO150PB4F13       | AA17          |  |  |  |

| IO152NB4F14       | AA14          |  |  |  |

| IO152PB4F14       | AA15          |  |  |  |

| IO154NB4F14       | AB14          |  |  |  |

| IO154PB4F14       | AB15          |  |  |  |

| IO155NB4F14       | AA13          |  |  |  |

| IO155PB4F14       | AB13          |  |  |  |

| IO158NB4F14       | Y12           |  |  |  |

| IO158PB4F14       | Y13           |  |  |  |

| IO159NB4F14/CLKEN | V12           |  |  |  |

| IO159PB4F14/CLKEP | V13           |  |  |  |

| IO160NB4F14/CLKFN | W11           |  |  |  |

| IO160PB4F14/CLKFP | W12           |  |  |  |

| Bank 5            |               |  |  |  |

| IO161NB5F15/CLKGN | U10           |  |  |  |

| IO161PB5F15/CLKGP | U11           |  |  |  |

| IO162NB5F15/CLKHN | V9            |  |  |  |

| IO162PB5F15/CLKHP | V10           |  |  |  |

| IO163NB5F15       | Y10           |  |  |  |

| IO163PB5F15       | Y11           |  |  |  |

| IO167NB5F15       | AA11          |  |  |  |

Package Pin Assignments

| FG676         |               | FG676          |               |

|---------------|---------------|----------------|---------------|

| X500 Function | Pin<br>Number | AX500 Function | Pin<br>Number |

| VCCIB3        | T19           | VCCIB7         | L8            |

| VCCIB3        | U19           | VCCIB7         | M8            |

| VCCIB3        | U20           | VCCIB7         | N8            |

| VCCIB3        | V19           | VCCPLA         | E12           |

| VCCIB3        | V20           | VCCPLB         | F13           |

| VCCIB3        | W20           | VCCPLC         | E15           |

| VCCIB4        | W14           | VCCPLD         | G14           |

| VCCIB4        | W15           | VCCPLE         | AF15          |

| VCCIB4        | W16           | VCCPLF         | AA14          |

| VCCIB4        | W17           | VCCPLG         | AF12          |

| VCCIB4        | W18           | VCCPLH         | AB13          |

| VCCIB4        | Y17           | VCOMPLA        | D12           |

| VCCIB4        | Y18           | VCOMPLB        | G13           |

| VCCIB4        | Y19           | VCOMPLC        | D15           |

| VCCIB5        | W10           | VCOMPLD        | F14           |

| VCCIB5        | W11           | VCOMPLE        | AD15          |

| VCCIB5        | W12           | VCOMPLF        | AB14          |

| VCCIB5        | W13           | VCOMPLG        | AD12          |

| VCCIB5        | W9            | VCOMPLH        | Y13           |

| VCCIB5        | Y10           | VPUMP          | E22           |

| VCCIB5        | Y8            |                |               |

| VCCIB5        | Y9            |                |               |

| VCCIB6        | P8            |                |               |

| VCCIB6        | R8            |                |               |

| VCCIB6        | Т8            |                |               |

| VCCIB6        | U7            |                |               |

| VCCIB6        | U8            |                |               |

| VCCIB6        | V7            |                |               |

| VCCIB6        | V8            |                |               |

| VCCIB6        | W7            |                |               |

| VCCIB7        | H7            |                |               |

| VCCIB7        | J7            |                |               |

| VCCIB7        | J8            |                |               |

| VCCIB7        | K7            |                |               |

| VCCIB7        | K8            |                |               |

| FG676           |            | FG676           |            | FG676           |            |

|-----------------|------------|-----------------|------------|-----------------|------------|

| AX1000 Function | Pin Number | AX1000 Function | Pin Number | AX1000 Function | Pin Number |

| GND             | A8         | GND             | L12        | GND             | R12        |

| GND             | AC23       | GND             | L13        | GND             | R13        |

| GND             | AC4        | GND             | L14        | GND             | R14        |

| GND             | AD24       | GND             | L15        | GND             | R15        |

| GND             | AD3        | GND             | L16        | GND             | R16        |

| GND             | AE2        | GND             | L17        | GND             | R17        |

| GND             | AE25       | GND             | M10        | GND             | T10        |

| GND             | AF1        | GND             | M11        | GND             | T11        |

| GND             | AF13       | GND             | M12        | GND             | T12        |

| GND             | AF14       | GND             | M13        | GND             | T13        |

| GND             | AF19       | GND             | M14        | GND             | T14        |

| GND             | AF26       | GND             | M15        | GND             | T15        |

| GND             | AF8        | GND             | M16        | GND             | T16        |

| GND             | B2         | GND             | M17        | GND             | T17        |

| GND             | B25        | GND             | N1         | GND             | U10        |

| GND             | B26        | GND             | N10        | GND             | U11        |

| GND             | C24        | GND             | N11        | GND             | U12        |

| GND             | C3         | GND             | N12        | GND             | U13        |

| GND             | G20        | GND             | N13        | GND             | U14        |

| GND             | G7         | GND             | N14        | GND             | U15        |

| GND             | H1         | GND             | N15        | GND             | U16        |

| GND             | H19        | GND             | N16        | GND             | U17        |

| GND             | H26        | GND             | N17        | GND             | V18        |

| GND             | H8         | GND             | N26        | GND             | V9         |

| GND             | J18        | GND             | P1         | GND             | W1         |

| GND             | J9         | GND             | P10        | GND             | W19        |

| GND             | K10        | GND             | P11        | GND             | W26        |

| GND             | K11        | GND             | P12        | GND             | W8         |

| GND             | K12        | GND             | P13        | GND             | Y20        |

| GND             | K13        | GND             | P14        | GND             | Y7         |

| GND             | K14        | GND             | P15        | GND/LP          | C2         |

| GND             | K15        | GND             | P16        | NC              | A25        |

| GND             | K16        | GND             | P17        | NC              | AC13       |

| GND             | K17        | GND             | P26        | NC              | AC14       |

| GND             | L10        | GND             | R10        | NC              | AF2        |

| GND             | L11        | GND             | R11        | NC              | AF25       |

Package Pin Assignments

| FG896           |               | FG896           |               |

|-----------------|---------------|-----------------|---------------|

| AX2000 Function | Pin<br>Number | AX2000 Function | Pin<br>Number |

| VCCIB3          | AH30          | VCCIB6          | W9            |

| VCCIB3          | T21           | VCCIB6          | Y10           |

| VCCIB3          | U21           | VCCIB6          | Y9            |

| VCCIB3          | V21           | VCCIB7          | C1            |

| VCCIB3          | W21           | VCCIB7          | C2            |

| VCCIB3          | W22           | VCCIB7          | K9            |

| VCCIB3          | Y21           | VCCIB7          | L10           |

| VCCIB3          | Y22           | VCCIB7          | L9            |

| VCCIB4          | AA16          | VCCIB7          | M10           |

| VCCIB4          | AA17          | VCCIB7          | M9            |

| VCCIB4          | AA18          | VCCIB7          | N10           |

| VCCIB4          | AA19          | VCCIB7          | P10           |

| VCCIB4          | AA20          | VCCIB7          | R10           |

| VCCIB4          | AB19          | VCCPLA          | G14           |

| VCCIB4          | AB20          | VCCPLB          | H15           |

| VCCIB4          | AB21          | VCCPLC          | G17           |

| VCCIB4          | AJ28          | VCCPLD          | J16           |

| VCCIB4          | AK28          | VCCPLE          | AH17          |

| VCCIB5          | AA11          | VCCPLF          | AC16          |

| VCCIB5          | AA12          | VCCPLG          | AH14          |

| VCCIB5          | AA13          | VCCPLH          | AD15          |

| VCCIB5          | AA14          | VCOMPLA         | F14           |

| VCCIB5          | AA15          | VCOMPLB         | J15           |

| VCCIB5          | AB10          | VCOMPLC         | F17           |

| VCCIB5          | AB11          | VCOMPLD         | H16           |

| VCCIB5          | AB12          | VCOMPLE         | AF17          |

| VCCIB5          | AJ3           | VCOMPLF         | AD16          |

| VCCIB5          | AK3           | VCOMPLG         | AF14          |

| VCCIB6          | AA9           | VCOMPLH         | AB15          |

| VCCIB6          | AH1           | VPUMP           | G24           |

| VCCIB6          | AH2           |                 |               |

| VCCIB6          | T10           |                 |               |

| VCCIB6          | U10           |                 |               |

| VCCIB6          | V10           |                 |               |

| VCCIB6          | W10           |                 |               |

## Note

For Package Manufacturing and Environmental information, visit Resource center at http://www.microsemi.com/soc/products/rescenter/package/index.html.

Datasheet Information

| Revision                   | Changes                                                                                                                                                                      | Page                               |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| Revision 10<br>(continued) | The "TRST" section was updated.                                                                                                                                              | 2-107                              |

|                            | The "Global Set Fuse" section was added.                                                                                                                                     | 2-109                              |

|                            | A footnote was added to "FG896" for the AX2000 regarding pins AB1, AE2, G1, and K2.                                                                                          | 3-52                               |

|                            | Pinouts for the AX250, AX500, and AX1000 were added for "CQ352".                                                                                                             | 3-98                               |

|                            | Pinout for the AX1000 was added for "CG624".                                                                                                                                 | 3-115                              |

| Revision 9                 | Table 2-79 was updated.                                                                                                                                                      | 2-69                               |

| (v2.1)                     | The "Low Power Mode" section was updated.                                                                                                                                    | 2-106                              |

| Revision 8<br>(v2.0)       | Table 1 has been updated.                                                                                                                                                    | i                                  |

|                            | The "Ordering Information" section has been updated.                                                                                                                         | ii                                 |

|                            | The "Device Resources" section has been updated.                                                                                                                             | ii                                 |

|                            | The "Temperature Grade Offerings" section is new.                                                                                                                            | iii                                |

|                            | The "Speed Grade and Temperature Grade Matrix" section has been updated.                                                                                                     | iii                                |

|                            | Table 2-9 has been updated.                                                                                                                                                  | 2-12                               |

|                            | Table 2-10 has been updated.                                                                                                                                                 | 2-12                               |

|                            | Table 2-1 has been updated.                                                                                                                                                  | 2-1                                |

|                            | Table 2-2 has been updated.                                                                                                                                                  | 2-1                                |

|                            | Table 2-3 has been updated.                                                                                                                                                  | 2-2                                |

|                            | Table 2-4 has been updated.                                                                                                                                                  | 2-3                                |

|                            | Table 2-5 has been updated.                                                                                                                                                  | 2-4                                |

|                            | The "Power Estimation Example" section has been updated.                                                                                                                     | 2-5                                |

|                            | The "Thermal Characteristics" section has been updated.                                                                                                                      | 2-6                                |

|                            | The "Package Thermal Characteristics" section has been updated.                                                                                                              | 2-6                                |

|                            | The "Timing Characteristics" section has been updated.                                                                                                                       | 2-7                                |

|                            | The "Pin Descriptions" section has been updated.                                                                                                                             | 2-9                                |

|                            | Timing numbers have been updated from the "3.3 V LVTTL" section to the "Timing Characteristics" section. Many AC Loads were updated as well.                                 | 2-25 to 2-59                       |

|                            | Timing characteristics for the "Hardwired Clocks" and "Routed Clocks" sections were updated.                                                                                 | 2-66, 2-68                         |

|                            | Table 2-89 to Table 2-92 and Table 2-98 to Table 2-99 were updated.                                                                                                          | 2-90 to 2-93,<br>2-102 to<br>2-103 |

|                            | The following sections were updated:<br>"Low Power Mode", "Interface", "Data Registers (DRs)", "Security", "Silicon<br>Explorer II Probe Interface", and "Programming"       | 2-106 to<br>2-110                  |

|                            | In the "PQ208" (AX500) section, pins 2, 52, and 156 changed from V <sub>CCDA</sub> to V <sub>CCA</sub> . For pins 170 and 171, the I/O names refer to pair 23 instead of 24. | 3-84                               |