# E·XFL

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                                  |

|--------------------------------|-------------------------------------------------------------------------|

| Number of LABs/CLBs            | 32256                                                                   |

| Number of Logic Elements/Cells | -                                                                       |

| Total RAM Bits                 | 294912                                                                  |

| Number of I/O                  | 586                                                                     |

| Number of Gates                | 200000                                                                  |

| Voltage - Supply               | 1.425V ~ 1.575V                                                         |

| Mounting Type                  | Surface Mount                                                           |

| Operating Temperature          | 0°C ~ 70°C (TA)                                                         |

| Package / Case                 | 896-BGA                                                                 |

| Supplier Device Package        | 896-FBGA (31x31)                                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/ax2000-1fg896 |

|                                |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

General Description

Up to four individual signals can be brought out to dedicated probe pins (PRA/B/C/D) on the device. The probe circuitry is accessed and controlled via Silicon Explorer II, Microsemi's integrated verification and logic analysis tool that attaches to the serial port of a PC and communicates with the FPGA via the JTAG port (See "Silicon Explorer II Probe Interface" on page 2-109).

# Summary

Microsemi's Axcelerator family of FPGAs extends the successful SX-A architecture, adding embedded RAM/FIFOs, PLLs, and high-speed I/Os. With the support of a suite of robust software tools, design engineers can incorporate high gate counts and fixed pins into an Axcelerator design yet still achieve high performance and efficient device utilization.

# **Related Documents**

# **Application Notes**

Simultaneous Switching Noise and Signal Integrity http://www.microsemi.com/soc/documents/SSN\_AN.pdf Axcelerator Family PLL and Clock Management http://www.microsemi.com/soc/documents/AX\_PLL\_AN.pdf Implementation of Security in Actel Antifuse FPGAs http://www.microsemi.com/soc/documents/Antifuse\_Security\_AN.pdf

# **User's Guides and Manuals**

Antifuse Macro Library Guide http://www.microsemi.com/soc/documents/libguide\_UG.pdf SmartGen, FlashROM, Analog System Builder, and Flash Memory System Builder http://www.microsemi.com/soc/documents/genguide\_ug.pdf Silicon Sculptor II User's Guide http://www.microsemi.com/soc/documents/silisculptII\_sculpt3\_ug.pdf

# White Paper

Design Security in Nonvolatile Flash and Antifuse FPGAs http://www.microsemi.com/soc/documents/DesignSecurity\_WP.pdf Understanding Actel Antifuse Device Security http://www.microsemi.com/soc/documents/DesignSecurity\_WP.pdf

# Miscellaneous

Libero IDE flow diagram http://www.microsemi.com/soc/products/tools/libero/flow.html

## **User-Defined Supply Pins**

#### VREF

#### Supply Voltage

Reference voltage for I/O banks. VREF pins are configured by the user from regular I/O pins; VREF pins are not in fixed locations. There can be one or more VREF pins in an I/O bank.

#### **Global Pins**

#### HCLKA/B/C/D Dedicated (Hardwired) Clocks A, B, C and D

These pins are the clock inputs for sequential modules or north PLLs. Input levels are compatible with all supported I/O standards. There is a P/N pin pair for support of differential I/O standards. Single-ended clock I/Os can only be assigned to the P side of a paired I/O. This input is directly wired to each R-cell and offers clock speeds independent of the number of R-cells being driven. When the HCLK pins are unused, it is recommended that they are tied to ground.

#### CLKE/F/G/H Routed Clocks E, F, G, and H

These pins are clock inputs for clock distribution networks or south PLLs. Input levels are compatible with all supported I/O standards. There is a P/N pin pair for support of differential I/O standards. Single-ended clock I/Os can only be assigned to the P side of a paired I/O. The clock input is buffered prior to clocking the R-cells. When the CLK pins are unused, Microsemi recommends that they are tied to ground.

#### JTAG/Probe Pins

#### PRA/B/C/D Probe A, B, C and D

The Probe pins are used to output data from any user-defined design node within the device (controlled with Silicon Explorer II). These independent diagnostic pins can be used to allow real-time diagnostic output of any signal path within the device. The pins' probe capabilities can be permanently disabled to protect programmed design confidentiality. The probe pins are of LVTTL output levels.

#### TCK Test Clock

Test clock input for JTAG boundary-scan testing and diagnostic probe (Silicon Explorer II).

#### TDI Test Data Input

Serial input for JTAG boundary-scan testing and diagnostic probe. TDI is equipped with an internal 10 k $\Omega$  pull-up resistor.

#### TDO Test Data Output

Serial output for JTAG boundary-scan testing.

#### TMS Test Mode Select

The TMS pin controls the use of the IEEE 1149.1 boundary-scan pins (TCK, TDI, TDO, TRST). TMS is equipped with an internal 10 k $\Omega$  pull-up resistor.

#### TRST Boundary Scan Reset Pin

The TRST pin functions as an active-low input to asynchronously initialize or reset the boundary scan circuit. The TRST pin is equipped with a 10 k $\Omega$  pull-up resistor.

#### **Special Functions**

#### LP Low Power Pin

The LP pin controls the low power mode of Axcelerator devices. The device is placed in the low power mode by connecting the LP pin to logic high. To exit the low power mode, the LP pin must be set Low. Additionally, the LP pin must be set Low during chip powering-up or chip powering-down operations. See "Low Power Mode" on page 2-106 for more details.

#### NC No Connection

This pin is not connected to circuitry within the device. These pins can be driven to any voltage or can be left floating with no effect on the operation of the device.

**Detailed Specifications**

#### Table 2-8 • I/O Standards Supported by the Axcelerator Family

| I/O Standard            | Input/Output Supply<br>Voltage (VCCI) | Input Reference<br>Voltage (VREF) | Board Termination<br>Voltage (VTT) |

|-------------------------|---------------------------------------|-----------------------------------|------------------------------------|

| LVTTL                   | 3.3                                   | N/A                               | N/A                                |

| LVCMOS 2.5 V            | 2.5                                   | N/A                               | N/A                                |

| LVCMOS 1.8 V            | 1.8                                   | N/A                               | N/A                                |

| LVCMOS 1.5 V (JDEC8-11) | 1.5                                   | N/A                               | N/A                                |

| 3.3V PCI/PCI-X          | 3.3                                   | N/A                               | N/A                                |

| GTL+ 3.3 V              | 3.3                                   | 1.0                               | 1.2                                |

| GTL+ 2.5 V <sup>*</sup> | 2.5                                   | 1.0                               | 1.2                                |

| HSTL Class 1            | 1.5                                   | 0.75                              | 0.75                               |

| SSTL3 Class 1 and II    | 3.3                                   | 1.5                               | 1.5                                |

| SSTL2 Class1 and II     | 2.5                                   | 1.25                              | 1.25                               |

| LVDS                    | 2.5                                   | N/A                               | N/A                                |

| LVPECL                  | 3.3                                   | N/A                               | N/A                                |

Note: \*2.5 V GTL+ is not supported across the full military temperature range.

#### Table 2-9 • Supply Voltages

| VCCA  | VCCI  | Input Tolerance | Output Drive Level |

|-------|-------|-----------------|--------------------|

| 1.5 V | 1.5 V | 3.3 V           | 1.5 V              |

| 1.5 V | 1.8 V | 3.3 V           | 1.8 V              |

| 1.5 V | 2.5 V | 3.3 V           | 2.5 V              |

| 1.5 V | 3.3 V | 3.3 V           | 3.3 V              |

Table 2-10 • I/O Features Comparison

| I/O Assignment                    | Clamp<br>Diode | Hot<br>Insertion | 5 V<br>Tolerance    | Input<br>Buffer  | Output<br>Buffer     |

|-----------------------------------|----------------|------------------|---------------------|------------------|----------------------|

| LVTTL                             | No             | Yes              | Yes <sup>1</sup>    | Enabled/         | Disabled             |

| 3.3 V PCI, 3.3 V PCI-X            | Yes            | No               | Yes <sup>1, 2</sup> | Enabled/         | Disabled             |

| LVCMOS 2.5 V                      | No             | Yes              | No                  | Enabled/Disabled |                      |

| LVCMOS 1.8 V                      | No             | Yes              | No                  | Enabled/Disabled |                      |

| LVCMOS 1.5 V (JESD8-11)           | No             | Yes              | No                  | Enabled/         | Disabled             |

| Voltage-Referenced Input Buffer   | No             | Yes              | No                  | Enabled/Disabled |                      |

| Differential, LVDS/LVPECL, Input  | No             | Yes              | No                  | Enabled Disabled |                      |

| Differential, LVDS/LVPECL, Output | No             | Yes              | No                  | Disabled         | Enabled <sup>4</sup> |

Notes:

1. Can be implemented with an IDT bus switch.

2. Can be implemented with an external resistor.

3. The OE input of the output buffer must be deasserted permanently (handled by software).

4. The OE input of the output buffer must be asserted permanently (handled by software).

**Detailed Specifications**

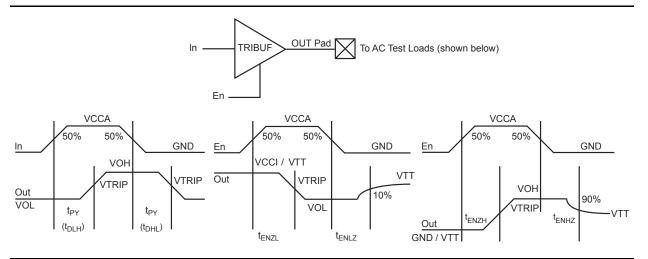

Figure 2-10 • Output Buffer Delays

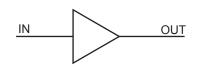

# **Buffer Module**

### Introduction

An additional resource inside each SuperCluster is the Buffer (B) module (Figure 1-4 on page 1-3). When a fanout constraint is applied to a design, the synthesis tool inserts buffers as needed. The buffer module has been added to the AX architecture to avoid logic duplication resulting from the hard fanout constraints. The router utilizes this logic resource to save area and reduce loading and delays on medium-to-high-fanout nets.

## Timing Models and Waveforms

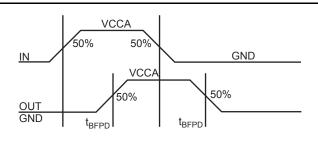

Figure 2-33 • Buffer Module Timing Model

Figure 2-34 • Buffer Module Waveform

# Timing Characteristics

#### Table 2-64 • Buffer Module

Worst-Case Commercial Conditions VCCA = 1.425 V, VCCI = 3.0 V, T<sub>J</sub> =  $70^{\circ}$ C

|                                  |                       | -2 Speed |      | –1 Speed |      | Std Speed |      |       |

|----------------------------------|-----------------------|----------|------|----------|------|-----------|------|-------|

| Parameter                        | Description           | Min.     | Max. | Min.     | Max. | Min.      | Max. | Units |

| Buffer Module Propagation Delays |                       |          |      |          |      |           |      |       |

| t <sub>BFPD</sub>                | Any input to output Y |          | 0.12 |          | 0.14 |           | 0.16 | ns    |

#### Table 2-77 • AX500 Routed Array Clock Networks Worst-Case Commercial Conditions VCCA = 1.425 V, VCCI = 3.0 V, T<sub>J</sub> = 70°C

|                    |                          | -2 Speed |      | -1 Speed |      | Std Speed |      |       |

|--------------------|--------------------------|----------|------|----------|------|-----------|------|-------|

| Parameter          | Description              | Min.     | Max. | Min.     | Max. | Min.      | Max. | Units |

| Routed Arra        | ay Clock Networks        |          |      |          |      |           |      |       |

| t <sub>RCKL</sub>  | Input Low to High        |          | 2.31 |          | 2.63 |           | 3.09 | ns    |

| t <sub>RCKH</sub>  | Input High to Low        |          | 2.44 |          | 2.78 |           | 3.27 | ns    |

| t <sub>RPWH</sub>  | Minimum Pulse Width High | 0.57     |      | 0.64     |      | 0.75      |      | ns    |

| t <sub>RPWL</sub>  | Minimum Pulse Width Low  | 0.52     |      | 0.59     |      | 0.69      |      | ns    |

| t <sub>RCKSW</sub> | Maximum Skew             |          | 0.35 |          | 0.39 |           | 0.46 | ns    |

| t <sub>RP</sub>    | Minimum Period           | 1.15     |      | 1.31     |      | 1.54      |      | ns    |

| t <sub>RMAX</sub>  | Maximum Frequency        |          | 870  |          | 763  |           | 649  | MHz   |

# Table 2-78 • AX1000 Routed Array Clock Networks

# Worst-Case Commercial Conditions VCCA = 1.425 V, VCCI = 3.0 V, T<sub>J</sub> = $70^{\circ}$ C

|                    |                          | -2 S | peed | -1 S | peed | Std S | Speed |       |

|--------------------|--------------------------|------|------|------|------|-------|-------|-------|

| Parameter          | Description              | Min. | Max. | Min. | Max. | Min.  | Max.  | Units |

| Routed Arra        | ay Clock Networks        |      |      |      |      |       |       |       |

| t <sub>RCKL</sub>  | Input Low to High        |      | 3.08 |      | 3.50 |       | 4.12  | ns    |

| t <sub>RCKH</sub>  | Input High to Low        |      | 3.13 |      | 3.56 |       | 4.19  | ns    |

| t <sub>RPWH</sub>  | Minimum Pulse Width High | 0.57 |      | 0.64 |      | 0.75  |       | ns    |

| t <sub>RPWL</sub>  | Minimum Pulse Width Low  | 0.52 |      | 0.59 |      | 0.69  |       | ns    |

| t <sub>RCKSW</sub> | Maximum Skew             |      | 0.35 |      | 0.39 |       | 0.46  | ns    |

| t <sub>RP</sub>    | Minimum Period           | 1.15 |      | 1.31 |      | 1.54  |       | ns    |

| t <sub>RMAX</sub>  | Maximum Frequency        |      | 870  |      | 763  |       | 649   | MHz   |

# Table 2-79 • AX2000 Routed Array Clock Networks

# Worst-Case Commercial Conditions VCCA = 1.425 V, VCCI = 3.0 V, T<sub>J</sub> = $70^{\circ}$ C

|                             |                          | –2 S | peed | –1 S | peed | Std S | peed |       |

|-----------------------------|--------------------------|------|------|------|------|-------|------|-------|

| Parameter                   | Description              | Min. | Max. | Min. | Max. | Min.  | Max. | Units |

| Routed Array Clock Networks |                          |      |      |      |      |       |      |       |

| t <sub>RCKL</sub>           | Input Low to High        |      | 3.08 |      | 3.50 |       | 4.12 | ns    |

| t <sub>RCKH</sub>           | Input High to Low        |      | 3.13 |      | 3.56 |       | 4.19 | ns    |

| t <sub>RPWH</sub>           | Minimum Pulse Width High | 0.57 |      | 0.64 |      | 0.75  |      | ns    |

| t <sub>RPWL</sub>           | Minimum Pulse Width Low  | 0.52 |      | 0.59 |      | 0.69  |      | ns    |

| t <sub>RCKSW</sub>          | Maximum Skew             |      | 0.35 |      | 0.39 |       | 0.46 | ns    |

| t <sub>RP</sub>             | Minimum Period           | 1.15 |      | 1.31 |      | 1.54  |      | ns    |

| t <sub>RMAX</sub>           | Maximum Frequency        |      | 870  |      | 763  |       | 649  | MHz   |

# **User Flow**

There are two methods of including a PLL in a design:

- The recommended method of using a PLL is to create custom PLL blocks using Microsemi's macro generator, SmartGen, that can be instantiated in a design.

- The alternative method is to instantiate one of the generic library primitives (PLL or PLLFB) into either a schematic or HDL netlist, using inverters for polarity control and tying all unused address and data bits to ground.

## Timing Model

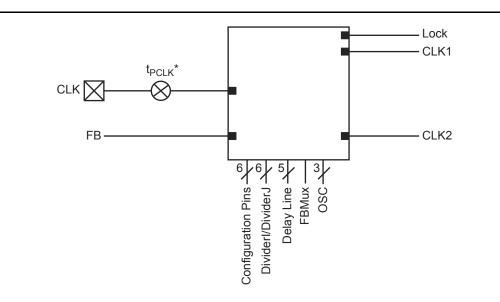

Note: t<sub>PCLK</sub> is the delay in the clock signal Figure 2-52 • PLL Model

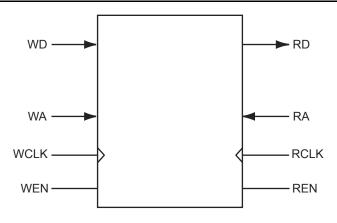

Note that the RAM blocks employ little-endian byte order for read and write operations.

| Table 2-88 • RA | M Signal   | Description |

|-----------------|------------|-------------|

|                 | in Olgilai | Description |

| Signal    | Direction | Description                                                                                                                                          |

|-----------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| WCLK      | Input     | Write clock (can be active on either edge).                                                                                                          |

| WA[J:0]   | Input     | Write address bus. The value J is dependent on the RAM configuration and the number of cascaded memory blocks. The valid range for J is from 6 to15. |

| WD[M-1:0] | Input     | Write data bus. The value M is dependent on the RAM configuration and can be 1, 2, 4, 9, 18, or 36.                                                  |

| RCLK      | Input     | Read clock (can be active on either edge).                                                                                                           |

| RA[K:0]   | Input     | Read address bus. The value K is dependent on the RAM configuration and the number of cascaded memory blocks. The valid range for K is from 6 to 15. |

| RD[N-1:0] | Output    | Read data bus. The value N is dependent on the RAM configuration and can be 1, 2, 4, 9, 18, or 36.                                                   |

| REN       | Input     | Read enable. When this signal is valid on the active edge of the clock, data at location RA will be driven onto RD.                                  |

| WEN       | Input     | Write enable. When this signal is valid on the active edge of the clock, WD data will be written at location WA.                                     |

| RW[2:0]   | Input     | Width of the read operation dataword.                                                                                                                |

| WW[2:0]   | Input     | Width of the write operation dataword.                                                                                                               |

| Pipe      | Input     | Sets the pipe option to be on or off.                                                                                                                |

# Modes of Operation

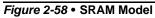

There are two read modes and one write mode:

- Read Nonpipelined (synchronous one clock edge)

- Read Pipelined (synchronous two clock edges)

- Write (synchronous one clock edge)

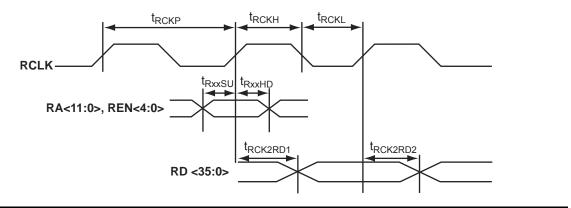

In the standard read mode, new data is driven onto the RD bus in the clock cycle immediately following RA and REN valid. The read address is registered on the read-port active-clock edge and data appears at read-data after the RAM access time. Setting the PIPE to OFF enables this mode.

The pipelined mode incurs an additional clock delay from address to data, but enables operation at a much higher frequency. The read-address is registered on the read-port active-clock edge, and the read data is registered and appears at RD after the second read clock edge. Setting the PIPE to ON enables this mode.

On the write active-clock edge, the write data are written into the SRAM at the write address when WEN is high. The setup time of the write address, write enables, and write data are minimal with respect to the write clock.

Write and read transfers are described with timing requirements beginning in the "Timing Characteristics" section on page 2-89.

# **Timing Characteristics**

**Detailed Specifications**

# Programming

Device programming is supported through the Silicon Sculptor II, a single-site, robust and compact device programmer for the PC. Up to four Silicon Sculptor IIs can be daisy-chained and controlled from a single PC host. With standalone software for the PC, Silicon Sculptor II is designed to allow concurrent programming of multiple units from the same PC when daisy-chained.

Silicon Sculptor II programs devices independently to achieve the fastest programming times possible. Each fuse is verified by Silicon Sculptor II to ensure correct programming. Furthermore, at the end of programming, there are integrity tests that are run to ensure that programming was completed properly. Not only does it test programmed and nonprogrammed fuses, Silicon Sculptor II also provides a self-test to test its own hardware extensively.

Programming an Axcelerator device using Silicon Sculptor II is similar to programming any other antifuse device. The procedure is as follows:

- 1. Load the \*.AFM file.

- 2. Select the device to be programmed.

- 3. Begin programming.

When the design is ready to go to production, Microsemi offers device volume-programming services either through distribution partners or via our In-House Programming Center.

In addition, BP Microsystems offers multi-site programmers that provide qualified support for Axcelerator devices.

For more details on programming the Axcelerator devices, please refer to the Silicon Sculptor II User's Guide.

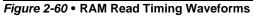

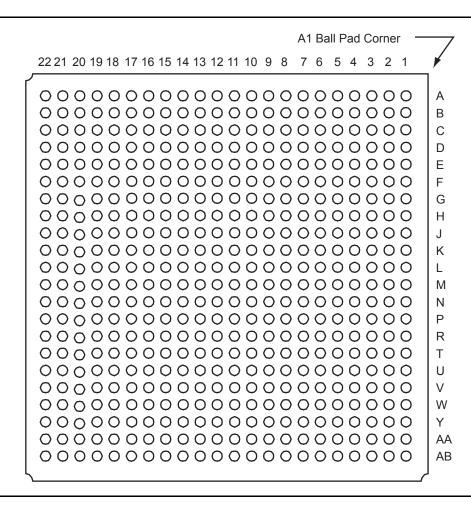

# 3 – Package Pin Assignments

# BG729

# Note

Package Pin Assignments

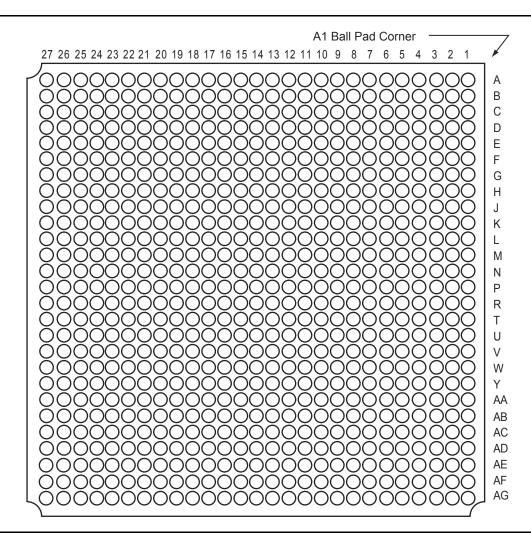

# FG324

### Note

| FG324            |               | FG324          |               | FG324           |               |

|------------------|---------------|----------------|---------------|-----------------|---------------|

| AX125 Function   | Pin<br>Number | AX125 Function | Pin<br>Number | AX125 Function  | Pin<br>Number |

| Bank 0           |               | IO16PB1F1      | C15           | IO33NB3F3       | R18           |

| IO00NB0F0        | C5            | IO17NB1F1      | E14           | IO33PB3F3       | P18           |

| IO00PB0F0        | C4            | IO17PB1F1      | E13           | IO34NB3F3       | N15           |

| IO01NB0F0        | A3            | Bank 2         | •             | IO34PB3F3       | M15           |

| IO01PB0F0        | A2            | IO18NB2F2      | G14           | IO35NB3F3       | M16           |

| IO02NB0F0        | C7            | IO18PB2F2      | F14           | IO35PB3F3       | M17           |

| IO02PB0F0        | C6            | IO19NB2F2      | D16           | IO36NB3F3       | P16           |

| IO03NB0F0        | B5            | IO19PB2F2      | D15           | IO36PB3F3       | N16           |

| IO03PB0F0        | B4            | IO20NB2F2      | C18           | IO37NB3F3       | R17           |

| IO04NB0F0        | A5            | IO20PB2F2      | B18           | IO37PB3F3       | P17           |

| IO04PB0F0        | A4            | IO21NB2F2      | D17           | IO38NB3F3       | N14           |

| IO05NB0F0        | A7            | IO21PB2F2      | C17           | IO38PB3F3       | M14           |

| IO05PB0F0        | A6            | IO22NB2F2      | F17           | IO39NB3F3       | U18           |

| IO06NB0F0        | B7            | IO22PB2F2      | E17           | IO39PB3F3       | T18           |

| IO06PB0F0        | B6            | IO23NB2F2      | G16           | IO40NB3F3       | R16           |

| IO07NB0F0/HCLKAN | C9            | IO23PB2F2      | F16           | IO40PB3F3       | T17           |

| IO07PB0F0/HCLKAP | C8            | IO24NB2F2      | E18           | IO41NB3F3       | P13           |

| IO08NB0F0/HCLKBN | B10           | IO24PB2F2      | D18           | IO41PB3F3       | P14           |

| IO08PB0F0/HCLKBP | B9            | IO25NB2F2      | G18           | Bank 4          |               |

| Bank 1           |               | IO25PB2F2      | F18           | IO42NB4F4       | T13           |

| IO09NB1F1/HCLKCN | D11           | IO26NB2F2      | H17           | IO42PB4F4       | T14           |

| IO09PB1F1/HCLKCP | D10           | IO26PB2F2      | G17           | IO43NB4F4       | U15           |

| IO10NB1F1/HCLKDN | C12           | IO27NB2F2      | J16           | IO43PB4F4       | T15           |

| IO10PB1F1/HCLKDP | C11           | IO27PB2F2      | H16           | IO44NB4F4       | U13           |

| IO11NB1F1        | A15           | IO28NB2F2      | J18           | IO44PB4F4       | U14           |

| IO11PB1F1        | A14           | IO28PB2F2      | H18           | IO45NB4F4       | V15           |

| IO12NB1F1        | B14           | IO29NB2F2      | K17           | IO45PB4F4       | V16           |

| IO12PB1F1        | B13           | IO29PB2F2      | J17           | IO46NB4F4       | V13           |

| IO13NB1F1        | A17           | Bank 3         |               | IO46PB4F4       | V14           |

| IO13PB1F1        | A16           | IO30NB3F3      | N18           | IO47NB4F4       | V12           |

| IO14NB1F1        | D13           | IO30PB3F3      | M18           | IO47PB4F4       | U12           |

| IO14PB1F1        | D12           | IO31NB3F3      | L18           | IO48NB4F4       | V10           |

| IO15NB1F1        | C14           | IO31PB3F3      | K18           | IO48PB4F4       | V11           |

| IO15PB1F1        | C13           | IO32NB3F3      | L16           | IO49NB4F4/CLKEN | T10           |

| IO16NB1F1        | B16           | IO32PB3F3      | L17           | IO49PB4F4/CLKEP | T11           |

# Note

Microsemi

Package Pin Assignments

| FG484          |            | FG48           | 4          | FG484          |            |  |

|----------------|------------|----------------|------------|----------------|------------|--|

| AX250 Function | Pin Number | AX250 Function | Pin Number | AX250 Function | Pin Number |  |

| IO104PB6F6     | N4         | IO122NB7F7     | G5         | GND            | J9         |  |

| IO105NB6F6     | M5         | IO122PB7F7     | G6         | GND            | K10        |  |

| IO105PB6F6     | N5         | IO123NB7F7     | F5         | GND            | K11        |  |

| IO106NB6F6     | M3         | IO123PB7F7     | E4         | GND            | K12        |  |

| IO106PB6F6     | N3         | Dedicate       | d I/O      | GND            | K13        |  |

| Bank           | 7          | VCCDA          | H7         | GND            | L1         |  |

| IO107NB7F7     | M2         | GND            | A1         | GND            | L10        |  |

| IO107PB7F7     | N1         | GND            | A11        | GND            | L11        |  |

| IO108NB7F7     | L3         | GND            | A12        | GND            | L12        |  |

| IO108PB7F7     | L2         | GND            | A2         | GND            | L13        |  |

| IO109NB7F7     | K2         | GND            | A21        | GND            | L22        |  |

| IO109PB7F7     | K1         | GND            | A22        | GND            | M1         |  |

| IO110NB7F7     | K5         | GND            | AA1        | GND            | M10        |  |

| IO110PB7F7     | L5         | GND            | AA2        | GND            | M11        |  |

| IO111NB7F7     | K6         | GND            | AA21       | GND            | M12        |  |

| IO111PB7F7     | L6         | GND            | AA22       | GND            | M13        |  |

| IO112NB7F7     | K4         | GND            | AB1        | GND            | M22        |  |

| IO112PB7F7     | K3         | GND            | AB11       | GND            | N10        |  |

| IO113NB7F7     | K7         | GND            | AB12       | GND            | N11        |  |

| IO113PB7F7     | L7         | GND            | AB2        | GND            | N12        |  |

| IO114NB7F7     | H1         | GND            | AB21       | GND            | N13        |  |

| IO114PB7F7     | J1         | GND            | AB22       | GND            | P14        |  |

| IO115NB7F7     | H2         | GND            | B1         | GND            | P9         |  |

| IO115PB7F7     | J2         | GND            | B2         | GND            | R15        |  |

| IO116NB7F7     | H4         | GND            | B21        | GND            | R8         |  |

| IO116PB7F7     | J4         | GND            | B22        | GND            | U16        |  |

| IO117NB7F7     | H5         | GND            | C20        | GND            | U6         |  |

| IO117PB7F7     | J5         | GND            | C3         | GND            | V18        |  |

| IO118NB7F7     | F2         | GND            | D19        | GND            | V5         |  |

| IO118PB7F7     | G2         | GND            | D4         | GND            | W19        |  |

| IO119NB7F7     | H6         | GND            | E18        | GND            | W4         |  |

| IO119PB7F7     | J6         | GND            | E5         | GND            | Y20        |  |

| IO120NB7F7     | F1         | GND            | G18        | GND            | Y3         |  |

| IO120PB7F7     | G1         | GND            | H15        | GND/LP         | G7         |  |

| IO121NB7F7     | F4         | GND            | H8         | NC             | A17        |  |

| IO121PB7F7     | G4         | GND            | J14        | NC             | A18        |  |

Package Pin Assignments

| FG484          |               | FG484          |               | FG484             |               |

|----------------|---------------|----------------|---------------|-------------------|---------------|

| AX500 Function | Pin<br>Number | AX500 Function | Pin<br>Number | AX500 Function    | Pin<br>Number |

| IO54PB2F5      | H22           | IO72PB3F6      | P20           | IO90NB4F8         | Y17           |

| IO55NB2F5      | L17           | IO73PB3F6      | R19           | IO90PB4F8         | Y18           |

| IO55PB2F5      | K17           | IO74NB3F7      | V21           | IO91NB4F8         | V15           |

| IO56NB2F5      | K21           | IO74PB3F7      | U21           | IO91PB4F8         | V16           |

| IO56PB2F5      | K22           | IO75NB3F7      | V22           | IO92PB4F8         | AB17          |

| IO58NB2F5      | L20           | IO75PB3F7      | U22           | IO93NB4F8         | Y15           |

| IO58PB2F5      | K20           | IO76NB3F7      | U20           | IO93PB4F8         | Y16           |

| IO59NB2F5      | L18           | IO76PB3F7      | T20           | IO94NB4F9         | AA16          |

| IO59PB2F5      | K18           | IO77NB3F7      | R17           | IO94PB4F9         | AA17          |

| IO60NB2F5      | M21           | IO77PB3F7      | P17           | IO95NB4F9         | AB14          |

| IO60PB2F5      | L21           | IO78NB3F7      | W21           | IO95PB4F9         | AB15          |

| IO61NB2F5      | L16           | IO78PB3F7      | W22           | IO96NB4F9         | W15           |

| IO61PB2F5      | K16           | IO79NB3F7      | T18           | IO96PB4F9         | W16           |

| IO62NB2F5      | M19           | IO79PB3F7      | R18           | IO97NB4F9         | AA13          |

| IO62PB2F5      | L19           | IO80NB3F7      | W20           | IO97PB4F9         | AB13          |

| Bank 3         | Bank 3        |                | V20           | IO98NB4F9         | AA14          |

| IO63NB3F6      | N16           | IO81NB3F7      | U19           | IO98PB4F9         | AA15          |

| IO63PB3F6      | M16           | IO81PB3F7      | T19           | IO100NB4F9        | Y14           |

| IO64NB3F6      | P22           | IO82NB3F7      | U18           | IO100PB4F9        | W14           |

| IO64PB3F6      | N22           | IO82PB3F7      | V19           | IO101NB4F9        | Y12           |

| IO65NB3F6      | N20           | IO83NB3F7      | R16           | IO101PB4F9        | Y13           |

| IO65PB3F6      | M20           | IO83PB3F7      | P16           | IO102NB4F9        | AA11          |

| IO66NB3F6      | P21           | Bank 4         | Bank 4        |                   | AA12          |

| IO66PB3F6      | N21           | IO84NB4F8      | AB18          | IO103NB4F9/CLKEN  | V12           |

| IO67NB3F6      | N18           | IO84PB4F8      | AB19          | IO103PB4F9/CLKEP  | V13           |

| IO67PB3F6      | N19           | IO85NB4F8      | T15           | IO104NB4F9/CLKFN  | W11           |

| IO68NB3F6      | T22           | IO85PB4F8      | T16           | IO104PB4F9/CLKFP  | W12           |

| IO68PB3F6      | R22           | IO86NB4F8      | AA18          | Bank 5            |               |

| IO69NB3F6      | N17           | IO86PB4F8      | AA19          | IO105NB5F10/CLKGN | U10           |

| IO69PB3F6      | M17           | IO87NB4F8      | W17           | IO105PB5F10/CLKGP | U11           |

| IO70NB3F6      | T21           | IO87PB4F8      | V17           | IO106NB5F10/CLKHN | V9            |

| IO70PB3F6      | R21           | IO88NB4F8      | Y19           | IO106PB5F10/CLKHP | V10           |

| IO71NB3F6      | P18           | IO88PB4F8      | W18           | IO107NB5F10       | Y10           |

| IO71PB3F6      | P19           | IO89NB4F8      | U14           | IO107PB5F10       | Y11           |

| IO72NB3F6      | R20           | IO89PB4F8      | U15           | IO108NB5F10       | AA9           |

Pin Number M8 Μ7 K4 L4 L6 M6 K5 L5 J4 J3 G2 H2 L8 L7 G3 H3 G4 H4 J6 K6 H5 J5 F2 F1 K8 K7 F4 F3 G6 H6 F5 G5 H7 J7

| FG896           |               | FG896           |               | FG896           |   |  |

|-----------------|---------------|-----------------|---------------|-----------------|---|--|

| AX1000 Function | Pin<br>Number | AX1000 Function | Pin<br>Number | AX1000 Function |   |  |

| IO206PB6F19     | AB4           | IO224NB6F20     | R2            | IO241NB7F22     |   |  |

| IO207NB6F19     | W6            | IO224PB6F20     | T2            | IO241PB7F22     |   |  |

| IO207PB6F19     | W7            | Bank 7          |               | IO242NB7F22     |   |  |

| IO208NB6F19     | AB3           | IO225NB7F21     | R7            | IO242PB7F22     |   |  |

| IO208PB6F19     | AC3           | IO225PB7F21     | R6            | IO243NB7F22     | Τ |  |

| IO209NB6F19     | V8            | IO226NB7F21     | R4            | IO243PB7F22     |   |  |

| IO209PB6F19     | V9            | IO226PB7F21     | R5            | IO244NB7F22     | Τ |  |

| IO210NB6F19     | AA2           | IO227NB7F21     | R8            | IO244PB7F22     |   |  |

| IO210PB6F19     | AA1           | IO227PB7F21     | R9            | IO245NB7F22     |   |  |

| IO211NB6F19     | V5            | IO228NB7F21     | P1            | IO245PB7F22     |   |  |

| IO211PB6F19     | W5            | IO228PB7F21     | R1            | IO246NB7F22     |   |  |

| IO212NB6F19     | Y3            | IO229NB7F21     | P9            | IO246PB7F22     |   |  |

| IO212PB6F19     | Y4            | IO229PB7F21     | P8            | IO247NB7F23     |   |  |

| IO213NB6F19     | V7            | IO230NB7F21     | N2            | IO247PB7F23     |   |  |

| IO213PB6F19     | V6            | IO230PB7F21     | P2            | IO248NB7F23     |   |  |

| IO214NB6F20     | W3            | IO231NB7F21     | P7            | IO248PB7F23     |   |  |

| IO214PB6F20     | W4            | IO231PB7F21     | P6            | IO249NB7F23     | Τ |  |

| IO215NB6F20     | U8            | IO232NB7F21     | N3            | IO249PB7F23     |   |  |

| IO215PB6F20     | U9            | IO232PB7F21     | P3            | IO250NB7F23     | Τ |  |

| IO216NB6F20     | W1            | IO233NB7F21     | P4            | IO250PB7F23     |   |  |

| IO216PB6F20     | W2            | IO233PB7F21     | P5            | IO251NB7F23     |   |  |

| IO217NB6F20     | U7            | IO234NB7F21     | L1            | IO251PB7F23     | Τ |  |

| IO217PB6F20     | U6            | IO234PB7F21     | M1            | IO252NB7F23     |   |  |

| IO218NB6F20     | U4            | IO235NB7F21     | M4            | IO252PB7F23     | Τ |  |

| IO218PB6F20     | V4            | IO235PB7F21     | N4            | IO253NB7F23     | Τ |  |

| IO219NB6F20     | T5            | IO236NB7F22     | N7            | IO253PB7F23     |   |  |

| IO219PB6F20     | U5            | IO236PB7F22     | N6            | IO254NB7F23     |   |  |

| IO220NB6F20     | U3            | IO237NB7F22     | N8            | IO254PB7F23     |   |  |

| IO220PB6F20     | V3            | IO237PB7F22     | N9            | IO255NB7F23     | Τ |  |

| IO221NB6F20     | Т8            | IO238NB7F22     | M5            | IO255PB7F23     |   |  |

| IO221PB6F20     | Т9            | IO238PB7F22     | N5            | IO256NB7F23     |   |  |

| IO222NB6F20     | U2            | IO239NB7F22     | L2            | IO256PB7F23     | Γ |  |

| IO222PB6F20     | V2            | IO239PB7F22     | M2            | IO257NB7F23     | Ι |  |

| IO223NB6F20     | T7            | IO240NB7F22     | L3            | IO257PB7F23     |   |  |

| IO223PB6F20     | T6            | IO240PB7F22     | M3            | Dedicated I/    | 0 |  |

Package Pin Assignments

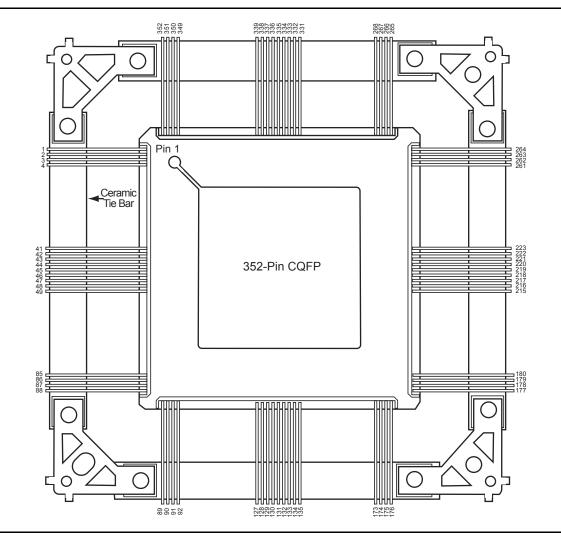

# CQ352

# Note

| CQ352          |               | CQ352          |               | CQ352          |               |

|----------------|---------------|----------------|---------------|----------------|---------------|

| AX500 Function | Pin<br>Number | AX500 Function | Pin<br>Number | AX500 Function | Pin<br>Number |

| GND            | 21            | GND            | 240           | TDI            | 348           |

| GND            | 27            | GND            | 246           | TDO            | 347           |

| GND            | 33            | GND            | 252           | TMS            | 350           |

| GND            | 39            | GND            | 258           | TRST           | 351           |

| GND            | 45            | GND            | 264           | VCCA           | 3             |

| GND            | 51            | GND            | 265           | VCCA           | 14            |

| GND            | 57            | GND            | 274           | VCCA           | 32            |

| GND            | 63            | GND            | 280           | VCCA           | 56            |

| GND            | 69            | GND            | 286           | VCCA           | 74            |

| GND            | 75            | GND            | 292           | VCCA           | 87            |

| GND            | 81            | GND            | 298           | VCCA           | 102           |

| GND            | 88            | GND            | 310           | VCCA           | 114           |

| GND            | 89            | GND            | 322           | VCCA           | 150           |

| GND            | 97            | GND            | 330           | VCCA           | 162           |

| GND            | 103           | GND            | 334           | VCCA           | 175           |

| GND            | 109           | GND            | 340           | VCCA           | 191           |

| GND            | 115           | GND            | 345           | VCCA           | 209           |

| GND            | 121           | GND/LP         | 352           | VCCA           | 233           |

| GND            | 133           | NC             | 91            | VCCA           | 251           |

| GND            | 145           | NC             | 117           | VCCA           | 263           |

| GND            | 151           | NC             | 130           | VCCA           | 279           |

| GND            | 157           | NC             | 131           | VCCA           | 291           |

| GND            | 163           | NC             | 148           | VCCA           | 329           |

| GND            | 169           | NC             | 174           | VCCA           | 339           |

| GND            | 176           | NC             | 268           | VCCDA          | 2             |

| GND            | 177           | NC             | 294           | VCCDA          | 44            |

| GND            | 186           | NC             | 307           | VCCDA          | 90            |

| GND            | 192           | NC             | 308           | VCCDA          | 116           |

| GND            | 198           | NC             | 327           | VCCDA          | 132           |

| GND            | 204           | NC             | 328           | VCCDA          | 149           |

| GND            | 210           | PRA            | 312           | VCCDA          | 178           |

| GND            | 216           | PRB            | 311           | VCCDA          | 221           |

| GND            | 222           | PRC            | 135           | VCCDA          | 266           |

| GND            | 228           | PRD            | 134           | VCCDA          | 293           |

| GND            | 234           | ТСК            | 349           | VCCDA          | 309           |

Datasheet Information

| Revision                   | Changes                                                                                                                                                                      | Page                               |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| Revision 10<br>(continued) | The "TRST" section was updated.                                                                                                                                              | 2-107                              |

|                            | The "Global Set Fuse" section was added.                                                                                                                                     | 2-109                              |

|                            | A footnote was added to "FG896" for the AX2000 regarding pins AB1, AE2, G1, and K2.                                                                                          | 3-52                               |

|                            | Pinouts for the AX250, AX500, and AX1000 were added for "CQ352".                                                                                                             | 3-98                               |

|                            | Pinout for the AX1000 was added for "CG624".                                                                                                                                 | 3-115                              |

| Revision 9                 | Table 2-79 was updated.                                                                                                                                                      | 2-69                               |

| (v2.1)                     | The "Low Power Mode" section was updated.                                                                                                                                    | 2-106                              |

| Revision 8<br>(v2.0)       | Table 1 has been updated.                                                                                                                                                    | i                                  |

|                            | The "Ordering Information" section has been updated.                                                                                                                         | ii                                 |

|                            | The "Device Resources" section has been updated.                                                                                                                             | ii                                 |

|                            | The "Temperature Grade Offerings" section is new.                                                                                                                            | iii                                |

|                            | The "Speed Grade and Temperature Grade Matrix" section has been updated.                                                                                                     | iii                                |

|                            | Table 2-9 has been updated.                                                                                                                                                  | 2-12                               |

|                            | Table 2-10 has been updated.                                                                                                                                                 | 2-12                               |

|                            | Table 2-1 has been updated.                                                                                                                                                  | 2-1                                |

|                            | Table 2-2 has been updated.                                                                                                                                                  | 2-1                                |

|                            | Table 2-3 has been updated.                                                                                                                                                  | 2-2                                |

|                            | Table 2-4 has been updated.                                                                                                                                                  | 2-3                                |

|                            | Table 2-5 has been updated.                                                                                                                                                  | 2-4                                |

|                            | The "Power Estimation Example" section has been updated.                                                                                                                     | 2-5                                |

|                            | The "Thermal Characteristics" section has been updated.                                                                                                                      | 2-6                                |

|                            | The "Package Thermal Characteristics" section has been updated.                                                                                                              | 2-6                                |

|                            | The "Timing Characteristics" section has been updated.                                                                                                                       | 2-7                                |

|                            | The "Pin Descriptions" section has been updated.                                                                                                                             | 2-9                                |

|                            | Timing numbers have been updated from the "3.3 V LVTTL" section to the "Timing Characteristics" section. Many AC Loads were updated as well.                                 | 2-25 to 2-59                       |

|                            | Timing characteristics for the "Hardwired Clocks" and "Routed Clocks" sections were updated.                                                                                 | 2-66, 2-68                         |

|                            | Table 2-89 to Table 2-92 and Table 2-98 to Table 2-99 were updated.                                                                                                          | 2-90 to 2-93,<br>2-102 to<br>2-103 |

|                            | The following sections were updated:<br>"Low Power Mode", "Interface", "Data Registers (DRs)", "Security", "Silicon<br>Explorer II Probe Interface", and "Programming"       | 2-106 to<br>2-110                  |

|                            | In the "PQ208" (AX500) section, pins 2, 52, and 156 changed from V <sub>CCDA</sub> to V <sub>CCA</sub> . For pins 170 and 171, the I/O names refer to pair 23 instead of 24. | 3-84                               |