Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                                   |

|--------------------------------|--------------------------------------------------------------------------|

| Number of LABs/CLBs            | 32256                                                                    |

| Number of Logic Elements/Cells | -                                                                        |

| Total RAM Bits                 | 294912                                                                   |

| Number of I/O                  | 586                                                                      |

| Number of Gates                | 200000                                                                   |

| Voltage - Supply               | 1.425V ~ 1.575V                                                          |

| Mounting Type                  | Surface Mount                                                            |

| Operating Temperature          | -55°C ~ 125°C (TA)                                                       |

| Package / Case                 | 896-BGA                                                                  |

| Supplier Device Package        | 896-FBGA (31x31)                                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/ax2000-1fg896m |

|                                |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

General Description

#### Figure 1-2 • Axcelerator Family Interconnect Elements

# **Logic Modules**

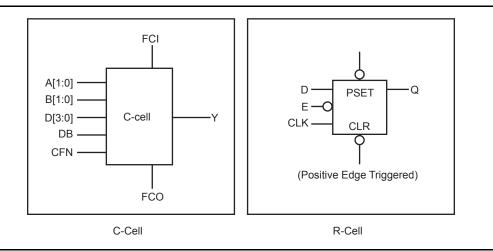

Microsemi's Axcelerator family provides two types of logic modules: the register cell (R-cell) and the combinatorial cell (C-cell). The Axcelerator device can implement more than 4,000 combinatorial functions of up to five inputs (Figure 1-3).

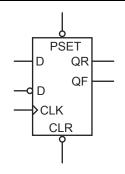

The R-cell contains a flip-flop featuring asynchronous clear, asynchronous preset, and active-low enable control signals (Figure 1-3). The R-cell registers feature programmable clock polarity selectable on a register-by-register basis. This provides additional flexibility (e.g., easy mapping of dual-data-rate functions into the FPGA) while conserving valuable clock resources. The clock source for the R-cell can be chosen from the hardwired clocks, routed clocks, or internal logic.

# **Timing Model**

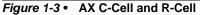

Note: Worst case timing data for the AX1000, -2 speed grade

#### Figure 2-1 • Worst Case Timing Data

### Hardwired Clock – Using LVTTL 24 mA High Slew Clock I/O

External Setup

=  $(t_{DP} + t_{RD2} + t_{SUD}) - t_{HCKL}$ = (1.72 + 0.53 + 0.23) - 3.02 = -0.54 ns Clock-to-Out (Pad-to-Pad)

=  $t_{HCKL} + t_{RCO} + t_{RD1} + t_{PY}$ = 3.02 + 0.67 + 0.45 + 2.99 = 7.13 ns

## Routed Clock – Using LVTTL 24 mA High Slew Clock I/O

External Setup

$= (t_{DP} + t_{RD2} + t_{SUD}) - t_{RCKH}$ = (1.72 + 0.53 + 0.23) - 3.13 = -0.65 ns Clock-to-Out (Pad-to-Pad) = t\_{RCKH} + t\_{RCO} + t\_{RD1} + t\_{PY} = 3.13 + 0.67 + 0.45 + 3.03 = 7.24 ns

### Using the Differential I/O Standards

Differential I/O macros should be instantiated in the netlist. The settings for these I/O standards cannot be changed inside Designer. Note that there are no tristated or bidirectional I/O buffers for differential standards.

#### Using the Voltage-Referenced I/O Standards

Using these I/O standards is similar to that of single-ended I/O standards. Their settings can be changed in Designer.

### Using DDR (Double Data Rate)

In Double Data Rate mode, new data is present on every transition of the clock signal. Clock and data lines have identical bandwidth and signal integrity requirements, making it very efficient for implementing very high-speed systems.

To implement a DDR, users need to:

- 1. Instantiate an input buffer (with the required I/O standard)

- 2. Instantiate the DDR\_REG macro (Figure 2-6)

- 3. Connect the output from the Input buffer to the input of the DDR macro

Figure 2-6 • DDR Register

### Macros for Specific I/O Standards

There are different macro types for any I/O standard or feature that determine the required VCCI and VREF voltages for an I/O. The generic buffer macros require the LVTTL standard with slow slew rate and 24 mA-drive strength. LVTTL can support high slew rate but this should only be used for critical signals.

Most of the macro symbols represent variations of the six generic symbol types:

- CLKBUF: Clock Buffer

- HCLKBUF: Hardwired Clock Buffer

- INBUF: Input Buffer

- OUTBUF: Output Buffer

- TRIBUF: Tristate Buffer

- BIBUF: Bidirectional Buffer

Other macros include the following:

- Differential I/O standard macros: The LVDS and LVPECL macros either have a pair of differential inputs (e.g. INBUF\_LVDS) or a pair of differential outputs (e.g. OUTBUF\_LVPECL).

- Pull-up and pull-down variations of the INBUF, BIBUF, and TRIBUF macros. These are available only with TTL and LVCMOS thresholds. They can be used to model the behavior of the pull-up and pull-down resistors available in the architecture. Whenever an input pin is left unconnected, the output pin will either go high or low rather than unknown. This allows users to leave inputs unconnected without having the negative effect on simulation of propagating unknowns.

- DDR\_REG macro. It can be connected to any I/O standard input buffers (i.e. INBUF) to implement a double data rate register. Designer software will map it to the I/O module in the same way it maps the other registers to the I/O module.

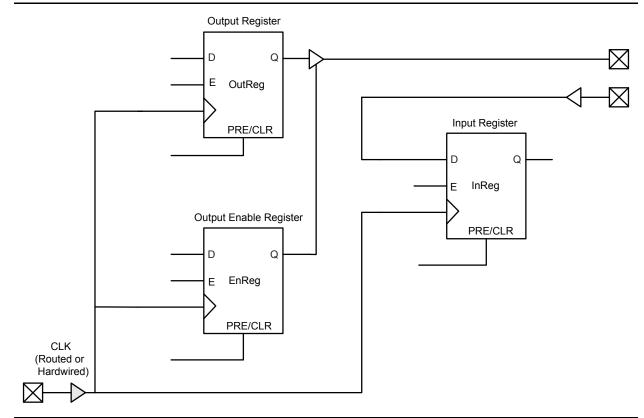

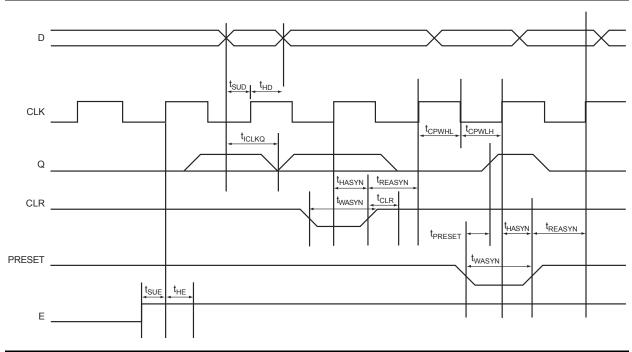

# **I/O Module Timing Characteristics**

Figure 2-11 • Timing Model

# SSTL3

Stub Series Terminated Logic for 3.3 V is a general-purpose 3.3 V memory bus standard (JESD8-8). The Axcelerator devices support both classes of this standard. This requires a differential amplifier input buffer and a push-pull output buffer.

#### Class I

Table 2-50 • DC Input and Output Levels

|         | VIL        | VIF       | 1       | VOL        | VOH        | IOL | IOH |

|---------|------------|-----------|---------|------------|------------|-----|-----|

| Min., V | Max., V    | Min., V   | Max., V | Max., V    | Min., V    | mA  | mA  |

| -0.3    | VREF – 0.2 | VREF +0.2 | 3.6     | VREF – 0.6 | VREF + 0.6 | 8   | -8  |

# AC Loadings

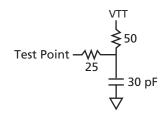

#### Figure 2-23 • AC Test Loads

Table 2-51 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | VREF (typ) (V) | C <sub>load</sub> (pF) |

|---------------|----------------|----------------------|----------------|------------------------|

| VREF – 1.0    | VREF + 1.0     | VREF                 | 1.50           | 30                     |

*Note:* \**Measuring Point* = *VTRIP*

### Timing Characteristics

#### Table 2-52 • 3.3 V SSTL3 Class I I/O Module

#### Worst-Case Commercial Conditions VCCA = 1.425 V, VCCI = 3.0 V, T<sub>J</sub> = $70^{\circ}$ C

|                     |                                                                    | –2 S | peed | –1 S | peed | Std S | Speed |       |

|---------------------|--------------------------------------------------------------------|------|------|------|------|-------|-------|-------|

| Parameter           | Description                                                        | Min. | Max. | Min. | Max. | Min.  | Max.  | Units |

| 3.3 V SSTL3         | Class I I/O Module Timing                                          |      |      |      |      |       |       |       |

| t <sub>DP</sub>     | Input Buffer                                                       |      | 1.78 |      | 2.03 |       | 2.39  | ns    |

| t <sub>PY</sub>     | Output Buffer                                                      |      | 2.17 |      | 2.47 |       | 2.91  | ns    |

| t <sub>ICLKQ</sub>  | Clock-to-Q for the I/O input register                              |      | 0.67 |      | 0.77 |       | 0.90  | ns    |

| t <sub>oclka</sub>  | Clock-to-Q for the I/O output register and the I/O enable register |      | 0.67 |      | 0.77 |       | 0.90  | ns    |

| t <sub>SUD</sub>    | Data Input Set-Up                                                  |      | 0.23 |      | 0.27 |       | 0.31  | ns    |

| t <sub>SUE</sub>    | Enable Input Set-Up                                                |      | 0.26 |      | 0.30 |       | 0.35  | ns    |

| t <sub>HD</sub>     | Data Input Hold                                                    |      | 0.00 |      | 0.00 |       | 0.00  | ns    |

| t <sub>HE</sub>     | Enable Input Hold                                                  |      | 0.00 |      | 0.00 |       | 0.00  | ns    |

| t <sub>CPWHL</sub>  | Clock Pulse Width High to Low                                      | 0.39 |      | 0.39 |      | 0.39  |       | ns    |

| t <sub>CPWLH</sub>  | Clock Pulse Width Low to High                                      | 0.39 |      | 0.39 |      | 0.39  |       | ns    |

| t <sub>WASYN</sub>  | Asynchronous Pulse Width                                           | 0.37 |      | 0.37 |      | 0.37  |       | ns    |

| t <sub>REASYN</sub> | Asynchronous Recovery Time                                         |      | 0.13 |      | 0.15 |       | 0.17  | ns    |

| t <sub>HASYN</sub>  | Asynchronous Removal Time                                          |      | 0.00 |      | 0.00 |       | 0.00  | ns    |

| t <sub>CLR</sub>    | Asynchronous Clear-to-Q                                            |      | 0.23 |      | 0.27 |       | 0.31  | ns    |

| t <sub>PRESET</sub> | Asynchronous Preset-to-Q                                           |      | 0.23 |      | 0.27 |       | 0.31  | ns    |

# **Module Specifications**

# **C-Cell**

#### Introduction

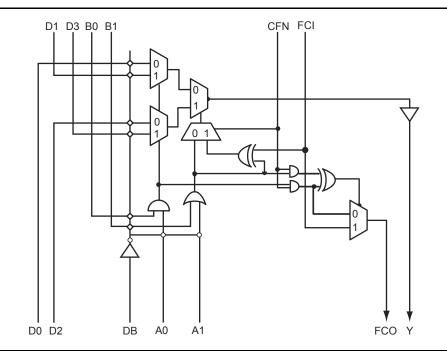

The C-cell is one of the two logic module types in the AX architecture. It is the combinatorial logic resource in the Axcelerator device. The AX architecture implements a new combinatorial cell that is an extension of the C-cell implemented in the SX-A family. The main enhancement of the new C-cell is the addition of carry-chain logic.

The C-cell can be used in a carry-chain mode to construct arithmetic functions. If carry-chain logic is not required, it can be disabled.

The C-cell features the following (Figure 2-27):

- Eight-input MUX (data: D0-D3, select: A0, A1, B0, B1). User signals can be routed to any one of these inputs. Any of the C-cell inputs (D0-D3, A0, A1, B0, B1) can be tied to one of the four routed clocks (CLKE/F/G/H).

- Inverter (DB input) can be used to drive a complement signal of any of the inputs to the C-cell.

- A carry input and a carry output. The carry input signal of the C-cell is the carry output from the C-cell directly to the north.

- · Carry connect for carry-chain logic with a signal propagation time of less than 0.1 ns.

- A hardwired connection (direct connect) to the adjacent R-cell (Register Cell) for all C-cells on the east side of a SuperCluster with a signal propagation time of less than 0.1 ns.

This layout of the C-cell (and the C-cell Cluster) enables the implementation of over 4,000 functions of up to five bits. For example, two C-cells can be used together to implement a four-input XOR function in a single cell delay.

The carry-chain configuration is handled automatically for the user with Microsemi's extensive macro library (please see the *Antifuse Macro Library Guide* for a complete listing of available Axcelerator macros).

Figure 2-27 • C-Cell

# **Timing Characteristics**

Table 2-65 • AX125 Predicted Routing Delays Worst-Case Commercial Conditions VCCA = 1.425 V, T<sub>J</sub> = 70°C

|                   |                                  | -2 Speed | -1 Speed | Std Speed |       |

|-------------------|----------------------------------|----------|----------|-----------|-------|

| Parameter         | Description                      | Typical  | Typical  | Typical   | Units |

| Predicted R       | Routing Delays                   |          |          |           |       |

| t <sub>DC</sub>   | DirectConnect Routing Delay, FO1 | 0.11     | 0.12     | 0.15      | ns    |

| t <sub>FC</sub>   | FastConnect Routing Delay, FO1   | 0.35     | 0.39     | 0.46      | ns    |

| t <sub>RD1</sub>  | Routing delay for FO1            | 0.35     | 0.40     | 0.47      | ns    |

| t <sub>RD2</sub>  | Routing delay for FO2            | 0.38     | 0.43     | 0.51      | ns    |

| t <sub>RD3</sub>  | Routing delay for FO3            | 0.43     | 0.48     | 0.57      | ns    |

| t <sub>RD4</sub>  | Routing delay for FO4            | 0.48     | 0.55     | 0.64      | ns    |

| t <sub>RD5</sub>  | Routing delay for FO5            | 0.55     | 0.62     | 0.73      | ns    |

| t <sub>RD6</sub>  | Routing delay for FO6            | 0.64     | 0.72     | 0.85      | ns    |

| t <sub>RD7</sub>  | Routing delay for FO7            | 0.79     | 0.89     | 1.05      | ns    |

| t <sub>RD8</sub>  | Routing delay for FO8            | 0.88     | 0.99     | 1.17      | ns    |

| t <sub>RD16</sub> | Routing delay for FO16           | 1.49     | 1.69     | 1.99      | ns    |

| t <sub>RD32</sub> | Routing delay for FO32           | 2.32     | 2.63     | 3.10      | ns    |

# Table 2-66 • AX250 Predicted Routing Delays

# Worst-Case Commercial Conditions VCCA = $1.425 \text{ V}, \text{ T}_{\text{J}} = 70^{\circ}\text{C}$

|                   |                                  | -2 Speed | -1 Speed | Std Speed |       |

|-------------------|----------------------------------|----------|----------|-----------|-------|

| Parameter         | Description                      | Typical  | Typical  | Typical   | Units |

| Predicted F       | Routing Delays                   |          |          |           |       |

| t <sub>DC</sub>   | DirectConnect Routing Delay, FO1 | 0.11     | 0.12     | 0.15      | ns    |

| t <sub>FC</sub>   | FastConnect Routing Delay, FO1   | 0.35     | 0.39     | 0.46      | ns    |

| t <sub>RD1</sub>  | Routing delay for FO1            | 0.39     | 0.45     | 0.53      | ns    |

| t <sub>RD2</sub>  | Routing delay for FO2            | 0.41     | 0.46     | 0.54      | ns    |

| t <sub>RD3</sub>  | Routing delay for FO3            | 0.48     | 0.55     | 0.64      | ns    |

| t <sub>RD4</sub>  | Routing delay for FO4            | 0.56     | 0.63     | 0.75      | ns    |

| t <sub>RD5</sub>  | Routing delay for FO5            | 0.60     | 0.68     | 0.80      | ns    |

| t <sub>RD6</sub>  | Routing delay for FO6            | 0.84     | 0.96     | 1.13      | ns    |

| t <sub>RD7</sub>  | Routing delay for FO7            | 0.90     | 1.02     | 1.20      | ns    |

| t <sub>RD8</sub>  | Routing delay for FO8            | 1.00     | 1.13     | 1.33      | ns    |

| t <sub>RD16</sub> | Routing delay for FO16           | 2.17     | 2.46     | 2.89      | ns    |

| t <sub>RD32</sub> | Routing delay for FO32           | 3.55     | 4.03     | 4.74      | ns    |

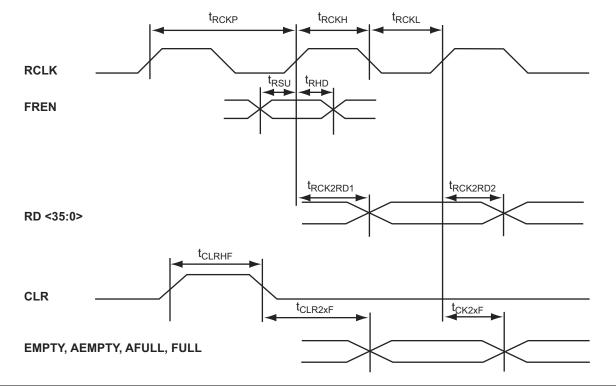

#### Table 2-93 • Sixteen RAM Blocks Cascaded

#### Worst-Case Commercial Conditions VCCA = 1.425 V, VCCI = 3.0 V, T<sub>J</sub> = 70°C

|                      |                               | –2 S  | peed  | –1 S  | peed  | Std S | peed  |       |

|----------------------|-------------------------------|-------|-------|-------|-------|-------|-------|-------|

| Parameter            | Description                   | Min.  | Max.  | Min.  | Max.  | Min.  | Max.  | Units |

| Write Mode           |                               |       |       |       |       |       |       |       |

| t <sub>WDASU</sub>   | Write Data Setup vs. WCLK     |       | 16.54 |       | 18.84 |       | 22.15 | ns    |

| t <sub>WDAHD</sub>   | Write Data Hold vs. WCLK      |       | 0.00  |       | 0.00  |       | 0.00  | ns    |

| t <sub>WADSU</sub>   | Write Address Setup vs. WCLK  |       | 16.54 |       | 18.84 |       | 22.15 | ns    |

| t <sub>WADHD</sub>   | Write Address Hold vs. WCLK   |       | 0.00  |       | 0.00  |       | 0.00  | ns    |

| t <sub>WENSU</sub>   | Write Enable Setup vs. WCLK   |       | 16.54 |       | 18.84 |       | 22.15 | ns    |

| t <sub>WENHD</sub>   | Write Enable Hold vs. WCLK    |       | 0.00  |       | 0.00  |       | 0.00  | ns    |

| t <sub>wcкн</sub>    | WCLK Minimum High Pulse Width | 0.75  |       | 0.75  |       | 0.75  |       | ns    |

| t <sub>WCLK</sub>    | WCLK Minimum Low Pulse Width  | 13.40 |       | 13.40 |       | 13.40 |       | ns    |

| t <sub>WCKP</sub>    | WCLK Minimum Period           | 14.15 |       | 14.15 |       | 14.15 |       | ns    |

| Read Mode            |                               |       |       |       |       |       |       |       |

| t <sub>RADSU</sub>   | Read Address Setup vs. RCLK   |       | 18.13 |       | 20.65 |       | 24.27 | ns    |

| t <sub>RADHD</sub>   | Read Address Hold vs. RCLK    |       | 0.00  |       | 0.00  |       | 0.00  | ns    |

| t <sub>RENSU</sub>   | Read Enable Setup vs. RCLK    |       | 18.13 |       | 20.65 |       | 24.27 | ns    |

| t <sub>RENHD</sub>   | Read Enable Hold vs. RCLK     |       | 0.00  |       | 0.00  |       | 0.00  | ns    |

| t <sub>RCK2RD1</sub> | RCLK-To-OUT (Pipelined)       |       | 12.08 |       | 13.76 |       | 16.17 | ns    |

| t <sub>RCK2RD2</sub> | RCLK-To-OUT (Non-Pipelined)   |       | 12.83 |       | 14.62 |       | 17.18 | ns    |

| t <sub>RCLKH</sub>   | RCLK Minimum High Pulse Width | 0.73  |       | 0.73  |       | 0.73  |       | ns    |

| t <sub>RCLKL</sub>   | RCLK Minimum Low Pulse Width  | 14.41 |       | 14.41 |       | 14.41 |       | ns    |

| t <sub>RCKP</sub>    | RCLK Minimum Period           | 15.14 |       | 15.14 |       | 15.14 |       | ns    |

Note: Timing data for these sixteen cascaded RAM blocks uses a depth of 65,536. For all other combinations, use Microsemi's timing software.

Figure 2-68 • FIFO Read Timing

# Microsemi

| BG729           |               | BG729           |               | BG729             |               |

|-----------------|---------------|-----------------|---------------|-------------------|---------------|

| AX1000 Function | Pin<br>Number | AX1000 Function | Pin<br>Number | AX1000 Function   | Pin<br>Number |

| IO109NB3F10     | V24           | IO127PB3F11     | AC27          | IO145PB4F13       | AD19          |

| IO109PB3F10     | V25           | IO128NB3F11     | Y20           | IO146NB4F13       | AC18          |

| IO110NB3F10     | T20           | IO128PB3F11     | W19           | IO146PB4F13       | AB18          |

| IO110PB3F10     | T21           | Bank 4          | <b>.</b>      | IO147NB4F13       | Y17           |

| IO111NB3F10     | W26           | IO129NB4F12     | AA20          | IO147PB4F13       | AA17          |

| IO111PB3F10     | W27           | IO129PB4F12     | Y21           | IO148NB4F13       | AF19          |

| IO112NB3F10     | U22           | IO130NB4F12     | AB22          | IO148PB4F13       | AF20          |

| IO112PB3F10     | U23           | IO130PB4F12     | AB23          | IO149NB4F13       | AC17          |

| IO113NB3F10     | Y26           | IO131NB4F12     | AC22          | IO149PB4F13       | AB17          |

| IO113PB3F10     | Y27           | IO131PB4F12     | AC23          | IO150NB4F13       | AE18          |

| IO114NB3F10     | U20           | IO132NB4F12     | AD23          | IO150PB4F13       | AE19          |

| IO114PB3F10     | U21           | IO132PB4F12     | AD24          | IO151NB4F13       | AA16          |

| IO115NB3F10     | W24           | IO133NB4F12     | AF23          | IO151PB4F13       | Y16           |

| IO115PB3F10     | W25           | IO133PB4F12     | AE23          | IO152NB4F14       | AG18          |

| IO116NB3F10     | V22           | IO134NB4F12     | AC21          | IO152PB4F14       | AG19          |

| IO116PB3F10     | V23           | IO134PB4F12     | AB21          | IO153NB4F14       | AC16          |

| IO117NB3F10     | Y24           | IO135NB4F12     | AC20          | IO153PB4F14       | AB16          |

| IO117PB3F10     | Y25           | IO135PB4F12     | AB20          | IO154NB4F14       | AF17          |

| IO118NB3F11     | V20           | IO136NB4F12     | AD21          | IO154PB4F14       | AF18          |

| IO118PB3F11     | V21           | IO136PB4F12     | AD22          | IO155NB4F14       | AB15          |

| IO119NB3F11     | AA26          | IO137NB4F12     | Y19           | IO155PB4F14       | AC15          |

| IO119PB3F11     | AA27          | IO137PB4F12     | AA19          | IO156NB4F14       | AE16          |

| IO120NB3F11     | W22           | IO138NB4F12     | AE21          | IO156PB4F14       | AE17          |

| IO120PB3F11     | W23           | IO138PB4F12     | AE22          | IO157NB4F14       | Y15           |

| IO121NB3F11     | AA24          | IO139NB4F13     | AF21          | IO157PB4F14       | AA15          |

| IO121PB3F11     | AA25          | IO139PB4F13     | AF22          | IO158NB4F14       | AG16          |

| IO122NB3F11     | W20           | IO140NB4F13     | AG22          | IO158PB4F14       | AG17          |

| IO122PB3F11     | W21           | IO140PB4F13     | AG23          | IO159NB4F14/CLKEN | AF15          |

| IO123NB3F11     | AB26          | IO141NB4F13     | Y18           | IO159PB4F14/CLKEP | AF16          |

| IO123PB3F11     | AB27          | IO141PB4F13     | AA18          | IO160NB4F14/CLKFN | AD14          |

| IO124NB3F11     | Y22           | IO142NB4F13     | AE20          | IO160PB4F14/CLKFP | AD15          |

| IO124PB3F11     | Y23           | IO142PB4F13     | AD20          | Bank 5            |               |

| IO125NB3F11     | AB24          | IO143NB4F13     | AG20          | IO161NB5F15/CLKGN | AE14          |

| IO125PB3F11     | AB25          | IO143PB4F13     | AG21          | IO161PB5F15/CLKGP | AE15          |

| IO126NB3F11     | AA22          | IO144NB4F13     | AC19          | IO162NB5F15/CLKHN | AC13          |

| IO126PB3F11     | AA23          | IO144PB4F13     | AB19          | IO162PB5F15/CLKHP | AD13          |

| IO127NB3F11     | AC26          | IO145NB4F13     | AD18          | IO163NB5F15       | Y14           |

# Microsemi

| BG729           |               | BG729           |               |  |  |  |

|-----------------|---------------|-----------------|---------------|--|--|--|

| AX1000 Function | Pin<br>Number | AX1000 Function | Pin<br>Number |  |  |  |

| VCCIB0          | B4            | VCCIB4          | W17           |  |  |  |

| VCCIB0          | C4            | VCCIB4          | W18           |  |  |  |

| VCCIB0          | J10           | VCCIB5          | AE4           |  |  |  |

| VCCIB0          | J11           | VCCIB5          | AF4           |  |  |  |

| VCCIB0          | J12           | VCCIB5          | AG4           |  |  |  |

| VCCIB0          | K12           | VCCIB5          | V12           |  |  |  |

| VCCIB0          | K13           | VCCIB5          | V13           |  |  |  |

| VCCIB1          | A24           | VCCIB5          | W10           |  |  |  |

| VCCIB1          | B24           | VCCIB5          | W11           |  |  |  |

| VCCIB1          | C24           | VCCIB5          | W12           |  |  |  |

| VCCIB1          | J16           | VCCIB6          | AD1           |  |  |  |

| VCCIB1          | J17           | VCCIB6          | AD2           |  |  |  |

| VCCIB1          | J18           | VCCIB6          | AD3           |  |  |  |

| VCCIB1          | K15           | VCCIB6          | R10           |  |  |  |

| VCCIB1          | K16           | VCCIB6          | T10           |  |  |  |

| VCCIB2          | D25           | VCCIB6          | Т9            |  |  |  |

| VCCIB2          | D26           | VCCIB6          | U9            |  |  |  |

| VCCIB2          | D27           | VCCIB6          | V9            |  |  |  |

| VCCIB2          | K19           | VCCIB7          | D1            |  |  |  |

| VCCIB2          | L19           | VCCIB7          | D2            |  |  |  |

| VCCIB2          | M18           | VCCIB7          | D3            |  |  |  |

| VCCIB2          | M19           | VCCIB7          | K9            |  |  |  |

| VCCIB2          | N18           | VCCIB7          | L9            |  |  |  |

| VCCIB3          | AD25          | VCCIB7          | M10           |  |  |  |

| VCCIB3          | AD26          | VCCIB7          | M9            |  |  |  |

| VCCIB3          | AD27          | VCCIB7          | N10           |  |  |  |

| VCCIB3          | R18           | VCOMPLA         | B13           |  |  |  |

| VCCIB3          | T18           | VCOMPLB         | A14           |  |  |  |

| VCCIB3          | T19           | VCOMPLC         | A15           |  |  |  |

| VCCIB3          | U19           | VCOMPLD         | J15           |  |  |  |

| VCCIB3          | V19           | VCOMPLE         | AG15          |  |  |  |

| VCCIB4          | AE24          | VCOMPLF         | W15           |  |  |  |

| VCCIB4          | AF24          | VCOMPLG         | AC14          |  |  |  |

| VCCIB4          | AG24          | VCOMPLH         | W13           |  |  |  |

| VCCIB4          | V15           | VPUMP           | D24           |  |  |  |

| VCCIB4          | V16           |                 |               |  |  |  |

| VCCIB4          | W16           |                 |               |  |  |  |

| FG256-Pin F       | BGA           | FG256-Pin FBGA |               |  |  |

|-------------------|---------------|----------------|---------------|--|--|

| AX125 Function    | Pin<br>Number | AX125 Function | Pin<br>Number |  |  |

| VCCA              | L10           | VCCIB4         | M11           |  |  |

| VCCA              | L7            | VCCIB4         | M9            |  |  |

| VCCA              | L8            | VCCIB5         | M6            |  |  |

| VCCA              | L9            | VCCIB5         | M7            |  |  |

| VCCA              | N3            | VCCIB5         | M8            |  |  |

| VCCA              | P14           | VCCIB6         | J5            |  |  |

| VCCPLA            | C7            | VCCIB6         | K5            |  |  |

| VCCPLB            | D6            | VCCIB6         | L5            |  |  |

| VCCPLC            | A10           | VCCIB7         | F5            |  |  |

| VCCPLD            | D10           | VCCIB7         | G5            |  |  |

| VCCPLE            | P10           | VCCIB7         | H5            |  |  |

| VCCPLF            | N11           | VCOMPLA        | A7            |  |  |

| VCCPLG            | T7            | VCOMPLB        | D7            |  |  |

| VCCPLH            | N7            | VCOMPLC        | B9            |  |  |

| VCCDA             | A2            | VCOMPLD        | D11           |  |  |

| VCCDA             | C13           | VCOMPLE        | T10           |  |  |

| VCCDA             | D9            | VCOMPLF        | N10           |  |  |

| V <sub>CCDA</sub> | H1            | VCOMPLG        | R8            |  |  |

| VCCDA             | J15           | VCOMPLH        | N6            |  |  |

| VCCDA             | N14           | VPUMP          | A14           |  |  |

| VCCDA             | N8            |                |               |  |  |

| VCCDA             | P4            |                |               |  |  |

| VCCIB0            | E6            |                |               |  |  |

| VCCIB0            | E7            |                |               |  |  |

| VCCIB0            | E8            |                |               |  |  |

| VCCIB1            | E10           |                |               |  |  |

| VCCIB1            | E11           |                |               |  |  |

| VCCIB1            | E9            |                |               |  |  |

| VCCIB2            | F12           |                |               |  |  |

| VCCIB2            | G12           |                |               |  |  |

| VCCIB2            | H12           |                |               |  |  |

| VCCIB3            | J12           |                |               |  |  |

| VCCIB3            | K12           |                |               |  |  |

| VCCIB3            | L12           |                |               |  |  |

| VCCIB4            | M10           |                |               |  |  |

| FG324          |               | FG324          |               | FG324          | FG324         |  |  |

|----------------|---------------|----------------|---------------|----------------|---------------|--|--|

| AX125 Function | Pin<br>Number | AX125 Function | Pin<br>Number | AX125 Function | Pin<br>Number |  |  |

| GND            | R4            | NC             | N4            | VCCA           | M8            |  |  |

| GND            | T16           | NC             | N5            | VCCA           | M9            |  |  |

| GND            | Т3            | NC             | R12           | VCCA           | P4            |  |  |

| GND            | U17           | NC             | R13           | VCCA           | R15           |  |  |

| GND            | U2            | NC             | R6            | VCCPLA         | D8            |  |  |

| GND            | V1            | NC             | R7            | VCCPLB         | E7            |  |  |

| GND            | V18           | NC             | T12           | VCCPLC         | B11           |  |  |

| GND/LP         | E5            | NC             | T6            | VCCPLD         | E11           |  |  |

| NC             | A10           | NC             | U16           | VCCPLE         | R11           |  |  |

| NC             | A11           | NC             | V17           | VCCPLF         | P12           |  |  |

| NC             | A12           | PRA            | E9            | VCCPLG         | U8            |  |  |

| NC             | A13           | PRB            | D9            | VCCPLH         | P8            |  |  |

| NC             | A8            | PRC            | P10           | VCCDA          | B3            |  |  |

| NC             | A9            | PRD            | R10           | VCCDA          | D14           |  |  |

| NC             | B12           | ТСК            | E6            | VCCDA          | E10           |  |  |

| NC             | F15           | TDI            | D7            | VCCDA          | J2            |  |  |

| NC             | F4            | TDO            | D5            | VCCDA          | K16           |  |  |

| NC             | G15           | TMS            | D4            | VCCDA          | P15           |  |  |

| NC             | G4            | TRST           | D6            | VCCDA          | P9            |  |  |

| NC             | H14           | VCCA           | E15           | VCCDA          | R5            |  |  |

| NC             | H15           | VCCA           | G10           | VCCIB0         | F7            |  |  |

| NC             | H5            | VCCA           | G11           | VCCIB0         | F8            |  |  |

| NC             | J1            | VCCA           | G5            | VCCIB0         | F9            |  |  |

| NC             | J14           | VCCA           | G8            | VCCIB1         | F10           |  |  |

| NC             | J15           | VCCA           | G9            | VCCIB1         | F11           |  |  |

| NC             | J5            | VCCA           | H12           | VCCIB1         | F12           |  |  |

| NC             | K14           | VCCA           | H7            | VCCIB2         | G13           |  |  |

| NC             | K15           | VCCA           | J12           | VCCIB2         | H13           |  |  |

| NC             | K5            | VCCA           | J7            | VCCIB2         | J13           |  |  |

| NC             | L14           | VCCA           | K12           | VCCIB3         | K13           |  |  |

| NC             | L15           | VCCA           | K7            | VCCIB3         | L13           |  |  |

| NC             | L5            | VCCA           | L12           | VCCIB3         | M13           |  |  |

| NC             | M4            | VCCA           | L7            | VCCIB4         | N10           |  |  |

| NC             | M5            | VCCA           | M10           | VCCIB4         | N11           |  |  |

| NC             | N17           | VCCA           | M11           | VCCIB4         | N12           |  |  |

### Note

For Package Manufacturing and Environmental information, visit Resource center at http://www.microsemi.com/soc/products/rescenter/package/index.html.

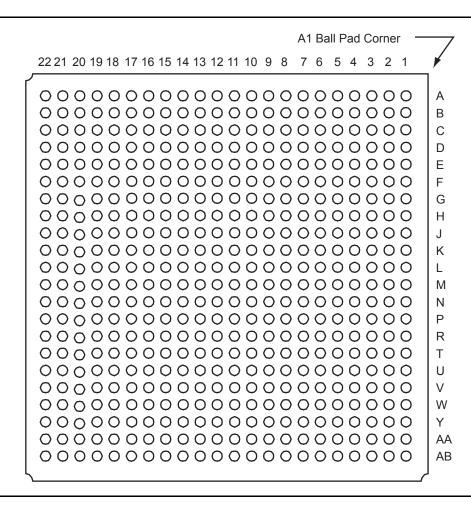

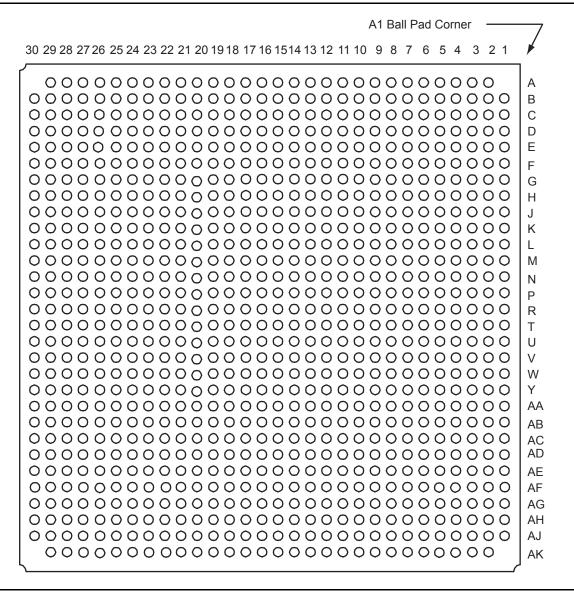

# FG896

### Note

For Package Manufacturing and Environmental information, visit Resource center at http://www.microsemi.com/soc/products/rescenter/package/index.html.

Package Pin Assignments

| CQ352          |               |  |  |  |  |

|----------------|---------------|--|--|--|--|

| AX250 Function | Pin<br>Number |  |  |  |  |

| VCCDA          | 346           |  |  |  |  |

| VCCIB0         | 321           |  |  |  |  |

| VCCIB0         | 333           |  |  |  |  |

| VCCIB0         | 344           |  |  |  |  |

| VCCIB1         | 273           |  |  |  |  |

| VCCIB1         | 285           |  |  |  |  |

| VCCIB1         | 297           |  |  |  |  |

| VCCIB2         | 227           |  |  |  |  |

| VCCIB2         | 239           |  |  |  |  |

| VCCIB2         | 245           |  |  |  |  |

| VCCIB2         | 257           |  |  |  |  |

| VCCIB3         | 185           |  |  |  |  |

| VCCIB3         | 197           |  |  |  |  |

| VCCIB3         | 203           |  |  |  |  |

| VCCIB3         | 215           |  |  |  |  |

| VCCIB4         | 144           |  |  |  |  |

| VCCIB4         | 156           |  |  |  |  |

| VCCIB4         | 168           |  |  |  |  |

| VCCIB5         | 96            |  |  |  |  |

| VCCIB5         | 108           |  |  |  |  |

| VCCIB5         | 120           |  |  |  |  |

| VCCIB6         | 50            |  |  |  |  |

| VCCIB6         | 62            |  |  |  |  |

| VCCIB6         | 68            |  |  |  |  |

| VCCIB6         | 80            |  |  |  |  |

| VCCIB7         | 8             |  |  |  |  |

| VCCIB7         | 20            |  |  |  |  |

| VCCIB7         | 26            |  |  |  |  |

| VCCIB7         | 38            |  |  |  |  |

| VCCPLA         | 317           |  |  |  |  |

| VCCPLB         | 315           |  |  |  |  |

| VCCPLC         | 303           |  |  |  |  |

| VCCPLD         | 301           |  |  |  |  |

| VCCPLE         | 140           |  |  |  |  |

| VCCPLF         | 138           |  |  |  |  |

| CQ352          |               |

|----------------|---------------|

| AX250 Function | Pin<br>Number |

| VCCPLG         | 126           |

| VCCPLH         | 124           |

| VCOMPLA        | 318           |

| VCOMPLB        | 316           |

| VCOMPLC        | 304           |

| VCOMPLD        | 302           |

| VCOMPLE        | 141           |

| VCOMPLF        | 139           |

| VCOMPLG        | 127           |

| VCOMPLH        | 125           |

| VPUMP          | 267           |

3-102

| CQ352             |               | CQ352          |               | CQ352          |               |

|-------------------|---------------|----------------|---------------|----------------|---------------|

| AX500 Function    | Pin<br>Number | AX500 Function | Pin<br>Number | AX500 Function | Pin<br>Number |

| IO87PB4F8         | 171           | IO119PB5F11    | 101           | IO146NB6F13    | 46            |

| IO89NB4F8         | 166           | IO121NB5F11    | 98            | IO146PB6F13    | 47            |

| IO89PB4F8         | 167           | IO121PB5F11    | 99            | Bank 7         |               |

| IO94NB4F9         | 164           | IO123NB5F11    | 94            | IO147NB7F14    | 40            |

| IO94PB4F9         | 165           | IO123PB5F11    | 95            | IO147PB7F14    | 41            |

| IO95NB4F9         | 160           | IO125NB5F11    | 92            | IO148NB7F14    | 42            |

| IO95PB4F9         | 161           | IO125PB5F11    | 93            | IO148PB7F14    | 43            |

| IO97NB4F9         | 158           | Bank 6         |               | IO149NB7F14    | 36            |

| IO97PB4F9         | 159           | IO126PB6F12    | 86            | IO149PB7F14    | 37            |

| IO99NB4F9         | 154           | IO127NB6F12    | 84            | IO151NB7F14    | 30            |

| IO99PB4F9         | 155           | IO127PB6F12    | 85            | IO151PB7F14    | 31            |

| IO100NB4F9        | 146           | IO129NB6F12    | 82            | IO152NB7F14    | 34            |

| IO100PB4F9        | 147           | IO129PB6F12    | 83            | IO152PB7F14    | 35            |

| IO101NB4F9        | 152           | IO131NB6F12    | 78            | IO153NB7F14    | 28            |

| IO101PB4F9        | 153           | IO131PB6F12    | 79            | IO153PB7F14    | 29            |

| IO103NB4F9/CLKEN  | 142           | IO133NB6F12    | 76            | IO155NB7F14    | 24            |

| IO103PB4F9/CLKEP  | 143           | IO133PB6F12    | 77            | IO155PB7F14    | 25            |

| IO104NB4F9/CLKFN  | 136           | IO134NB6F12    | 72            | IO157NB7F14    | 22            |

| IO104PB4F9/CLKFP  | 137           | IO134PB6F12    | 73            | IO157PB7F14    | 23            |

| Bank 5            |               | IO135NB6F12    | 70            | IO159NB7F15    | 16            |

| IO105NB5F10/CLKGN | 128           | IO135PB6F12    | 71            | IO159PB7F15    | 17            |

| IO105PB5F10/CLKGP | 129           | IO137NB6F13    | 66            | IO160NB7F15    | 18            |

| IO106NB5F10/CLKHN | 122           | IO137PB6F13    | 67            | IO160PB7F15    | 19            |

| IO106PB5F10/CLKHP | 123           | IO138NB6F13    | 64            | IO161NB7F15    | 12            |

| IO107NB5F10       | 118           | IO138PB6F13    | 65            | IO161PB7F15    | 13            |

| IO107PB5F10       | 119           | IO139NB6F13    | 60            | IO163NB7F15    | 10            |

| IO114NB5F11       | 112           | IO139PB6F13    | 61            | IO163PB7F15    | 11            |

| IO114PB5F11       | 113           | IO141NB6F13    | 54            | IO165NB7F15    | 6             |

| IO115NB5F11       | 110           | IO141PB6F13    | 55            | IO165PB7F15    | 7             |

| IO115PB5F11       | 111           | IO142NB6F13    | 58            | IO167NB7F15    | 4             |

| IO116NB5F11       | 106           | IO142PB6F13    | 59            | IO167PB7F15    | 5             |

| IO116PB5F11       | 107           | IO143NB6F13    | 52            | Dedicated I/C  | )             |

| IO117NB5F11       | 104           | IO143PB6F13    | 53            | GND            | 1             |

| IO117PB5F11       | 105           | IO145NB6F13    | 48            | GND            | 9             |

| IO119NB5F11       | 100           | IO145PB6F13    | 49            | GND            | 15            |

# 4 – Datasheet Information

# **List of Changes**

The following table lists critical changes that were made in the current version of the document.

| Revision                        | Changes                                                                                                                                                                                                                                                                            | Page          |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| Revision 18<br>(March 2012)     | Table 2-1 • Absolute Maximum Ratings was updated to correct the maximum DC core supply voltage (VCCA) from 1.6 V to 1.7 V (SAR 36786). The maximum input voltage (VI) was corrected from 3.75 V to 4.1 V (SAR 35419).                                                              | 2-1           |

|                                 | Values for tristate leakage current IOZ, and IIH and IIL were added to Table 2-3<br>• Standby Current (SARs 35774, 32021).                                                                                                                                                         |               |

|                                 | Figure 2-2 • VCCPLX and VCOMPLX Power Supply Connect was updated to correct the units for the resistance from "W" to $\Omega$ (SAR 36415).                                                                                                                                         | 2-9           |

|                                 | In the Introduction to the "User I/Os" section, the following sentence was added to clarify the slew rate setting (SAR 34943):<br>The slew rate setting is effective for both rising and falling edges.                                                                            | 2-11          |

|                                 | Figure 2-3 • Use of an External Resistor for 5 V Tolerance was revised to show the VCCI and GND clamp diodes. The explanatory text above the figure was revised as well (SAR 34942).                                                                                               | 2-13          |

|                                 | EQ 3 for 5 V tolerance was corrected to change Vdiode from 0.6 V to 0.7 V (SAR 36786).                                                                                                                                                                                             | 2-13          |

|                                 | Additional information was added to the "Using the Weak Pull-Up and Pull-Down Circuits" section to clarify how the weak pull-up and pull-down resistors are physically implemented (SAR 34945).                                                                                    | 2-17          |

|                                 | The description for the C <sub>INCLK</sub> parameter in Table 2-18 • Input Capacitance was changed from "Input capacitance on clock pin" to "Input capacitance on HCLK and RCLK pin" (SAR 34944).                                                                                  | 2-21          |

|                                 | Table 2-19 • I/O Input Rise Time and Fall Time* is new (SAR 34942).                                                                                                                                                                                                                | 2-21          |

|                                 | The minimum VIL for 1.5 V LVCMOS and PCI was corrected from –0.5 to –0.3 in Table 2-29 • DC Input and Output Levels and Table 2-33 • DC Input and Output Levels (SAR 34358).                                                                                                       | 2-38, 2-40    |

|                                 | Support for simulating the GCLR/ GPSET feature in the Axcelerator Family was added in Libero software v9.0 SPI1. Reference to the section explaining this in the <i>Antifuse Macro Library Guide</i> was added to the "R-Cell" section (SAR 26413).                                | 2-58          |

|                                 | The enable signal in Figure 2-32 • R-Cell Delays was corrected to show it is active low rather than active high (SAR 34946).                                                                                                                                                       | 2-59          |

| Revision 17<br>(September 2011) | The versioning system for datasheets has been changed. Datasheets are assigned a revision number that increments each time the datasheet is revised. The "Axcelerator Family Device Status" table indicates the status for each device in the device family.                       | iii           |

|                                 | The "Features" section, "Programmable Interconnect Element" section, and "Security" section were revised to clarify that although no existing security measures can give an absolute guarantee, Microsemi FPGAs implement the best security available in the industry (SAR 32865). | i, 1-1, 2-108 |

Datasheet Information

| Revision                         | Changes                                                                                                                                                                                                                                                                                                                                          | Page                 |

|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| Revision 17<br>(continued)       | The C180 package was removed from product tables and the "Package Pin Assignments" section (PDN 0909).                                                                                                                                                                                                                                           | 3-1                  |

|                                  | Package names used in the "Axcelerator Family Product Profile" and "Package Pin Assignments" section were revised to match standards given in <i>Package Mechanical Drawings</i> (SAR 27395).                                                                                                                                                    | i, 3-1               |

|                                  | The "Introduction" section for "User I/Os" was updated as follows:                                                                                                                                                                                                                                                                               | 2-11                 |

|                                  | "The user does not need to assign VREF pins for OUTBUF and TRIBUF. VREF pins are needed only for input and bidirectional I/Os" (SARs 24181, 24309).                                                                                                                                                                                              |                      |

|                                  | Power values in Table 2-4 • Default CLOAD/VCCI were updated to reflect those of SmartPower (SAR 33945).                                                                                                                                                                                                                                          | 2-3                  |

|                                  | Two parameter names were corrected in Figure 2-10 • Output Buffer Delays. One occurrence of $t_{\text{ENLZ}}$ was changed to $t_{\text{ENZL}}$ and one occurrence of $t_{\text{ENHZ}}$ was changed to $t_{\text{ENZH}}$ (SAR 33890).                                                                                                             | 2-22                 |

|                                  | The "Timing Model" section was updated with new timing values. Timing tables<br>in the "I/O Specifications" section were updated to include enable paths. Values<br>in the timing tables in the "Voltage-Referenced I/O Standards" section and<br>"Differential Standards" section were updated. Table 2-63 • R-Cell was updated<br>(SAR 33945). | 2-8, 2-26 to<br>2-53 |

|                                  | Figure 2-11 • Timing Model was replaced (SAR 33043).                                                                                                                                                                                                                                                                                             | 2-23                 |

|                                  | The timing tables for "RAM" and "FIFO" were updated (SAR 33945).                                                                                                                                                                                                                                                                                 | 2-90 to 2-106        |

|                                  | "Data Registers (DRs)" values were modified for IDCODE and USERCODE (SARs 18257, 26406).                                                                                                                                                                                                                                                         | 2-108                |

|                                  | The package diagram for the "CQ208" package was incorrect and has been replaced with the correct diagram (SARs 23865, 26345).                                                                                                                                                                                                                    | 3-89                 |

| Revision 16<br>(v2.8, Oct. 2009) | The datasheet was updated to include AX2000-CQ2526 information.                                                                                                                                                                                                                                                                                  | N/A                  |

|                                  | MIL-STD-883 Class B is no longer supported by Axcelerator FPGAs and as a result was removed.                                                                                                                                                                                                                                                     | N/A                  |

|                                  | A footnote was added to the "Introduction" in the "Axcelerator Clock Management System" section.                                                                                                                                                                                                                                                 | 2-75                 |

| Revision 15                      | RoHS-compliant information was added to the "Ordering Information".                                                                                                                                                                                                                                                                              | ii                   |

| (v2.7, Nov. 2008)                | ACTgen was changed to SmartGen because ACTgen is obsolete.                                                                                                                                                                                                                                                                                       | N/A                  |

| Revision 14<br>(v2.6)            | In Table 2-4, the units for the $P_{LOAD},P_{10},andP_{I/O}$ were updated from mW/MHz to mW/MHz.                                                                                                                                                                                                                                                 | 2-3                  |

|                                  | In the "Pin Descriptions"section, the HCLK and CLK descriptions were updated to include tie-off information.                                                                                                                                                                                                                                     | 2-9                  |

|                                  | The "Global Resource Distribution" section was updated.                                                                                                                                                                                                                                                                                          | 2-70                 |

|                                  | The " CG624" table was updated.                                                                                                                                                                                                                                                                                                                  | 3-116                |

| Revision 13<br>(v2.5)            | A note was added to Table 2-2.                                                                                                                                                                                                                                                                                                                   | 2-1                  |

|                                  | In the "Package Thermal Characteristics", the temperature was changed from 150°C to 125°C.                                                                                                                                                                                                                                                       | 2-6                  |

Datasheet Information

| Revision                  | Changes                                                                   | Page              |

|---------------------------|---------------------------------------------------------------------------|-------------------|

| Revision 3<br>(continued) | The timing characteristics tables from pages 2-26 to 2-60 were updated.   | 2-26 to 2-60      |

|                           | The "Global Resources" section was updated.                               | 2-66              |

|                           | The timing characteristics tables from pages 2-102 to 2-103 were updated. | 2-102 to<br>2-103 |

|                           | The "PQ208", "FG256", and "FG324" tables are new.                         | 3-9,3-16, 3-84    |