Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                              |

|--------------------------------|--------------------------------------------------------------|

| Product Status                 | Obsolete                                                     |

| Number of LABs/CLBs            | 32256                                                        |

| Number of Logic Elements/Cells | -                                                            |

| Total RAM Bits                 | 294912                                                       |

| Number of I/O                  | 684                                                          |

| Number of Gates                | 2000000                                                      |

| Voltage - Supply               | 1.425V ~ 1.575V                                              |

| Mounting Type                  | Surface Mount                                                |

| Operating Temperature          | 0°C ~ 70°C (TA)                                              |

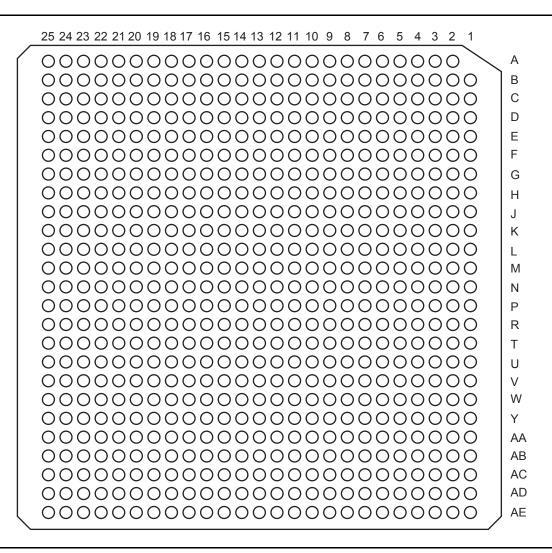

| Package / Case                 | 1152-BGA                                                     |

| Supplier Device Package        | 1152-FPBGA (35x35)                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microsemi/ax2000-fg1152 |

|                                |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 – General Description

Axcelerator devices offer high performance at densities of up to two million equivalent system gates. Based upon the Microsemi AX architecture, Axcelerator has several system-level features such as embedded SRAM (with complete FIFO control logic), PLLs, segmentable clocks, chip-wide highway routing, and carry logic.

## **Device Architecture**

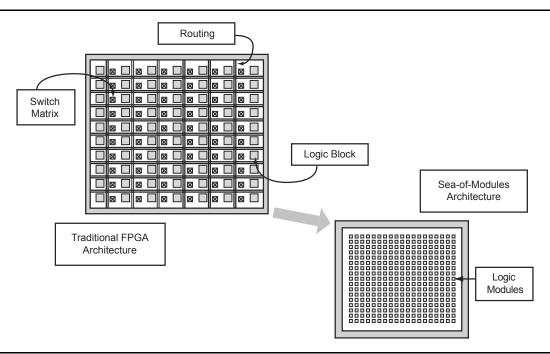

AX architecture, derived from the highly-successful SX-A sea-of-modules architecture, has been designed for high performance and total logic module utilization (Figure 1-1). Unlike in traditional FPGAs, the entire floor of the Axcelerator device is covered with a grid of logic modules, with virtually no chip area lost to interconnect elements or routing.

## Programmable Interconnect Element

The Axcelerator family uses a patented metal-to-metal antifuse programmable interconnect element that resides between the upper two layers of metal (Figure 1-2 on page 1-2). This completely eliminates the channels of routing and interconnect resources between logic modules (as implemented on traditional FPGAs) and enables the efficient sea-of-modules architecture. The antifuses are normally open circuit and, when programmed, form a permanent, passive, low-impedance connection, leading to the fastest signal propagation in the industry. In addition, the extremely small size of these interconnect elements gives the Axcelerator family abundant routing resources.

The very nature of Microsemi's nonvolatile antifuse technology provides excellent protection against design pirating and cloning (FuseLock technology). Typical cloning attempts are impossible (even if the security fuse is left unprogrammed) as no bitstream or programming file is ever downloaded or stored in the device. Reverse engineering is virtually impossible due to the difficulty of trying to distinguish between programmed and unprogrammed antifuses and also due to the programming methodology of antifuse devices (see "Security" on page 2-108).

Figure 1-1 • Sea-of-Modules Comparison

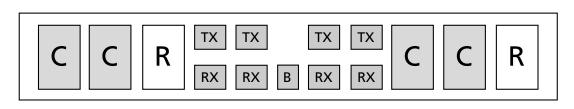

Two C-cells, a single R-cell, two Transmit (TX), and two Receive (RX) routing buffers form a Cluster, while two Clusters comprise a SuperCluster (Figure 1-4). Each SuperCluster also contains an independent Buffer (B) module, which supports buffer insertion on high-fanout nets by the place-and-route tool, minimizing system delays while improving logic utilization.

#### Figure 1-4 • AX SuperCluster

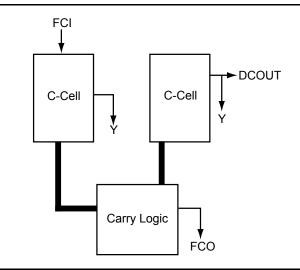

The logic modules within the SuperCluster are arranged so that two combinatorial modules are side-byside, giving a C–C–R – C–C–R pattern to the SuperCluster. This C–C–R pattern enables efficient implementation (minimum delay) of two-bit carry logic for improved arithmetic performance (Figure 1-5 on page 1-3).

Figure 1-5 • AX 2-Bit Carry Logic

The AX architecture is fully fracturable, meaning that if one or more of the logic modules in a SuperCluster are used by a particular signal path, the other logic modules are still available for use by other paths.

At the chip level, SuperClusters are organized into core tiles, which are arrayed to build up the full chip. For example, the AX1000 is composed of a 3x3 array of nine core tiles. Surrounding the array of core tiles are blocks of I/O Clusters and the I/O bank ring (Table 1-1). Each core tile consists of an array of 336 SuperClusters and four SRAM blocks (176 SuperClusters and three SRAM blocks for the AX250).

| Table 1-1 | • Number | of Core | Tiles | per | Device |

|-----------|----------|---------|-------|-----|--------|

|-----------|----------|---------|-------|-----|--------|

| Device | Number of Core Tiles |

|--------|----------------------|

| AX125  | 1 regular tile       |

| AX250  | 4 smaller tiles      |

| AX500  | 4 regular tiles      |

| AX1000 | 9 regular tiles      |

| AX2000 | 16 regular tiles     |

**Detailed Specifications**

Figure 2-10 • Output Buffer Delays

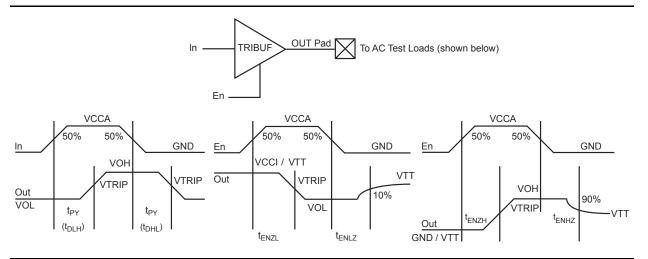

## Timing Model and Waveforms

## **Timing Characteristics**

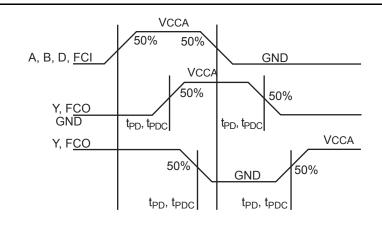

#### Table 2-62 • C-Cell

Worst-Case Commercial Conditions VCCA = 1.425 V, VCCI = 3.0 V, T<sub>J</sub> =  $70^{\circ}$ C

|                           |                                                        | –2 S | peed | –1 S | peed | Std S | Speed |       |

|---------------------------|--------------------------------------------------------|------|------|------|------|-------|-------|-------|

| Parameter                 | Description                                            | Min. | Max. | Min. | Max. | Min.  | Max.  | Units |

| C-Cell Propagation Delays |                                                        |      |      |      |      |       |       |       |

| t <sub>PD</sub>           | Any input to output Y                                  |      | 0.74 |      | 0.84 |       | 0.99  | ns    |

| t <sub>PDC</sub>          | Any input to carry chain output (FCO)                  |      | 0.57 |      | 0.64 |       | 0.76  | ns    |

| t <sub>PDB</sub>          | Any input through DB when one input is used            |      | 0.95 |      | 1.09 |       | 1.28  | ns    |

| t <sub>CCY</sub>          | Input to carry chain (FCI) to Y                        |      | 0.61 |      | 0.69 |       | 0.82  | ns    |

| tcc                       | Input to carry chain (FCI) to carry chain output (FCO) |      | 0.08 |      | 0.09 |       | 0.11  | ns    |

**Detailed Specifications**

The HM and CM modules can select between:

- The HCLK or CLK source respectively

- · A local signal routed on generic routing resources

This allows each core tile to have eight clocks independent of the other core tiles in the device.

Both HCLK and CLK are segmentable, meaning that individual branches of the global resource can be used independently.

Like the HM and CM modules, the HD and RD modules can select between:

- The HCLK or CLK source from the HM or CM module respectively

- A local signal routed on generic routing resources

The AX architecture is capable of supporting a large number of local clocks—24 segments per HCLK driving north-south and 28 segments per CLK driving east-west per core tile.

Microsemi's Designer software's place-and-route takes advantage of the segmented clock structure found in Axcelerator devices by turning off any unused clock segments. This results in not only better performance but also lower power consumption.

## **Global Resource Access Macros**

Global resources can be driven by one of three sources: external pad(s), an internal net, or the output of a PLL. These connections can be made by using one of three types of macros: CLKBUF, CLKINT, and PLLCLK.

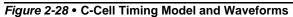

### CLKBUF and HCLKBUF

CLKBUF (HCLKBUF) is used to drive a CLK (HCLK) from external pads. These macros can be used either generically or with the specific I/O standard desired (e.g. CLKBUF\_LVCMOS25, HCLKBUF\_LVDS, etc.) (Figure 2-42).

Figure 2-42 • CLKBUF and HCLKBUF

Package pins CLKEP and CLKEN are associated with CLKE; package pins HCLKAP and HCLKAN are associated with HCLKA, etc.

Note that when CLKBUF (HCLKBUF) is used with a single-ended I/O standard, it must be tied to the P-pad of the CLK (HCLK) package pin. In this case, the CLK (HCLK) N-pad can be used for user signals.

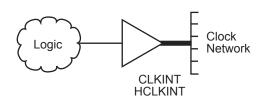

## **CLKINT and HCLKINT**

CLKINT (HCLKINT) is used to access the CLK (HCLK) resource internally from the user signals (Figure 2-43).

| CLK1                       | CLK2                     |

|----------------------------|--------------------------|

| CLK1                       | Routed net               |

| CLK1                       | Unused                   |

| CLK2                       | CLK1                     |

| CLK2                       | Routed net               |

| CLK2                       | Both CLK1 and routed net |

| CLK2                       | Unused                   |

| Unused                     | CLK1                     |

| Unused                     | Routed net               |

| Unused                     | Both CLK1 and routed net |

| Unused                     | Unused                   |

| Routed net                 | CLK1                     |

| Routed net                 | Unused                   |

| Both CLK1 and CLK2         | Routed net               |

| Both CLK1 and CLK2         | Unused                   |

| Both CLK1 and routed net   | Unusable                 |

| Both CLK2 and routed net   | CLK1                     |

| Both CLK2 and routed net   | Unused                   |

| CLK1, CLK2, and routed net | Unusable                 |

#### Table 2-83 • South PLL Connections

Note: Designer software currently does not support all of these connections. Only exclusive connections where one output connects to a single net are supported at this time (e.g., CLK1 driving both CLK1 and CLK2 is not supported).

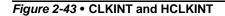

## **Embedded Memory**

The AX architecture provides extensive, high-speed memory resources to the user. Each 4,608 bit block of RAM contains its own embedded FIFO controller, allowing the user to configure each block as either RAM or FIFO.

To meet the needs of high performance designs, the memory blocks operate in synchronous mode for both read and write operations. However, the read and write clocks are completely independent, and each may operate up to and above 500 MHz.

No additional core logic resources are required to cascade the address and data buses when cascading different RAM blocks. Dedicated routing runs along each column of RAM to facilitate cascading.

The AX memory block includes dedicated FIFO control logic to generate internal addresses and external flag logic (FULL, EMPTY, AFULL, AEMPTY). Since read and write operations can occur asynchronously to one another, special control circuitry is included to prevent metastability, overflow, and underflow. A block diagram of the memory module is illustrated in Figure 2-57.

During RAM operation, read (RA) and write (WA) addresses are sourced by user logic and the FIFO controller is ignored. In FIFO mode, the internal addresses are generated by the FIFO controller and routed to the RAM array by internal MUXes. Enables with programmable polarity are provided to create upper address bits for cascading up to 16 memory blocks. When cascading memory blocks, the bussed signals WA, WD, WEN, RA, RD, and REN are internally linked to eliminate external routing congestion.

Figure 2-57 • Axcelerator Memory Module

**Detailed Specifications**

#### Table 2-89 • One RAM Block

### Worst-Case Commercial Conditions VCCA = 1.425 V, VCCI = 3.0 V, T<sub>J</sub> = $70^{\circ}\text{C}$

|                      |                               | -2 Speed |      | -1 S | -1 Speed |      | Std Speed |       |

|----------------------|-------------------------------|----------|------|------|----------|------|-----------|-------|

| Parameter            | Description                   | Min.     | Max. | Min. | Max.     | Min. | Max.      | Units |

| Write Mode           |                               |          |      |      |          |      |           |       |

| t <sub>WDASU</sub>   | Write Data Setup vs. WCLK     |          | 1.08 |      | 1.23     |      | 1.45      | ns    |

| t <sub>WDAHD</sub>   | Write Data Hold vs. WCLK      |          | 0.22 |      | 0.25     |      | 0.30      | ns    |

| t <sub>WADSU</sub>   | Write Address Setup vs. WCLK  |          | 1.08 |      | 1.23     |      | 1.45      | ns    |

| t <sub>WADHD</sub>   | Write Address Hold vs. WCLK   |          | 0.00 |      | 0.00     |      | 0.00      | ns    |

| t <sub>WENSU</sub>   | Write Enable Setup vs. WCLK   |          | 1.08 |      | 1.23     |      | 1.45      | ns    |

| t <sub>WENHD</sub>   | Write Enable Hold vs. WCLK    |          | 0.22 |      | 0.25     |      | 0.30      | ns    |

| t <sub>wcкн</sub>    | WCLK Minimum High Pulse Width | 0.75     |      | 0.75 |          | 0.75 |           | ns    |

| t <sub>WCLK</sub>    | WCLK Minimum Low Pulse Width  | 0.88     |      | 0.88 |          | 0.88 |           | ns    |

| t <sub>WCKP</sub>    | WCLK Minimum Period           | 1.63     |      | 1.63 |          | 1.63 |           | ns    |

| Read Mode            |                               |          |      |      |          |      |           |       |

| t <sub>RADSU</sub>   | Read Address Setup vs. RCLK   |          | 0.81 |      | 0.92     |      | 1.08      | ns    |

| t <sub>RADHD</sub>   | Read Address Hold vs. RCLK    |          | 0.00 |      | 0.00     |      | 0.00      | ns    |

| t <sub>RENSU</sub>   | Read Enable Setup vs. RCLK    |          | 0.81 |      | 0.92     |      | 1.08      | ns    |

| t <sub>RENHD</sub>   | Read Enable Hold vs. RCLK     |          | 0.00 |      | 0.00     |      | 0.00      | ns    |

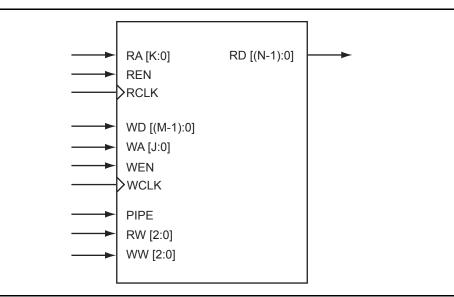

| t <sub>RCK2RD1</sub> | RCLK-to-OUT (Pipelined)       |          | 1.32 |      | 1.51     |      | 1.77      | ns    |

| t <sub>RCK2RD2</sub> | RCLK-to-OUT (Non-Pipelined)   |          | 2.16 |      | 2.46     |      | 2.90      | ns    |

| t <sub>RCLKH</sub>   | RCLK Minimum High Pulse Width | 0.77     |      | 0.77 |          | 0.77 |           | ns    |

| t <sub>RCLKL</sub>   | RCLK Minimum Low Pulse Width  | 0.93     |      | 0.93 |          | 0.93 |           | ns    |

| t <sub>RCKP</sub>    | RCLK Minimum Period           | 1.70     |      | 1.70 |          | 1.70 |           | ns    |

Note: Timing data for this single block RAM has a depth of 4,096. For all other combinations, use Microsemi's timing software.

Figure 2-68 • FIFO Read Timing

mode if desired. Please note, if the I/O bank is not disabled, differential I/Os belonging to the I/O bank will still consume normal power, even when operating in the low power mode.

The Axcelerator device will resume normal operation  $10\mu s$  after the LP pin is pulled Low.

To further reduce power consumption, the internal charge pump can be bypassed and an external power supply voltage can be used instead. This saves the internal charge-pump operating current, resulting in no DC current draw. The Axcelerator family devices have a dedicated " $V_{PUMP}$ " pin that can be used to access an external charge pump device. In normal chip operation, when using the internal charge pump,  $V_{PUMP}$  should be tied to GND. When the voltage level on  $V_{PUMP}$  is set to 3.3V, the internal charge pump is turned off, and the  $V_{PUMP}$  voltage will be used as the charge pump voltage. Adequate voltage regulation (i.e. high drive, low output impedance, and good decoupling) should be used at  $V_{PUMP}$ .

In addition, any PLL in use can be powered down to further reduce power consumption. This can be done with the PowerDown pin driven Low. Driving this pin High restarts the PLL with the output clock(s) being stable once lock is restored.

## JTAG

Axcelerator offers a JTAG interface that is compliant with the IEEE 1149.1 standard. The user can employ the JTAG interface for probing a design and performing any JTAG Public Instructions as defined in the Table 2-103.

| Instruction (IR4:IR0) | Binary Code |

|-----------------------|-------------|

| Extest                | 00000       |

| Preload / Sample      | 00001       |

| Intest                | 00010       |

| USERCODE              | 00011       |

| IDCODE                | 00100       |

| HIGHZ                 | 01110       |

| CLAMP                 | 01111       |

| Diagnostic            | 10000       |

| Reserved              | All others  |

| Bypass                | 11111       |

Table 2-103 • JTAG Instruction Code

## Interface

The interface consists of four inputs: Test Mode Select (TMS), Test Data In (TDI), Test Clock (TCK), TAP Controller Reset (TRST), and an output, Test Data Out (TDO). TMS, TDI, and TRST have on-chip pull-up resistors.

## TRST

TRST (Test-Logic Reset) is an active-low, asynchronous reset signal to the TAP controller. The TRST input can be used to reset the Test Access Port (TAP) Controller to the TRST state. The TAP Controller can be held at this state permanently by grounding the TRST pin. To hold the JTAG TAP controller in the TRST state, it is recommended to connect TRST to ground via a 1 k $\Omega$  resistor.

There is an optional internal pull-up resistor available for the TRST input that can be set by the user at programming. Care should be exercised when using this option in combination with an external tie-off to ground.

An on-chip power-on-reset (POWRST) circuit is included. POWRST has the same function as "TRST," but it only occurs at power-up or during recovery from a VCCA and/or VCCDA voltage drop.

Package Pin Assignments

| FG484          |               | FG484          |               | FG484             | FG484         |  |  |

|----------------|---------------|----------------|---------------|-------------------|---------------|--|--|

| AX500 Function | Pin<br>Number | AX500 Function | Pin<br>Number | AX500 Function    | Pin<br>Number |  |  |

| IO54PB2F5      | H22           | IO72PB3F6      | P20           | IO90NB4F8         | Y17           |  |  |

| IO55NB2F5      | L17           | IO73PB3F6      | R19           | IO90PB4F8         | Y18           |  |  |

| IO55PB2F5      | K17           | IO74NB3F7      | V21           | IO91NB4F8         | V15           |  |  |

| IO56NB2F5      | K21           | IO74PB3F7      | U21           | IO91PB4F8         | V16           |  |  |

| IO56PB2F5      | K22           | IO75NB3F7      | V22           | IO92PB4F8         | AB17          |  |  |

| IO58NB2F5      | L20           | IO75PB3F7      | U22           | IO93NB4F8         | Y15           |  |  |

| IO58PB2F5      | K20           | IO76NB3F7      | U20           | IO93PB4F8         | Y16           |  |  |

| IO59NB2F5      | L18           | IO76PB3F7      | T20           | IO94NB4F9         | AA16          |  |  |

| IO59PB2F5      | K18           | IO77NB3F7      | R17           | IO94PB4F9         | AA17          |  |  |

| IO60NB2F5      | M21           | IO77PB3F7      | P17           | IO95NB4F9         | AB14          |  |  |

| IO60PB2F5      | L21           | IO78NB3F7      | W21           | IO95PB4F9         | AB15          |  |  |

| IO61NB2F5      | L16           | IO78PB3F7      | W22           | IO96NB4F9         | W15           |  |  |

| IO61PB2F5      | K16           | IO79NB3F7      | T18           | IO96PB4F9         | W16           |  |  |

| IO62NB2F5      | M19           | IO79PB3F7      | R18           | IO97NB4F9         | AA13          |  |  |

| IO62PB2F5      | L19           | IO80NB3F7      | W20           | IO97PB4F9         | AB13          |  |  |

| Bank 3         |               | IO80PB3F7      | V20           | IO98NB4F9         | AA14          |  |  |

| IO63NB3F6      | N16           | IO81NB3F7      | U19           | IO98PB4F9         | AA15          |  |  |

| IO63PB3F6      | M16           | IO81PB3F7      | T19           | IO100NB4F9        | Y14           |  |  |

| IO64NB3F6      | P22           | IO82NB3F7      | U18           | IO100PB4F9        | W14           |  |  |

| IO64PB3F6      | N22           | IO82PB3F7      | V19           | IO101NB4F9        | Y12           |  |  |

| IO65NB3F6      | N20           | IO83NB3F7      | R16           | IO101PB4F9        | Y13           |  |  |

| IO65PB3F6      | M20           | IO83PB3F7      | P16           | IO102NB4F9        | AA11          |  |  |

| IO66NB3F6      | P21           | Bank 4         |               | IO102PB4F9        | AA12          |  |  |

| IO66PB3F6      | N21           | IO84NB4F8      | AB18          | IO103NB4F9/CLKEN  | V12           |  |  |

| IO67NB3F6      | N18           | IO84PB4F8      | AB19          | IO103PB4F9/CLKEP  | V13           |  |  |

| IO67PB3F6      | N19           | IO85NB4F8      | T15           | IO104NB4F9/CLKFN  | W11           |  |  |

| IO68NB3F6      | T22           | IO85PB4F8      | T16           | IO104PB4F9/CLKFP  | W12           |  |  |

| IO68PB3F6      | R22           | IO86NB4F8      | AA18          | Bank 5            |               |  |  |

| IO69NB3F6      | N17           | IO86PB4F8      | AA19          | IO105NB5F10/CLKGN | U10           |  |  |

| IO69PB3F6      | M17           | IO87NB4F8      | W17           | IO105PB5F10/CLKGP | U11           |  |  |

| IO70NB3F6      | T21           | IO87PB4F8      | V17           | IO106NB5F10/CLKHN | V9            |  |  |

| IO70PB3F6      | R21           | IO88NB4F8      | Y19           | IO106PB5F10/CLKHP | V10           |  |  |

| IO71NB3F6      | P18           | IO88PB4F8      | W18           | IO107NB5F10       | Y10           |  |  |

| IO71PB3F6      | P19           | IO89NB4F8      | U14           | IO107PB5F10       | Y11           |  |  |

| IO72NB3F6      | R20           | IO89PB4F8      | U15           | IO108NB5F10       | AA9           |  |  |

Package Pin Assignments

| FG484           | FG484 FG48    |                  |               | FG484           |               |

|-----------------|---------------|------------------|---------------|-----------------|---------------|

| AX1000 Function | Pin<br>Number | AX1000 Function  | Pin<br>Number | AX1000 Function | Pin<br>Number |

| Bank 0          | 1             | IO29NB0F2        | B12           | IO51PB1F4       | D22           |

| IO01NB0F0       | E3            | IO29PB0F2        | B11           | IO52NB1F4       | E16           |

| IO01PB0F0       | D3            | IO30NB0F2/HCLKAN | E11           | IO52PB1F4       | E15           |

| IO02NB0F0       | E7            | IO30PB0F2/HCLKAP | E10           | IO57NB1F5       | E21           |

| IO02PB0F0       | E6            | IO31NB0F2/HCLKBN | D12           | IO57PB1F5       | D21           |

| IO05NB0F0       | D2            | IO31PB0F2/HCLKBP | D11           | IO60NB1F5       | G16           |

| IO05PB0F0       | E2            | Bank 1           |               | IO60PB1F5       | G15           |

| IO06NB0F0       | C5            | IO32NB1F3/HCLKCN | F13           | IO61NB1F5       | D18           |

| IO06PB0F0       | C4            | IO32PB1F3/HCLKCP | F12           | IO61PB1F5       | E17           |

| IO12NB0F1       | D7            | IO33NB1F3/HCLKDN | E14           | IO63NB1F5       | E20           |

| IO12PB0F1       | D6            | IO33PB1F3/HCLKDP | E13           | IO63PB1F5       | D20           |

| IO13NB0F1       | B5            | IO34NB1F3        | C13           | Bank 2          |               |

| IO13PB0F1       | B4            | IO34PB1F3        | C12           | IO64NB2F6       | F18           |

| IO14NB0F1       | E9            | IO37NB1F3        | B14           | IO64PB2F6       | F17           |

| IO14PB0F1       | E8            | IO37PB1F3        | B13           | IO67NB2F6       | F19           |

| IO15NB0F1       | C7            | IO38NB1F3        | A16           | IO67PB2F6       | E19           |

| IO15PB0F1       | C6            | IO38PB1F3        | A15           | IO68NB2F6       | J16           |

| IO16NB0F1       | A5            | IO40NB1F3        | C15           | IO68PB2F6       | H16           |

| IO16PB0F1       | A4            | IO42NB1F4        | A18           | IO70NB2F6       | J17           |

| IO17NB0F1       | B7            | IO42PB1F4        | A17           | IO70PB2F6       | H17           |

| IO17PB0F1       | B6            | IO43NB1F4        | B16           | IO74NB2F7       | J18           |

| IO18NB0F1       | A7            | IO43PB1F4        | B15           | IO74PB2F7       | H18           |

| IO18PB0F1       | A6            | IO44NB1F4        | B18           | IO75NB2F7       | G20           |

| IO19NB0F1       | C9            | IO44PB1F4        | B17           | IO75PB2F7       | F20           |

| IO19PB0F1       | C8            | IO45NB1F4        | B19           | IO79NB2F7       | H19           |

| IO20NB0F1       | D9            | IO45PB1F4        | A19           | IO79PB2F7       | G19           |

| IO20PB0F1       | D8            | IO46NB1F4        | C19           | IO80NB2F7       | L16           |

| IO21NB0F1       | B9            | IO46PB1F4        | C18           | IO80PB2F7       | K16           |

| IO21PB0F1       | B8            | IO48NB1F4        | F15           | IO84NB2F7       | L17           |

| IO22NB0F2       | A9            | IO48PB1F4        | F14           | IO84PB2F7       | K17           |

| IO22PB0F2       | A8            | IO49NB1F4        | D16           | IO85NB2F8       | G21           |

| IO23NB0F2       | B10           | IO49PB1F4        | D15           | IO85PB2F8       | F21           |

| IO23PB0F2       | A10           | IO50NB1F4        | C17           | IO86NB2F8       | G22           |

| IO26NB0F2       | A14           | IO50PB1F4        | C16           | IO86PB2F8       | F22           |

| IO26PB0F2       | A13           | IO51NB1F4        | E22           | IO87NB2F8       | J20           |

| FG676           |            |      |

|-----------------|------------|------|

| AX1000 Function | Pin Number | A    |

| IO129PB4F12     | AA21       |      |

| IO131NB4F12     | AD22       |      |

| IO131PB4F12     | AD23       |      |

| IO132NB4F12     | AE23       |      |

| IO132PB4F12     | AE24       |      |

| IO133NB4F12     | AB20       |      |

| IO133PB4F12     | AA20       |      |

| IO134NB4F12     | AC21       | 1015 |

| IO134PB4F12     | AC22       | 1015 |

| IO135NB4F12     | AF22       | 1016 |

| IO135PB4F12     | AF23       | 1016 |

| IO137NB4F12     | AB19       |      |

| IO137PB4F12     | AA19       | 1016 |

| IO139NB4F13     | AC19       | 1016 |

| IO139PB4F13     | AC20       | 1016 |

| IO140NB4F13     | AE21       | 1016 |

| IO140PB4F13     | AE22       |      |

| IO141NB4F13     | AD20       |      |

| IO141PB4F13     | AD21       |      |

| IO143NB4F13     | AB17       |      |

| IO143PB4F13     | AB18       |      |

| IO144NB4F13     | AE19       |      |

| IO144PB4F13     | AE20       |      |

| IO145NB4F13     | AC17       |      |

| IO145PB4F13     | AC18       |      |

| IO146NB4F13     | AD18       |      |

| IO146PB4F13     | AD19       |      |

| IO147NB4F13     | AA17       |      |

| IO147PB4F13     | AA18       |      |

| IO148NB4F13     | AF20       |      |

| IO148PB4F13     | AF21       |      |

| IO149NB4F13     | AA16       |      |

| IO149PB4F13     | Y16        |      |

| IO151NB4F13     | AC16       |      |

| IO151PB4F13     | AB16       |      |

| IO153NB4F14     | AE17       |      |

| FG676             |            |  |  |  |  |

|-------------------|------------|--|--|--|--|

| AX1000 Function   | Pin Number |  |  |  |  |

| IO153PB4F14       | AE18       |  |  |  |  |

| IO154NB4F14       | AF17       |  |  |  |  |

| IO154PB4F14       | AF18       |  |  |  |  |

| IO155NB4F14       | AA15       |  |  |  |  |

| IO155PB4F14       | Y15        |  |  |  |  |

| IO157NB4F14       | AC15       |  |  |  |  |

| IO157PB4F14       | AB15       |  |  |  |  |

| IO159NB4F14/CLKEN | AE16       |  |  |  |  |

| IO159PB4F14/CLKEP | AF16       |  |  |  |  |

| IO160NB4F14/CLKFN | AE14       |  |  |  |  |

| IO160PB4F14/CLKFP | AE15       |  |  |  |  |

| Bank 5            |            |  |  |  |  |

| IO161NB5F15/CLKGN | AE12       |  |  |  |  |

| IO161PB5F15/CLKGP | AE13       |  |  |  |  |

| IO162NB5F15/CLKHN | AE11       |  |  |  |  |

| IO162PB5F15/CLKHP | AF11       |  |  |  |  |

| IO163NB5F15       | AC12       |  |  |  |  |

| IO163PB5F15       | AB12       |  |  |  |  |

| IO165NB5F15       | Y12        |  |  |  |  |

| IO165PB5F15       | AA13       |  |  |  |  |

| IO167NB5F15       | Y11        |  |  |  |  |

| IO167PB5F15       | AA12       |  |  |  |  |

| IO168NB5F15       | AF9        |  |  |  |  |

| IO168PB5F15       | AF10       |  |  |  |  |

| IO169NB5F15       | AB11       |  |  |  |  |

| IO169PB5F15       | AA11       |  |  |  |  |

| IO171NB5F16       | AE9        |  |  |  |  |

| IO171PB5F16       | AE10       |  |  |  |  |

| IO173NB5F16       | AC10       |  |  |  |  |

| IO173PB5F16       | AC11       |  |  |  |  |

| IO174NB5F16       | AE7        |  |  |  |  |

| IO174PB5F16       | AE8        |  |  |  |  |

| IO175NB5F16       | AC9        |  |  |  |  |

| IO175PB5F16       | AD9        |  |  |  |  |

| IO176NB5F16       | AF6        |  |  |  |  |

| IO176PB5F16       | AF7        |  |  |  |  |

| 50070           |            |  |  |  |  |

|-----------------|------------|--|--|--|--|

| FG676           |            |  |  |  |  |

| AX1000 Function | Pin Number |  |  |  |  |

| IO177NB5F16     | AA10       |  |  |  |  |

| IO177PB5F16     | AB10       |  |  |  |  |

| IO179NB5F16     | AD7        |  |  |  |  |

| IO179PB5F16     | AD8        |  |  |  |  |

| IO180NB5F16     | AC7        |  |  |  |  |

| IO180PB5F16     | AC8        |  |  |  |  |

| IO181NB5F17     | AA9        |  |  |  |  |

| IO181PB5F17     | AB9        |  |  |  |  |

| IO183NB5F17     | AD6        |  |  |  |  |

| IO183PB5F17     | AE6        |  |  |  |  |

| IO184NB5F17     | AE5        |  |  |  |  |

| IO184PB5F17     | AF5        |  |  |  |  |

| IO185NB5F17     | AA8        |  |  |  |  |

| IO185PB5F17     | AB8        |  |  |  |  |

| IO187NB5F17     | AC5        |  |  |  |  |

| IO187PB5F17     | AC6        |  |  |  |  |

| IO188NB5F17     | AD4        |  |  |  |  |

| IO188PB5F17     | AD5        |  |  |  |  |

| IO189NB5F17     | AB6        |  |  |  |  |

| IO189PB5F17     | AB7        |  |  |  |  |

| IO190NB5F17     | AF4        |  |  |  |  |

| IO190PB5F17     | AE4        |  |  |  |  |

| IO191NB5F17     | AE3        |  |  |  |  |

| IO191PB5F17     | AF3        |  |  |  |  |

| IO192NB5F17     | AA6        |  |  |  |  |

| IO192PB5F17     | AA7        |  |  |  |  |

| Bank 6          |            |  |  |  |  |

| IO193NB6F18     | Y5         |  |  |  |  |

| IO193PB6F18     | AA5        |  |  |  |  |

| IO194NB6F18     | AB3        |  |  |  |  |

| IO194PB6F18     | AC3        |  |  |  |  |

| IO195NB6F18     | Y4         |  |  |  |  |

| IO195PB6F18     | AA4        |  |  |  |  |

| IO196NB6F18     | AC2        |  |  |  |  |

| IO196PB6F18     | AD2        |  |  |  |  |

| IO197NB6F18     | W6         |  |  |  |  |

|                 | •          |  |  |  |  |

| FG676           |            | FG676           |            | FG676           |            |

|-----------------|------------|-----------------|------------|-----------------|------------|

| AX1000 Function | Pin Number | AX1000 Function | Pin Number | AX1000 Function | Pin Number |

| GND             | A8         | GND             | L12        | GND             | R12        |

| GND             | AC23       | GND             | L13        | GND             | R13        |

| GND             | AC4        | GND             | L14        | GND             | R14        |

| GND             | AD24       | GND             | L15        | GND             | R15        |

| GND             | AD3        | GND             | L16        | GND             | R16        |

| GND             | AE2        | GND             | L17        | GND             | R17        |

| GND             | AE25       | GND             | M10        | GND             | T10        |

| GND             | AF1        | GND             | M11        | GND             | T11        |

| GND             | AF13       | GND             | M12        | GND             | T12        |

| GND             | AF14       | GND             | M13        | GND             | T13        |

| GND             | AF19       | GND             | M14        | GND             | T14        |

| GND             | AF26       | GND             | M15        | GND             | T15        |

| GND             | AF8        | GND             | M16        | GND             | T16        |

| GND             | B2         | GND             | M17        | GND             | T17        |

| GND             | B25        | GND             | N1         | GND             | U10        |

| GND             | B26        | GND             | N10        | GND             | U11        |

| GND             | C24        | GND             | N11        | GND             | U12        |

| GND             | C3         | GND             | N12        | GND             | U13        |

| GND             | G20        | GND             | N13        | GND             | U14        |

| GND             | G7         | GND             | N14        | GND             | U15        |

| GND             | H1         | GND             | N15        | GND             | U16        |

| GND             | H19        | GND             | N16        | GND             | U17        |

| GND             | H26        | GND             | N17        | GND             | V18        |

| GND             | H8         | GND             | N26        | GND             | V9         |

| GND             | J18        | GND             | P1         | GND             | W1         |

| GND             | J9         | GND             | P10        | GND             | W19        |

| GND             | K10        | GND             | P11        | GND             | W26        |

| GND             | K11        | GND             | P12        | GND             | W8         |

| GND             | K12        | GND             | P13        | GND             | Y20        |

| GND             | K13        | GND             | P14        | GND             | Y7         |

| GND             | K14        | GND             | P15        | GND/LP          | C2         |

| GND             | K15        | GND             | P16        | NC              | A25        |

| GND             | K16        | GND             | P17        | NC              | AC13       |

| GND             | K17        | GND             | P26        | NC              | AC14       |

| GND             | L10        | GND             | R10        | NC              | AF2        |

| GND             | L11        | GND             | R11        | NC              | AF25       |

| FG1152          |               | FG1152          |               | FG1152          |               |

|-----------------|---------------|-----------------|---------------|-----------------|---------------|

| AX2000 Function | Pin<br>Number | AX2000 Function | Pin<br>Number | AX2000 Function | Pin<br>Number |

| GND             | AK12          | GND             | AN34          | GND             | D1            |

| GND             | AK17          | GND             | AN4           | GND             | D11           |

| GND             | AK18          | GND             | AN9           | GND             | D2            |

| GND             | AK23          | GND             | AP13          | GND             | D24           |

| GND             | AK30          | GND             | AP2           | GND             | D3            |

| GND             | AK5           | GND             | AP22          | GND             | D31           |

| GND             | AL1           | GND             | AP27          | GND             | D32           |

| GND             | AL11          | GND             | AP3           | GND             | D33           |

| GND             | AL2           | GND             | AP31          | GND             | D34           |

| GND             | AL24          | GND             | AP32          | GND             | D4            |

| GND             | AL3           | GND             | AP33          | GND             | E12           |

| GND             | AL31          | GND             | AP4           | GND             | E17           |

| GND             | AL32          | GND             | AP8           | GND             | E18           |

| GND             | AL33          | GND             | B1            | GND             | E23           |

| GND             | AL34          | GND             | B2            | GND             | E30           |

| GND             | AL4           | GND             | B26           | GND             | E5            |

| GND             | AM1           | GND             | B3            | GND             | F29           |

| GND             | AM10          | GND             | B31           | GND             | F30           |

| GND             | AM15          | GND             | B32           | GND             | F6            |

| GND             | AM2           | GND             | B33           | GND             | G28           |

| GND             | AM20          | GND             | B34           | GND             | G7            |

| GND             | AM25          | GND             | B4            | GND             | H1            |

| GND             | AM3           | GND             | B9            | GND             | H34           |

| GND             | AM31          | GND             | C1            | GND             | J2            |

| GND             | AM32          | GND             | C10           | GND             | J33           |

| GND             | AM33          | GND             | C15           | GND             | K3            |

| GND             | AM34          | GND             | C2            | GND             | K32           |

| GND             | AM4           | GND             | C20           | GND             | L11           |

| GND             | AN1           | GND             | C25           | GND             | L24           |

| GND             | AN2           | GND             | C3            | GND             | L31           |

| GND             | AN26          | GND             | C31           | GND             | L4            |

| GND             | AN3           | GND             | C32           | GND             | M12           |

| GND             | AN31          | GND             | C33           | GND             | M23           |

| GND             | AN32          | GND             | C34           | GND             | M30           |

| GND             | AN33          | GND             | C4            | GND             | M5            |

Package Pin Assignments

## PQ208

## Note

For Package Manufacturing and Environmental information, visit Resource center at http://www.microsemi.com/soc/products/rescenter/package/index.html.

| CQ352            |               | CQ352          |               | CQ352          |               |

|------------------|---------------|----------------|---------------|----------------|---------------|

| AX250 Function   | Pin<br>Number | AX250 Function | Pin<br>Number | AX250 Function | Pin<br>Number |

| Bank 0           | -             | IO24NB1F1      | 275           | Bank 3         |               |

| IO00NB0F0        | 341           | IO24PB1F1      | 276           | IO45NB3F3      | 217           |

| IO00PB0F0        | 342           | IO25NB1F1      | 271           | IO45PB3F3      | 218           |

| IO01NB0F0        | 343           | IO25PB1F1      | 272           | IO46NB3F3      | 219           |

| IO02NB0F0        | 337           | IO27NB1F1      | 269           | IO46PB3F3      | 220           |

| IO02PB0F0        | 338           | IO27PB1F1      | 270           | IO47NB3F3      | 213           |

| IO04NB0F0        | 335           | Bank 2         |               | IO47PB3F3      | 214           |

| IO04PB0F0        | 336           | IO29NB2F2      | 261           | IO48NB3F3      | 211           |

| IO06NB0F0        | 331           | IO29PB2F2      | 262           | IO48PB3F3      | 212           |

| IO06PB0F0        | 332           | IO30NB2F2      | 259           | IO49NB3F3      | 207           |

| IO08NB0F0        | 325           | IO30PB2F2      | 260           | IO49PB3F3      | 208           |

| IO08PB0F0        | 326           | IO31NB2F2      | 255           | IO51NB3F3      | 205           |

| IO10NB0F0        | 323           | IO31PB2F2      | 256           | IO51PB3F3      | 206           |

| IO10PB0F0        | 324           | IO33NB2F2      | 249           | IO52NB3F3      | 201           |

| IO12NB0F0/HCLKAN | 319           | IO33PB2F2      | 250           | IO52PB3F3      | 202           |

| IO12PB0F0/HCLKAP | 320           | IO34NB2F2      | 253           | IO53NB3F3      | 199           |

| IO13NB0F0/HCLKBN | 313           | IO34PB2F2      | 254           | IO53PB3F3      | 200           |

| IO13PB0F0/HCLKBP | 314           | IO35NB2F2      | 247           | IO54NB3F3      | 195           |

| Bank 1           |               | IO35PB2F2      | 248           | IO54PB3F3      | 196           |

| IO14NB1F1/HCLKCN | 305           | IO36NB2F2      | 243           | IO55NB3F3      | 193           |

| IO14PB1F1/HCLKCP | 306           | IO36PB2F2      | 244           | IO55PB3F3      | 194           |

| IO15NB1F1/HCLKDN | 299           | IO37NB2F2      | 241           | IO56NB3F3      | 187           |

| IO15PB1F1/HCLKDP | 300           | IO37PB2F2      | 242           | IO56PB3F3      | 188           |

| IO16NB1F1        | 289           | IO38NB2F2      | 237           | IO57NB3F3      | 189           |

| IO16PB1F1        | 290           | IO38PB2F2      | 238           | IO57PB3F3      | 190           |

| IO17NB1F1        | 295           | IO39NB2F2      | 235           | IO59NB3F3      | 183           |

| IO17PB1F1        | 296           | IO39PB2F2      | 236           | IO59PB3F3      | 184           |

| IO18NB1F1        | 287           | IO41NB2F2      | 231           | IO60NB3F3      | 181           |

| IO18PB1F1        | 288           | IO41PB2F2      | 232           | IO60PB3F3      | 182           |

| IO20NB1F1        | 283           | IO42NB2F2      | 229           | IO61NB3F3      | 179           |

| IO20PB1F1        | 284           | IO42PB2F2      | 230           | IO61PB3F3      | 180           |

| IO22NB1F1        | 277           | IO43NB2F2      | 225           | Bank 4         |               |

| IO22PB1F1        | 278           | IO43PB2F2      | 226           | IO62NB4F4      | 172           |

| IO23NB1F1        | 281           | IO44NB2F2      | 223           | IO62PB4F4      | 173           |

| IO23PB1F1        | 282           | IO44PB2F2      | 224           | IO64NB4F4      | 166           |

## Note

For Package Manufacturing and Environmental information, visit Resource center at http://www.microsemi.com/soc/products/rescenter/package/index.html.

| CG624           |               |  |

|-----------------|---------------|--|

| AX2000 Function | Pin<br>Number |  |

| IO229PB5F21     | AD10          |  |

| IO230NB5F21     | V11           |  |

| IO233NB5F21     | AD7           |  |

| IO233PB5F21     | AD8           |  |

| IO234NB5F21     | V9            |  |

| IO234PB5F21     | V10           |  |

| IO236NB5F22     | AC9           |  |

| IO238NB5F22     | W8            |  |

| IO238PB5F22     | W9            |  |

| IO239NB5F22     | AE4           |  |

| IO239PB5F22     | AE5           |  |

| IO240NB5F22     | AB9           |  |

| IO242NB5F22     | AA9           |  |

| IO242PB5F22     | Y9            |  |

| IO243NB5F22     | AD5           |  |

| IO243PB5F22     | AD6           |  |

| IO244NB5F22     | U8            |  |

| IO246NB5F23     | AB8           |  |

| IO246PB5F23     | AC8           |  |

| IO247NB5F23     | AB7           |  |

| IO247PB5F23     | AC7           |  |

| IO250NB5F23     | AA8           |  |

| IO250PB5F23     | Y8            |  |

| IO251NB5F23     | V8            |  |

| IO251PB5F23     | V7            |  |

| IO252NB5F23     | Y7            |  |

| IO252PB5F23     | W7            |  |

| IO253NB5F23     | AC5           |  |

| IO253PB5F23     | AC6           |  |

| IO254NB5F23     | Y6            |  |

| IO254PB5F23     | W6            |  |

| IO256NB5F23     | AB6*          |  |

| CG624           |               |

|-----------------|---------------|

| AX2000 Function | Pin<br>Number |

| IO256PB5F23     | AA6*          |

| Bank 6          |               |

| IO257NB6F24     | Y3            |

| IO257PB6F24     | AA3           |

| IO258NB6F24     | V3            |

| IO258PB6F24     | W3            |

| IO259NB6F24     | AA2           |

| IO259PB6F24     | AB2           |

| IO260NB6F24     | V6*           |

| IO260PB6F24     | W4*           |

| IO262NB6F24     | U4            |

| IO262PB6F24     | V4            |

| IO263NB6F24     | Y5            |

| IO263PB6F24     | W5            |

| IO268NB6F25     | U6            |

| IO268PB6F25     | U5            |

| IO269PB6F25     | U3            |

| IO272NB6F25     | T2            |

| IO272PB6F25     | U2            |

| IO273NB6F25     | W2            |

| IO273PB6F25     | Y2            |

| IO274NB6F25     | R6            |

| IO274PB6F25     | Т6            |

| IO275NB6F25     | T7            |

| IO275PB6F25     | U7            |

| IO277NB6F25     | V2            |

| IO278NB6F26     | R4            |

| IO278PB6F26     | T4            |

| IO279PB6F26     | R3            |

| IO280NB6F26     | R5            |

| IO281NB6F26     | AA1           |

| IO281PB6F26     | AB1           |

| 00004           |               |  |  |  |

|-----------------|---------------|--|--|--|

| CG624           |               |  |  |  |

| AX2000 Function | Pin<br>Number |  |  |  |

| IO284NB6F26     | R8            |  |  |  |

| IO284PB6F26     | Т8            |  |  |  |

| IO285NB6F26     | W1            |  |  |  |

| IO285PB6F26     | Y1            |  |  |  |

| IO286NB6F26     | P2            |  |  |  |

| IO286PB6F26     | R2            |  |  |  |

| IO287NB6F26     | T1            |  |  |  |

| IO287PB6F26     | U1            |  |  |  |

| IO288NB6F26     | P5            |  |  |  |

| IO290NB6F27     | P6            |  |  |  |

| IO291NB6F27     | P1            |  |  |  |

| IO291PB6F27     | R1            |  |  |  |

| IO292NB6F27     | P7            |  |  |  |

| IO292PB6F27     | R7            |  |  |  |

| IO293NB6F27     | M1            |  |  |  |

| IO293PB6F27     | N1            |  |  |  |

| IO294NB6F27     | P8            |  |  |  |

| IO296NB6F27     | N3            |  |  |  |

| IO296PB6F27     | P3            |  |  |  |

| IO298NB6F27     | N4            |  |  |  |

| IO298PB6F27     | P4            |  |  |  |

| IO299NB6F27     | M2            |  |  |  |

| IO299PB6F27     | N2            |  |  |  |

| Bank 7          |               |  |  |  |

| IO300NB7F28     | P9*           |  |  |  |

| IO300PB7F28     | N6*           |  |  |  |

| IO302NB7F28     | M6            |  |  |  |

| IO304NB7F28     | N8            |  |  |  |

| IO304PB7F28     | N7            |  |  |  |

| IO308NB7F28     | M4            |  |  |  |

| IO309NB7F28     | L3            |  |  |  |

| IO309PB7F28     | M3            |  |  |  |

|                 |               |  |  |  |

Note: \*Not routed on the same package layer and to adjacent LGA pads as its differential pair complement. Recommended to be used as a single-ended I/O. Note: \*Not routed on the same package layer and to adjacent LGA pads as its differential pair complement. Recommended to be used as a single-ended I/O. Note: \*Not routed on the same package layer and to adjacent LGA pads as its differential pair complement. Recommended to be used as a single-ended I/O.

# 4 – Datasheet Information

## **List of Changes**

The following table lists critical changes that were made in the current version of the document.

| Revision                        | Changes                                                                                                                                                                                                                                                                            | Page          |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| Revision 18<br>(March 2012)     | Table 2-1 • Absolute Maximum Ratings was updated to correct the maximum DC core supply voltage (VCCA) from 1.6 V to 1.7 V (SAR 36786). The maximum input voltage (VI) was corrected from 3.75 V to 4.1 V (SAR 35419).                                                              |               |

|                                 | Values for tristate leakage current IOZ, and IIH and IIL were added to Table 2-3<br>• Standby Current (SARs 35774, 32021).                                                                                                                                                         | 2-2           |

|                                 | Figure 2-2 • VCCPLX and VCOMPLX Power Supply Connect was updated to correct the units for the resistance from "W" to $\Omega$ (SAR 36415).                                                                                                                                         | 2-9           |

|                                 | In the Introduction to the "User I/Os" section, the following sentence was added to clarify the slew rate setting (SAR 34943):<br>The slew rate setting is effective for both rising and falling edges.                                                                            | 2-11          |

|                                 | Figure 2-3 • Use of an External Resistor for 5 V Tolerance was revised to show the VCCI and GND clamp diodes. The explanatory text above the figure was revised as well (SAR 34942).                                                                                               | 2-13          |

|                                 | EQ 3 for 5 V tolerance was corrected to change Vdiode from 0.6 V to 0.7 V (SAR 36786).                                                                                                                                                                                             | 2-13          |

|                                 | Additional information was added to the "Using the Weak Pull-Up and Pull-Down Circuits" section to clarify how the weak pull-up and pull-down resistors are physically implemented (SAR 34945).                                                                                    | 2-17          |

|                                 | The description for the C <sub>INCLK</sub> parameter in Table 2-18 • Input Capacitance was changed from "Input capacitance on clock pin" to "Input capacitance on HCLK and RCLK pin" (SAR 34944).                                                                                  | 2-21          |

|                                 | Table 2-19 • I/O Input Rise Time and Fall Time* is new (SAR 34942).                                                                                                                                                                                                                | 2-21          |

| -                               | The minimum VIL for 1.5 V LVCMOS and PCI was corrected from –0.5 to –0.3 in Table 2-29 • DC Input and Output Levels and Table 2-33 • DC Input and Output Levels (SAR 34358).                                                                                                       | 2-38, 2-40    |

|                                 | Support for simulating the GCLR/ GPSET feature in the Axcelerator Family was added in Libero software v9.0 SPI1. Reference to the section explaining this in the <i>Antifuse Macro Library Guide</i> was added to the "R-Cell" section (SAR 26413).                                | 2-58          |

|                                 | The enable signal in Figure 2-32 • R-Cell Delays was corrected to show it is active low rather than active high (SAR 34946).                                                                                                                                                       | 2-59          |

| Revision 17<br>(September 2011) | The versioning system for datasheets has been changed. Datasheets are assigned a revision number that increments each time the datasheet is revised. The "Axcelerator Family Device Status" table indicates the status for each device in the device family.                       | iii           |

|                                 | The "Features" section, "Programmable Interconnect Element" section, and "Security" section were revised to clarify that although no existing security measures can give an absolute guarantee, Microsemi FPGAs implement the best security available in the industry (SAR 32865). | i, 1-1, 2-108 |