Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

### Details

| Details                        |                                                              |

|--------------------------------|--------------------------------------------------------------|

| Product Status                 | Obsolete                                                     |

| Number of LABs/CLBs            | 4224                                                         |

| Number of Logic Elements/Cells | -                                                            |

| Total RAM Bits                 | 55296                                                        |

| Number of I/O                  | 115                                                          |

| Number of Gates                | 250000                                                       |

| Voltage - Supply               | 1.425V ~ 1.575V                                              |

| Mounting Type                  | Surface Mount                                                |

| Operating Temperature          | 0°C ~ 70°C (TA)                                              |

| Package / Case                 | 208-BFQFP                                                    |

| Supplier Device Package        | 208-PQFP (28x28)                                             |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microsemi/ax250-2pqg208 |

|                                |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|           |                                                                      | Dev   | ice Spe   | cific Val | ue (in µW  | /MHz)  |

|-----------|----------------------------------------------------------------------|-------|-----------|-----------|------------|--------|

| Component | Definition                                                           | AX125 | AX250     | AX500     | AX1000     | AX2000 |

| P1        | Core tile HCLK power component                                       | 33    | 49        | 71        | 130        | 216    |

| P2        | R-cell power component                                               | 0.2   | 0.2       | 0.2       | 0.2        | 0.2    |

| P3        | HCLK signal power dissipation                                        | 4.5   | 4.5       | 9         | 13.5       | 18     |

| P4        | Core tile RCLK power component                                       | 33    | 49        | 71        | 130        | 216    |

| P5        | R-cell power component                                               | 0.3   | 0.3       | 0.3       | 0.3        | 0.3    |

| P6        | RCLK signal power dissipation                                        | 6.5   | 6.5       | 13        | 19.5       | 26     |

| P7        | Power dissipation due to the switching activity on the R-cell        | 1.6   | 1.6       | 1.6       | 1.6        | 1.6    |

| P8        | Power dissipation due to the switching activity on the C-cell        | 1.4   | 1.4       | 1.4       | 1.4        | 1.4    |

| P9        | Power component associated with the input voltage                    | 10    | 10        | 10        | 10         | 10     |

| P10       | Power component associated with the output voltage                   | Ś     | See table | e Per pin | contributi | on     |

| P11       | Power component associated with the read operation in the RAM block  | 25    | 25        | 25        | 25         | 25     |

| P12       | Power component associated with the write operation in the RAM block | 30    | 30        | 30        | 30         | 30     |

| P13       | Core PLL power component                                             | 1.5   | 1.5       | 1.5       | 1.5        | 1.5    |

### Table 2-5 • Different Components Contributing to the Total Power Consumption in Axcelerator Devices

#### Ptotal = Pdc + Pac

P<sub>dc</sub> = ICCA \* VCCA

P<sub>ac</sub> = P<sub>HCLK</sub> + P<sub>CLK</sub> + P<sub>R-cells</sub> + P<sub>C-cells</sub> + P<sub>inputs</sub> + P<sub>outputs</sub> + P<sub>memory</sub> + P<sub>PLL</sub>

#### P<sub>HCLK</sub> = (P1 + P2 \* s + P3 \* sqrt[s]) \* Fs

- s = the number of R-cells clocked by this clock

- Fs = the clock frequency

#### PCLK = (P4 + P5 \* s + P6 \* sqrt[s]) \* Fs

- s = the number of R-cells clocked by this clock

- Fs = the clock frequency

#### PR-cells = P7 \* ms \* Fs

- ms = the number of R-cells switching at each Fs cycle

- Fs = the clock frequency

# PC-cells = P8 \* mc \* Fs

- mc = the number of C-cells switching at each Fs cycle

- Fs = the clock frequency

# Pinputs = P9 \* pi \* Fpi

- pi = the number of inputs

- $F_{pi}$  = the average input frequency

# I/O Specifications

# **Pin Descriptions**

**Supply Pins**

GND

VCCA

Ground

Low supply voltage.

Supply Voltage

Supply voltage for array (1.5V). See "Operating Conditions" on page 2-1 for more information.

# VCCIBx Supply Voltage

Supply voltage for I/Os. Bx is the I/O Bank ID – 0 to 7. See "Operating Conditions" on page 2-1 for more information.

# VCCDA Supply Voltage

Supply voltage for the I/O differential amplifier and JTAG and probe interfaces. See "Operating Conditions" on page 2-1 for more information. VCCDA should be tied to 3.3V.

# VCCPLA/B/C/D/E/F/G/H Supply Voltage

PLL analog power supply (1.5V) for internal PLL. There are eight in each device. VCCPLA supports the PLL associated with global resource HCLKA, VCCPLB supports the PLL associated with global resource HCLKB, etc. The PLL analog power supply pins should be connected to 1.5V whether PLL is used or not.

# VCOMPLA/B/C/D/E/F/G/H Supply Voltage

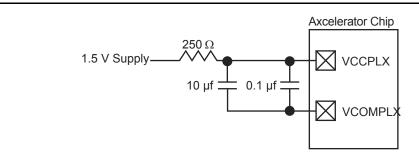

Compensation reference signals for internal PLL. There are eight in each device. **VCOMPLA** supports the PLL associated with global resource HCLKA, VCOMPLE supports the PLL associated with global resource CLKE, etc. (see Figure 2-2 on page 2-9 for correct external connection to the supply). The VCOMPLX pins should be left floating if PLL is not used.

# VPUMP Supply Voltage (External Pump)

In the low power mode, VPUMP will be used to access an external charge pump (if the user desires to bypass the internal charge pump to further reduce power). The device starts using the external charge pump when the voltage level on VPUMP reaches VIH<sup>1</sup>. In normal device operation, when using the internal charge pump, VPUMP should be tied to GND.

Figure 2-2 • VCCPLX and VCOMPLX Power Supply Connect

<sup>1.</sup> When  $V_{PUMP} = V_{IH}$ , it shuts off the internal charge pump. See "Low Power Mode" on page 2-106.

# Using the Differential I/O Standards

Differential I/O macros should be instantiated in the netlist. The settings for these I/O standards cannot be changed inside Designer. Note that there are no tristated or bidirectional I/O buffers for differential standards.

# Using the Voltage-Referenced I/O Standards

Using these I/O standards is similar to that of single-ended I/O standards. Their settings can be changed in Designer.

# Using DDR (Double Data Rate)

In Double Data Rate mode, new data is present on every transition of the clock signal. Clock and data lines have identical bandwidth and signal integrity requirements, making it very efficient for implementing very high-speed systems.

To implement a DDR, users need to:

- 1. Instantiate an input buffer (with the required I/O standard)

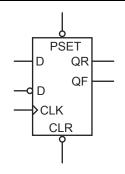

- 2. Instantiate the DDR\_REG macro (Figure 2-6)

- 3. Connect the output from the Input buffer to the input of the DDR macro

Figure 2-6 • DDR Register

# Macros for Specific I/O Standards

There are different macro types for any I/O standard or feature that determine the required VCCI and VREF voltages for an I/O. The generic buffer macros require the LVTTL standard with slow slew rate and 24 mA-drive strength. LVTTL can support high slew rate but this should only be used for critical signals.

Most of the macro symbols represent variations of the six generic symbol types:

- CLKBUF: Clock Buffer

- HCLKBUF: Hardwired Clock Buffer

- INBUF: Input Buffer

- OUTBUF: Output Buffer

- TRIBUF: Tristate Buffer

- BIBUF: Bidirectional Buffer

Other macros include the following:

- Differential I/O standard macros: The LVDS and LVPECL macros either have a pair of differential inputs (e.g. INBUF\_LVDS) or a pair of differential outputs (e.g. OUTBUF\_LVPECL).

- Pull-up and pull-down variations of the INBUF, BIBUF, and TRIBUF macros. These are available only with TTL and LVCMOS thresholds. They can be used to model the behavior of the pull-up and pull-down resistors available in the architecture. Whenever an input pin is left unconnected, the output pin will either go high or low rather than unknown. This allows users to leave inputs unconnected without having the negative effect on simulation of propagating unknowns.

- DDR\_REG macro. It can be connected to any I/O standard input buffers (i.e. INBUF) to implement a double data rate register. Designer software will map it to the I/O module in the same way it maps the other registers to the I/O module.

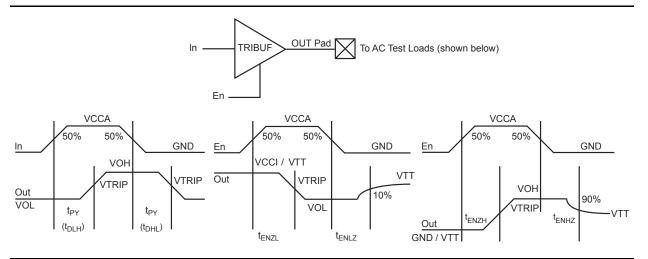

Figure 2-10 • Output Buffer Delays

# Table 2-36 • 3.3 V PCI-X I/O Module

Worst-Case Commercial Conditions VCCA = 1.425 V, VCCI = 3.0 V, T<sub>J</sub> =  $70^{\circ}$ C

|                     |                                                                              | –2 S | peed | –1 S | peed | Std S | Speed |       |

|---------------------|------------------------------------------------------------------------------|------|------|------|------|-------|-------|-------|

| Parameter           | Description                                                                  | Min. | Max. | Min. | Max. | Min.  | Max.  | Units |

| 3.3 V PCI-X         | Output Module Timing                                                         |      |      |      |      |       |       |       |

| t <sub>DP</sub>     | Input Buffer                                                                 |      | 1.57 |      | 1.79 |       | 2.10  | ns    |

| t <sub>PY</sub>     | Output Buffer                                                                |      | 2.10 |      | 2.40 |       | 2.82  | ns    |

| t <sub>ENZL</sub>   | Enable to Pad Delay through the Output Buffer—Z to Low                       |      | 1.61 |      | 1.62 |       | 1.63  | ns    |

| t <sub>ENZH</sub>   | Enable to Pad Delay through the Output Buffer—Z to High                      |      | 1.59 |      | 1.60 |       | 1.61  | ns    |

| t <sub>ENLZ</sub>   | Enable to Pad Delay through the Output Buffer—Low to Z                       |      | 2.65 |      | 3.02 |       | 3.55  | ns    |

| t <sub>ENHZ</sub>   | Enable to Pad Delay through the Output Buffer—High to Z                      |      | 3.11 |      | 3.55 |       | 4.17  | ns    |

| t <sub>IOCLKQ</sub> | Sequential Clock-to-Q for the I/O Input Register                             |      | 0.67 |      | 0.77 |       | 0.90  | ns    |

| t <sub>IOCLKY</sub> | Clock-to-output Y for the I/O Output<br>Register and the I/O Enable Register |      | 0.67 |      | 0.77 |       | 0.90  | ns    |

| t <sub>SUD</sub>    | Data Input Set-Up                                                            |      | 0.23 |      | 0.27 |       | 0.31  | ns    |

| t <sub>SUE</sub>    | Enable Input Set-Up                                                          |      | 0.26 |      | 0.30 |       | 0.35  | ns    |

| t <sub>HD</sub>     | Data Input Hold                                                              |      | 0.00 |      | 0.00 |       | 0.00  | ns    |

| t <sub>HE</sub>     | Enable Input Hold                                                            |      | 0.00 |      | 0.00 |       | 0.00  | ns    |

| t <sub>CPWHL</sub>  | Clock Pulse Width High to Low                                                | 0.39 |      | 0.39 |      | 0.39  |       | ns    |

| t <sub>CPWLH</sub>  | Clock Pulse Width Low to High                                                | 0.39 |      | 0.39 |      | 0.39  |       | ns    |

| t <sub>WASYN</sub>  | Asynchronous Pulse Width                                                     | 0.37 |      | 0.37 |      | 0.37  |       | ns    |

| t <sub>REASYN</sub> | Asynchronous Recovery Time                                                   |      | 0.13 |      | 0.15 |       | 0.17  | ns    |

| t <sub>HASYN</sub>  | Asynchronous Removal Time                                                    |      | 0.00 |      | 0.00 |       | 0.00  | ns    |

| t <sub>CLR</sub>    | Asynchronous Clear-to-Q                                                      |      | 0.23 |      | 0.27 |       | 0.31  | ns    |

| t <sub>PRESET</sub> | Asynchronous Preset-to-Q                                                     |      | 0.23 |      | 0.27 |       | 0.31  | ns    |

# **Timing Characteristics**

# *Table 2-61* • LVPECL I/O Module Worst-Case Commercial Conditions VCCA = 1.425 V, VCCI = 3.0 V, T<sub>J</sub> = 70°C

|                     |                                                                   | –2 S | peed | –1 S | peed | Std S | peed |       |

|---------------------|-------------------------------------------------------------------|------|------|------|------|-------|------|-------|

| Parameter           | Description                                                       | Min. | Max. | Min. | Max. | Min.  | Max. | Units |

| LVPECL Ou           | itput Module Timing                                               |      |      |      |      |       |      |       |

| t <sub>DP</sub>     | Input Buffer                                                      |      | 1.66 |      | 1.89 |       | 2.22 | ns    |

| t <sub>PY</sub>     | Output Buffer                                                     |      | 2.24 |      | 2.55 |       | 3.00 | ns    |

| t <sub>ICLKQ</sub>  | Clock-to-Q for the I/O input register                             |      | 0.67 |      | 0.77 |       | 0.90 | ns    |

| t <sub>oclkq</sub>  | Clock-to-Q for the IO output register and the I/O enable register |      | 0.67 |      | 0.77 |       | 0.90 | ns    |

| t <sub>SUD</sub>    | Data Input Set-Up                                                 |      | 0.23 |      | 0.27 |       | 0.31 | ns    |

| t <sub>SUE</sub>    | Enable Input Set-Up                                               |      | 0.26 |      | 0.30 |       | 0.35 | ns    |

| t <sub>HD</sub>     | Data Input Hold                                                   |      | 0.00 |      | 0.00 |       | 0.00 | ns    |

| t <sub>HE</sub>     | Enable Input Hold                                                 |      | 0.00 |      | 0.00 |       | 0.00 | ns    |

| t <sub>CPWHL</sub>  | Clock Pulse Width High to Low                                     | 0.39 |      | 0.39 |      | 0.39  |      | ns    |

| t <sub>CPWLH</sub>  | Clock Pulse Width Low to High                                     | 0.39 |      | 0.39 |      | 0.39  |      | ns    |

| t <sub>WASYN</sub>  | Asynchronous Pulse Width                                          | 0.37 |      | 0.37 |      | 0.37  |      | ns    |

| t <sub>REASYN</sub> | Asynchronous Recovery Time                                        |      | 0.13 |      | 0.15 |       | 0.17 | ns    |

| t <sub>HASYN</sub>  | Asynchronous Removal Time                                         |      | 0.00 |      | 0.00 |       | 0.00 | ns    |

| t <sub>CLR</sub>    | Asynchronous Clear-to-Q                                           |      | 0.23 |      | 0.27 |       | 0.31 | ns    |

| t <sub>PRESET</sub> | Asynchronous Preset-to-Q                                          |      | 0.23 |      | 0.27 |       | 0.31 | ns    |

# **Timing Characteristics**

Table 2-65 • AX125 Predicted Routing Delays Worst-Case Commercial Conditions VCCA = 1.425 V, T<sub>J</sub> = 70°C

|                   |                                  | -2 Speed | -1 Speed | Std Speed |       |

|-------------------|----------------------------------|----------|----------|-----------|-------|

| Parameter         | Description                      | Typical  | Typical  | Typical   | Units |

| Predicted R       | Routing Delays                   |          |          |           |       |

| t <sub>DC</sub>   | DirectConnect Routing Delay, FO1 | 0.11     | 0.12     | 0.15      | ns    |

| t <sub>FC</sub>   | FastConnect Routing Delay, FO1   | 0.35     | 0.39     | 0.46      | ns    |

| t <sub>RD1</sub>  | Routing delay for FO1            | 0.35     | 0.40     | 0.47      | ns    |

| t <sub>RD2</sub>  | Routing delay for FO2            | 0.38     | 0.43     | 0.51      | ns    |

| t <sub>RD3</sub>  | Routing delay for FO3            | 0.43     | 0.48     | 0.57      | ns    |

| t <sub>RD4</sub>  | Routing delay for FO4            | 0.48     | 0.55     | 0.64      | ns    |

| t <sub>RD5</sub>  | Routing delay for FO5            | 0.55     | 0.62     | 0.73      | ns    |

| t <sub>RD6</sub>  | Routing delay for FO6            | 0.64     | 0.72     | 0.85      | ns    |

| t <sub>RD7</sub>  | Routing delay for FO7            | 0.79     | 0.89     | 1.05      | ns    |

| t <sub>RD8</sub>  | Routing delay for FO8            | 0.88     | 0.99     | 1.17      | ns    |

| t <sub>RD16</sub> | Routing delay for FO16           | 1.49     | 1.69     | 1.99      | ns    |

| t <sub>RD32</sub> | Routing delay for FO32           | 2.32     | 2.63     | 3.10      | ns    |

# Table 2-66 • AX250 Predicted Routing Delays

# Worst-Case Commercial Conditions VCCA = $1.425 \text{ V}, \text{ T}_{\text{J}} = 70^{\circ}\text{C}$

|                   |                                  | -2 Speed | -1 Speed | Std Speed |       |

|-------------------|----------------------------------|----------|----------|-----------|-------|

| Parameter         | Description                      | Typical  | Typical  | Typical   | Units |

| Predicted F       | Routing Delays                   |          |          |           |       |

| t <sub>DC</sub>   | DirectConnect Routing Delay, FO1 | 0.11     | 0.12     | 0.15      | ns    |

| t <sub>FC</sub>   | FastConnect Routing Delay, FO1   | 0.35     | 0.39     | 0.46      | ns    |

| t <sub>RD1</sub>  | Routing delay for FO1            | 0.39     | 0.45     | 0.53      | ns    |

| t <sub>RD2</sub>  | Routing delay for FO2            | 0.41     | 0.46     | 0.54      | ns    |

| t <sub>RD3</sub>  | Routing delay for FO3            | 0.48     | 0.55     | 0.64      | ns    |

| t <sub>RD4</sub>  | Routing delay for FO4            | 0.56     | 0.63     | 0.75      | ns    |

| t <sub>RD5</sub>  | Routing delay for FO5            | 0.60     | 0.68     | 0.80      | ns    |

| t <sub>RD6</sub>  | Routing delay for FO6            | 0.84     | 0.96     | 1.13      | ns    |

| t <sub>RD7</sub>  | Routing delay for FO7            | 0.90     | 1.02     | 1.20      | ns    |

| t <sub>RD8</sub>  | Routing delay for FO8            | 1.00     | 1.13     | 1.33      | ns    |

| t <sub>RD16</sub> | Routing delay for FO16           | 2.17     | 2.46     | 2.89      | ns    |

| t <sub>RD32</sub> | Routing delay for FO32           | 3.55     | 4.03     | 4.74      | ns    |

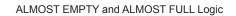

Figure 2-63 illustrates flag generation.

# Figure 2-63 • ALMOST-EMPTY and ALMOST-FULL Logic

The Verilog codes for the flags are:

assign AF = (DIFF[15:0] >={AFVAL[7:0],8'b00000000})?1:0; assign AE = ({AEVAL[7:0],8'b00000000}>=DIFF[15:0])?1:0;

The number of DIFF-bits active depends on the configuration depth and width (Table 2-95).

### Table 2-95 • Number of Available Configuration Bits

| Number of Blocks | Block DxW | Number of AEVAL/AFVAL Bits |

|------------------|-----------|----------------------------|

| 1                | 1x1       | 4                          |

| 2                | 1x2       | 4                          |

| 2                | 2x1       | 5                          |

| 4                | 1x4       | 4                          |

| 4                | 2x2       | 5                          |

| 4                | 4x1       | 6                          |

| 8                | 1x8       | 4                          |

| 8                | 2x4       | 5                          |

| 8                | 4x2       | 6                          |

| 8                | 8x1       | 7                          |

| 16               | 1x16      | 4                          |

| 16               | 2x8       | 5                          |

| 16               | 4x4       | 6                          |

| 16               | 8x2       | 7                          |

| 16               | 16x1      | 8                          |

The active-high CLR pin is used to reset the FIFO to the empty state, which sets FULL and AFULL low, and EMPTY and AEMPTY high.

Assuming that the EMPTY flag is not set, new data is read from the FIFO when REN is valid on the active edge of the clock. Write and read transfers are described with timing requirements in "Timing Characteristics" on page 2-100.

# Table 2-98 • One FIFO Block

# Worst-Case Commercial Conditions VCCA = 1.425 V, VCCI = 3.0 V, T<sub>J</sub> = $70^{\circ}$ C

|                      |                              | –2 S | peed  | –1 S | peed  | Std S | Speed |       |

|----------------------|------------------------------|------|-------|------|-------|-------|-------|-------|

| Parameter            | Description                  | Min. | Max.  | Min. | Max.  | Min.  | Max.  | Units |

| FIFO Module          | Timing                       |      |       |      |       |       |       |       |

| t <sub>WSU</sub>     | Write Setup                  |      | 11.40 |      | 12.98 |       | 15.26 | ns    |

| t <sub>WHD</sub>     | Write Hold                   |      | 0.22  |      | 0.25  |       | 0.30  | ns    |

| t <sub>WCKH</sub>    | WCLK High                    |      | 0.75  |      | 0.75  |       | 0.75  | ns    |

| t <sub>WCKL</sub>    | WCLK Low                     |      | 0.88  |      | 0.88  |       | 0.88  | ns    |

| t <sub>WCKP</sub>    | Minimum WCLK Period          | 1.63 |       | 1.63 |       | 1.63  |       | ns    |

| t <sub>RSU</sub>     | Read Setup                   |      | 11.63 |      | 13.25 |       | 15.58 | ns    |

| t <sub>RHD</sub>     | Read Hold                    |      | 0.00  |      | 0.00  |       | 0.00  | ns    |

| t <sub>RCKH</sub>    | RCLK High                    |      | 0.77  |      | 0.77  |       | 0.77  | ns    |

| t <sub>RCKL</sub>    | RCLK Low                     |      | 0.93  |      | 0.93  |       | 0.93  | ns    |

| t <sub>RCKP</sub>    | Minimum RCLK period          | 1.70 |       | 1.70 |       | 1.70  |       | ns    |

| t <sub>CLRHF</sub>   | Clear High                   |      | 0.00  |      | 0.00  |       | 0.00  | ns    |

| t <sub>CLR2FF</sub>  | Clear-to-flag (EMPTY/FULL)   |      | 1.92  |      | 2.18  |       | 2.57  | ns    |

| t <sub>CLR2AF</sub>  | Clear-to-flag (AEMPTY/AFULL) |      | 4.39  |      | 5.00  |       | 5.88  | ns    |

| t <sub>CK2FF</sub>   | Clock-to-flag (EMPTY/FULL)   |      | 2.13  |      | 2.42  |       | 2.85  | ns    |

| t <sub>CK2AF</sub>   | Clock-to-flag (AEMPTY/AFULL) |      | 5.04  |      | 5.75  |       | 6.75  | ns    |

| t <sub>RCK2RD1</sub> | RCLK-To-OUT (Pipelined)      |      | 1.32  |      | 1.51  |       | 1.77  | ns    |

| t <sub>RCK2RD2</sub> | RCLK-To-OUT (Non-Pipelined)  |      | 2.16  |      | 2.46  |       | 2.90  | ns    |

Note: Timing data for this single block FIFO has a depth of 4,096. For all other combinations, use Microsemi's timing software.

# Table 2-100 • Four FIFO Blocks Cascaded

Worst-Case Commercial Conditions VCCA = 1.425 V, VCCI = 3.0 V, T<sub>J</sub> =  $70^{\circ}\text{C}$

|                      |                              | –2 S | peed  | –1 S | peed  | Std S | Speed |       |

|----------------------|------------------------------|------|-------|------|-------|-------|-------|-------|

| Parameter            | Description                  | Min. | Max.  | Min. | Max.  | Min.  | Max.  | Units |

| FIFO Module          | Timing                       |      |       |      |       |       |       |       |

| t <sub>WSU</sub>     | Write Setup                  |      | 14.60 |      | 16.63 |       | 19.55 | ns    |

| t <sub>WHD</sub>     | Write Hold                   |      | 0.00  |      | 0.00  |       | 0.00  | ns    |

| t <sub>WCKH</sub>    | WCLK High                    |      | 0.75  |      | 0.75  |       | 0.75  | ns    |

| t <sub>WCKL</sub>    | WCLK Low                     |      | 2.51  |      | 2.51  |       | 2.51  | ns    |

| t <sub>WCKP</sub>    | Minimum WCLK Period          | 3.26 |       | 3.26 |       | 3.26  |       | ns    |

| t <sub>RSU</sub>     | Read Setup                   |      | 15.27 |      | 17.39 |       | 20.44 | ns    |

| t <sub>RHD</sub>     | Read Hold                    |      | 0.00  |      | 0.00  |       | 0.00  | ns    |

| t <sub>RCKH</sub>    | RCLK High                    |      | 0.73  |      | 0.73  |       | 0.73  | ns    |

| t <sub>RCKL</sub>    | RCLK Low                     |      | 2.96  |      | 2.96  |       | 2.96  | ns    |

| t <sub>RCKP</sub>    | Minimum RCLK period          | 3.69 |       | 3.69 |       | 3.69  |       | ns    |

| t <sub>CLRHF</sub>   | Clear High                   |      | 0.00  |      | 0.00  |       | 0.00  | ns    |

| t <sub>CLR2FF</sub>  | Clear-to-flag (EMPTY/FULL)   |      | 1.92  |      | 2.18  |       | 2.57  | ns    |

| t <sub>CLR2AF</sub>  | Clear-to-flag (AEMPTY/AFULL) |      | 4.39  |      | 5.00  |       | 5.88  | ns    |

| t <sub>CK2FF</sub>   | Clock-to-flag (EMPTY/FULL)   |      | 2.13  |      | 2.42  |       | 2.85  | ns    |

| t <sub>CK2AF</sub>   | Clock-to-flag (AEMPTY/AFULL) |      | 5.04  |      | 5.75  |       | 6.75  | ns    |

| t <sub>RCK2RD1</sub> | RCLK-To-OUT (Pipelined)      |      | 2.36  |      | 2.69  |       | 3.16  | ns    |

| t <sub>RCK2RD2</sub> | RCLK-To-OUT (Nonpipelined)   |      | 2.83  |      | 3.23  |       | 3.79  | ns    |

Note: Timing data for these four cascaded FIFO blocks uses a depth of 16,384. For all other combinations, use Microsemi's timing software.

Microsemi

| FG484          | 4          | FG48           | 4          | FG48           | 34         |

|----------------|------------|----------------|------------|----------------|------------|

| AX250 Function | Pin Number | AX250 Function | Pin Number | AX250 Function | Pin Number |

| IO104PB6F6     | N4         | IO122NB7F7     | G5         | GND            | J9         |

| IO105NB6F6     | M5         | IO122PB7F7     | G6         | GND            | K10        |

| IO105PB6F6     | N5         | IO123NB7F7     | F5         | GND            | K11        |

| IO106NB6F6     | M3         | IO123PB7F7     | E4         | GND            | K12        |

| IO106PB6F6     | N3         | Dedicate       | d I/O      | GND            | K13        |

| Bank           | 7          | VCCDA          | H7         | GND            | L1         |

| IO107NB7F7     | M2         | GND            | A1         | GND            | L10        |

| IO107PB7F7     | N1         | GND            | A11        | GND            | L11        |

| IO108NB7F7     | L3         | GND            | A12        | GND            | L12        |

| IO108PB7F7     | L2         | GND            | A2         | GND            | L13        |

| IO109NB7F7     | K2         | GND            | A21        | GND            | L22        |

| IO109PB7F7     | K1         | GND            | A22        | GND            | M1         |

| IO110NB7F7     | K5         | GND            | AA1        | GND            | M10        |

| IO110PB7F7     | L5         | GND            | AA2        | GND            | M11        |

| IO111NB7F7     | K6         | GND            | AA21       | GND            | M12        |

| IO111PB7F7     | L6         | GND            | AA22       | GND            | M13        |

| IO112NB7F7     | K4         | GND            | AB1        | GND            | M22        |

| IO112PB7F7     | K3         | GND            | AB11       | GND            | N10        |

| IO113NB7F7     | K7         | GND            | AB12       | GND            | N11        |

| IO113PB7F7     | L7         | GND            | AB2        | GND            | N12        |

| IO114NB7F7     | H1         | GND            | AB21       | GND            | N13        |

| IO114PB7F7     | J1         | GND            | AB22       | GND            | P14        |

| IO115NB7F7     | H2         | GND            | B1         | GND            | P9         |

| IO115PB7F7     | J2         | GND            | B2         | GND            | R15        |

| IO116NB7F7     | H4         | GND            | B21        | GND            | R8         |

| IO116PB7F7     | J4         | GND            | B22        | GND            | U16        |

| IO117NB7F7     | H5         | GND            | C20        | GND            | U6         |

| IO117PB7F7     | J5         | GND            | C3         | GND            | V18        |

| IO118NB7F7     | F2         | GND            | D19        | GND            | V5         |

| IO118PB7F7     | G2         | GND            | D4         | GND            | W19        |

| IO119NB7F7     | H6         | GND            | E18        | GND            | W4         |

| IO119PB7F7     | J6         | GND            | E5         | GND            | Y20        |

| IO120NB7F7     | F1         | GND            | G18        | GND            | Y3         |

| IO120PB7F7     | G1         | GND            | H15        | GND/LP         | G7         |

| IO121NB7F7     | F4         | GND            | H8         | NC             | A17        |

| IO121PB7F7     | G4         | GND            | J14        | NC             | A18        |

Microsemi

| FG48           | 4          | FG48           | 4          |

|----------------|------------|----------------|------------|

| AX250 Function | Pin Number | AX250 Function | Pin Number |

| VCCPLH         | T10        | VCCIB4         | R14        |

| VCCDA          | D14        | VCCIB5         | AA3        |

| VCCDA          | D5         | VCCIB5         | AB3        |

| VCCDA          | F16        | VCCIB5         | R10        |

| VCCDA          | G12        | VCCIB5         | R11        |

| VCCDA          | L4         | VCCIB5         | R9         |

| VCCDA          | M18        | VCCIB6         | M8         |

| VCCDA          | T11        | VCCIB6         | N8         |

| VCCDA          | T17        | VCCIB6         | P8         |

| VCCDA          | U7         | VCCIB6         | Y1         |

| VCCDA          | V14        | VCCIB6         | Y2         |

| VCCDA          | V8         | VCCIB7         | C1         |

| VCCIB0         | A3         | VCCIB7         | C2         |

| VCCIB0         | B3         | VCCIB7         | J8         |

| VCCIB0         | H10        | VCCIB7         | K8         |

| VCCIB0         | H11        | VCCIB7         | L8         |

| VCCIB0         | H9         | VCOMPLA        | D10        |

| VCCIB1         | A20        | VCOMPLB        | G10        |

| VCCIB1         | B20        | VCOMPLC        | E12        |

| VCCIB1         | H12        | VCOMPLD        | G14        |

| VCCIB1         | H13        | VCOMPLE        | W13        |

| VCCIB1         | H14        | VCOMPLF        | T13        |

| VCCIB2         | C21        | VCOMPLG        | V11        |

| VCCIB2         | C22        | VCOMPLH        | Т9         |

| VCCIB2         | J15        | VPUMP          | D17        |

| VCCIB2         | K15        | L              |            |

| VCCIB2         | L15        |                |            |

| VCCIB3         | M15        |                |            |

| VCCIB3         | N15        |                |            |

| VCCIB3         | P15        |                |            |

| VCCIB3         | Y21        |                |            |

| VCCIB3         | Y22        |                |            |

| VCCIB4         | AA20       |                |            |

| VCCIB4         | AB20       |                |            |

| VCCIB4         | R12        |                |            |

| VCCIB4         | R13        |                |            |

| FG484          |               | FG484          |               |

|----------------|---------------|----------------|---------------|

| AX500 Function | Pin<br>Number | AX500 Function | Pin<br>Number |

| VCCA           | P11           | VCCIB2         | C22           |

| VCCA           | P12           | VCCIB2         | J15           |

| VCCA           | P13           | VCCIB2         | K15           |

| VCCA           | Т6            | VCCIB2         | L15           |

| VCCA           | U17           | VCCIB3         | M15           |

| VCCPLA         | F10           | VCCIB3         | N15           |

| VCCPLB         | G9            | VCCIB3         | P15           |

| VCCPLC         | D13           | VCCIB3         | Y21           |

| VCCPLD         | G13           | VCCIB3         | Y22           |

| VCCPLE         | U13           | VCCIB4         | AA20          |

| VCCPLF         | T14           | VCCIB4         | AB20          |

| VCCPLG         | W10           | VCCIB4         | R12           |

| VCCPLH         | T10           | VCCIB4         | R13           |

| VCCDA          | D14           | VCCIB4         | R14           |

| VCCDA          | D5            | VCCIB5         | AA3           |

| VCCDA          | F16           | VCCIB5         | AB3           |

| VCCDA          | G12           | VCCIB5         | R10           |

| VCCDA          | L4            | VCCIB5         | R11           |

| VCCDA          | M18           | VCCIB5         | R9            |

| VCCDA          | T11           | VCCIB6         | M8            |

| VCCDA          | T17           | VCCIB6         | N8            |

| VCCDA          | U7            | VCCIB6         | P8            |

| VCCDA          | V14           | VCCIB6         | Y1            |

| VCCDA          | V8            | VCCIB6         | Y2            |

| VCCIB0         | A3            | VCCIB7         | C1            |

| VCCIB0         | B3            | VCCIB7         | C2            |

| VCCIB0         | H10           | VCCIB7         | J8            |

| VCCIB0         | H11           | VCCIB7         | K8            |

| VCCIB0         | H9            | VCCIB7         | L8            |

| VCCIB1         | A20           | VCOMPLA        | D10           |

| VCCIB1         | B20           | VCOMPLB        | G10           |

| VCCIB1         | H12           | VCOMPLC        | E12           |

| VCCIB1         | H13           | VCOMPLD        | G14           |

| VCCIB1         | H14           | VCOMPLE        | W13           |

| VCCIB2         | C21           | VCOMPLF        | T13           |

| FG484          |               |  |  |

|----------------|---------------|--|--|

| AX500 Function | Pin<br>Number |  |  |

| VCOMPLG        | V11           |  |  |

| VCOMPLH        | Т9            |  |  |

| VPUMP          | D17           |  |  |

| FG484           |               | FG484           |               | FG484           |               |

|-----------------|---------------|-----------------|---------------|-----------------|---------------|

| AX1000 Function | Pin<br>Number | AX1000 Function | Pin<br>Number | AX1000 Function | Pin<br>Number |

| IO246NB7F22     | F3            | GND             | D4            | GND             | V5            |

| IO246PB7F22     | G3            | GND             | E18           | GND             | W19           |

| IO250NB7F23     | F4            | GND             | E5            | GND             | W4            |

| IO250PB7F23     | G4            | GND             | G18           | GND             | Y20           |

| IO253NB7F23     | G5            | GND             | H15           | GND             | Y3            |

| IO253PB7F23     | G6            | GND             | H8            | GND/LP          | G7            |

| IO254NB7F23     | D1            | GND             | J14           | PRA             | G11           |

| IO254PB7F23     | E1            | GND             | J9            | PRB             | F11           |

| IO257NB7F23     | F5            | GND             | K10           | PRC             | T12           |

| IO257PB7F23     | E4            | GND             | K11           | PRD             | U12           |

| Dedicated I/    | 0             | GND             | K12           | ТСК             | G8            |

| VCCDA           | H7            | GND             | K13           | TDI             | F9            |

| GND             | A1            | GND             | L1            | TDO             | F7            |

| GND             | A11           | GND             | L10           | TMS             | F6            |

| GND             | A12           | GND             | L11           | TRST            | F8            |

| GND             | A2            | GND             | L12           | VCCA            | G17           |

| GND             | A21           | GND             | L13           | VCCA            | J10           |

| GND             | A22           | GND             | L22           | VCCA            | J11           |

| GND             | AA1           | GND             | M1            | VCCA            | J12           |

| GND             | AA2           | GND             | M10           | VCCA            | J13           |

| GND             | AA21          | GND             | M11           | VCCA            | J7            |

| GND             | AA22          | GND             | M12           | VCCA            | K14           |

| GND             | AB1           | GND             | M13           | VCCA            | K9            |

| GND             | AB11          | GND             | M22           | VCCA            | L14           |

| GND             | AB12          | GND             | N10           | VCCA            | L9            |

| GND             | AB2           | GND             | N11           | VCCA            | M14           |

| GND             | AB21          | GND             | N12           | VCCA            | M9            |

| GND             | AB22          | GND             | N13           | VCCA            | N14           |

| GND             | B1            | GND             | P14           | VCCA            | N9            |

| GND             | B2            | GND             | P9            | VCCA            | P10           |

| GND             | B21           | GND             | R15           | VCCA            | P11           |

| GND             | B22           | GND             | R8            | VCCA            | P12           |

| GND             | C20           | GND             | U16           | VCCA            | P13           |

| GND             | C3            | GND             | U6            | VCCA            | Т6            |

| GND             | D19           | GND             | V18           | VCCA            | U17           |

| FG1152          |               | FG1152          |               | FG1152                     |     |

|-----------------|---------------|-----------------|---------------|----------------------------|-----|

| AX2000 Function | Pin<br>Number | AX2000 Function | Pin<br>Number | Pin<br>AX2000 Function Num |     |

| Bank 0          |               | IO17NB0F1       | F12           | IO34PB0F3                  | D14 |

| IO00NB0F0       | D6            | IO17PB0F1       | F11           | IO35NB0F3                  | A15 |

| IO00PB0F0       | C6            | IO18NB0F1       | E11           | IO35PB0F3                  | B15 |

| IO01NB0F0       | H10           | IO18PB0F1       | E10           | IO36NB0F3                  | B16 |

| IO01PB0F0       | H9            | IO19NB0F1       | F13           | IO36PB0F3                  | A16 |

| IO02NB0F0       | F8            | IO19PB0F1       | G13           | IO37NB0F3                  | G16 |

| IO02PB0F0       | G8            | IO20NB0F1       | A10           | IO37PB0F3                  | G15 |

| IO03NB0F0       | A6            | IO20PB0F1       | A9            | IO38NB0F3                  | D16 |

| IO03PB0F0       | B6            | IO21NB0F1       | K14           | IO38PB0F3                  | C16 |

| IO04NB0F0       | C7            | IO21PB0F1       | K13           | IO39NB0F3                  | K16 |

| IO04PB0F0       | D7            | IO22NB0F2       | B11           | IO39PB0F3                  | L16 |

| IO05NB0F0       | K10           | IO22PB0F2       | B10           | IO40NB0F3                  | D17 |

| IO05PB0F0       | J10           | IO23NB0F2       | C12           | IO40PB0F3                  | C17 |

| IO06NB0F0       | F9            | IO23PB0F2       | C11           | IO41NB0F3/HCLKAN           | E16 |

| IO06PB0F0       | G9            | IO24NB0F2       | A12           | IO41PB0F3/HCLKAP           | F16 |

| IO07NB0F0       | F10           | IO24PB0F2       | A11           | IO42NB0F3/HCLKBN           | G17 |

| IO07PB0F0       | G10           | IO25NB0F2       | H14           | IO42PB0F3/HCLKBP           | F17 |

| IO08NB0F0       | E9            | IO25PB0F2       | J14           | Bank 1                     |     |

| IO08PB0F0       | E8            | IO26NB0F2       | D13           | IO43NB1F4/HCLKCN           | G19 |

| IO09NB0F0       | J11           | IO26PB0F2       | D12           | IO43PB1F4/HCLKCP           | G18 |

| IO09PB0F0       | K11           | IO27NB0F2       | F14           | IO44NB1F4/HCLKDN           | E19 |

| IO10NB0F0       | C8            | IO27PB0F2       | G14           | IO44PB1F4/HCLKDP           | F19 |

| IO10PB0F0       | D8            | IO28NB0F2       | E14           | IO45NB1F4                  | C18 |

| IO11NB0F0       | K12           | IO28PB0F2       | E13           | IO45PB1F4                  | D18 |

| IO11PB0F0       | J12           | IO29NB0F2       | B13           | IO46NB1F4                  | A18 |

| IO12NB0F1       | G11           | IO29PB0F2       | B12           | IO46PB1F4                  | B18 |

| IO12PB0F1       | H11           | IO30NB0F2       | C14           | IO47NB1F4                  | K19 |

| IO13NB0F1       | G12           | IO30PB0F2       | C13           | IO47PB1F4                  | L19 |

| IO13PB0F1       | H12           | IO31NB0F2       | H15           | IO48NB1F4                  | C19 |

| IO14NB0F1       | A7            | IO31PB0F2       | J15           | IO48PB1F4                  | D19 |

| IO14PB0F1       | B7            | IO32NB0F2       | A14           | IO49NB1F4                  | K20 |

| IO15NB0F1       | H13           | IO32PB0F2       | B14           | IO49PB1F4                  | L20 |

| IO15PB0F1       | J13           | IO33NB0F2       | K15           | IO50NB1F4                  | A19 |

| IO16NB0F1       | C9            | IO33PB0F2       | L15           | IO50PB1F4                  | B19 |

| IO16PB0F1       | D9            | IO34NB0F3       | D15           | IO51NB1F4                  | H20 |

| CQ352           |               | CQ352          |               | CQ352          |               |

|-----------------|---------------|----------------|---------------|----------------|---------------|

| AX250 Function  | Pin<br>Number | AX250 Function | Pin<br>Number | AX250 Function | Pin<br>Number |

| IO64PB4F4       | 167           | IO85PB5F5      | 105           | IO106NB6F6     | 46            |

| IO65NB4F4       | 170           | IO86NB5F5      | 98            | IO106PB6F6     | 47            |

| IO65PB4F4       | 171           | IO86PB5F5      | 99            | Bank 7         |               |

| IO66NB4F4       | 164           | IO87NB5F5      | 94            | IO107NB7F7     | 40            |

| IO66PB4F4       | 165           | IO87PB5F5      | 95            | IO107PB7F7     | 41            |

| IO67NB4F4       | 160           | IO89NB5F5      | 92            | IO108NB7F7     | 42            |

| IO67PB4F4       | 161           | IO89PB5F5      | 93            | IO108PB7F7     | 43            |

| IO68NB4F4       | 158           | Bank 6         |               | IO109NB7F7     | 36            |

| IO68PB4F4       | 159           | IO90PB6F6      | 86            | IO109PB7F7     | 37            |

| IO70NB4F4       | 154           | IO91NB6F6      | 84            | IO110NB7F7     | 34            |

| IO70PB4F4       | 155           | IO91PB6F6      | 85            | IO110PB7F7     | 35            |

| IO72NB4F4       | 152           | IO92NB6F6      | 78            | IO111NB7F7     | 30            |

| IO72PB4F4       | 153           | IO92PB6F6      | 79            | IO111PB7F7     | 31            |

| IO73NB4F4       | 146           | IO93NB6F6      | 82            | IO113NB7F7     | 28            |

| IO73PB4F4       | 147           | IO93PB6F6      | 83            | IO113PB7F7     | 29            |

| IO74NB4F4/CLKEN | 142           | IO95NB6F6      | 76            | IO114NB7F7     | 24            |

| IO74PB4F4/CLKEP | 143           | IO95PB6F6      | 77            | IO114PB7F7     | 25            |

| IO75NB4F4/CLKFN | 136           | IO96NB6F6      | 72            | IO115NB7F7     | 22            |

| IO75PB4F4/CLKFP | 137           | IO96PB6F6      | 73            | IO115PB7F7     | 23            |

| Bank 5          |               | IO97NB6F6      | 70            | IO116NB7F7     | 18            |

| IO76NB5F5/CLKGN | 128           | IO97PB6F6      | 71            | IO116PB7F7     | 19            |

| IO76PB5F5/CLKGP | 129           | IO98NB6F6      | 66            | IO117NB7F7     | 16            |

| IO77NB5F5/CLKHN | 122           | IO98PB6F6      | 67            | IO117PB7F7     | 17            |

| IO77PB5F5/CLKHP | 123           | IO99NB6F6      | 64            | IO118NB7F7     | 12            |

| IO78NB5F5       | 112           | IO99PB6F6      | 65            | IO118PB7F7     | 13            |

| IO78PB5F5       | 113           | IO100NB6F6     | 60            | IO119NB7F7     | 10            |

| IO79NB5F5       | 118           | IO100PB6F6     | 61            | IO119PB7F7     | 11            |

| IO79PB5F5       | 119           | IO101NB6F6     | 58            | IO121NB7F7     | 6             |

| IO80NB5F5       | 110           | IO101PB6F6     | 59            | IO121PB7F7     | 7             |

| IO80PB5F5       | 111           | IO103NB6F6     | 54            | IO123NB7F7     | 4             |

| IO82NB5F5       | 106           | IO103PB6F6     | 55            | IO123PB7F7     | 5             |

| IO82PB5F5       | 107           | IO104NB6F6     | 52            | Dedicated I/C  | )             |

| IO84NB5F5       | 100           | IO104PB6F6     | 53            | GND            | 1             |

| IO84PB5F5       | 101           | IO105NB6F6     | 48            | GND            | 9             |

| IO85NB5F5       | 104           | IO105PB6F6     | 49            | GND            | 15            |

| CQ352           |               |  |  |

|-----------------|---------------|--|--|

| AX1000 Function | Pin<br>Number |  |  |

| VCCDA           | 346           |  |  |

| VCCIB0          | 321           |  |  |

| VCCIB0          | 333           |  |  |

| VCCIB0          | 344           |  |  |

| VCCIB1          | 273           |  |  |

| VCCIB1          | 285           |  |  |

| VCCIB1          | 297           |  |  |

| VCCIB2          | 227           |  |  |

| VCCIB2          | 239           |  |  |

| VCCIB2          | 245           |  |  |

| VCCIB2          | 257           |  |  |

| VCCIB3          | 185           |  |  |

| VCCIB3          | 197           |  |  |

| VCCIB3          | 203           |  |  |

| VCCIB3          | 215           |  |  |

| VCCIB4          | 144           |  |  |

| VCCIB4          | 156           |  |  |

| VCCIB4          | 168           |  |  |

| VCCIB5          | 96            |  |  |

| VCCIB5          | 108           |  |  |

| VCCIB5          | 120           |  |  |

| VCCIB6          | 50            |  |  |

| VCCIB6          | 62            |  |  |

| VCCIB6          | 68            |  |  |

| VCCIB6          | 80            |  |  |

| VCCIB7          | 8             |  |  |

| VCCIB7          | 20            |  |  |

| VCCIB7          | 26            |  |  |

| VCCIB7          | 38            |  |  |

| VCCPLA          | 317           |  |  |

| VCCPLB          | 315           |  |  |

| VCCPLC          | 303           |  |  |

| VCCPLD          | 301           |  |  |

| VCCPLE          | 140           |  |  |

| VCCPLF          | 138           |  |  |

| CQ352           |               |

|-----------------|---------------|

| AX1000 Function | Pin<br>Number |

| VCCPLG          | 126           |

| VCCPLH          | 124           |

| VCOMPLA         | 318           |

| VCOMPLB         | 316           |

| VCOMPLC         | 304           |

| VCOMPLD         | 302           |

| VCOMPLE         | 141           |

| VCOMPLF         | 139           |

| VCOMPLG         | 127           |

| VCOMPLH         | 125           |

| VPUMP           | 267           |

Datasheet Information

| Revision                         | Changes                                                                                                                                                                                                                                                                                                                                          | Page                 |

|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| Revision 17<br>(continued)       | The C180 package was removed from product tables and the "Package Pin Assignments" section (PDN 0909).                                                                                                                                                                                                                                           | 3-1                  |

|                                  | Package names used in the "Axcelerator Family Product Profile" and "Package Pin Assignments" section were revised to match standards given in <i>Package Mechanical Drawings</i> (SAR 27395).                                                                                                                                                    | i, 3-1               |

|                                  | The "Introduction" section for "User I/Os" was updated as follows:                                                                                                                                                                                                                                                                               | 2-11                 |

|                                  | "The user does not need to assign VREF pins for OUTBUF and TRIBUF. VREF pins are needed only for input and bidirectional I/Os" (SARs 24181, 24309).                                                                                                                                                                                              |                      |

|                                  | Power values in Table 2-4 • Default CLOAD/VCCI were updated to reflect those of SmartPower (SAR 33945).                                                                                                                                                                                                                                          | 2-3                  |

|                                  | Two parameter names were corrected in Figure 2-10 • Output Buffer Delays. One occurrence of $t_{\text{ENLZ}}$ was changed to $t_{\text{ENZL}}$ and one occurrence of $t_{\text{ENHZ}}$ was changed to $t_{\text{ENZH}}$ (SAR 33890).                                                                                                             | 2-22                 |

|                                  | The "Timing Model" section was updated with new timing values. Timing tables<br>in the "I/O Specifications" section were updated to include enable paths. Values<br>in the timing tables in the "Voltage-Referenced I/O Standards" section and<br>"Differential Standards" section were updated. Table 2-63 • R-Cell was updated<br>(SAR 33945). | 2-8, 2-26 to<br>2-53 |

|                                  | Figure 2-11 • Timing Model was replaced (SAR 33043).                                                                                                                                                                                                                                                                                             | 2-23                 |

|                                  | The timing tables for "RAM" and "FIFO" were updated (SAR 33945).                                                                                                                                                                                                                                                                                 | 2-90 to 2-106        |

|                                  | "Data Registers (DRs)" values were modified for IDCODE and USERCODE (SARs 18257, 26406).                                                                                                                                                                                                                                                         | 2-108                |

|                                  | The package diagram for the "CQ208" package was incorrect and has been replaced with the correct diagram (SARs 23865, 26345).                                                                                                                                                                                                                    | 3-89                 |

| Revision 16<br>(v2.8, Oct. 2009) | The datasheet was updated to include AX2000-CQ2526 information.                                                                                                                                                                                                                                                                                  | N/A                  |

|                                  | MIL-STD-883 Class B is no longer supported by Axcelerator FPGAs and as a result was removed.                                                                                                                                                                                                                                                     | N/A                  |

|                                  | A footnote was added to the "Introduction" in the "Axcelerator Clock Management System" section.                                                                                                                                                                                                                                                 | 2-75                 |

| Revision 15                      | RoHS-compliant information was added to the "Ordering Information".                                                                                                                                                                                                                                                                              | ii                   |

| (v2.7, Nov. 2008)                | ACTgen was changed to SmartGen because ACTgen is obsolete.                                                                                                                                                                                                                                                                                       | N/A                  |

| Revision 14<br>(v2.6)            | In Table 2-4, the units for the $P_{\text{LOAD}},P_{10},\text{and}P_{\text{I/O}}$ were updated from mW/MHz to mW/MHz.                                                                                                                                                                                                                            | 2-3                  |

|                                  | In the "Pin Descriptions"section, the HCLK and CLK descriptions were updated to include tie-off information.                                                                                                                                                                                                                                     | 2-9                  |

|                                  | The "Global Resource Distribution" section was updated.                                                                                                                                                                                                                                                                                          | 2-70                 |

|                                  | The " CG624" table was updated.                                                                                                                                                                                                                                                                                                                  | 3-116                |

| Revision 13<br>(v2.5)            | A note was added to Table 2-2.                                                                                                                                                                                                                                                                                                                   | 2-1                  |

|                                  | In the "Package Thermal Characteristics", the temperature was changed from 150°C to 125°C.                                                                                                                                                                                                                                                       | 2-6                  |

| Revision              | Changes                                                                                                                                           | Page              |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| Revision 12<br>(v2.4) | Revised ordering information and timing data to reflect phase out of –3 speed grade options.                                                      |                   |

|                       | Table 2-3 was updated.                                                                                                                            | 2                 |

| Revision 11<br>(v2.3) | The "Packaging Data" section is new.                                                                                                              | iv                |

|                       | Table 2-2 was updated.                                                                                                                            | 2-1               |

|                       | "VCCDA Supply Voltage" was updated.                                                                                                               | 2-9               |

|                       | "PRA/B/C/D Probe A, B, C and D" was updated.                                                                                                      | 2-10              |

|                       | The "User I/Os" was updated.                                                                                                                      | 2-11              |

| Revision 10           | Figure 1-3 was updated.                                                                                                                           | 1-2               |

| (v2.2)                | Table 2-2 was updated.                                                                                                                            | 2-1               |

|                       | The "Power-Up/Down Sequence" section was updated.                                                                                                 | 2-1               |

|                       | Table 2-4 was updated.                                                                                                                            | 2-3               |

|                       | Table 2-5 was updated.                                                                                                                            | 2-4               |

|                       | The "Timing Characteristics" section was added.                                                                                                   | 2-7               |

|                       | Table 2-7 was updated.                                                                                                                            | 2-7               |

|                       | Figure 2-1 was updated.                                                                                                                           | 2-8               |

|                       | The External Setup and Clock-to-Out (Pad-to-Pad) equations in the "Hardwired Clock – Using LVTTL 24 mA High Slew Clock I/O" section were updated. | 2-8               |

|                       | The External Setup and Clock-to-Out (Pad-to-Pad) in the "Routed Clock – Using LVTTL 24 mA High Slew Clock I/O" section were updated.              | 2-8               |

|                       | The "Global Pins" section was updated.                                                                                                            | 2-10              |

|                       | The "User I/Os" section was updated.                                                                                                              | 2-11              |

|                       | Table 2-17 was updated.                                                                                                                           | 2-19              |

|                       | Figure 2-8 was updated.                                                                                                                           | 2-20              |

|                       | Figure 2-13 and Figure 2-14 were updated.                                                                                                         | 2-24              |

|                       | The following timing parameters were renamed in I/O timing characteristic tables from Table 2-22 to Table 2-60:                                   | 2-26 to 2-52      |

|                       | $t_{IOCLKQ} > t_{ICLKQ}$                                                                                                                          |                   |

|                       | t <sub>IOCLKY</sub> > t <sub>OCLKQ</sub>                                                                                                          |                   |

|                       | Timing numbers were updated from Table 2-22 to Table 2-78.                                                                                        | 2-26 to 2-69      |

|                       | The "R-Cell" section was updated.                                                                                                                 | 2-58              |

|                       | Figure 2-59 was updated.                                                                                                                          | 2-89              |

|                       | Figure 2-60 was updated.                                                                                                                          | 2-89              |

|                       | Figure 2-67 was updated.                                                                                                                          | 2-100             |

|                       | Figure 2-68 was updated.                                                                                                                          | 2-101             |

|                       | Table 2-89 to Table 2-93 were updated.                                                                                                            | 2-90 to 2-94      |

|                       | Table 2-98 to Table 2-102 were updated.                                                                                                           | 2-102 to<br>2-106 |

Datasheet Information

| Revision                  | Changes                                                                   | Page              |

|---------------------------|---------------------------------------------------------------------------|-------------------|

| Revision 3<br>(continued) | The timing characteristics tables from pages 2-26 to 2-60 were updated.   | 2-26 to 2-60      |

|                           | The "Global Resources" section was updated.                               | 2-66              |

|                           | The timing characteristics tables from pages 2-102 to 2-103 were updated. | 2-102 to<br>2-103 |

|                           | The "PQ208", "FG256", and "FG324" tables are new.                         | 3-9,3-16, 3-84    |